# MTCH6102

## **MTCH6102** Low-Power Projected Capacitive Touch Controller

#### **Description:**

Microchip's MTCH6102 is a turnkey projected capacitive touch controller that simplifies adding gestures to touch interface designs with industry-leading low-power performance. It utilizes up to 15 channels to support taps, swipes, and scrolling on XY touch pads and touch screens. MTCH6102 allows designers to quickly and easily integrate projected capacitive touch into their cost-sensitive, low-power application. MTCH6102 provides developers with a flexible touch-sensing solution to optimize common constraints of size, power and cost that are critical to applications such as wearable devices, remote controls, gaming devices and track pads.

#### **Applications:**

- Wearable Devices such as Headphones, Watches, Fitness Wristbands

- Track Pads and Computer Peripherals

- Input Devices with Configurable Button, Keypad or Scrolling Functions

- Any Interface with Single-Finger Gestures to Swipe, Scroll, or Doubletap Controls

- Home Automation Control Panels

- Security Control Keypads

- Automotive Center Stack Controls

- Gaming Devices

- · Remote Control Touch Pads

#### **Touch Sensor Support:**

- · Up to 15 Channels

- Sensor Sizes up to 120 mm (4.7")

- · Individual Channel Tuning for Optimal Sensitivity

- Works with Printed Circuit Board (PCB) Sensors, Film, Glass and Flexible Printed Circuit (FPC) Sensors

#### **Cover Layer Support:**

- · Plastic: up to 3 mm

- Glass: up to 5 mm

#### **Touch Performance:**

- >200 Reports per Second (configurable)

- 12-Bit Resolution Coordinate Reporting

#### **Touch Features:**

- Gesture Detection and Reporting

- Self-Capacitance Signal Acquisition

- Multiple Built-in Filtering Options

#### **Power Management:**

- Configurable Sleep/Idle Frame Rates

- Standby mode <500 nA (typical)</li>

- Active mode <12 uA possible</li>

#### **Communication Interface:**

- I<sup>2</sup>C<sup>™</sup> (up to 400 kbps)

- Both Polling and Interrupt Schemes Supported

- Sync Signal Allows for Host Frame Detection

- Field Upgradeable over I<sup>2</sup>C

#### **Operating Conditions:**

• 1.8V to 3.6V, -40°C to +85°C

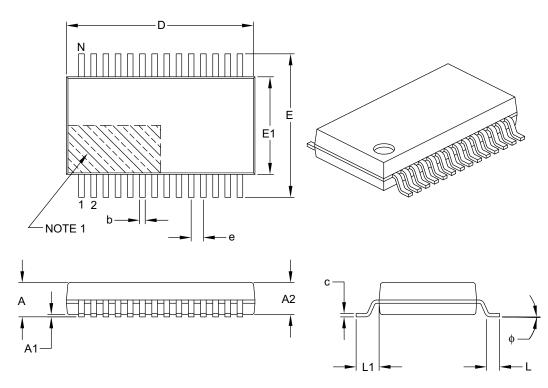

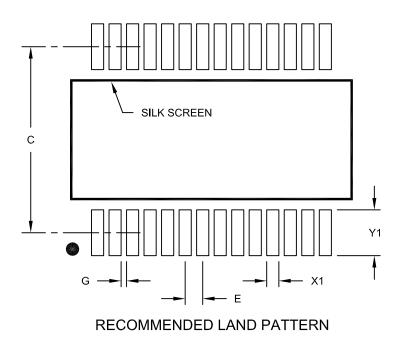

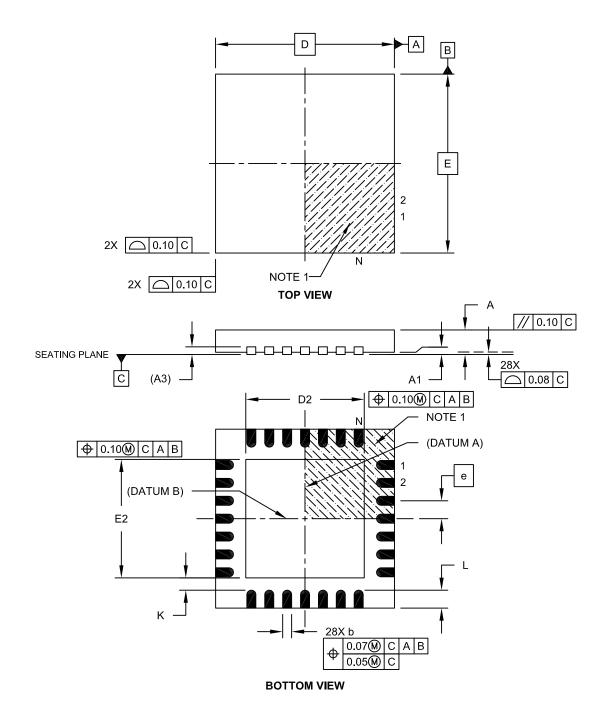

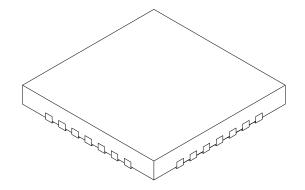

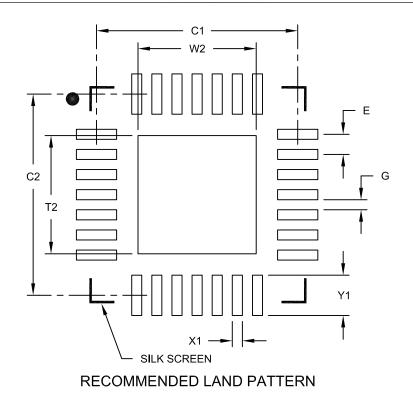

#### Package Types:

- 28-Pin SSOP

- 28-Pin UQFN

#### **Table of Contents**

| 1.0   | MTCH6102 Block Diagram                | 3  |

|-------|---------------------------------------|----|

| 2.0   | Pin Diagrams                          | 4  |

| 3.0   | MTCH6102 Pinout Description           | 5  |

| 4.0   | Layout                                |    |

| 5.0   | Communication                         |    |

| 6.0   | Sensor Design Considerations          | 10 |

| 7.0   | Operating Modes                       | 13 |

| 8.0   | Controller Commands                   | 15 |

| 9.0   | Touch Frame Control                   | 16 |

| 10.0  | Touch Data Registers                  | 17 |

| 11.0  | Acquisition and Touch Parameters      | 18 |

| 12.0  | Compensation RAM                      | 20 |

| 13.0  | Baseline                              | 21 |

| 14.0  | Gesture Features and Parameters       | 22 |

| 15.0  | Configuring a Non-Default Application | 26 |

| 16.0  | Manufacturing Testing                 | 27 |

| 17.0  | Memory Map                            |    |

| 18.0  | Electrical Characteristics            | 31 |

| 19.0  | Ordering Information                  | 35 |

| 20.0  | Packaging Information                 | 36 |

| The N | ficrochip Web Site                    | 43 |

| Custo | mer Change Notification Service       | 43 |

| Custo | mer Support                           | 43 |

| World | lwide Sales and Service               | 45 |

|       |                                       |    |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# MTCH6102

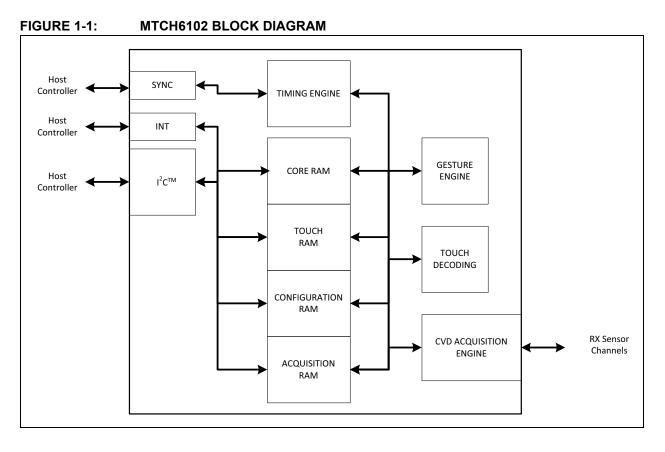

#### 1.0 MTCH6102 BLOCK DIAGRAM

# MTCH6102

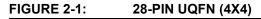

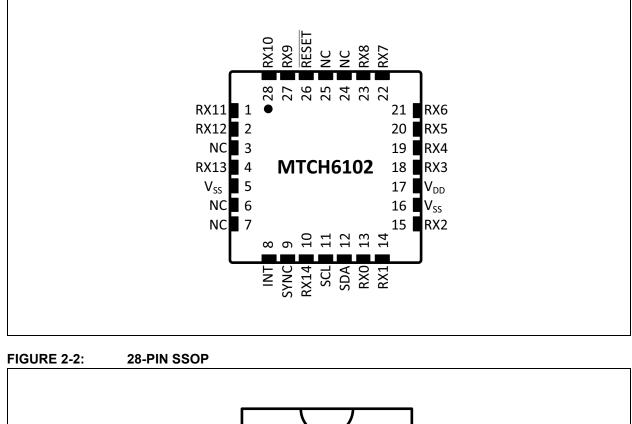

#### 2.0 PIN DIAGRAMS

# 3.0 MTCH6102 PINOUT DESCRIPTION

| Pin Name | UQFN Pin        | SSOP Pin         | Pin Type | Description                        |

|----------|-----------------|------------------|----------|------------------------------------|

| RESET    | 26              | 1                | I        | Master Reset with Internal Pull-up |

| SCL      | 11              | 14               | I/O      | I <sup>2</sup> C™ Clock            |

| SDA      | 12              | 15               | I/O      | I <sup>2</sup> C Data Input/Output |

| INT      | 8               | 11               | 0        | Interrupt Request Output           |

| SYNC     | 9               | 12               | 0        | Synchronous Frame Output           |

| RX0      | 13              | 16               | I/O      | Touch Sensor Channel Input         |

| RX1      | 14              | 17               | I/O      |                                    |

| RX2      | 15              | 18               | I/O      |                                    |

| RX3      | 18              | 21               | I/O      |                                    |

| RX4      | 19              | 22               | I/O      |                                    |

| RX5      | 20              | 23               | I/O      |                                    |

| RX6      | 21              | 24               | I/O      |                                    |

| RX7      | 22              | 25               | I/O      |                                    |

| RX8      | 23              | 26               | I/O      |                                    |

| RX9      | 27              | 2                | I/O      |                                    |

| RX10     | 28              | 3                | I/O      |                                    |

| RX11     | 1               | 4                | I/O      |                                    |

| RX12     | 2               | 5                | I/O      |                                    |

| RX13     | 4               | 7                | I/O      |                                    |

| RX14     | 10              | 13               | I/O      |                                    |

| Vdd      | 17              | 20               | Power    | Positive Supply                    |

| Vss      | 5,16            | 8,19             | Power    | Ground Reference                   |

| N/C      | 3, 6, 7, 24, 25 | 6, 9, 10, 27, 28 | N/C      | No Connect                         |

TABLE 3-1:MTCH6102 PINOUT DESCRIPTION

# MTCH6102

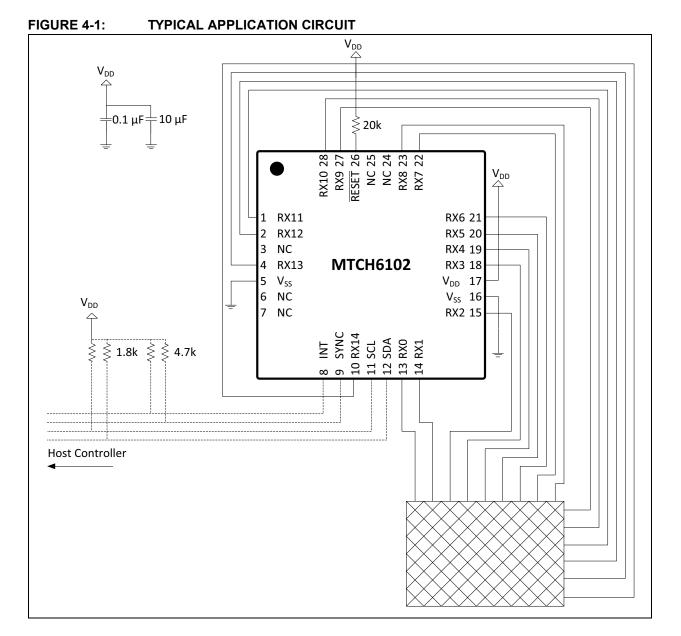

## 4.0 LAYOUT

#### 4.1 Decoupling Capacitors

The use of decoupling capacitors on power-supply pins, such as VDD and Vss, is required. Consider the following criteria when using decoupling capacitors:

1. Value and type of capacitor:

A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

2. Placement on the Printed Circuit Board:

The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

3. Handling high-frequency noise:

If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above-described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (for example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

4. Maximizing performance:

On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. It is equally important to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

#### 4.2 Bulk Capacitors

The use of a bulk capacitor is recommended to improve power-supply stability. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F. This capacitor should be located as close to the device as possible.

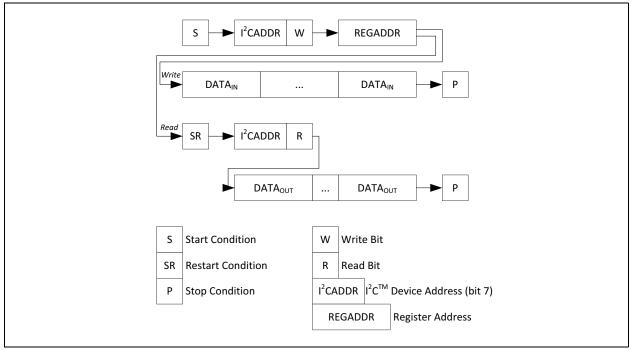

## 5.0 COMMUNICATION

#### 5.1 I<sup>2</sup>C Pin Specification

#### 5.1.1 DESCRIPTION

The MTCH6102 low-power projected capacitive touch controller uses a standard register-based read/write  $I^2C$  protocol based upon the memory map. This protocol is similar to many other devices such as temperature sensors and serial EEPROMs. Although data can be read at any time (polling), an interrupt pin (INT) is provided for flexible integration options.

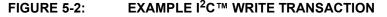

#### 5.1.2 READING/WRITING REGISTERS

To access memory (both to read or write), the  $I^2C$  transaction must start by addressing the chip with the Write bit set, then writing out a single byte of data representing the memory address to be operated on. After that, the host can choose to do either of the following (see Figure 5-1):

- 1. To write memory, continue writing [n] data bytes (see Figure 5-2).

- To read memory, restart the I<sup>2</sup>C transaction (via either a Stop-Start or Restart), then address the chip with the Read bit set. Continue to read in [n] data bytes (see Figure 5-3).

During either of these transactions, multiple bytes within the same block may be read or written due to the device's address auto-increment feature. See **Section 17.0 "Memory Map**" for block separation.

## FIGURE 5-1: I<sup>2</sup>C™ TRANSACTION DIAGRAM

#### FIGURE 5-3: EXAMPLE I<sup>2</sup>C<sup>™</sup> READ TRANSACTION Address Data I<sup>2</sup>C<sup>™</sup> 0x25 W ACK 0x10 SR 0x25 R ACK ACK 0x01 NK S Р INT

#### 5.1.3 DEVICE ADDRESSING

The MTCH6102 default 7-bit base address is 0x25. Every transmission must be prefixed with this address, as well as a bit signifying whether the transmission is a master write ('0') or master read ('1'). After appending this Read/Write bit to the base address, this first byte becomes either 0x4A (write) or 0x4B (read).

This address can be modified (see I<sup>2</sup>CADDR), but this requires initially communicating with the device under the default address. If this is not feasible in the user's application, contact Microchip support for additional options.

#### 5.2 Interrupt Pin

MTCH6102 provides an open-collector active-low Interrupt pin (INT) that will be asserted any time new data is available. INT is automatically released under two conditions:

- 1. A read is performed of *any* register within the device.

- 2. The next frame of decoding has started.

#### 5.3 SYNC Output Pin

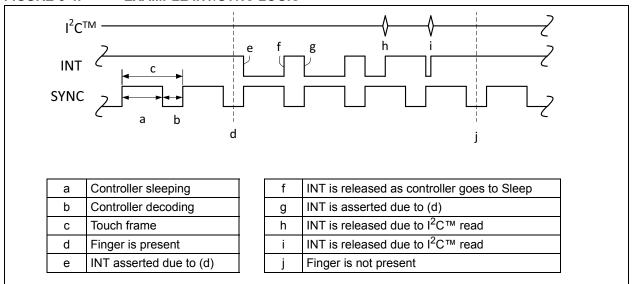

MTCH6102 provides an active-high sync signal that correlates with the current touch frame status. The SYNC pin is low while the device is sleeping (between frames) and high while touch sensing/decoding is occurring. A common use of this pin includes a host that makes use of data on every frame (such as raw-acquisition data), for host-side decoding (see Figure 5-4).

FIGURE 5-4: EXAMPLE INT/SYNC LOGIC

#### 6.0 SENSOR DESIGN CONSIDERATIONS

#### 6.1 General Guidelines

#### 6.1.1 PROTOTYPING DESIGNS

Touch sensor designs typically require a thorough debugging phase to ensure a reliable product. If possible, it is suggested that flexible prototyping hardware be created with this in mind. A common example is providing external access to the communication lines for quick test and tuning while in-circuit.

#### 6.1.2 SENSOR OVERLAY MATERIAL

To prevent saturation of sensor levels, a minimum overlay of 0.5 mm plastic or glass is required for proper operation of the device, even during a prototyping phase, even if this value is different than the final design.

| Note: | At no time should the device be expected  |

|-------|-------------------------------------------|

|       | to respond correctly to a user touching a |

|       | bare PCB sensor.                          |

#### 6.1.3 OPERATION WITH AN LCD

MTCH6102 has integrated algorithms to detect and minimize the effects of noise, but proper care should always be taken in selecting an LCD and support components with a focus on reducing noise as much as possible. Since the interaction between the touch sensor and display is highly dependent upon the physical arrangement of the components, proper testing should always be executed with a fully integrated device. Please reference the appropriate projected capacitive touch screen manufacturer's integration guide for additional design considerations.

#### 6.2 Sensor Layout Configuration

| Address | Name              | Description                        |

|---------|-------------------|------------------------------------|

| 0x20    | NUMBEROFXCHANNELS | Number of channels used for X axis |

| 0x21    | NUMBEROFYCHANNELS | Number of channels used for Y axis |

TABLE 6-1: REGISTERS ASSOCIATED WITH SENSOR LAYOUT CONFIGURATION

MTCH6102 is designed to work with sensors with a minimum of 3x3 sensor channels, and a total maximum of 15 channels. The number of channels on each axis is governed by the registers in Table 6-1. For all sensor configurations, the following conditions must be met:

- 1. Channel layout must start at RX0.

- 2. Each axis must have the associated channels in either ascending or descending order.

- 3. No unconnected channel pins are allowed in the middle of a layout.

Table 6-2 shows an example of each rule being broken by a 6x5 sensor layout, followed by the correct layout in the last column.

TABLE 6-2:EXAMPLE OF INCORRECT<br/>6X5 SENSOR CONNECTIONS

|      | (1) | (2) | (3) | Correct |

|------|-----|-----|-----|---------|

| RX0  |     | X0  | X0  | X0      |

| RX1  |     | X1  | X1  | X1      |

| RX2  |     | X2  | X2  | X2      |

| RX3  |     | X4  | X3  | X3      |

| RX4  | X0  | X3  | X4  | X4      |

| RX5  | X1  | X5  | X5  | X5      |

| RX6  | X2  | Y0  |     | Y0      |

| RX7  | X3  | Y2  |     | Y1      |

| RX8  | X4  | Y1  | Y0  | Y2      |

| RX9  | X5  | Y3  | Y1  | Y3      |

| RX10 | Y0  | Y4  | Y2  | Y4      |

| RX11 | Y1  |     | Y3  |         |

| RX12 | Y2  |     |     |         |

| RX13 | Y3  |     | Y4  |         |

| RX14 | Y4  |     |     |         |

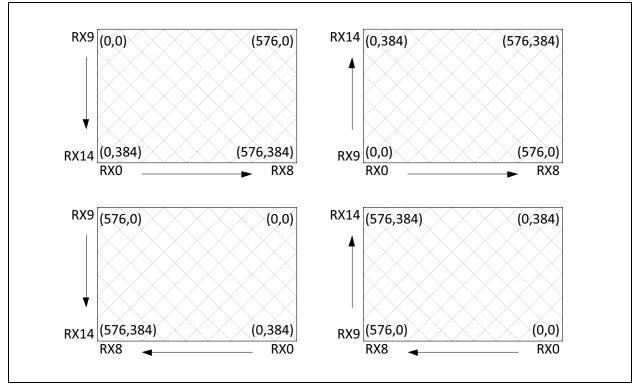

#### 6.3 Sensor Output Resolution

MTCH6102 interpolates 64 discrete points between each channel and 32 points past the centerline of each edge. As a result, the maximum value in the TOUCHX and TOUCHY registers will be (64xNUMBEROFCHANNELS) on each axis. For the default 9x6 sensor, this results in a maximum resolution of 576x384.

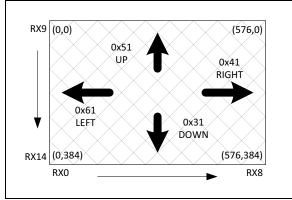

#### 6.4 Sensor Orientation

To aid in PCB layout, the sensor can be oriented in any direction, have either axis reversed, or even have the axes swapped. The host controller must take into account the X/Y output and gesture orientation based on Figure 6-2.

## 7.0 OPERATING MODES

MTCH6102 operates in multiple modes (see Table 7-1) governed by the MODE register (see Register 7-1).

| Mode<br>Name | Description                                                                                                                                             | INT Behavior                                                                           |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Full         | Full X/Y and gesture decoding occurs (Default mode)                                                                                                     | Asserted if touch is present or if a change in touch status or a gesture have occurred |

| Touch        | Full X/Y decoding only                                                                                                                                  | Asserted if touch is present or if a change in touch status occurs                     |

| Gesture      | Full X/Y and gesture decoding occurs, but INT is no longer asserted for touch data                                                                      | Asserted for gestures only <sup>(1)</sup>                                              |

| Raw          | Raw-capacitance signals are stored in RAWADC registers, no decoding done. Channel selection and type of measurement is governed by the MODECON register | None                                                                                   |

| Standby      | Device is no longer sensing or performing baseline tasks                                                                                                | None                                                                                   |

#### TABLE 7-1: OPERATING MODE DESCRIPTIONS

Note 1: Data in TOUCH registers is still valid.

#### REGISTER 7-1: MODE: TOUCH DECODE MODE REGISTER

| U-x   | U-x | U-x | U-x | R/W-0 | R/W-0 | R/W-1  | R/W-1 |

|-------|-----|-----|-----|-------|-------|--------|-------|

| —     | —   | —   | —   |       | MOD   | E<3:0> |       |

| bit 7 |     |     |     |       |       |        | bit 0 |

| Legend:          |                      |                       |                                              |

|------------------|----------------------|-----------------------|----------------------------------------------|

| R = Readable bit | '1' = Bit is set     | x = Bit is unknown    | -n = Value after initialization<br>(default) |

| W = Writable bit | '0' = Bit is cleared | U = Unimplemented bit | q = Conditional                              |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 **MODE<3:0>:** Touch Decoding mode bits

- 0000 = Standby

- 0001 = Gesture

- 0010 = Touch only

- 0011 = Full (touch and gesture)

- 01XX = Raw ADC

|                                   | · · -· · ·· | OBEOONTRA             |                 |              | INE OIG LEIN                    |                 |       |

|-----------------------------------|-------------|-----------------------|-----------------|--------------|---------------------------------|-----------------|-------|

| R/W-0                             | R/W-0       | ) R/W-0               | R/W-0           | R/W-0        | R/W-0                           | R/W-0           | R/W-0 |

|                                   | TY          | ′PE<3:0>              |                 |              | С                               | H<3:0>          |       |

| bit 7                             |             |                       |                 |              |                                 |                 | bit 0 |

|                                   |             |                       |                 |              |                                 |                 |       |

| Legend:                           |             |                       |                 |              |                                 |                 |       |

| R = Readable bit '1' = Bit is set |             |                       | x = Bit is unkr | nown         | -n = Value after i<br>(default) | nitialization   |       |

| W = Writab                        | le bit      | '0' = Bit is cle      | eared           | U = Unimplen | nented bit                      | q = Conditional |       |

|                                   |             |                       |                 |              |                                 |                 |       |

| bit 7-4                           | TYPE<3:     | :0>: CVD Result A     | Arithmetic bits | S            |                                 |                 |       |

|                                   | 0000 =      | (1023 – Result        | 1) + Result 2   | 2            |                                 |                 |       |

|                                   | 0001 =      | Result 1 only         |                 |              |                                 |                 |       |

|                                   | 0010 =      | Result 2 only         |                 |              |                                 |                 |       |

| bit 3-0                           | CH<3:0>     | : RX Sense Char       | inel bits       |              |                                 |                 |       |

|                                   | 0000 =      | RX0                   |                 |              |                                 |                 |       |

|                                   |             |                       |                 |              |                                 |                 |       |

|                                   |             |                       |                 |              |                                 |                 |       |

|                                   | 1110 =      | RX14<br>Reconved do r | ot upo          |              |                                 |                 |       |

|                                   | 1111 =      | Reserved, do r        | ioi use         |              |                                 |                 |       |

#### REGISTER 7-2: MODECON: RAWADC MODE CONTROL REGISTER

#### 8.0 CONTROLLER COMMANDS

Various controller commands can be initiated by writing a '1' to the appropriate bit in the CMD register (Register 8-1). This bit will automatically be cleared after the command has been completed.

#### REGISTER 8-1: CMD: COMMAND REGISTER

| R/W-0 | R/W-0 | R/W-0 | U-x | R/W-0 | U-x | U-x | R/W-0 |

|-------|-------|-------|-----|-------|-----|-----|-------|

| NV    | DEF   | CFG   | —   | MFG   | —   | —   | BS    |

| bit 7 |       |       |     |       |     |     | bit 0 |

| Legend:          |                      |                       |                                              |

|------------------|----------------------|-----------------------|----------------------------------------------|

| R = Readable bit | '1' = Bit is set     | x = Bit is unknown    | -n = Value after initialization<br>(default) |

| W = Writable bit | '0' = Bit is cleared | U = Unimplemented bit | q = Conditional                              |

| bit 7   | NV: Nonvolatile Storage Write bit                                  |

|---------|--------------------------------------------------------------------|

| bit 6   | DEF: Restore Controller to Default Configuration Values bit        |

| bit 5   | CFG: Configure Controller bit (after parameters have been changed) |

| bit 4   | Unimplemented: Read as '0'                                         |

| bit 3   | MFG: Execute Manufacturing Test bit                                |

| bit 2-1 | Unimplemented: Read as '0'                                         |

| bit 0   | BS: Force Baseline bit (recalibration) to occur                    |

|         |                                                                    |

#### 9.0 TOUCH FRAME CONTROL

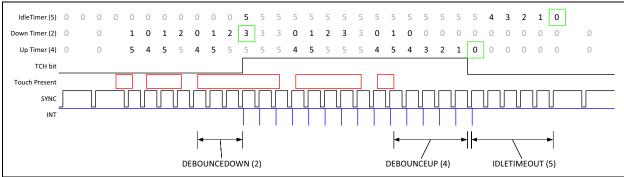

Touch decoding is based around the concept of a touch *frame* that begins with acquisition, followed by decoding of the acquired values, and lastly a Sleep phase for power savings. The duration of the touch frame is governed by the current touch state, as well as the timing registers outlined in this section (see Table 9-1). Figure 9-1 shows the interaction between these registers during a typical touch cycle.

# TABLE 9-1:REGISTERS ASSOCIATED<br/>WITH TOUCH FRAME<br/>CONTROL

| Address | Name          | Description            |

|---------|---------------|------------------------|

| 0x25    | ACTIVEPERIODL | Active Period          |

| 0x26    | ACTIVEPERIODH |                        |

| 0x27    | IDLEPERIODL   | Idle Period            |

| 0x28    | IDLEPERIODH   |                        |

| 0x29    | IDLETIMEOUT   | Idle Timeout           |

| 0x2B    | DEBOUNCEUP    | Liftoff Debounce       |

| 0x2C    | DEBOUNCEDOWN  | Touch Down<br>Debounce |

|         |               | Debouilce              |

#### FIGURE 9-1: TOUCH FRAME TIMING

Both active and idle period calculations are as shown in Equation 9-1.

**EQUATION 9-1:**

$$\left(\frac{Duration(ms) \times 1000}{31}\right) + 1 = PERIOD$$

Typical frame rates have been computed for the user's convenience and are shown in Table 9-2.

| <b>TABLE 9-2:</b> | EXAMPLE FRAME RATE  |  |  |  |  |

|-------------------|---------------------|--|--|--|--|

|                   | PERIOD CALCULATIONS |  |  |  |  |

| Desired Rate<br>(ms) | Period |

|----------------------|--------|

| 10                   | 0x0142 |

| 20                   | 0x0284 |

| 50                   | 0x064C |

| 100                  | 0x0C99 |

## 10.0 TOUCH DATA REGISTERS

| R/W-0          | R/W-0 | R/W-0             | R/W-0 | U-x             | R/W-0      | R/W-0                         | R/W-0          |

|----------------|-------|-------------------|-------|-----------------|------------|-------------------------------|----------------|

|                | FRAM  | E<3:0>            |       | _               | LRG        | GES                           | ТСН            |

| bit 7          |       |                   |       |                 |            |                               | bit            |

| Legend:        |       |                   |       |                 |            |                               |                |

| R = Readable   | bit   | '1' = Bit is set  |       | x = Bit is unki | nown       | -n = Value after<br>(default) | initialization |

| W = Writable b | bit   | '0' = Bit is clea | ared  | U = Unimpler    | mented bit | q = Conditional               |                |

#### **REGISTER 10-1: TOUCHSTATE: CURRENT TOUCH STATE REGISTER**

| bit 7-4 | FRAME<3:0>: Increments on Every Touch Frame |

|---------|---------------------------------------------|

| bit 3   | Unimplemented: Read as '0'                  |

| bit 2   | LRG: Large Activation is Present            |

| bit 1   | GES: Gesture is Present                     |

| bit 0   | TCH: Touch is Present                       |

#### REGISTER 10-2: TOUCHLSB REGISTER

| R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-------|--------|-------|-------------|-------|-------|-------|--|

|       | TOUCH | X<3:0> |       | TOUCHY<3:0> |       |       |       |  |

| bit 7 |       |        |       |             |       |       | bit 0 |  |

| Legend:          |                      |                       |                                              |

|------------------|----------------------|-----------------------|----------------------------------------------|

| R = Readable bit | '1' = Bit is set     | x = Bit is unknown    | -n = Value after initialization<br>(default) |

| W = Writable bit | '0' = Bit is cleared | U = Unimplemented bit | q = Conditional                              |

bit 7-4 **TOUCHX<3:0>:** Current X Position (Least Significant bits)

bit 3-0 **TOUCHY<3:0>:** Current Y Position (Least Significant bits)

#### TABLE 10-1: SUMMARY OF REGISTERS ASSOCIATED WITH TOUCH DATA

| Address | Name       | Bit 7                   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|------------|-------------------------|-------|-------|-------|-------|-------|-------|-------|

| 0x10    | TOUCHSTATE | FRAME<3:0>              |       |       |       | _     | LRG   | GES   | TCH   |

| 0x11    | TOUCHX     | TOUCHX<11:4>            |       |       |       |       |       |       |       |

| 0x12    | TOUCHY     | TOUCHY<11:4>            |       |       |       |       |       |       |       |

| 0x13    | TOUCHLSB   | TOUCHX<3:0> TOUCHY<3:0> |       |       |       |       |       |       |       |

#### 11.0 ACQUISITION AND TOUCH PARAMETERS

# TABLE 11-1:REGISTERS ASSOCIATED<br/>WITH ACQUISITION AND<br/>TOUCH PARAMETERS

| Address | Name                   | Default |

|---------|------------------------|---------|

| 0x22    | SCANCOUNT              | 6       |

| 0x23    | TOUCHTHRESHX           | 55      |

| 0x24    | TOUCHTHRESHY           | 40      |

| 0x2A    | HYSTERESIS             | 4       |

| 0x31    | FILTERTYPE             | 2       |

| 0x32    | FILTERSTRENGTH         | 1       |

| 0x35    | LARGEACTIVATIONTHRESHL | 0       |

| 0x36    | LARGEACTIVATIONTHRESHH | 0       |

#### 11.1 SCANCOUNT

Every time a channel is scanned, it is scanned multiple times (SCANCOUNT) and summed. Increasing this number will give an inherent averaging effect, but at the cost of time and subsequently increased power consumption.

#### 11.2 TOUCHTHRESHX/ TOUCHTHRESHY and HYSTERESIS

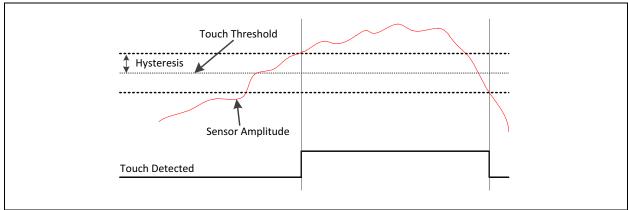

The presence of a touch is determined by the sensor channel's current value compared to the touch thresholds set by TOUCHTHRESHX (or TOUCHTHRESHY if the channel is on the Y axis).

The HYSTERESIS register contains a threshold modifier that acts as a dynamic threshold modifier depending on the state of the touch (higher without a touch). A single channel of touch is shown in Figure 11-1.

#### FIGURE 11-1: TOUCH THRESHOLD AND HYSTERESIS FUNCTIONALITY

#### 11.3 FILTERTYPE/FILTERSTRENGTH

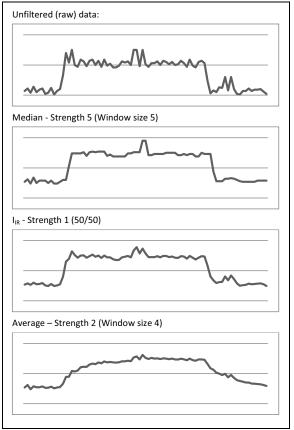

As new sensor values are acquired, they are filtered based on the settings of the FILTERTYPE/ FILTERSTRENGTH registers (see Table 11-2). Examples of the effects of each filter type are shown in Figure 11-2.

#### TABLE 11-2: FILTERTYPE AND FILTERSTRENGTH DEFINITIONS

| FILTERTYPE    | FILTERSTRENGTH                         | Valid Values                                     |

|---------------|----------------------------------------|--------------------------------------------------|

| 0 – No Filter | N/A                                    | _                                                |

| 1 – Median    | Size of median window                  | 3, 5, 7, 9                                       |

| 2 – Iir       | Weighting of previous to current value | 1, 2, 3 (1/2, 1/4 and 1/8 weighting accordingly) |

| 3 – Average   | Size of average window                 | 1, 2, 3 (2, 4 and 8 accordingly)                 |

#### FIGURE 11-2: FILTER EXAMPLES

Choosing the correct filtering option for the user's application depends on the environment and sensor. Note that while the median filter has good characteristics, it is not the most efficient and will consume more power than other filters.

#### 11.4 Large Activation

The LARGEACTIVATIONTHRESH registers provide a way to do simple rejection of signals that are too large to interpret. The amplitude of all sensor channels are added together and compared to this threshold. If greater, the LRG bit of the TOUCHSTATE register (Register 10-1) will be set.

Note that this does not affect touch decoding. In other words, even if the large activation threshold is breached, the controller will still decode the touch position as normal. The LRG bit merely serves to inform the host that the large activation threshold has been reached.

If this functionality is not intended to be used, this register should be set to zero, which will disable the large activation routines from running.

#### 12.0 COMPENSATION RAM

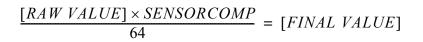

It is very common for a typical touch sensor to have non-uniform capacitive properties. To equalize the sensor, a series of coefficients can be written to the compensation RAM block. These coefficients represent a ratio that is applied to the individual channel in post-acquisition, before touch decoding occurs.

#### EQUATION 12-1: COMPENSATION RAM CALCULATION

To obtain the correct compensation RAM values, the following procedure should be used:

- Set all SENSORVALUES registers to zero (if necessary).

- Record the peak values that occur in the SENSORVALUES registers when using the sensor under normal conditions (column A of Table 12-1).

- 3. Pick a commonly occurring value to represent the median of the set ('125').

- 4. Calculate the ratio of the peak value by dividing the median value by the peak (column B).

- 5. Multiply this value by 64 and truncate (column C). These are the compensation values that should be written to the SENSORCOMP registers. Please note that, if no compensation is required (value of '64', ratio of '1'), the register should be set to '0', to save time running compensation routines for that channel.

- 6. To see the expected output from the compensation values, follow Equation 12-1 (result in column D).

| СН | Α   | В     | С      | D   |

|----|-----|-------|--------|-----|

| 0  | 102 | 1.225 | 78     | 124 |

| 1  | 113 | 1.106 | 71     | 125 |

| 2  | 118 | 1.059 | 68     | 125 |

| 3  | 125 | 1     | 64 (0) | 125 |

| 4  | 125 | 1     | 64 (0) | 125 |

| 5  | 128 | 0.977 | 63     | 126 |

| 6  | 132 | 0.947 | 61     | 126 |

| 7  | 160 | 0.781 | 50     | 125 |

## TABLE 12-1:COMPENSATION RAM<br/>EXAMPLE CALCULATION

#### 13.0 BASELINE

Capacitive touch principles rely on analyzing a change in capacitance from a previously-stored baseline value (sometimes referred to as a calibration value). Baseline routines and behavior can be tweaked using the registers listed in Table 13-1.

| Address | Bit 7 | Bit 6          | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1 | Bit 0 | Default |

|---------|-------|----------------|-------|--------|---------|-------|-------|-------|---------|

| 0x04    | NV    | DEF            | CFG   | -      | MFG     | -     | -     | BS    | 0       |

| 0x2D    |       | BASEINTERVALL  |       |        |         |       |       |       |         |

| 0x2E    |       | BASEINTERVALH  |       |        |         |       |       |       | 0       |

| 0x2F    |       | BASEPOSFILTER  |       |        |         |       |       |       | 20      |

| 0x30    |       | BASENEGFILTER  |       |        |         |       |       |       | 20      |

| 0x33    |       | BASEFILTERTYPE |       |        |         |       |       |       | 2       |

| 0x34    |       |                | BASEF | ILTERS | TRENGTH |       |       |       | 1       |

TABLE 13-1: REGISTERS ASSOCIATED WITH BASELINE

#### 13.1 BS Bit (CMD Register)

The BS bit forces the current sensor values to be stored as the baseline values, disregarding the constraints of BASEPOSFILTER and BASENEGFILTER.

#### 13.2 BASEINTERVAL

It represents the number of touch frames between baseline sampling. Data that is sampled will be applied at the next baseline interval, provided that a touch has not occurred between the two.

If at any point, the touch threshold is breached, the baseline counter is reset, and a full interval without a touch must occur before baselining resumes.

Note that this value is specified in terms of the number of touch frames, so any changes in frame rate should take this into consideration by raising or lowering this interval accordingly.

#### 13.3 BASEPOSFILTER/BASENEGFILTER

The positive and negative filters act as slew-rate limiters for a new baseline being applied. For example, if the new baseline value is larger than the previous by a value of 35, and the BASEPOSFILTER is set to 20 (default), the new baseline will only be increased by 20.

Use of these registers helps prevent unwanted spikes in the baseline value.

#### 13.4 BASEFILTERTYPE/ BASEFILTERSTRENGTH

Baseline acquisition frames follow the same filter type and strength parameters as normal acquisition filters, defined in **Section 11.3** "FILTERTYPE/FILTER-STRENGTH".

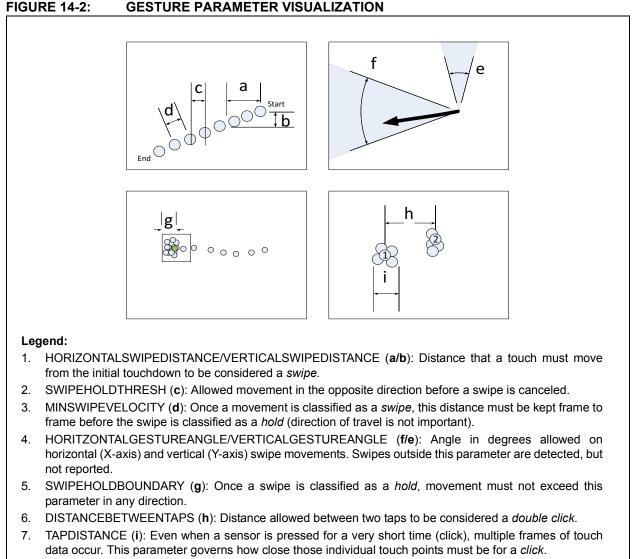

#### 14.0 GESTURE FEATURES AND PARAMETERS

Gesture detection and reporting is governed by the registers outlined in Table 14-1.

| Address | Name                    | Bit 7            | Bit 6                   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | Default |

|---------|-------------------------|------------------|-------------------------|--------|--------|--------|--------|-------|-------|---------|

| 0x10    | TOUCHSTATE              |                  | FRAM                    | E<3:0> |        | -      | LRG    | GES   | TCH   | N/A     |

| 0x14    | GESTURESTATE            |                  |                         |        | GESTL  | IRESTA | TE     |       |       | 0       |

| 0x15    | GESTUREDIAG             |                  | GESTUREDIAG             |        |        |        | 0      |       |       |         |

| 0x37    | HORIZONTALSWIPEDISTANCE |                  | HORIZONTALSWIPEDISTANCE |        |        |        | 64     |       |       |         |

| 0x38    | VERTICALSWIPEDISTANCE   |                  | VERTICALSWIPEDISTANCE   |        |        |        | 64     |       |       |         |

| 0x39    | SWIPEHOLDBOUNDARY       |                  | SWIPEHOLDBOUNDARY       |        |        |        | 25     |       |       |         |

| 0x3A    | TAPDISTANCE             |                  | TAPDISTANCE             |        |        |        | 25     |       |       |         |

| 0x3B    | DISTANCEBETWEENTAPS     |                  | DISTANCEBETWEENTAPS     |        |        |        | 64     |       |       |         |

| 0x3C    | TAPHOLDTIME             | TAPHOLDTIMEL     |                         |        |        |        |        |       | 50    |         |

| 0x3D    | TAPHOEDTIME             | TAPHOLDTIMEH     |                         |        |        |        |        |       | 0     |         |

| 0x3E    | GESTURECLICKTIME        |                  |                         | GE     | STUR   | ECLICK | TIME   |       |       | 12      |

| 0x3F    | SWIPEHOLDTHRESH         |                  |                         | SV     | VIPEHO | OLDTHF | RESH   |       |       | 32      |

| 0x40    | MINSWIPEVELOCITY        | MINSWIPEVELOCITY |                         |        | 4      |        |        |       |       |         |

| 0x41    | HORIZONTALGESTUREANGLE  |                  | HORIZONTALGESTUREANGLE  |        |        | 45     |        |       |       |         |

| 0x42    | VERTICALGESTUREANGLE    |                  |                         | VERT   | ICALGI | ESTUR  | EANGLE | Ξ     |       | 45      |

TABLE 14-1:

SUMMARY OF REGISTERS ASSOCIATED WITH GESTURES

When a gesture is performed, the gesture ID will be placed in GESTURESTATE, and the GES bit of the TOUCHSTATE register will be set. Both of these items are cleared after reading the GESTURESTATE register. The GESTUREDIAG register contains a code explaining the logic behind the last operation of the gesture engine, primarily to help with debugging of the gesture parameters. These diagnostic codes are shown in Register 14-2.

| R/W-0            | R/W-0   | R/W-0            | R/W-0    | R/W-0                 | R/W-0    | R/W-0                                        | R/W-0 |  |

|------------------|---------|------------------|----------|-----------------------|----------|----------------------------------------------|-------|--|

|                  |         |                  | GESTU    | RESTATE<7:0>          | <b>`</b> |                                              |       |  |

| bit 7            |         |                  |          |                       |          |                                              | bit 0 |  |

|                  |         |                  |          |                       |          |                                              |       |  |

| Legend:          |         |                  |          |                       |          |                                              |       |  |

| R = Readable bit |         | '1' = Bit is set |          | x = Bit is unkr       | IOWN     | -n = Value after initialization<br>(default) |       |  |

| W = Writable bit |         | '0' = Bit is cle | ared     | U = Unimplemented bit |          | q = Conditional                              |       |  |

| bit 7-0          | GESTURE | STATE<7:0>:      |          |                       |          |                                              |       |  |

|                  | 0x00    | No Gesture F     | Present  |                       |          |                                              |       |  |

|                  | 0x10    | Single Click     |          |                       |          |                                              |       |  |

|                  | 0x11    | Click and Hol    | d        |                       |          |                                              |       |  |

|                  | 0x20    | Double Click     |          |                       |          |                                              |       |  |

|                  | 0x31    | Down Swipe       |          |                       |          |                                              |       |  |

|                  | 0x32    | Down Swipe       | and Hold |                       |          |                                              |       |  |

|                  | 0x41    | Right Swipe      |          |                       |          |                                              |       |  |

|                  | 0x42    | Right Swipe a    | and Hold |                       |          |                                              |       |  |

|                  | a = /   |                  |          |                       |          |                                              |       |  |

#### REGISTER 14-1: GESTURESTATE: CURRENT GESTURE STATE REGISTER

| 0x00 | No Gesture Present   |

|------|----------------------|

| 0x10 | Single Click         |

| 0x11 | Click and Hold       |

| 0x20 | Double Click         |

| 0x31 | Down Swipe           |

| 0x32 | Down Swipe and Hold  |

| 0x41 | Right Swipe          |

| 0x42 | Right Swipe and Hold |

| 0x51 | Up Swipe             |

| 0x52 | Up Swipe and Hold    |

| 0x61 | Left Swipe           |

| 0x62 | Left Swipe and Hold  |

Please note that the gesture orientations listed in Register 14-1 are correct for a default layout, with right moving on increasing X-axis channels, and down moving on increasing Y-axis channels. These default orientations are shown in Figure 14-1. Depending on the application, the host may need to associate the gesture IDs differently.

| R/W-0                                                                       | R/W-0   | R/W-0            | R/W-0 | R/W-0           | R/W-0 | R/W-0                                        | R/W-0 |  |  |  |  |  |

|-----------------------------------------------------------------------------|---------|------------------|-------|-----------------|-------|----------------------------------------------|-------|--|--|--|--|--|

| GESTUREDIAG<7:0>                                                            |         |                  |       |                 |       |                                              |       |  |  |  |  |  |

| bit 7                                                                       |         |                  |       |                 |       |                                              | bit 0 |  |  |  |  |  |

|                                                                             |         |                  |       |                 |       |                                              |       |  |  |  |  |  |

| Legend:                                                                     |         |                  |       |                 |       |                                              |       |  |  |  |  |  |

| R = Readable bit                                                            |         | '1' = Bit is set |       | x = Bit is unkr | nown  | -n = Value after initialization<br>(default) |       |  |  |  |  |  |

| W = Writable bit '0' = Bit is cleared U = Unimplemented bit q = Conditional |         |                  |       |                 |       |                                              |       |  |  |  |  |  |

| bit 7-0                                                                     | GESTURE | DIAG<7:0>:       |       |                 |       |                                              |       |  |  |  |  |  |

#### REGISTER 14-2: GESTUREDIAG: GESTURE DIAGNOSTICS REGISTER

#### bit 7-0 GESTUREDIAG<7:0>:

| 0x01 | Click Timeout                               |

|------|---------------------------------------------|

| 0x02 | Swipe Timeout                               |

| 0x03 | General Timeout                             |

| 0x04 | Click Threshold Exceeded                    |

| 0x05 | Swipe Threshold Exceeded                    |

| 0x06 | Swipe and Hold Threshold Exceeded           |

| 0x07 | Swipe Opposite Direction Threshold Exceeded |

| 0x08 | Reserved                                    |

| 0x09 | Swipe and Hold Value Exceeded               |

| 0x0A | Outside Swipe Angle                         |

DS40001750A-page 24

#### 14.1 Gesture Tuning

- 8. TAPHOLDTIME (not shown): Duration of time a click must be held for to be considered a *click and hold*.

- 9. GESTURECLICKTIME (not shown): Maximum time between two clicks to be considered a *double click*.

#### 15.0 CONFIGURING A NON-DEFAULT APPLICATION

When modifying sensor configuration parameters, the CFG bit of the CMD register must be set for the configuration to take effect. Setting this bit analyzes the following registers for validity and coerces them if necessary:

- 1. IDLEPERIOD/ACTIVEPERIOD

- 2. FILTERTYPE/FILTERSTRENGTH

- 3. BASELINEFILTERTYPE/FILTERSTRENGTH

- 4. NUMBEROFXCHANNELS/NUMBEROFYCHAN-NELS

Afterwards, the values take effect, and the sensor is base-lined and ready for use.

| Note: | If the controller is not in Standby mode |

|-------|------------------------------------------|

|       | when changing configuration parameters,  |

|       | unreliable touch data may be generated   |

|       | until the CFG is set.                    |

Most applications will require custom parameters to be stored in the configuration RAM. The following methods are recommended for achieving this:

- For permanent configuration: Either during manufacturing test or on first start-up, the host controller writes all configuration values to the controller, sets the CFG bit and stores them to NVRAM by using the NV bit.

- 2. For configuration on every power-up: The host writes all configuration data to the controller and sets the CFG bit on start-up.

#### 16.0 MANUFACTURING TESTING

#### 16.1 Automated Manufacturing Test

To start the automated manufacturing test, set the MFG bit of the CMD register. This test re-purposes the same RAM used for RAWADC commands to store the results. When the test is complete, the MFG bit will be cleared. The results of the manufacturing test are stored in the registers shown in Table 16-1.

| TABLE 16-1: MFG TEST RX LOOK-UP TABLE <sup>(1,2)</sup> | TABLE 16-1: | MFG TEST RX LOOK-UP TABLE <sup>(1,2)</sup> |

|--------------------------------------------------------|-------------|--------------------------------------------|

|--------------------------------------------------------|-------------|--------------------------------------------|

| Address | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0XD0    | —     | —     | RX13H | —     | RX12H | RX11H | RX10H | RX9H  |

| 0XD1    | —     | —     | RX13L | —     | RX12L | RX11L | RX10L | RX9L  |

| 0XD2    | —     | —     | RX8H  | RX7H  | RX6H  | RX5H  | RX4H  | RX3H  |

| 0XD3    | —     | —     | RX8L  | RX7L  | RX6L  | RX5L  | RX4L  | RX3L  |

| 0XD4    | RX2H  | RX1H  | RX0H  | —     | _     | RX14H | _     | _     |

| 0XD5    | RX2L  | RX1L  | RX0L  | —     | _     | RX14L | _     | _     |

Note 1: RXnH: Pin was unable to set high and is likely shorted to VDD.

2: RXnL: Pin was unable to set low and is likely shorted to GND.

#### 16.2 Sensor Integrity Testing

To test the integrity of both the touch sensor and the overlay for defects, the following test outline is advised:

- 1. For this test, a way to retrieve data from the MTCH6102 will be required. This can be either through a host controller, or the host controller can conduct the test itself with pre-set test values.

- 2. Collect the raw-capacitance values by reading the RAWVALUES registers under normal conditions on a set of at least 30 completely assembled sensors.

- 3. Use the information collected in step 2 to determine the variance and average value for each sensor channel. These values will be used as the standard by which manufactured sensors will need to fall within.

- For each new sensor produced, compare the RAWVALUES to the range described in step 3. If the sensor falls out of this range, inspect the sensor assembly for defects.

- 5. To test for touch acquisition ability, repeat steps 1-4 with a known touch stimulus applied (e.g., simulated metal finger).

The above outline is intentionally generic, as manufacturing test setup will need to be modified for every application.

#### 17.0 MEMORY MAP

#### TABLE 17-1: CORE RAM MEMORY MAP

| Addr. | Name    | Core F            | RAM      |        |       |       |       |       |       |         |

|-------|---------|-------------------|----------|--------|-------|-------|-------|-------|-------|---------|

| Auur. | Name    | Bit 7             | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default |

| 0x00  | FWMAJOR |                   | FW MAJOR |        |       |       |       |       |       |         |

| 0x01  | FWMINOR |                   | FW MINOR |        |       |       |       |       |       |         |

| 0x02  | APPID   | APPIDH <15:8>     |          |        |       |       |       |       | 0x00  |         |

| 0x03  |         | APPIDL <7:0>      |          |        |       |       |       |       |       | 0x12    |

| 0x04  | CMD     | NV                | DEF      | CFG    | _     | MFG   |       | —     | BS    | 0x00    |

| 0x05  | MODE    | — — — — MODE<3:0> |          |        |       |       |       | 0x03  |       |         |

| 0x06  | MODECON |                   | TYP      | E<3:0> |       |       | CH<   | 3:0>  |       | 0x00    |

#### TABLE 17-2: TOUCH RAM MEMORY MAP

|       |              | Touch | RAM                     |         |        |          |       |       |       |         |

|-------|--------------|-------|-------------------------|---------|--------|----------|-------|-------|-------|---------|

| Addr. | Name         | Bit 7 | Bit 6                   | Bit 5   | Bit 4  | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Default |

| 0x10  | TOUCHSTATE   |       | FRAN                    | 1E<3:0> |        |          | LRG   | GES   | TCH   | 0x00    |

| 0x11  | TOUCHX       |       | TOUCHX<11:4>            |         |        |          |       |       |       |         |

| 0x12  | TOUCHY       |       |                         |         | TOUCH  | HY<11:4> |       |       |       | 0x00    |

| 0x13  | TOUCHLSB     |       | TOUCHX<3:0> TOUCHY<3:0> |         |        |          |       |       | 0x00  |         |

| 0x14  | GESTURESTATE |       | GESTURESTATE            |         |        |          |       |       | 0x00  |         |

| 0x15  | GESTUREDIAG  |       |                         | GI      | ESTURE | DIAGNOS  | TIC   |       |       | 0x00    |

#### TABLE 17-3: COMPENSATION RAM MEMORY MAP

| Addr. | Compensat                                                                                           | ion RAM                |  |         |                   |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------|------------------------|--|---------|-------------------|--|--|--|--|--|

| Addr. | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         I |                        |  |         |                   |  |  |  |  |  |

| 0x50  |                                                                                                     | SENSORCOMP <rx0></rx0> |  |         |                   |  |  |  |  |  |

|       |                                                                                                     |                        |  |         |                   |  |  |  |  |  |

| 0x5F  |                                                                                                     |                        |  | SENSORC | OMP <rx14></rx14> |  |  |  |  |  |

| A al al u | Acquisition | RAM                        |       |          |                   |       |       |       |  |  |  |

|-----------|-------------|----------------------------|-------|----------|-------------------|-------|-------|-------|--|--|--|

| Addr.     | Bit 7       | Bit 6                      | Bit 5 | Bit 4    | Bit 3             | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| 0x80      |             | SENSORVALUES <rx0></rx0>   |       |          |                   |       |       |       |  |  |  |

|           |             |                            |       |          |                   |       |       |       |  |  |  |

| 0x8E      |             | SENSORVALUES <rx14></rx14> |       |          |                   |       |       |       |  |  |  |

| _         |             |                            |       |          |                   |       |       |       |  |  |  |

| 0x90      |             |                            |       | RAWVAL   | JES <rx0></rx0>   |       |       |       |  |  |  |

|           |             |                            |       |          |                   |       |       |       |  |  |  |

| 0xAC      |             |                            |       | RAWVALL  | IES <rx14></rx14> |       |       |       |  |  |  |

|           |             |                            |       |          |                   |       |       |       |  |  |  |

| 0xB0      |             |                            |       | BASEVAL  | UES <rx0></rx0>   |       |       |       |  |  |  |

|           |             |                            |       |          | ••                |       |       |       |  |  |  |

| 0xCC      |             |                            |       | BASEVALU | JES <rx15></rx15> |       |       |       |  |  |  |

|           |             |                            |       |          |                   |       |       |       |  |  |  |

| 0xD0      |             | RAWADC<0>                  |       |          |                   |       |       |       |  |  |  |

|           |             |                            |       |          | ••                |       |       |       |  |  |  |

| 0xEF      |             |                            |       | SENSORV  | ALUES<31>         |       |       |       |  |  |  |

#### TABLE 17-4: ACQUISITION RAM MEMORY MAP

| Addr. | Configuration RAM |                        |       |                   |          |       |       |       |         |

|-------|-------------------|------------------------|-------|-------------------|----------|-------|-------|-------|---------|

| Auur. | Bit 7             | Bit 6                  | Bit 5 | Bit 4             | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Default |

| 0x20  |                   | NUMBEROFXCHANNELS      |       |                   |          |       |       |       | 0x09    |

| 0x21  |                   |                        | NU    | MBEROF            | YCHANNE  | ELS   |       |       | 0x06    |

| 0x22  |                   |                        |       | SCAN              | COUNT    |       |       |       | 0x06    |

| 0x23  |                   |                        |       | TOUCHT            | HRESHX   |       |       |       | 0x37    |

| 0x24  |                   |                        |       | TOUCHT            | HRESHY   |       |       |       | 0x28    |

| 0x25  |                   |                        |       | ACTIVE            | PERIODL  |       |       |       | 0x85    |

| 0x26  |                   |                        |       | ACTIVE            | PERIODH  |       |       |       | 0x02    |

| 0x27  |                   |                        |       | IDLEPE            | ERIODL   |       |       |       | 0x4C    |

| 0x28  |                   |                        |       | IDLEPE            | RIODH    |       |       |       | 0x06    |

| 0x29  |                   |                        |       | IDLETI            | MEOUT    |       |       |       | 0x10    |

| 0x2A  |                   |                        |       | HYSTE             | RESIS    |       |       |       | 0x04    |

| 0x2B  |                   |                        |       | DEBOU             | NCEUP    |       |       |       | 0x01    |

| 0x2C  |                   |                        |       | DEBOUN            | CEDOWN   |       |       |       | 0x01    |

| 0x2D  |                   | BASEINTERVALL          |       |                   |          |       |       | 0x0A  |         |

| 0x2E  |                   | BASEINTERVALH          |       |                   |          |       |       | 0x00  |         |

| 0x2F  |                   | BASEPOSFILTER          |       |                   |          |       | 0x14  |       |         |

| 0x30  |                   | BASENEGFILTER          |       |                   |          |       | 0x14  |       |         |

| 0x31  |                   | FILTERTYPE             |       |                   |          |       | 0x02  |       |         |

| 0x32  |                   | FILTERSTRENGTH         |       |                   |          | 0x01  |       |       |         |

| 0x33  |                   | BASEFILTERTYPE         |       |                   |          |       |       | 0x01  |         |

| 0x34  |                   | BASEFILTERSTRENGTH     |       |                   |          |       | 0x05  |       |         |

| 0x35  |                   | LARGEACTIVATIONTHRESHL |       |                   |          |       | 0x00  |       |         |

| 0x36  |                   |                        | LARG  | EACTIVA           | TIONTHR  | ESHH  |       |       | 0x00    |

| 0x37  |                   |                        | HORIZ | CONTALS           | WIPEDIST | TANCE |       |       | 0x40    |

| 0x38  |                   |                        | VER   | TICALSW           | IPEDISTA | NCE   |       |       | 0x40    |

| 0x39  |                   |                        | SM    | /IPEHOLD          | BOUNDA   | RY    |       |       | 0x19    |

| 0x3A  |                   |                        |       | TAPDIS            | TANCE    |       |       |       | 0x19    |

| 0x3B  |                   |                        | DIS   | TANCEBE           | TWEENT   | APS   |       |       | 0x40    |

| 0x3C  |                   |                        |       | TAPHOL            | DTIMEL   |       |       |       | 0x32    |

| 0x3D  |                   |                        |       | TAPHOL            | .DTIMEH  |       |       |       | 0x00    |

| 0x3E  |                   |                        | G     | ESTURE            | CLICKTIM | E     |       |       | 0x0C    |

| 0x3F  |                   |                        | S     | WIPEHO            | DTHRES   | Н     |       |       | 0x20    |

| 0x40  |                   |                        | Ν     | IINSWIPE          | VELOCIT  | Y     |       |       | 0x04    |

| 0x41  |                   |                        | HORIZ | ZONTALG           | ESTUREA  | ANGLE |       |       | 0x2D    |

| 0x42  |                   |                        | VER   | TICALGE           | STUREAN  | IGLE  |       |       | 0x2D    |

| 0x43  |                   |                        |       | I <sup>2</sup> CA | DDR      |       |       |       | 0x25    |

#### TABLE 17-5: CONFIGURATION RAM MEMORY MAP

#### 18.0 ELECTRICAL CHARACTERISTICS

#### 18.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias      | 40°C to +85°C        |

|-------------------------------------|----------------------|

| Storage temperature                 | 65°C to +150°C       |

| Voltage on pins with respect to Vss |                      |

| on VDD pin                          | 0.3V to +4.0V        |

| on all other pins                   | 0.3V to (VDD + 0.3V) |

| Maximum current                     |                      |

| out of Vss pin                      |                      |

| into Vod pin                        |                      |

| Maximum output current              |                      |

| sunk by any I/O pin                 |                      |

| sourced by any I/O pin              |                      |

|                                     |                      |

**Note:** This device is sensitive to ESD damage and must be handled appropriately. Failure to properly handle and protect the device in an application may cause partial to complete failure of the device.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

#### 18.2 Standard Operating Conditions

The standard operating conditions for any device are defined as:

| Operating Voltage:<br>Operating Temperature: | $\label{eq:VDDMAX} \begin{split} V DDMIN &\leq VDD \leq VDDMAX \\ TA\_MIN &\leq TA \leq TA\_MAX \end{split}$ |       |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|

| VDD — Operating Suppl                        | y Voltage                                                                                                    |       |

| MTCH6102                                     |                                                                                                              |       |

| VDDMIN                                       |                                                                                                              |       |

| VDDMAX                                       |                                                                                                              |       |

| TA — Operating Ambien                        | t Temperature Range                                                                                          |       |

| Industrial Tempera                           | ture                                                                                                         |       |

| TA_MIN                                       |                                                                                                              | –40°C |

| Та_мах                                       |                                                                                                              | +85°C |

# **MTCH6102**

#### 18.3 **DC Characteristics**

#### TABLE 18-1: OPERATING CONDITIONS

| Rating                                      | Min. | Тур. | Max. | Units |

|---------------------------------------------|------|------|------|-------|

| Supply Voltage                              | 1.8  | _    | 3.6  | V     |

| Supply Current (Full Active, No Frame Rate) | 0.7  | -    | 1.17 | mA    |

| Supply Current (Sleep)                      |      | <1   |      | uA    |

#### TABLE 18-2: I/O PORTS

|               | DC CI                 | HARACTERISTICS                       | Standard Operating Conditions (unless otherwise stated) |       |            |    |                                                                 |

|---------------|-----------------------|--------------------------------------|---------------------------------------------------------|-------|------------|----|-----------------------------------------------------------------|

| Param.<br>No. | Sym.                  | Characteristic Min. Typ.† Max.       |                                                         | Units | Conditions |    |                                                                 |

|               | VIL Input Low Voltage |                                      |                                                         |       |            |    |                                                                 |

|               |                       | I/O PORT:                            |                                                         |       |            |    |                                                                 |

| D030          |                       | with TTL buffer                      | _                                                       |       | 0.15 VDD   | V  | $1.8V \leq V\text{DD} \leq 4.5V$                                |

| D031          |                       | with Schmitt Trigger buffer          | —                                                       |       | 0.2 VDD    | V  | $2.0V \leq V\text{DD} \leq 5.5V$                                |

|               |                       | with I <sup>2</sup> C™ levels        | _                                                       |       | 0.3 VDD    | V  |                                                                 |

|               |                       | with SMBus levels                    | —                                                       |       | 0.8        | V  | $2.7V \leq V\text{DD} \leq 5.5V$                                |

| D032          |                       | RESET, OSC1 (RC mode)                | —                                                       |       | 0.2 VDD    | V  |                                                                 |

| D033          |                       | OSC1 (HS mode)                       | —                                                       |       | 0.3 VDD    | V  |                                                                 |

|               | VIH                   | Input High Voltage                   |                                                         |       |            |    |                                                                 |

|               |                       | I/O ports:                           |                                                         |       |            |    |                                                                 |

| D040          |                       | with TTL buffer                      | 0.25 VDD + 0.8                                          |       |            | V  | $1.8V \leq V\text{DD} \leq 4.5V$                                |

| D041          |                       | with Schmitt Trigger buffer          | 0.8 Vdd                                                 | _     | _          | V  | $2.0V \leq V\text{DD} \leq 5.5V$                                |

|               |                       | with I <sup>2</sup> C levels         | 0.7 Vdd                                                 |       |            | V  |                                                                 |

|               |                       | with SMBus levels                    | 2.1                                                     |       | _          | V  | $2.7V \le V\text{DD} \le 5.5V$                                  |

| D042          |                       | RESET                                | 0.8 Vdd                                                 |       |            | V  |                                                                 |

| D043A         |                       | OSC1 (HS mode)                       | 0.7 Vdd                                                 |       | _          | V  |                                                                 |

| D043B         |                       | OSC1 (RC mode)                       | 0.9 Vdd                                                 |       |            | V  | Note 1                                                          |

|               | lı∟                   | Input Leakage Current <sup>(2)</sup> |                                                         |       |            |    | •                                                               |

| D060          |                       | I/O ports                            | —                                                       | ± 5   | ± 125      | nA | $Vss \le VPIN \le VDD$ , Pin at high-impedance at $85^{\circ}C$ |

| D061          |                       | RESET <sup>(2)</sup>                 | _                                                       | ± 50  | ± 200      | nA | $Vss \le VPIN \le VDD at 85^{\circ}C$                           |

These parameters are characterized but not tested.

Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only t and are not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

2: The leakage current on the RESET pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

|               | DC CHARACTERISTICS     |                          |                | Standard Operating Conditions (unless otherwise stated) |      |       |                                                    |  |

|---------------|------------------------|--------------------------|----------------|---------------------------------------------------------|------|-------|----------------------------------------------------|--|

| Param.<br>No. | Sym.                   | Characteristic           | Min. Typ.†     |                                                         | Max. | Units | Conditions                                         |  |

|               | IPUR                   | Weak Pull-up Current     |                |                                                         |      |       |                                                    |  |

| D070*         |                        |                          | 25             | 100                                                     | 200  | μA    | VDD = 3.3V, VPIN = VSS                             |  |

|               | VOL Output Low Voltage |                          |                |                                                         |      |       |                                                    |  |

| D080          |                        | I/O ports                | —              | —                                                       | 0.6  | V     | IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |  |

|               | Voн                    | Output High Voltage      |                |                                                         |      |       |                                                    |  |

| D090          |                        | I/O ports                | VDD - 0.7      | —                                                       | —    | V     | IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8V   |  |

|               | Сю                     | Capacitive Loading Specs | on Output Pins |                                                         |      | •     |                                                    |  |

| D101*         |                        | All I/O pins             | _              | —                                                       | 50   | pF    |                                                    |  |

#### TABLE 18-2: I/O PORTS (CONTINUED)

\* These parameters are characterized but not tested.

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

2: The leakage current on the RESET pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

#### 18.4 AC Characteristics and Timing Parameters

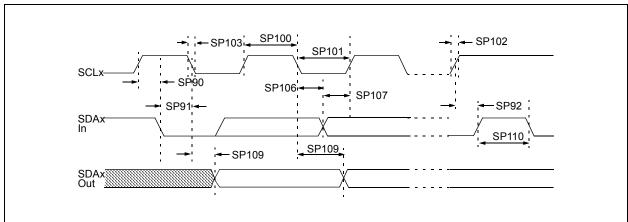

## FIGURE 18-1: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

| TABLE 18-3: I <sup>2</sup> C <sup>1</sup> | M BUS DATA REQUIREMENTS |

|-------------------------------------------|-------------------------|

|-------------------------------------------|-------------------------|

| Param.<br>No. | Symbol  | Characteristic          |              | Min.       | Max. | Units | Conditions |

|---------------|---------|-------------------------|--------------|------------|------|-------|------------|

| SP100*        | Тнідн   | Clock high time         | 400 kHz mode | 0.6        | —    | μS    |            |

|               |         |                         | SSP module   | 1.5Tcy     | —    | _     |            |

| SP101*        | TLOW    | Clock low time          | 400 kHz mode | 1.3        | —    | μS    |            |

|               |         |                         | SSP module   | 1.5Tcy     | —    | _     |            |

| SP102*        | Tr      | SDAx and SCLx rise time | 400 kHz mode | 20 + 0.1CB | 300  | ns    |            |

| SP103*        | TF      | SDAx and SCLx fall time | 400 kHz mode | 20 + 0.1Св | 250  | ns    |            |

| SP106*        | THD:DAT | Data input hold time    | 400 kHz mode | 0          | 0.9  | μS    |            |

| SP107*        | TSU:DAT | Data input setup time   | 400 kHz mode | 100        | —    | ns    |            |

| SP109*        | Таа     | Output valid from clock | 400 kHz mode | —          | —    | ns    |            |

| SP110*        | TBUF    | Bus free time           | 400 kHz mode | 1.3        | —    | μS    |            |

| SP111         | Св      | Bus capacitive loading  |              | _          | 400  | рF    |            |

\* These parameters are characterized but not tested.

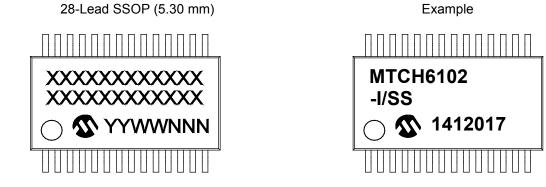

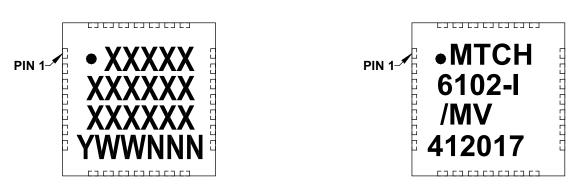

#### **19.0 ORDERING INFORMATION**

#### TABLE 19-1: ORDERING INFORMATION

| Part Number    | Pin Package               | Packing |

|----------------|---------------------------|---------|

| MTCH6102-I/SS  | 28-Lead SSOP (5.30 mm)    | Tube    |