## Si8920 Data Sheet

### Isolated Amplifier for Current Shunt Measurement

The Si8920 is a galvanically isolated analog amplifier. The low-voltage differential input is ideal for measuring voltage across a current shunt resistor or for any place where a sensor must be isolated from the control system. The output is a differential analog signal amplified by either 8.1x or 16.2x.

The very low signal delay of the Si8920 allows control systems to respond quickly to fault conditions or changes in load. Low offset and gain drift ensure that accuracy is maintained over the entire operating temperature range. Exceptionally high common-mode transient immunity means that the Si8920 delivers accurate measurements even in the presence of high-power switching as is found in motor drive systems and inverters.

The Si8920 isolated amplifier utilizes Skyworks' proprietary isolation technology. It supports up to 5.0 kVrms withstand voltage per UL1577. This technology enables higher performance, reduced variation with temperature and age, tighter part-to-part matching, and longer lifetimes compared to other isolation technologies.

Automotive Grade is available for certain part numbers. These products are built using automotive-specific flows at all steps in the manufacturing process to ensure the robustness and low defectivity required for automotive applications.

**Automotive Applications**

· Onboard chargers

· Charging pedestals

· Hybrid and EV traction inverters

### **Industrial Applications**

- Industrial and renewable energy inverters

- AC, Brushless, and DC motor controls and drives

- Variable speed motor control in consumer white goods

- Isolated switch mode and UPS power supplies

### Safety Regulatory Approvals

- · UL 1577 recognized

- Up to 5000 Vrms for 1 minute

- · CSA component notice 5A approval

- IEC 60950-1 (reinforced insulation)

- VDE certification conformity

- VDE0884 Part 10 (basic/reinforced insulation)

- · CQC certification approval

- · GB4943.1

# KEY FEATURES

- · Low voltage differential input

- ±100 mV and ±200 mV options

- Low signal delay: 0.75 μs

- · Input offset: 0.2 mV

- Gain error: <0.5%</li>

- · Excellent drift specifications

- 1 μV/°C offset drift

- 10 ppm/°C gain drift

- · Nonlinearity: 0.025% full-scale

- Low noise: 0.10 mVrms over 100 kHz bandwidth

- High common-mode transient immunity: 75 kV/µs

- · Compact packages

- 16-pin wide body SOIC

- 8-pin surface mount DIP

- -40 to 125 °C

- AEC-Q100

- · Automotive-grade OPNs available

- AIAG compliant PPAP documentation support

- IMDS and CAMDS listing support

### 1. Ordering Guide

Table 1.1. Ordering Guide for Valid OPNs

| New Ordering Part Number | Ordering Options      |                  |                 |  |  |

|--------------------------|-----------------------|------------------|-----------------|--|--|

| (OPN)                    | Specified Input Range | Isolation Rating | Package Type    |  |  |

| Si8920AC-IP              | ±100 mV               | 3.75 kVrms       | Gull-wing DIP-8 |  |  |

| Si8920BC-IP              | ±200 mV               | 3.75 kVrms       | Gull-wing DIP-8 |  |  |

| Si8920AD-IS              | ±100 mV               | 5.0 kVrms        | WB SOIC-16      |  |  |

| Si8920BD-IS              | ±200 mV               | 5.0 kVrms        | WB SOIC-16      |  |  |

| Si8920AC-IS              | ±100 mV               | 3.75 kVrms       | WB SOIC-16      |  |  |

| Si8920BC-IS              | ±200 mV               | 3.75 kVrms       | WB SOIC-16      |  |  |

### Note:

- 1. All packages are RoHS-compliant.

- 2. "Si" and "SI" are used interchangeably.

### **Automotive Grade OPNs**

Automotive-grade devices are built using automotive-specific flows at all steps in the manufacturing process to ensure robustness and low defectivity. These devices are supported with AIAG-compliant Production Part Approval Process (PPAP) documentation, and feature International Material Data System (IMDS) and China Automotive Material Data System (CAMDS) listing. Qualifications are compliant with AEC-Q100, and a zero-defect methodology is maintained throughout definition, design, evaluation, qualification, and mass production steps.

Table 1.2. Ordering Guide for Automotive Grade OPNs 1, 2, 4, 5

| New Ordering Part Number | Ordering Options      |                  |                 |  |  |

|--------------------------|-----------------------|------------------|-----------------|--|--|

| (OPN)                    | Specified Input Range | Isolation Rating | Package Type    |  |  |

| Si8920AC-AP              | ±100 mV               | 3.75 kVrms       | Gull-wing DIP-8 |  |  |

| Si8920BC-AP              | ±200 mV               | 3.75 kVrms       | Gull-wing DIP-8 |  |  |

- 1. All packages are RoHS-compliant.

- 2. "Si" and "SI" are used interchangeably.

- 3. An "R" at the end of the part number denotes tape and reel packaging option.

- 4. Automotive-Grade devices (with an "-A" suffix) are identical in construction materials, topside marking, and electrical parameters to their Industrial-Grade (with a "-I" suffix) version counterparts. Automotive-Grade products are produced utilizing full automotive process flows and additional statistical process controls throughout the manufacturing flow. The Automotive-Grade part number is included on shipping labels.

- 5. Additional Ordering Part Numbers may be available in Automotive-Grade. Please contact your local Skyworks sales representative for further information.

- 6. In Section 6.5 Top Marking: DIP8 and Section 6.6 Top Marking: 16-Pin Wide Body SOIC, the Manufacturing Code represented by either "RTTTTT" or "TTTTTT" contains as its first character a letter in the range N through Z to indicate Automotive-Grade."

# **Table of Contents**

| 1. | Ordering Guide                             | . 2  |

|----|--------------------------------------------|------|

| 2. | System Overview                            | . 4  |

| 3. | Current Sense Application                  | . 5  |

| 4. | Electrical Specifications                  | . 6  |

|    | 4.1 Typical Operating Characteristics      | . 11 |

|    | 4.2 Regulatory Information                 | .13  |

| 5. | Pin Descriptions                           | 15   |

| 6. | Packaging                                  | 16   |

|    | 6.1 Package Outline: DIP8                  | .16  |

|    | 6.2 Land Pattern: DIP8                     | .17  |

|    | 6.3 Package Outline: 16-Pin Wide Body SOIC | .18  |

|    | 6.4 Land Pattern: 16-Pin Wide Body SOIC    | .20  |

|    | 6.5 Top Marking: DIP8                      | .21  |

|    | 6.6 Top Marking: 16-Pin Wide Body SOIC     | .22  |

| 7  | Revision History                           | 23   |

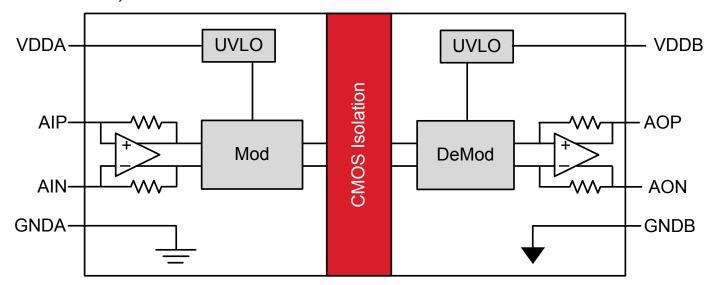

### 2. System Overview

The input to the Si8920 is designed for low-voltage, differential signals. This is ideal for connection to low resistance current shunt measurement resistors. The Si8920A has a full scale input range of  $\pm 100$  mV, and the Si8920B has a full scale input range of  $\pm 200$  mV. In both cases, the internal gain is set so that the full scale output is 1.6 V.

The Si8920 modulates the analog signal in a unique way for transmission across the semiconductor based isolation barrier. The input signal is first converted to a pulse-width modulated digital signal. For transmission across the isolation barrier, the signal is further modulated with a high frequency carrier. On the other side of the isolation barrier, the signal is demodulated and the carrier portion is removed. The resulting PWM signal is then used to faithfully reproduce the analog signal. This solution provides exceptional signal bandwidth and accuracy.

Figure 2.1. Functional Block Diagram

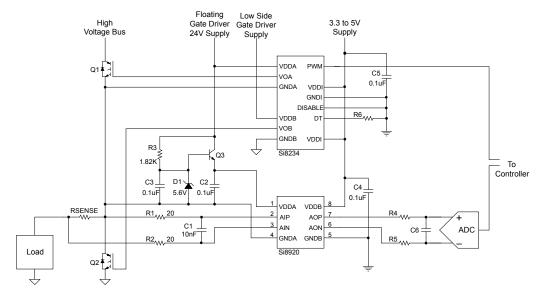

### 3. Current Sense Application

In the driver circuit presented below, the Si8920 is used to amplify the voltage across the sense resistor, RSENSE, and transmit the analog signal to the low-voltage domain across an isolation barrier. Isolation is needed because the voltage of RSENSE with respect to ground will swing between 0 V and the high voltage rail connected to the drain of Q1.

Figure 3.1. Current Sense Application

The load in this application can be a motor winding or a similar inductive winding. In a three-phase motor drive application, this circuit would be repeated three times, one for each phase. RSENSE should be a small resistor value to reduce power loss. However, an excessively low resistance will reduce the signal-to-noise ratio of the measurement. Si8920 offers two specified full-scale input options, ±100 mV (Si8920A) and ±200 mV (Si8920B), for optimizing the value of RSENSE.

AIP and AIN connections to the RSENSE resistor should be made as close as possible to each end of the RSENSE resistor as trace resistance will add error to the measurement. The input to the Si8920 is differential, and the PCB traces back to the input pins should run in parallel. This ensures that any large noise transients that occur on the high-voltage side are coupled equally to the AIP and AIN pins and will be rejected by the Si8920 as a common-mode signal.

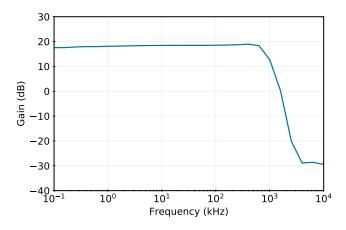

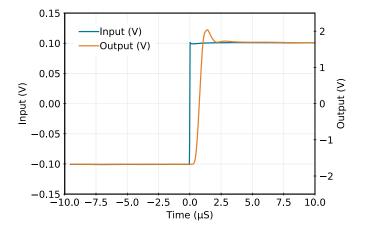

The amplifier bandwidth of the Si8920 is approximately 950 kHz. If further input filtering is required, a passive, differential RC low-pass filter can be placed between RSENSE and the input pins. Values of R1 = R2 = 20  $\Omega$  and C1 = 10 nF, as shown in Figure 4.8 Step Response Low to High on page 11, provides a cutoff at approximately 400 kHz. For the lowest gain error, R1 and R2 should always be less than 33  $\Omega$  to keep the source impedance sufficiently low compared to the Si8920 input impedance.

The common-mode voltage of AIN and AIP must be greater than -0.2 V but less than 1 V with respect to GNDA. To meet this requirement, connect GNDA of the Si8920 to one side of the RSENSE resistor. In this example, GNDA, RSENSE, the source of Q1, and the drain of Q2 are connected. The ground of the gate driver (Skyworks' Si8234 in this circuit) is also commonly connected to the same node.

The Q1 gate driver has a floating supply, 24 V in this example. Since the input and output of the Si8920 are galvanically isolated from each other, separate power supplies are necessary on each side. Q3, R3, C3, and D1 make a regulator circuit for powering the input side of the Si8920 from this floating supply. D1 establishes a voltage of 5.6 V at the base of Q3. R3 is selected to provide a Zener current of 10 mA for D1. C3 provides filtering at the base of Q3, and the emitter output of Q3 provides approximately 5 V to VDDA. C2 is a bypass capacitor for the supply and should be placed at the VDDA pin with its return trace connecting to the GNDA connection at RSENSE.

C4, the local bypass capacitor for the B-side of Si8920, should be placed closed to VDDB supply pin with its return close to GNDB. The output signal at AOP and AON is differential with a nominal gain of 8.1 (Si8920B) or 16.2 (Si8920A) and common mode of 1.1 V. The outputs are sampled by a differential input ADC. Depending on the sample rate of the ADC, an anti-aliasing filter may be required. A simple anti-aliasing filter can be made from the passive components, R4, C6, and R5. The characteristics of this filter are dictated by the input topology and sampling frequency of the ADC. However, to ensure the Si8920 outputs are not overloaded, R4 = R5 > 5 k $\Omega$  and C6 can be calculated by the following equation:

$$C6 = \frac{1}{2 \times \pi \times (R4 + R5) \times f_{3dB}}$$

### 4. Electrical Specifications

**Table 4.1. Electrical Specifications**

$V_{DDA}$ ,  $V_{DDB}$  = 5 V,  $T_{A}$  = -40 to +125 °C; typical specs at 25 °C

| Paran                      | neter           | Symbol             | Test Condition         | Min  | Тур   | Max  | Units  |

|----------------------------|-----------------|--------------------|------------------------|------|-------|------|--------|

| Input Side Supply Voltage  |                 | VDDA               |                        | 3.0  |       | 5.5  | V      |

| Input Supply Current       |                 | IVDDA              | VDDA = VDDB = 3.3 V    | 3.2  | 4.2   | 5.5  | mA     |

| Output Side S              | upply Voltage   | VDDB               |                        | 3.0  |       | 5.5  | V      |

| Output Sup                 | ply Current     | IVDDB              | VDDA = VDDB = 3.3 V    | 2.7  | 3.8   | 4.9  | mA     |

| VDD Undervolt              | age Threshold   | VDDUV+             | VDDA, VDDB rising      |      | 2.7   |      | V      |

| VDD Undervolt              | age Threshold   | VDDUV-             | VDDA, VDDB falling     |      | 2.6   |      | V      |

| VDD Undervolta             | age Hysteresis  | VDD <sub>HYS</sub> |                        |      | 100   |      | mV     |

| Amplifier E                | Bandwidth       |                    |                        |      | 950   |      | kHz    |

| Amplifier Input            |                 |                    |                        | 1    |       |      |        |

| Specified Full-            | Si8920A         |                    |                        | -100 |       | 100  | mV     |

| Scale Input Am-<br>plitude | Si8920B         | VAIP – VAIN        |                        | -200 |       | 200  | mV     |

| Maximum Input              | Si8920A         |                    |                        |      | ±125  |      | mV     |

| Voltage Before<br>Clipping | Si8920B         | VAIP – VAIN        |                        |      | ±250  |      | mV     |

| Common-Mode C              | Operating Range | VCM                |                        | -0.2 |       | 1    | V      |

| Input Refer                | red Offset      | VOS                |                        |      | 0.2   | 1.0  | mV     |

| Input Off                  | set Drift       | VOS <sub>T</sub>   |                        |      | 1.0   |      | μV/°C  |

| Differential Input         | Si8920A         | DIN                |                        |      | 20    |      | kΩ     |

| impedance                  | Si8920B         | RIN                |                        |      | 37.2  |      | kΩ     |

| Differential Input         | Impedance Drift | RIN <sub>T</sub>   |                        |      | 850   |      | ppm/°C |

| Amplifier Output           |                 |                    |                        | I    | 1     | l    |        |

| Full-scale                 | e Output        | VAOP – VAON        |                        | 1.58 | 1.62  | 1.65 | Vpk    |

| Onin                       | Si8920A         |                    |                        |      | 16.2  |      |        |

| Gain                       | Si8920B         |                    |                        |      | 8.1   |      |        |

| Gain                       | Error           |                    | T <sub>A</sub> = 25 °C | -0.5 |       | 0.5  | %      |

| Gain Eri                   | ror Drift       |                    |                        |      | 10    |      | ppm/°C |

| Output Commor              | n Mode Voltage  | (VAOP + VAON)/2    |                        | 1.02 | 1.1   | 1.17 | V      |

| Output Naise               | Si8920A         |                    | 100 kHz bandwidth      |      | 0.14  | 0.28 | mVrms  |

| Output Noise               | Si8920B         |                    | 100 kHz bandwidth      |      | 0.10  | 0.20 | mVrms  |

| Nonlinearity               | Si8920A         |                    |                        |      | 0.04  | 0.15 | %      |

| Nonlinearity               | Si8920B         |                    |                        |      | 0.025 | 0.1  | %      |

| Output Res                 | istive Load     | RLOAD              |                        | 5    |       |      | kΩ     |

| Output Capa                | acitive Load    | CLOAD              |                        |      |       | 100  | pF     |

| Parameter                                      | Symbol          | Test Condition                    | Min | Тур  | Max | Units |

|------------------------------------------------|-----------------|-----------------------------------|-----|------|-----|-------|

| Timing                                         |                 |                                   |     |      |     |       |

| Signal Delay                                   | t <sub>PD</sub> | 50% to 50%                        |     | 0.75 |     |       |

|                                                |                 | 50% to 99%                        |     | 1.85 |     | μs    |

| Rise Time                                      | t <sub>R</sub>  | 10% to 90%                        |     | 0.42 |     | μs    |

| Common-Mode Transient<br>Immunity <sup>1</sup> | CMTI            | AIP = AIN = AGND,<br>VCM = 1500 V | 50  | 75   |     | kV/μs |

1. An analog CMTI failure is defined as an output error of more than 100 mV persisting for at least 1  $\mu$ s.

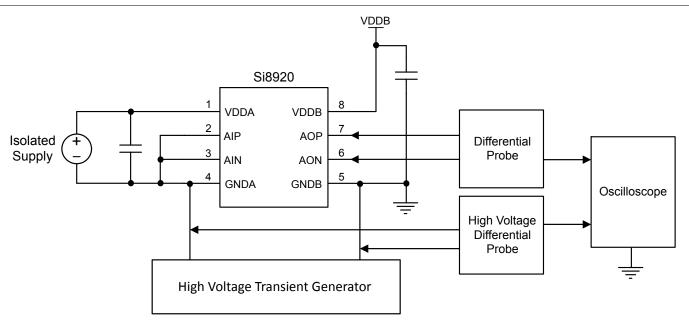

Figure 4.1. Common-Mode Transient Immunity Characterization Circuit

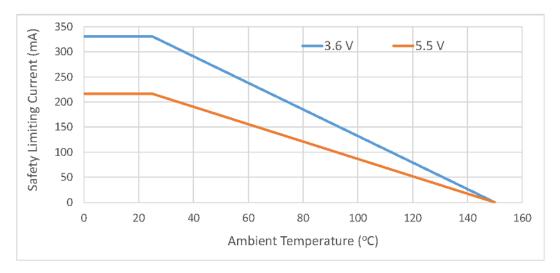

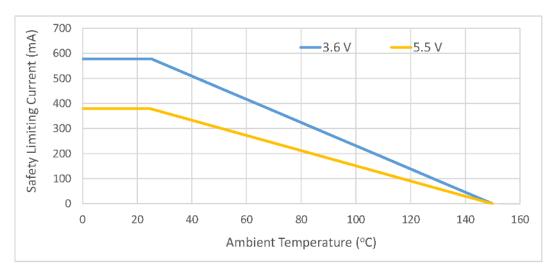

Table 4.2. IEC Safety Limiting Values<sup>1</sup>

| Parameter                         | Symbol         | Test Condition             | Characteristic | Unit |

|-----------------------------------|----------------|----------------------------|----------------|------|

| Safety Temperature                | T <sub>S</sub> |                            | 150            | °C   |

|                                   |                | θ <sub>JA</sub> = 105 °C/W |                |      |

|                                   |                | VDD = 5.5 V                | 040            |      |

|                                   |                | T <sub>J</sub> = 150 °C    | 216            | mA   |

| Safety Input Current (DIP-8)      |                | T <sub>A</sub> = 25 °C     |                |      |

|                                   | Is             | θ <sub>JA</sub> = 105 °C/W |                |      |

|                                   |                | VDD = 3.6 V                |                | _    |

|                                   |                | T <sub>J</sub> = 150 °C    | 331            | mA   |

|                                   |                | T <sub>A</sub> = 25 °C     |                |      |

|                                   |                | θ <sub>JA</sub> = 60 °C/W  |                |      |

|                                   |                | VDD = 5.5 V                |                |      |

|                                   |                | T <sub>J</sub> = 150 °C    | 379            | mA   |

|                                   |                | T <sub>A</sub> = 25 °C     |                |      |

| Safety Input Current (WB SOIC-16) | I <sub>S</sub> | θ <sub>JA</sub> = 60 °C/W  |                |      |

|                                   |                | VDD = 3.6 V                |                |      |

|                                   |                | T <sub>J</sub> = 150 °C    | 579            | mA   |

|                                   |                | T <sub>A</sub> = 25 °C     |                |      |

|                                   |                | θ <sub>JA</sub> = 105 °C/W |                |      |

| Safety Input Power (DIP-8)        | Ps             | T <sub>J</sub> = 150 °C    | 1191           | mW   |

|                                   |                | T <sub>A</sub> = 25 °C     |                |      |

|                                   |                | θ <sub>JA</sub> = 60 °C/W  |                |      |

| Safety Input Power (WB SOIC-16)   | Ps             | T <sub>J</sub> = 150 °C    | 2083           | mW   |

|                                   |                | T <sub>A</sub> = 25 °C     |                |      |

|                                   |                | PDIP-8                     | 1.19           | W    |

| Device Power Dissipation          | P <sub>D</sub> | WB SOIC-16                 | 2.08           | W    |

**Table 4.3. Thermal Characteristics**

| Parameter                             | Symbol        | PDIP-8 | WB SOIC-16 | Unit |

|---------------------------------------|---------------|--------|------------|------|

| IC Junction-to-Air Thermal Resistance | $\theta_{JA}$ | 105    | 60         | °C   |

<sup>1.</sup> Maximum value allowed in the event of a failure. Refer to the thermal derating curves below.

Figure 4.2. Thermal Derating Curve for Safety Limiting Current (DIP8)

Figure 4.3. Thermal Derating Curve for Safety Limiting Current (WB SOIC-16)

Table 4.4. Absolute Maximum Ratings<sup>1</sup>

| Parameter                                      | Symbol           | Min  | Max        | Unit             |

|------------------------------------------------|------------------|------|------------|------------------|

| Storage Temperature                            | T <sub>STG</sub> | -65  | 150        | °C               |

| Ambient Temperature Under Bias                 | T <sub>A</sub>   | -40  | 125        | °C               |

| Junction Temperature                           | T <sub>J</sub>   | _    | 150        | °C               |

| Supply Voltage                                 | VDDA, VDDB       | -0.5 | 6.0        | V                |

| Input Voltage respect to GNDA                  | VAIP, VAIN       | -0.5 | VDDx + 0.5 | V                |

| Output Sink or Source Current                  | ΙΙοΙ             | _    | 5          | mA               |

| Total Power Dissipation                        | P <sub>T</sub>   | _    | 212        | mW               |

| Lead Solder Termperature (10 s)                |                  | _    | 260        | °C               |

| Human Body Model ESD Rating                    |                  | 4000 | _          | V                |

| Capacitive Discharge Model ESD Rating PDIP     |                  | 2000 | _          | V                |

| Capacitive Discharge Model ESD Rating SOIC     |                  | 2000 | _          | V                |

| Maximum Isolation (Input to Output) (1 s) PDIP |                  | _    | 6500       | V <sub>RMS</sub> |

| Maximum Isolation (Input to Output) (1 s) SOIC |                  | _    | 6500       | V <sub>RMS</sub> |

<sup>1.</sup> Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to conditions as specified in the operational sections of the data sheet.

### 4.1 Typical Operating Characteristics

Figure 4.4. Amplifier Bandwidth

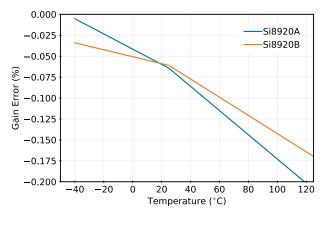

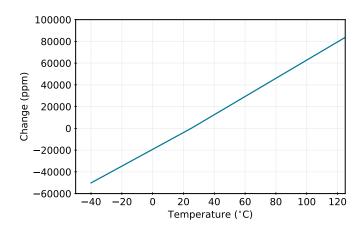

Figure 4.5. Gain Error vs. Temperature

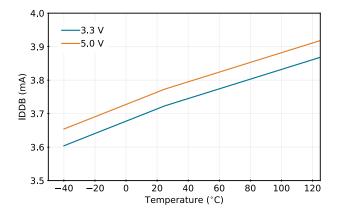

Figure 4.6. IDDB vs. Temperature

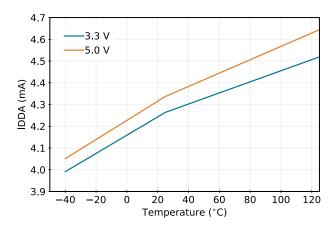

Figure 4.7. IDDA vs. Temperature

Figure 4.8. Step Response Low to High

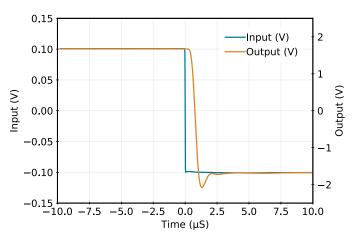

Figure 4.9. Step Response High to Low

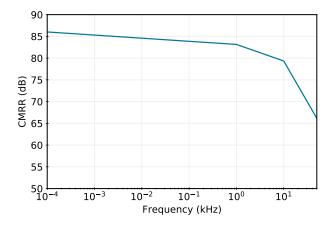

Figure 4.10. CMRR vs. Frequency

Figure 4.11. Normalized Differential Input Resistance vs. Temperature

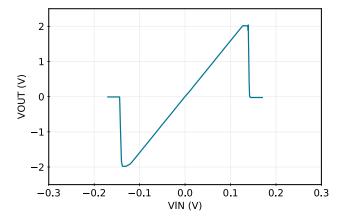

Figure 4.12. Si8920A Typical  $V_{OUT}$  vs.  $V_{IN}$

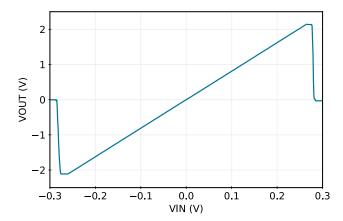

Figure 4.13. Si8920B Typical V<sub>OUT</sub> vs. V<sub>IN</sub>

### 4.2 Regulatory Information

### Table 4.5. Regulatory Information<sup>1, 2</sup>

### CSA

The Si8920 is certified under CSA Component Acceptance Notice 5A. For more details, see File 232873.

60950-1: Up to 600  $V_{RMS}$  reinforced insulation working voltage; up to 1000  $V_{RMS}$  basic insulation working voltage.

### **VDE**

The Si8920 is certified according to VDE 0884-10. For more details, see File 5006301-4880-0001.

VDE 0884-10: Up to 1200 V<sub>peak</sub> for reinforced insulation working voltage.

### UL

The Si8920 is certified under UL1577 component recognition program. For more details, see File E257455.

Rated up to 5000 V<sub>RMS</sub> isolation voltage for basic protection.

### CQC

The Si8920 is certified under GB4943.1-2011.

Rated up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

### Note:

- 1. Regulatory Certifications apply to 5 kV<sub>RMS</sub> rated devices which are production tested to 6.0 kV<sub>RMS</sub> for 1 sec.

- 2. Regulatory Certifications apply to 3.75 kV<sub>RMS</sub> rated devices which are production tested to 4.5 kV<sub>RMS</sub> for 1 sec.

Table 4.6. Insulation and Safety-Related Specifications

| Parameter                                     | Symbol          | Test Condition | Value            |                  | Unit |

|-----------------------------------------------|-----------------|----------------|------------------|------------------|------|

|                                               |                 |                | GW DIP-8         | WB SOIC-16       |      |

| Nominal Air Gap (Clearance)                   | L(IO1)          |                | 7.2              | 8.0 <sup>1</sup> | mm   |

| Nominal External Tracking (Creepage)          | L(IO2)          |                | 7.0              | 8.0 <sup>1</sup> | mm   |

| Minimum Internal Gap<br>(Internal Clearance)  |                 |                | 0.016            | 0.016            | mm   |

| Tracking Resistance<br>(Proof Tracking Index) | PTI             | IEC60112       | 600              | 600              | V    |

| Erosion Depth                                 | ED              |                | 0.031            | 0.019            | mm   |

| Resistance (Input-Output) <sup>2</sup>        | R <sub>IO</sub> |                | 10 <sup>12</sup> | 10 <sup>12</sup> | Ω    |

| Capacitance (Input-Output) <sup>2</sup>       | C <sub>IO</sub> | f = 1 MHz      | 1                | 1                | pF   |

- 1. The values in this table correspond to the nominal creepage and clearance values. VDE certifies the clearance and creepage limits as 8.5 mm minimum for the WB SOIC-16 package. UL does not impose a clearance and creepage minimum for component-level certifications. CSA certifies the clearance and creepage limits as 7.6 mm minimum for the WB SOIC-16 package.

- 2. To determine resistance and capacitance, the Si8920 is converted into a 2-terminal device. Pins 1–8 (1–4 DIP8) are shorted together to form the first terminal, and pins 9–16 (5–8 DIP8) are shorted together to form the second terminal. The parameters are then measured between these two terminals.

Table 4.7. IEC 60664-1 (VDE 0884) Ratings

| Parameter             | Test Conditions                             | Specification |            |  |

|-----------------------|---------------------------------------------|---------------|------------|--|

|                       |                                             | GW DIP-8      | WB SOIC-16 |  |

| Basic Isolation Group | Material Group                              | I             | 1          |  |

| Installation          | Rated Mains Voltages ≤ 150 V <sub>RMS</sub> | I-IV          | I-IV       |  |

| Classification        | Rated Mains Voltages ≤ 300 V <sub>RMS</sub> | I-IV          | I-IV       |  |

|                       | Rated Mains Voltages ≤ 450 V <sub>RMS</sub> | 1-111         | 1-111      |  |

|                       | Rated Mains Voltages ≤ 600 V <sub>RMS</sub> | I-III         | I-III      |  |

Table 4.8. VDE 0884-10 Insulation Characteristics<sup>1</sup>

| Parameter                                                         | Symbol            | Test Condition                                                                                               | Characteristic   |                  | Unit   |

|-------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|------------------|------------------|--------|

|                                                                   |                   |                                                                                                              | 3.75 kVrms-rated | 5.0 kVrms-rated  |        |

| Maximum Working Insulation Voltage                                | V <sub>IORM</sub> |                                                                                                              | 891              | 1200             | V peak |

| Input to Output Test Voltage                                      | $V_{PR}$          | Method b1 $(V_{IORM} \times 1.875 = V_{PR}, 100\%$ Production Test, $t_m = 1$ sec, Partial Discharge < 5 pC) | 1671             | 2250             | V peak |

| Transient Overvoltage                                             | V <sub>IOTM</sub> | t = 60 sec                                                                                                   | 6000             | 8000             | V peak |

| Pollution Degree<br>(DIN VDE 0110, Table 1)                       |                   |                                                                                                              | 2                | 2                |        |

| Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500 V | R <sub>S</sub>    |                                                                                                              | >10 <sup>9</sup> | >10 <sup>9</sup> | Ω      |

<sup>1.</sup> This isolator is suitable for reinforced electrical isolation only within the safety limit data. Maintenance of the safety data is ensured by protective circuits. The Si8920 provides a climate classification of 40/125/21.

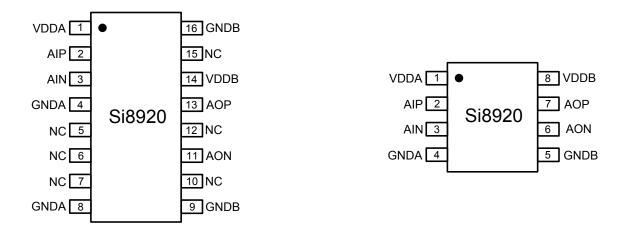

### 5. Pin Descriptions

Table 5.1. Si8920 Pin Descriptions

| Name            | WB SOIC-16<br>Pin # | GW DIP-8<br>Pin # | Description             |

|-----------------|---------------------|-------------------|-------------------------|

| VDDA            | 1                   | 1                 | Input side power supply |

| AIP             | 2                   | 2                 | Analog input high       |

| AIN             | 3                   | 3                 | Analog input low        |

| GNDA            | 4, 8                | 4                 | Input side ground       |

| GNDB            | 9, 16               | 5                 | Output side ground      |

| AON             | 11                  | 6                 | Analog output low       |

| AOP             | 13                  | 7                 | Analog output high      |

| VDDB            | 14                  | 8                 | Output power supply     |

| NC <sup>1</sup> | 5, 6, 7, 10, 12, 15 | _                 | No Connect              |

<sup>1.</sup> No Connect. These pins are not internally connected. To maximize CMTI performance, these pins should be connected to the ground plane.

### 6. Packaging

### 6.1 Package Outline: DIP8

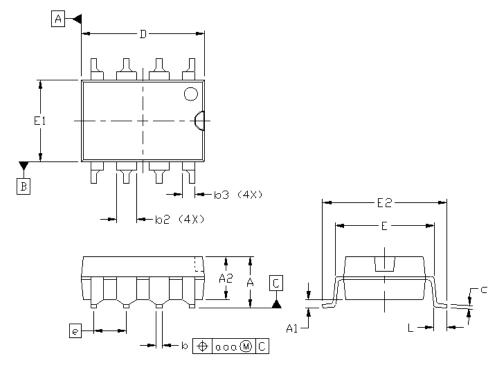

The figure below illustrates the package details for the Si8920 in a DIP8 package. The table lists the values for the dimensions shown in the illustration.

Figure 6.1. DIP8 Package

Table 6.1. DIP8 Package Diagram Dimensions

| Dimension | Min       | Max  |

|-----------|-----------|------|

| А         | _         | 4.19 |

| A1        | 0.55      | 0.75 |

| A2        | 3.17      | 3.43 |

| b         | 0.35      | 0.55 |

| b2        | 1.14      | 1.78 |

| b3        | 0.76      | 1.14 |

| С         | 0.20      | 0.33 |

| D         | 9.40      | 9.90 |

| E         | 7.37      | 7.87 |

| E1        | 6.10      | 6.60 |

| E2        | 9.40      | 9.90 |

| е         | 2.54 BSC. |      |

| L         | 0.38      | 0.89 |

| aaa       | _         | 0.25 |

| Dimension                                                               | Min | Max |

|-------------------------------------------------------------------------|-----|-----|

| Note:                                                                   |     |     |

| 1. All dimensions shown are in millimeters (mm) unless otherwise noted. |     |     |

| 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.                   |     |     |

|                                                                         |     |     |

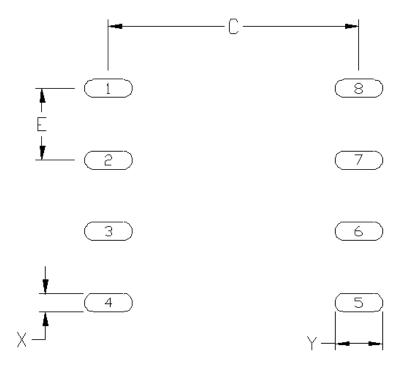

### 6.2 Land Pattern: DIP8

The figure below illustrates the recommended land pattern details for the Si8920 in a DIP8 package. The table lists the values for the dimensions shown in the illustration.

Figure 6.2. DIP8 Land Pattern

Table 6.2. DIP8 Land Pattern Dimensions<sup>1</sup>

| Dimension | Min  | Max  |

|-----------|------|------|

| С         | 8.85 | 8.90 |

| E         | 2.54 | BSC. |

| X         | 0.60 | 0.65 |

| Y         | 1.65 | 1.70 |

### Note:

1. This Land Pattern Design is based on the IPC-7351 specification.

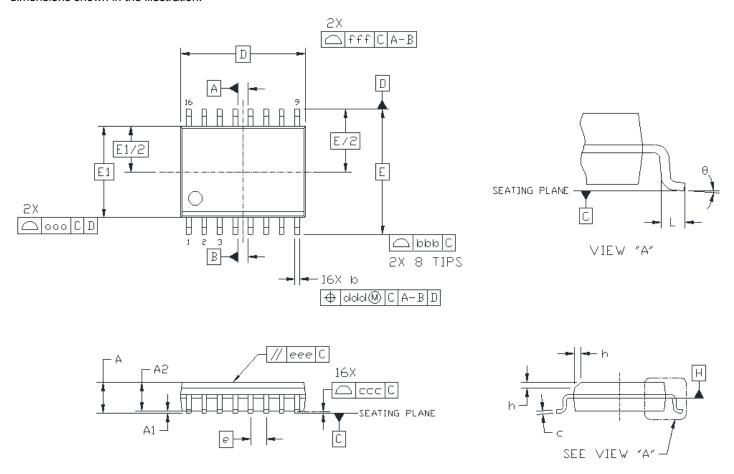

### 6.3 Package Outline: 16-Pin Wide Body SOIC

The figure below illustrates the package details for the Si8920 in a 16-Pin Wide Body SOIC package. The table lists the values for the dimensions shown in the illustration.

Figure 6.3. 16-Pin Wide Body SOIC Package

Table 6.3. 16-Pin Wide Body SOIC Package Diagram Dimensions

| Symbol | Millimeters |      |

|--------|-------------|------|

|        | Min         | Max  |

| А      | <del></del> |      |

| A1     | 0.10        | 0.30 |

| A2     | 2.05        | _    |

| b      | 0.31        | 0.51 |

| С      | 0.20        | 0.33 |

| D      | 10.30 BSC   |      |

| E      | 10.30 BSC   |      |

| E1     | 7.50 BSC    |      |

| е      | 1.27 BSC    |      |

| L      | 0.40        | 1.27 |

| h      | 0.25        | 0.75 |

| θ      | 0°          | 8°   |

| Symbol | Millimeters |      |

|--------|-------------|------|

|        | Min         | Max  |

| aaa    | _           | 0.10 |

| bbb    | _           | 0.33 |

| ccc    | _           | 0.10 |

| ddd    | _           | 0.25 |

| eee    | _           | 0.10 |

| fff    | _           | 0.20 |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC Outline MS-013, Variation AA.

- 4. Recommended reflow profile per JEDEC J-STD-020C specification for small body, lead-free components.

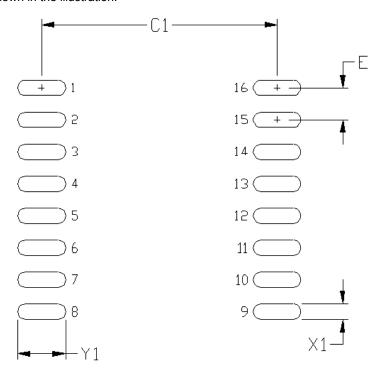

### 6.4 Land Pattern: 16-Pin Wide Body SOIC

The figure below illustrates the recommended land pattern details for the Si8920 in a 16-Pin Wide Body SOIC package. The table lists the values for the dimensions shown in the illustration.

Figure 6.4. 16-Pin Wide Body SOIC Land Pattern

Table 6.4. 16-Pin Wide Body SOIC Land Pattern Dimensions<sup>1</sup>

| Dimension | Feature            | (mm) |

|-----------|--------------------|------|

| C1        | Pad Column Spacing | 9.40 |

| E         | Pad Row Pitch      | 1.27 |

| X1        | Pad Width          | 0.60 |

| Y1        | Pad Length         | 1.90 |

- 1. This Land Pattern Design is based on IPC-7351 pattern SOIC127P1032X265-16AN for Density Level B (Median Land Protrusion).

- 2. All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.

### 6.5 Top Marking: DIP8

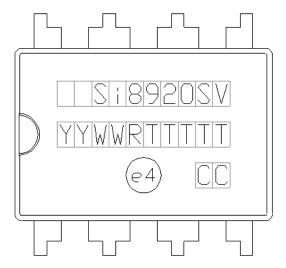

The figure below illustrates the top markings for the Si8920 in a DIP8 package. The table explains the top marks shown in the illustration.

Figure 6.5. Si8920 DIP8 Top Marking

Table 6.5. DIP8 Top Marking Explanation

| Line 1 Marking: | Customer Part Number      | Si8920 = Isolator Amplifier Series                          |

|-----------------|---------------------------|-------------------------------------------------------------|

|                 |                           | S = Input Range:                                            |

|                 |                           | • A = ±100 mV                                               |

|                 |                           | • B = ±200 mV                                               |

|                 |                           | V = Insulation rating:                                      |

|                 |                           | • C = 3.75 kV                                               |

|                 |                           | • D = 5.0 kV                                                |

| Line 2 Marking: | YY = Year                 | Assigned by the Assembly House. Corresponds to the year and |

|                 | WW = Work Week            | work week of the mold date.                                 |

|                 | RTTTTT = Mfg Code         | Manufacturing Code from the Assembly Purchase Order form.   |

|                 |                           | "R" indicates revision.                                     |

| Line 3 Marking: | Circle = 51 mils Diameter | "e4" Pb-Free Symbol                                         |

|                 | Center-Justified          |                                                             |

|                 | Country of Origin         | СС                                                          |

|                 | (Iso-Code Abbreviation)   |                                                             |

### 6.6 Top Marking: 16-Pin Wide Body SOIC

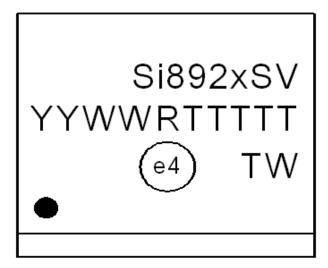

The figure below illustrates the top markings for the Si8920 in a 16-Pin Wide Body SOIC package. The table explains the top marks shown in the illustration.

Figure 6.6. Si8920 16-Pin Wide Body SOIC Top Marking

Table 6.6. 16-Pin Wide Body SOIC Top Mark Explanation

| Line 1 Marking: | Customer Part Number      | Si8920 = Isolator Amplifier Series                                                |  |

|-----------------|---------------------------|-----------------------------------------------------------------------------------|--|

|                 |                           | S = Input Range:                                                                  |  |

|                 |                           | • A = ±100 mV                                                                     |  |

|                 |                           | • B = ±200 mV                                                                     |  |

|                 |                           | V = Insulation rating:                                                            |  |

|                 |                           | • C = 3.75 kV                                                                     |  |

|                 |                           | • D = 5.0 kV                                                                      |  |

| Line 2 Marking: | YY = Year                 | Assigned by the Assembly House. Corresponds to the year and work week of the mold |  |

|                 | WW = Work Week            | date.                                                                             |  |

|                 | RTTTTT = Mfg Code         | Manufacturing Code from the Assembly Purchase Order form.                         |  |

|                 |                           | "R" indicates revision.                                                           |  |

| Line 3 Marking: | Circle = 43 mils Diameter | "e4" Pb-Free Symbol                                                               |  |

|                 | Left-Justified            |                                                                                   |  |

### 7. Revision History

### **Revision A**

July 2022

· Added Agile data sheet revision in footer.

### **Revision 1.04**

September 2020

• Updated the Ordering Guide with an Automotive-Grade OPN option

### Revision 1.03

January 2019

· Added new OPNs for 3.75kVrms in WB SOIC-16 package

### Revision 1.02

May 2018

· Updated the Ordering Guide for Automotive-Grade OPN option

### **Revision 1.01**

**April 2018**

· Added an Ordering Guide for Automotive-Grade OPN option

### **Revision 1.0**

- · Updated linearity, offset, gain drift, and IVVDB specifications.

- · Added typical Vout vs. Vin charts.

- Added Table 4.2 IEC Safety Limiting Values<sup>1</sup> on page 8, Table 4.3 Thermal Characteristics on page 8, and thermal derating curves.

### Revision 0.8

• Corrected the C6 equation in 3. Current Sense Application.

### Revision 0.7

• Updated Figure 6.1 DIP8 Package on page 16.

skyworksinc.com

skyworksinc.com/quality

Support & Resources skyworksinc.com/support

### Copyright © 2022 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters.

Skyworks, the Skyworks symbol, Sky5®, SkyOne®, SkyBlue™, Skyworks Green™, ClockBuilder®, DSPLL®, ISOmodem®, ProSLIC®, and SiPHY® are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.