LX24232

### **32 CHANNEL LED BACKLIGHT CONTROLLER**

### DATASHEET

### **KEY FEATURES**

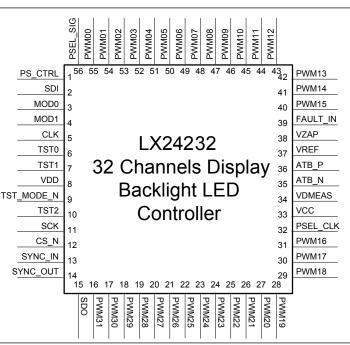

DESCRIPTION LX24232 is a 32 channel display backlight LED controller. The device is part of a chipset consisting of 32 independent PWM output channels with LX24232 and LX23108 - an 8 channel LED driver. independent 12-bit resolution duty-cycle (PWM high-Each LX24232 controller is capable of controlling up to time) control for each channel. 32 LED channels, by controlling up to 4 LX23108 LED Independent 12-bit phase delay (PD) control for each • drivers. Each LX23108 8-channel LED driver contains PWM output channel, optimized for 3D applications. eight FETs driving and controls up to 4x8 LED channels, where each channel is capable of driving a current of up to 32 independent, frame-by-frame controlled, Duty-200mA. Cycle data (DTC) LX24232 has 32 independent, frame-by-frame 32 independent, frame-by-frame controlled, Phase • controlled PWM output channels; each output channel Delay data (PD) supports independent duty-cycle and phase delay control. LX24232 uses  $V_{sync}$  input for flexible synchronization Duty-cycle & Phase Delay can be updated multiple schemes, including synchronization to either rising or times per frame falling edges, optimal V<sub>svnc</sub> jitter support, as well as single Single or multiple PWM cycles in a single frame or multiple PWM cycles per frame support, and loss of support. V<sub>svnc</sub> support. LX24232 consists of an on-chip internal power supply Frame-by-frame or multiple times per frame data rate • control circuitry that can be used to adjust voltage level of through high-speed SPI interface an external LED power source. This is done by regulating V<sub>sync</sub> synchronization. LED supply voltage to optimum level, and thus minimizing system power loss. At the same time, accurate current Configurable PWM output synchronization to either regulation for each of the 32 LED strings is maintained. rising or falling edge of external sync pulse. LX24232 includes an on-chip analog to digital converter Advanced V<sub>sync</sub> jitter support for drain voltage (VD) measurements, for power supply control, fault detection and protection. aunnart

|                                                      | Channel Display Backlight LED Controller                                                                                      | <ul> <li>Loss of V<sub>sync</sub> support</li> </ul>                                                        |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                      | hrough SPI interface which speeds up                                                                                          | Optimized LED power supply voltage control.                                                                 |  |  |  |

| communication<br>between LX24                        | and reduces the number of control signals<br>232 and host system (FPGA, Video                                                 | <ul> <li>On-chip power supply trimming DAC for enhanced power supply control.</li> </ul>                    |  |  |  |

| Processor, and<br>LX24232 sup                        | ports a daisy chain connection in case                                                                                        | <ul> <li>±1.5% precision current matching.</li> </ul>                                                       |  |  |  |

| more than 32 ch<br>LX24232 32-0                      | annels are required.<br>Channel Display Backlight LED Controller                                                              | 8-bit resolution current setting.                                                                           |  |  |  |

|                                                      | e types of system faults on each of its 32                                                                                    | <ul> <li>Internal A/D for drain voltage measurements.</li> </ul>                                            |  |  |  |

|                                                      | temperature, open LEDs and short LEDs).<br>aults, unit takes the required measures to                                         | <ul> <li>Automatic minimum FET Vd report.</li> </ul>                                                        |  |  |  |

| protect system.<br>LX24232 is o                      | capable of controlling up to 8 LX23108                                                                                        | <ul> <li>Open string, short LED and over-temperature<br/>protection for each individual channel.</li> </ul> |  |  |  |

| channels are c                                       | cial configuration, where two consecutive<br>onnected together for increased current<br>re details refer to application note. | On-chip thermal monitoring.                                                                                 |  |  |  |

| IPORTANT: For                                        | the most current data, consult Microsemi's webs                                                                               | •                                                                                                           |  |  |  |

|                                                      |                                                                                                                               |                                                                                                             |  |  |  |

| T (00)                                               | Plastic MLPQ 8 x 8mm QFN 56 pin                                                                                               |                                                                                                             |  |  |  |

| <b>T</b> <sub>A</sub> (°C)                           | Plastic MLPQ 8 x 8mm QFN 56 pin<br>RoHS Compliant/Pb free MSL1                                                                |                                                                                                             |  |  |  |

| <b>T</b> <sub>A</sub> (° <b>C</b> )<br>-40° to +85°C |                                                                                                                               |                                                                                                             |  |  |  |

# 32 CHANNEL LED BACKLIGHT CONTROLLER

CONFIDENTIAL

LX24232

DATASHEET

### THERMAL DATA (POWER CONSUMPTION)

21°C/W, according to JESD51-7.

Thermal resistance-junction to ambient

Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{iA})$ .

### ABSOLUTE MAXIMUM RATINGS

| Supply Input Voltage ( $V_{CC}$ , $V_{DD}$ )                             | -0.5V $_{\text{DC}}$ to 4.5V $_{\text{DC}}$ |

|--------------------------------------------------------------------------|---------------------------------------------|

| All other pins                                                           | -0.5V_{DC} toV_{CC}+0.3 up to $4.5V_{DC}$   |

| Operating Ambient Temperature Range                                      | -40°C to +85°C                              |

| Maximum Operating Junction Temperature                                   | 150°C                                       |

| ESD Protection at all I/O pins                                           | ± 4KV HBM                                   |

| Storage Temperature Range                                                | -65°C to +150°C                             |

| Package Peak Temperature for Solder Reflow (40 seconds maximum exposure) | +260°C (+0,-5°C)                            |

Notes: Exceeding these ratings could result in damage to device. All voltages are with respect to Ground.

### APPLICABLE DOCUMENTS

- LX23108AL 8 Channel LED Drivers datasheet (32QFN 5x5)

- LX23108AH 8 Channel LED Drivers datasheet (32QFN 7x7)

- AN-182, Designing a Low Current LED Backlight Driver System, cat no. 06-0077-080

# LX24232

### 32 CHANNEL LED BACKLIGHT CONTROLLER

### DATASHEET

### TYPICAL APPLICATION INFORMATION

### **Typical Applications**

- LCD Display Back-lighting

- LED Signage

- LED Displays

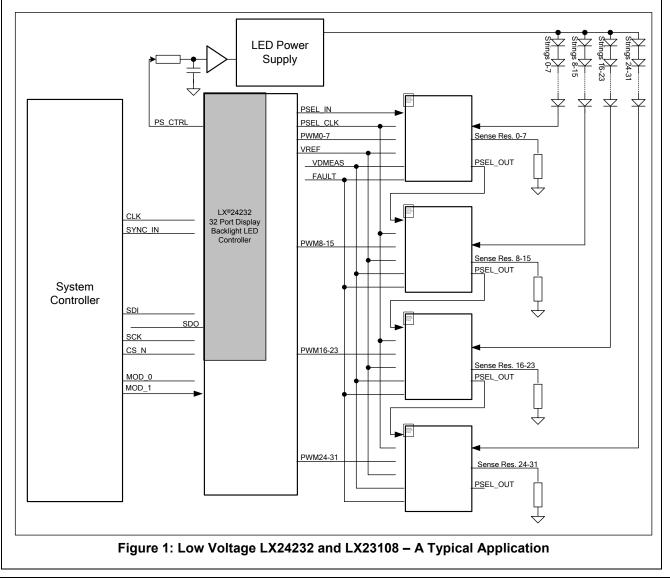

Figure 1 illustrates a typical application where a System Controller communicates with a LX24232 32 Channel Display Backlight LED Controller through an SPI bus. LX24232 is connected to four LX23108 arrays supporting a total of 32 LED strings. Each LX23108 transmits current very accurately and can drive eight LED strings. Output currents' value is set by the LX24232 which produces a precise and stable voltage,  $V_{REF}$ .

All four LX23108 components are cascaded, allowing LX24232 LED controller to sequentially select all 32 channels for monitoring, searching for  $VD_{MIN}$  and optimally adjusting power supply voltage through PDM control. Channel dimming is individually adjusted by 32 PWM output pins; 8 input channels per single LX23108 component. Currents are scaled by the external sense resistors.

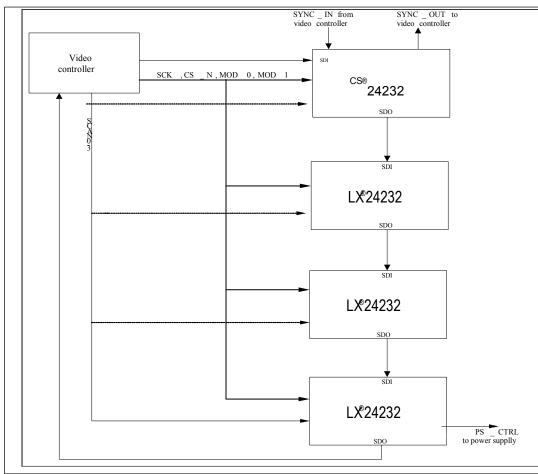

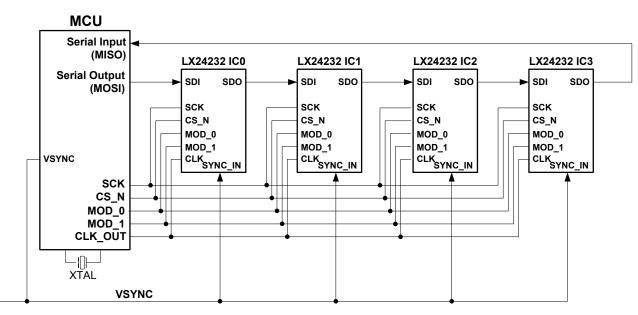

Figure 2 shows a multiple connection of several LX24232 controllers, supporting 32x4 LED strings.

32 CHANNEL LED BACKLIGHT CONTROLLER

Figure 2: Typical Application with Four LED Controllers

32 CHANNEL LED BACKLIGHT CONTROLLER

DATASHEET

### **Electrical Characteristics**

Unless otherwise specified, the following specifications apply to the operating ambient temperature, -40° to +85° C, and the following test conditions:  $V_{DD} = V_{CC} = 3.3$  VDC.

Performance must be guaranteed for  $0^{\circ}C \leq T_{J} \leq +110^{\circ}C$ .

| PARAMETER                                | SYMBOL                            | TEST CONDITIONS /                                       |      | LX24232 LED<br>CONTROLLER |        | UNITS           |

|------------------------------------------|-----------------------------------|---------------------------------------------------------|------|---------------------------|--------|-----------------|

|                                          |                                   | COMMENT                                                 | MIN. | TYP.                      | MAX.   |                 |

| POWER SUPPLY                             |                                   |                                                         |      |                           |        |                 |

| Input voltage                            | V <sub>DD</sub> , V <sub>CC</sub> | *Note 1                                                 | 3.0  | 3.3                       | 3.6    | VDC             |

| Operating current                        | I <sub>DD</sub>                   | From V <sub>DD</sub> power supply                       |      | 3                         | 5      | mA              |

|                                          | I <sub>CC</sub>                   | From V <sub>CC</sub> power supply                       |      | 3.5                       | 5      | mA              |

| DIGITAL INTERFACE                        |                                   |                                                         |      |                           |        |                 |

| Input logic high threshold               | V <sub>IH</sub>                   |                                                         | 2.2  |                           |        | VDC             |

| Input logic low threshold                | V <sub>IL</sub>                   |                                                         |      |                           | 0.8    | VDC             |

| Output high voltage                      | V <sub>он</sub>                   | I <sub>ОН</sub> = -1mA                                  | 2.4  |                           |        | VDC             |

| Output low voltage                       | V <sub>OL</sub>                   | I <sub>OH</sub> = 1mA                                   |      |                           | 0.4    | VDC             |

| SCK clock frequency                      | F <sub>sck</sub>                  |                                                         |      |                           | 32     | MHz             |

| CLK frequency                            | F <sub>clk</sub>                  | Duty Cycle 40% - 60%                                    | 3.5  |                           | 8.192  | MHz             |

| SYNC_IN pulse width                      | sync_in_pulse                     |                                                         | 3    |                           |        | Clocks          |

| SYNC_OUT pulse width                     | sync_out_pulse                    | T <sub>SYNC_OUT</sub> [CLK] =<br>320*(PWM_FRDIV+1)      |      | 320                       |        | Clocks          |

|                                          | LED                               | CURRENT CONTROL                                         |      |                           |        |                 |

| DAC resolution                           | V <sub>ref_err</sub>              |                                                         |      | 8                         |        | bits            |

| V <sub>REF</sub> output accuracy error   |                                   | $1.25 V_{DC} < V_{REF} \le 2.5 V_{DC}$                  |      |                           | ± 1.43 | %               |

|                                          |                                   | $0.5 \text{ VDC} < V_{\text{REF}} < 1.25 V_{\text{DC}}$ |      |                           | ± 2    | %               |

|                                          | V <sub>ref</sub>                  | $0.234 V_{DC} < V_{REF} < 0.5 V_{DC}$                   |      |                           | ± 5.26 | %               |

| V <sub>REF</sub> output range            |                                   |                                                         |      |                           | 2.5    | V <sub>DC</sub> |

| Note 1: During power up, V <sub>DI</sub> | should not preced                 | e V <sub>CC</sub> .                                     | 1    | •                         | •      |                 |

| ADC                                      |                                   |                                                         |      |                           |        |                 |

| Resolution                               |                                   |                                                         |      | 7                         |        | bits            |

| LSB                                      |                                   |                                                         |      | 15.6                      |        | mV              |

| Offset error                             |                                   |                                                         |      | 1                         |        | LSB             |

| Reading error                            |                                   | 1 $V_{DC} \le Drain Voltage \le 2$<br>$V_{DC}$          |      |                           | ± 3    | LSB             |

| Full scale ADC input                     |                                   |                                                         |      | 2                         |        | V               |

| PWS CONTROL                              |                                   |                                                         |      |                           |        |                 |

| Duty-cycle resolution                    |                                   | At all system clock<br>frequencies (fPWM)               |      | 12                        |        | bits            |

| Phase-delay resolution                   |                                   | At all system clock<br>frequencies (fPWM)               |      | 12                        |        | bits            |

LX24232

# LX24232

32 CHANNEL LED BACKLIGHT CONTROLLER

|                     |                                     | DATASHEET                                                                 |                           |      |    |       |  |  |

|---------------------|-------------------------------------|---------------------------------------------------------------------------|---------------------------|------|----|-------|--|--|

| PARAMETER           | SYMBOL TEST CONDITIONS /<br>COMMENT |                                                                           | LX24232 LED<br>CONTROLLER |      |    | UNITS |  |  |

|                     |                                     | MIN.                                                                      | TYP.                      | MAX. |    |       |  |  |

| PWM frequency range |                                     | $F_{PWM}[Hz] = \frac{CLK[MHz] \cdot 10^{6}}{4096 \cdot (PWM\_FRDIV + 1)}$ | 50                        |      | 2K | Hz    |  |  |

| SYSTEM PARAMETERS – PROTECTIO | NS                                                                                                                                                                                                             |     |     |     |                 |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----------------|

| Short LED detection           | At $T_{AMB}$ = 25°C and $V_{CC}$ =<br>5VDC<br>Short LED detection of<br><i>LX23108</i> FET Array.<br>Detection is traced per<br>channel when LED voltage<br>is higher than "Short Drain<br>Voltage Threshold". | 6.0 | 6.4 | 6.8 | V <sub>DC</sub> |

| Over-temperature detection    | Over-temperature<br>indications per channel<br>from <i>LX23108</i> LED Driver.                                                                                                                                 | 150 | 180 | 210 | ° C             |

### **Functional Pin Description**

| NAME           | PIN #  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |

|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND           | EPAD   | Exposed PAD – Analog ground.<br>A proper ground plane should be deployed around this pin wherever possible.                                                                                                                                                                                                                                                   |

| VCC            | 33     | Supply voltage for the internal analog circuit. A low ESR bypass capacitor $(1\mu F)$ should be placed as close as possible to this pin, using low impedance traces to AGND.                                                                                                                                                                                  |

| ATB_N<br>ATB_P | 35, 36 | Internal test output pins; do not connect.                                                                                                                                                                                                                                                                                                                    |

| SDI            | 2      | Serial Data Input pin. Data from SPI Host to this pin is clocked into input shift register at the rising edge of SCK clock. MSB is input first.                                                                                                                                                                                                               |

| SDO            | 15     | Serial Data Output pin. Data from input shift register is shifted out from this pin at the falling edge of SCK clock. MSB is output first. SDO pin can be connected to SDI pin of another device to form a cascaded SPI chain. Data from LED controller can also be transmitted to System Controller from this pin. If not used, leave this pin disconnected. |

| SCK            | 11     | Clock signal for SPI operation. A single clock shifts data by one bit. It is only active when shifting data. This happens when CS_N is at 'low' level.                                                                                                                                                                                                        |

| CS_N           | 12     | Chip Select – SPI control signal input. Data shift starts when CS falls from 'high' to 'low' and data shifted into input register is latched into buffer registers at the rising edge of this signal.                                                                                                                                                         |

| SYNC_IN        | 13     | Synchronization input. If not used, connect this pin to Ground.                                                                                                                                                                                                                                                                                               |

| SYNC_OUT       | 14     | Synchronization output utilized for multi-chip applications. If unused, leave unconnected.                                                                                                                                                                                                                                                                    |

| CLK            | 5      | LX24232 system clock.                                                                                                                                                                                                                                                                                                                                         |

# LX24232

32 CHANNEL LED BACKLIGHT CONTROLLER

| NAME        | PIN #                      | DESCRIPTION                                                                                                                                                                                                                                                           |  |  |

|-------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VDD         | 8                          | Connects to Core Logic and I/O supply rail. A ceramic 1µF or greater decoupling capacitor should be connected from this pin to DGND.                                                                                                                                  |  |  |

| PWM0-31     | 55 to<br>40<br>31 to<br>16 | PWM Gate control output signals used to command up to 4 x 8-channel LX23018LILQ LED Driver ICs                                                                                                                                                                        |  |  |

| VDMEAS      | 34                         | MOSFET drain voltage sensing input. External MOSFET drain voltage is sensed via this pin and used to control external power supply, maintaining optimum voltage for LED strings.                                                                                      |  |  |

| FAULT_IN    | 39                         | A fault input signal coming from LED Driver IC. It is asserted 'low' when fault event is detected at one of the LED strings.                                                                                                                                          |  |  |

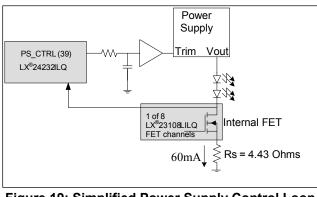

| PS_CTRL     | 1                          | Power supply control signal output. This Pulse Density Modulation signal (PDM) is used for interfacing to power supply, adjusting DC voltage of LED strings to optimum level. Should be connected to power supply control through resistor-capacitor low pass filter. |  |  |

| MOD0        | 3                          | MOD_1MOD_0TRANSACTION TYPE00Duty Cycle Packet (12-bits resolution per channel)01Phase Delay Packet (12 bits resolution per channel)10Configuration Packet                                                                                                             |  |  |

| MOD1        | 4                          | 1     0     Comparation Facket       1     1     Reserved for production                                                                                                                                                                                              |  |  |

| TST0        | 6                          | Internal test pins. Should be tied to VDD.                                                                                                                                                                                                                            |  |  |

| TST1        | 7                          | Internal test pins. Should be tied to VDD.                                                                                                                                                                                                                            |  |  |

| TEST_MODE_N | 9                          | Production test mode pin. Should be tied to VCC for normal operation.                                                                                                                                                                                                 |  |  |

| TST2        | 10                         | Internal test pins. Should be tied to VDD.                                                                                                                                                                                                                            |  |  |

| VZAP        | 38                         | Zapping input for IC production trimming; must be tied to VCC.                                                                                                                                                                                                        |  |  |

| VREF        | 37                         | Analog reference output signal used for 8-channel LED drivers.                                                                                                                                                                                                        |  |  |

| PSEL_SIG    | 56                         | Channel selection serial output signal to LX23108, which is a 32 bits packet, used for selecting (monitoring) one of the 32 strings drain voltages and thermal sensors signals.                                                                                       |  |  |

| PSEL_CLK    | 32                         | Channel selection serial clock signal. Each single clock shifts internal register data of LX23108 by one bit, allowing monitoring the next channel.                                                                                                                   |  |  |

**32 CHANNEL LED BACKLIGHT CONTROLLER**

DATASHEET

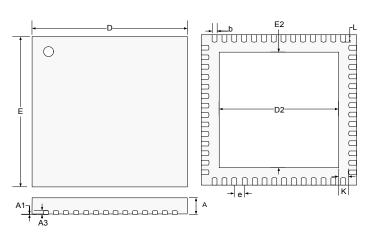

### **Package Information**

LQ

### 56-Pin 8x8mm QFN

| DIM | MILLIM   | ETERS | INCHES    |       |  |

|-----|----------|-------|-----------|-------|--|

| DIW | MIN      | MAX   | MIN       | MAX   |  |

| А   | 0.80     | 1.00  | 0.031     | 0.039 |  |

| A1  | 0.00     | 0.05  | 0         | 0.002 |  |

| A3  | 0.20 RE  | F     | 0.008 R   | EF    |  |

| K   | 0.20 MI  | N     | 0.008 MIN |       |  |

| е   | 0.50 BS  | C     | 0.02 BSC  |       |  |

| L   | 0.30     | 0.50  | 0.012     | 0.02  |  |

| b   | 0.18     | 0.30  | 0.007     | 0.012 |  |

| D2  | 6.00     | 6.25  | 0.236     | 0.246 |  |

| E2  | 6.00     | 6.25  | 0.236     | 0.246 |  |

| D   | 8.00 BSC |       | 0.315 BSC |       |  |

| E   | 8.00 BS  | C     | 0.315 BSC |       |  |

### Note:

1. Dimensions do not include protrusions; these shall not exceed 0.155mm (.006") on any side. Lead dimension shall not include solder coverage.

www.Microsemi.com

32 CHANNEL LED BACKLIGHT CONTROLLER

DATASHEET

# LX24232ILQ Principle of Operation

LX<sup>®</sup>24232ILQ 32-Channel Display Backlight LED Controller is designed to drive up to 32 LED strings and control external power supplies to regulate LED current. Interface with the Hosting system (Video Processor / Timing Controller (TCON) / MCU) is accomplished via a standard SPI bus. LED current and PWM dimming duty-cycle commands are received from Hosting system in a digital format and executed by internal circuitry to obtain desired backlight control. In addition, device provides a power supply control signal (PS\_CTRL) used to control external power supply and trim it to optimum level. This minimizes system power dissipation, while maintaining accurate current regulation for each of the 32 LED strings.

# **Block Diagram**

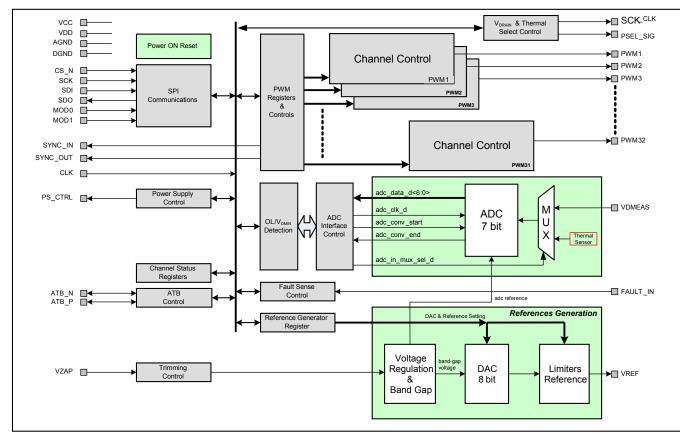

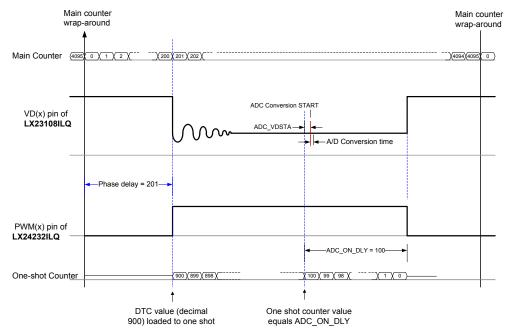

Figure 3 shows LX<sup>®</sup>24232ILQ LED 32-Channel Display Backlight LED Controller block diagram, describing its main functions. SPI block implements communication with external Controller. Power supply control circuitry adjusts LED strings' main voltage by utilizing PDM method (Pulse Density Modulation). Scanning control circuitry includes the required logic needed for performing zone selection.

Figure 3: LX®24232ILQ: Detailed Block Diagram

LX24232

www.Microsemi.com

**32 CHANNEL LED BACKLIGHT CONTROLLER**

DATASHEET

### **SPI Interface Characteristics**

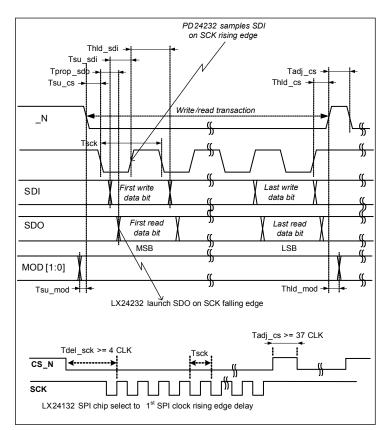

SPI interface consists of four signal lines: SDI, SDO, SCK, and CS\_N (see

Figure 4).

- **SDI**: Serial data input to LX<sup>®</sup>24232ILQ

- SDO: Serial data output from LX<sup>®</sup>24232ILQ

- SCK: Serial data clock input

- **CS\_N**: Serial data chip select

SDI signal is sampled at the rising edge of SCK, while SDO is driven at the falling edge of SDK, where MSB is shifted out first.

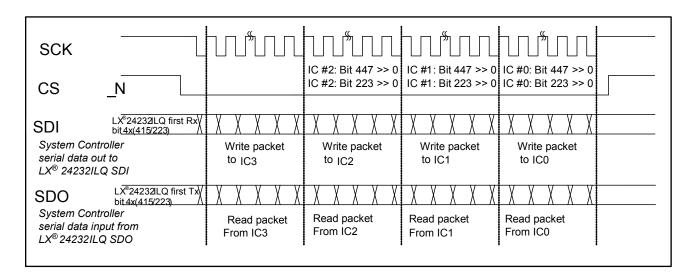

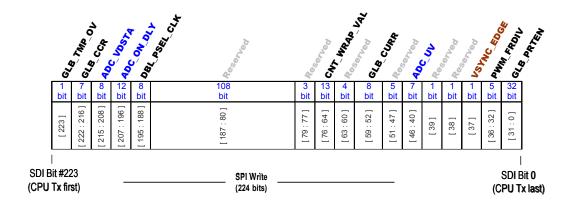

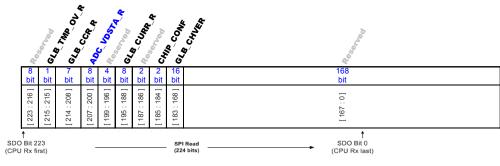

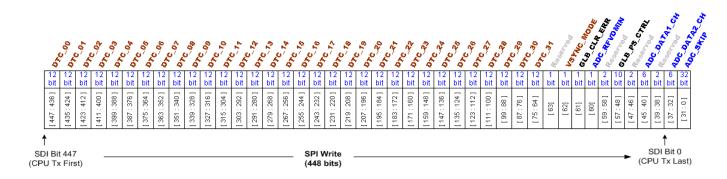

SPI data transmission/reception should be executed, starting from bit 447 to bit 0 (DTC Packet / Phase-Delay Packet modes), or starting from bit 223 to bit 0 (Configuration mode). Figure 5 displays SPI timing diagram for a 4-driver configuration. SPI data of the fourth LX<sup>®</sup>24232ILQ is transmitted first, following SPI data of the third, second and then first LX<sup>®</sup>24232ILQ.

# **SPI Noise Immunity**

LX<sup>®</sup>24232ILQ SPI interface includes special noise immunity protection mechanisms, which improve electrical SPI interface immunity against high frequencies noise, short spikes and glitches in a noisy PCB environment. These mechanisms include:

- Filter short glitches and spikes of CS\_N, MOD\_0 and MOD\_1 signals. These signals should remain in either logic "1" or logic "0" for at least 8 clocks (CLK). Shorter periods will be ignored.

- Ignore SPI transaction if number of SPI SCK clocks is not an integer multiple of 8 (8, 16, 24, 32, etc.); in this case

internal registers remains unchanged.

- If SPI CS\_N chip select signal is Set Low for less than 8 x System Clocks, this pulse is ignored, the transaction is canceled and the internal registers remains unchanged.

# **SPI** Timing

Figure 4 and Figure 5 describe LX<sup>®</sup>24232ILQ SPI timing. Refer to Table 1 for timing characteristics.

- Last communication transaction before main counter wraps MUST be of "DTC Packet" type, otherwise transaction will not be loaded.

- First SCK SPI rising edge should occur Tdel\_sck after CS\_N SPI chip select negation.

- Minimum time between the end of SPI transaction to the beginning of the next one should be Tadj\_cs.

- CS\_N must be set to "1" at least 8 sysclks before SYNC\_IN signal arrives. Otherwise, data will be ignored.

# LX24232

# 32 CHANNEL LED BACKLIGHT CONTROLLER

### DATASHEET

Figure 4: SPI Signals Diagrams

### **Table 1 - Timing Characteristics**

| PARAMETER                                             | SYMBOL                  | TEST CONDITIONS / COMMENT                          |      | LX <sup>®</sup> 24232ILQ LED<br>CONTROLLER |      |     |

|-------------------------------------------------------|-------------------------|----------------------------------------------------|------|--------------------------------------------|------|-----|

|                                                       |                         |                                                    | MIN. | TYP.                                       | MAX. |     |

| SDI set up time to SCK                                | T <sub>su_sdi</sub>     |                                                    | 5    |                                            |      | ns  |

| SDI hold time to SCK                                  | T <sub>hld_sdi</sub>    |                                                    | 5    |                                            |      | ns  |

| SDO prop delay from SCK                               | T <sub>prop_sdo</sub>   | 20 pF capacitive load                              |      |                                            | 12   | ns  |

| CS_N set up time to SCK                               | T <sub>su_cs</sub>      |                                                    | 5    |                                            |      | ns  |

| CS_N hold time to SCK                                 | T <sub>hld_cs</sub>     |                                                    | 5    |                                            |      | ns  |

| Time between adjacent SPI transactions                | T <sub>adj_cs</sub>     |                                                    |      | 37                                         |      | CLK |

| Time from de-assertion of CS_N to 1st SCK rising edge | T <sub>del_sck</sub>    |                                                    | 8    |                                            |      | CLK |

| MOD[1:0] set up time to CS                            | T <sub>su_mod</sub>     |                                                    | 8    |                                            |      | CLK |

| MOD[1:0] hold time to CS                              | T <sub>hld_mod</sub>    |                                                    | 0    |                                            |      | CLK |

| SYNC_IN propagation delay                             | T <sub>PD_SYNC_IN</sub> |                                                    | 8    |                                            |      | CLK |

| SYNC_IN pulse width                                   | sync_in_pulse           |                                                    | 4    |                                            |      | CLK |

| SYNC_OUT pulse width                                  | sync_out_pulse          | T <sub>SYNC_OUT</sub> [CLK] =<br>320*(PWM_FRDIV+1) |      | 320                                        |      | CLK |

Copyright © Microsemi

Rev 2.2 Updated: August 23, 2011, 17:21

### CONFIDENTIAL

# LX24232

**32 CHANNEL LED BACKLIGHT CONTROLLER**

DATASHEET

### Figure 5: SPI Signals Diagram for a Four LED Controllers Configuration

LX24232

mi *Microsemi* Page 1 gust 23, 2011, 17:21 Analog Mixed Signal Group 11861 Western Avenue, Garden Grove, CA. 92841, USA; Phone: 714-898-8121, Fax: 714-893-2570

32 CHANNEL LED BACKLIGHT CONTROLLER

DATASHEET

# LX24232ILQ Application Information \_

### **Communication packet types**

Chip configuration and monitoring is accomplished by sending and receiving a series of bits over SPI.

There are four transaction types that select the type of communication packet to be transmitted to LX24232. Only three of the four possible transaction types are used. These transactions are described in Table 2:

Table 2 – Communication Packet Types

| MOD_1 pin | MOD_0 pin | TRANSACTION TYPE                                    |

|-----------|-----------|-----------------------------------------------------|

| "0"       | "0"       | Duty Cycle Packet (12-bits resolution per channel)  |

| "0"       | "1"       | Phase Delay Packet (12 bits resolution per channel) |

| "1"       | "0"       | Configuration Packet                                |

| '1"       | '1"       | Reserved for production                             |

Packet type is chosen by setting MOD\_0 and MOD\_1 pins of LX24232ILQ according to Table 2, where: "0" – MOD\_x signal is logic low.

"1" – MOD\_x signal is logic high.

### **SPI Transaction Packets Overview:**

LX24232ILQ SPI mechanism is based on a shift-register.

For each SPI transaction sent to LX24232ILQ (*Write* transactions), an SPI transaction of the same length is sent back to MCU (*Read* transaction).

There are four types of transaction packets:

- DTC (Duty-Cycle) Packet: Write packet contains duty-cycle data for each channel, in addition to control bits for controlling on-going operations. Read packet contains all information (ADC measurements, channel number having minimum drain-voltage measurement, etc.) required for on-going operation.

- **PD (Phase-Delay) Packet**: Write packet contains phase-delay values for each channel; Read packet contains no information (don't care).

- **CONFIG (Configuration) Packet**: Write packet contains all LX24232ILQ configuration fields, such as PWM frequency, LED current, etc. Read packet contains read-back of configuration information.

- **Production packet**: For production purposes only; cannot be accessed in normal operation.

Important note: Bit locations with higher values indicate the most significant bit.

Example:

In ADC\_DATA2 register in DTC-Read packet, bits 0-6 (bit location 400-406) represent ADC measurement value. Therefore, <u>bit location 406</u> (bit 6 of the register) is the <u>Most Significant bit</u>, and <u>bit location 400</u> (bit 0 of the register) is the <u>least significant bit</u>.

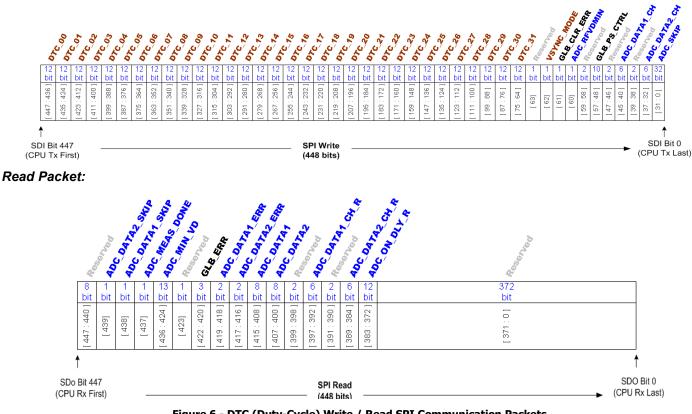

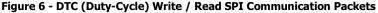

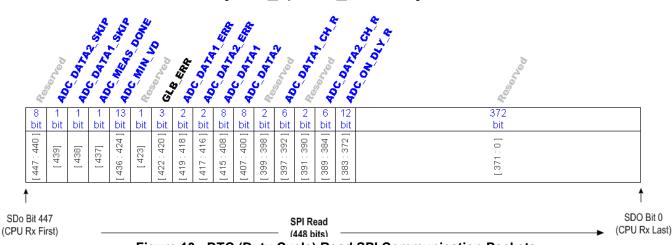

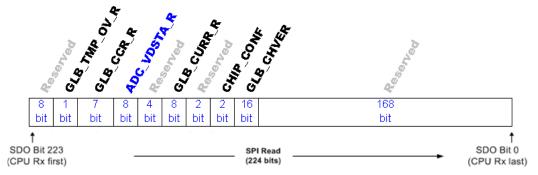

Figure 6, Figure 7, and Figure 8 illustrate the read/write registers involved in each SPI bit stream for operation and configuration mode<sup>1</sup>.

<sup>1</sup> For more details regarding specific bit(s) functions, contact your local Microsemi© representative.

**32 CHANNEL LED BACKLIGHT CONTROLLER**

DATASHEET

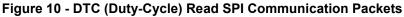

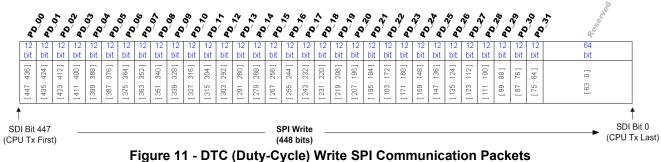

### DTC (Duty-Cycle) Packet (Mode Select Pins MOD\_1, MOD\_0 = "00"):

### Write Packet:

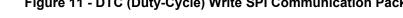

### PD (Phase Delay) Packet (Mode Select Pins MOD\_1, MOD\_0 = "01"):

### Write Packet:

### Read Packet:

**32 CHANNEL LED BACKLIGHT CONTROLLER**

DATASHEET

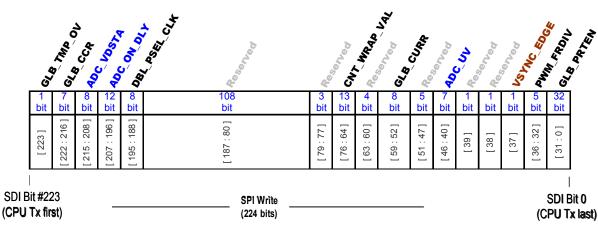

### Configuration Packet (Mode Select Pins MOD\_1, MOD\_0 = "10"):

Write Packet:

Read Packet:

Figure 8 - Config Packet Write / Read Packets

For multiple chip applications, SPI communication should be cascaded (see Figure 5).

LX24232

www.Microsemi.com

**32 CHANNEL LED BACKLIGHT CONTROLLER**

DATASHEET

# **Detailed SPI Transaction Packets Description**

DTC-Write Packet Bit Description (MOD\_1, MOD\_0 = "00"):

### Figure 9 - DTC (Duty-Cycle) Write SPI Communication Packets

### Table 3 - DTC Write Packet Bit Description Table

| Field<br># | Register Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Trans.<br>Type | Bit Location | Length<br>(bits) | Reset<br>Value |

|------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|------------------|----------------|

| 1          | ADC_SKIP      | ADC converter "skip channel measurement" control bit.<br>Bit-per-channel control. When ADC_SKIP(n) bit is set, ADC will skip drain voltage measurement of the selected channel. For example, if ADC_SKIP(1) = "1", then LX23108ILQ channel connected to PWM1 pin will be skipped.<br>ADC_SKIP bit should be set if duty-cycle value (DTC_xx) of a channel is lower than ADC_ON_DLY register value (see CONFIG-Write packet):<br>set ADC_SKIP(n) = $\begin{cases} 0 & if (DTC_n > ADC_ON_DLY) \\ 1 & if (DTC_n \le ADC_ON_DLY) \end{cases}$ | DTC<br>Write   | 0-31         | 32               | N/A            |

| 2          | ADC_DATA2_CH  | ADC_DATA2_CH = 0 to 31: Selects which PWM FET V <sub>drain</sub> channel ADC2<br>should measure.<br>ADC_DATA2_CH = 32: ADC2 measures LX <sup>®</sup> 24232ILQ chip temperature.<br>Refer to ADC_DATA2 register (DTC read-packet)                                                                                                                                                                                                                                                                                                           | DTC<br>Write   | 32-37        | 6                | 0x00           |

| 3          | Reserved      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DTC<br>Write   | 38-39        | 2                | N/A            |

| 4          | ADC_DATA1_CH  | ADC_DATA2_CH = 0 to 31: Selects which PWM FET Vdrain channel ADC1 should measure.<br>ADC_DATA2_CH = 32: ADC1 measures LX <sup>®</sup> 24232ILQ chip temperature.<br>Refer to ADC_DATA1 register (DTC read-packet).                                                                                                                                                                                                                                                                                                                         | DTC<br>Write   | 40-45        | 6                | 0x00           |

| 5          | Reserved      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DTC<br>Write   | 46-47        | 2                | N/A            |

32 CHANNEL LED BACKLIGHT CONTROLLER

### DATASHEET

| Field<br># | Register Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Trans.<br>Type | Bit Location | Length<br>(bits) | Reset<br>Value |

|------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|------------------|----------------|

| 6          | GLB_PS_CTRL   | Ten bit D/A used for controlling PS voltage, controlling LEDs power supply.<br>Register value controls PDM (Pulsed Density Modulation) signal on PS_CTRL output pin. External RC-filter (typically 2K $\Omega$ and 0.1µF) converts PDM signal to DC voltage ranging from 0 to 3.3VDC.<br>$PS\_CTRL[V]^* = GLB\_PS\_CTRL \cdot \frac{3.3V}{1024}$ * After RC low-pass filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DTC<br>Write   | 48-57        | 10               | 0x100          |

| 7          | Reserved      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DTC<br>Write   | 58-59        | 2                | N/A            |

| 8          | ADC_RFVDMIN   | ADC refresh minimum VD measurement control bit.<br>Setting bit to "1" sets ADC_MINVD register measured bits 0-6 to 0x7F and clears valid bit 7 (DTC read-packet).<br>ADC_RFMINVD bit is immediately cleared. Chip starts measuring FET V <sub>drain</sub> for all 32 strings.<br>After all 32 FET V <sub>drain</sub> channels are measured, ADC_MIN_VD register, bits 0-6 (adc_measure bits), contains the lowest FET V <sub>drain</sub> ADC reading.<br>ADC_MIN_VD Valid bit 7 is set to '1' and ADC_MEASURE_DONE register bit 0 is set to '1'.<br>Whenever ADC_MEASURE_DONE register equals '1', it means LX®24232ILQ had found the lowest FET V <sub>drain</sub> out of 32 channels. User should read<br>ADC_MIN_VD register's value and trim PS voltage by writing to the GLB_PS_CTRL register.<br>Setting again ADC_RFMINVD bit to 1 will start a new minimum FET V <sub>drain</sub> search cycle.                                      | DTC<br>Write   | 60           | 1                | 0x00           |

| 9          | GLB_CLR_ERR   | Setting bit to 1 clears GLB_ERR register error bits (DTC Read-packet bits 420 to 422) and re-enables all channels that were turned off by $LX^{\textcircled{0}}23108ILQ$ 8-Port LED Drivers due to FET V <sub>drain</sub> over-voltage or over-temperature. Note that over temperature/over-voltage bit in GLB_ERR register cannot be cleared by GLB_CLR_ERR register in cases where it was set due to over temperature event.<br>This field is cleared on write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DTC<br>Write   | 61           | 1                | 0x00           |

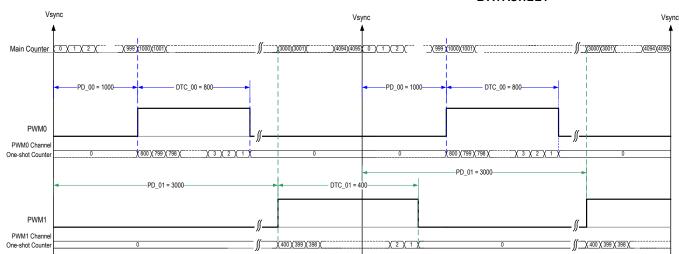

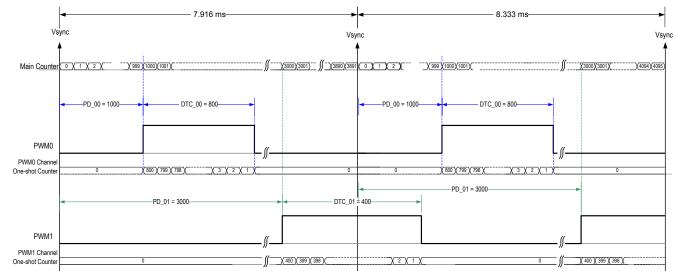

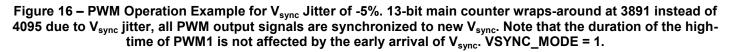

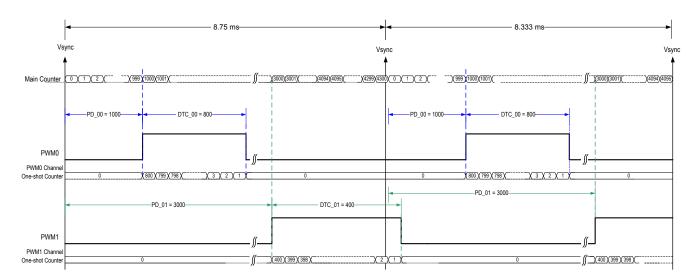

| 10         | VSYNC_MODE    | External <i>SYNC_IN pin</i> synchronization mode.<br><b>VSYNC_MODE = "0":</b> No synchronization mode (Stand-Alone operation).<br>In this mode LX24232ILQ ignores SYNC_IN input pin state, and PWM block<br>internal 13-bit main counter automatically wraps-around at 4095> 0.<br><b>VSYNC_MODE = "1":</b> External Synchronization mode.<br>In this mode, PWM output signals are synchronized to either a rising-edge or<br>a falling edge (selected by VSYNC_EDGE field in CONFIG packet, bit 37) of<br>SYNC_IN pin.<br>PWM block 13-bit main counter wraps-around when synchronization signal<br>arrives, synchronizing PWM output signals.<br>If synchronization signal fails to arrive (SYNC_IN pin state does not change),<br>13-bit main counter wraps-around at the value written in CNT_WRAP_VAL<br>register (CONFIG-Write packet, bits 64 to 76).<br>For more information, see <u>"PWM Synchronization input (SYNC_IN pin)"</u> . | DTC<br>Write   | 62           | 1                | 0x00           |

Page 17 of 43

**LX24232**

32 CHANNEL LED BACKLIGHT CONTROLLER

DATASHEET

| #Register NameDescriptionTypeRel Location(bits)Vi11ReservedReserved $DTC_{10}$ 63111ReservedReserved $DTC_{10}$ 63112PVM output high-time (duty-cycle) control.<br>Sets PVM high-time (duty-cycle) control for PVM channel 31 one-shot down-<br>control.DTC_064-75112DTC_31 $\frac{17PML(a)-TT}{MML} = \frac{MTC_0(a)}{4M6} \cdot \frac{TPMML_CTCLE fms] + if OTC_0(a) - 4005}{MMH_CTCLE(m) + if OCOTC_1(a) - 4005}.DTC64-75113DTC_30PVM high-time (duty-cycle) control for PVM23. Refer to DTC_31.DTCWrite76-671214DTC_29PVM high-time (duty-cycle) control for PVM22. Refer to DTC_31.DTCWrite88-9912115DTC_26PVM high-time (duty-cycle) control for PVM23. Refer to DTC_31.DTCWrite100-1111216DTC_27PVM high-time (duty-cycle) control for PVM25. Refer to DTC_31.DTCWrite136-1471218DTC_26PVM high-time (duty-cycle) control for PVM25. Refer to DTC_31.DTCWrite136-1471219DTC_23PVM high-time (duty-cycle) control for PVM25. Refer to DTC_31.DTCWrite136-1471219DTC_24PVM high-time (duty-cycle) control for PVM25. Refer to DTC_31.DTCWrite146-1711219DTC_23PVM high-time (duty-cyc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | DATASHEET     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |              |    |                |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|----|----------------|--|--|

| 11ReservedWrite6.3112PWM output light-time (duty-cycle) control.<br>Sets PWM high-time (duty-cycle) control.<br>Sets PWM high-time (duty-cycle) control.<br>Sets PWM high-time (duty-cycle) control for PWM31 output pin.<br>DTC range is 0 to 0495.<br>Value writen to FWM output is defined by the following formula:<br>$T_{PRH_{1}(p)=T}[m] = \begin{bmatrix} \frac{DTC_{-2}(1)}{2006} - T_{PRH_{-1}CTC_{-1}(p) \leq 4094} \\ \frac{DTC_{-31}}{2006} - T_{PRH_{-1}CTC_{-1}(p) \leq 4095} \end{bmatrix}$ DTC<br>More is 0 to 31, and:<br>$T_{PRH_{1}(p)=T}[m] = \begin{bmatrix} \frac{DTC_{-2}(1)}{4006} - T_{PRH_{-1}CTC_{-1}(p) \leq 4094} \\ \frac{DTC_{-31}}{2006} - T_{PRH_{-1}CTC_{-1}(p) \leq 4095} \end{bmatrix}$ DTC<br>More is 0 to 31, and:<br>$T_{PRH_{-1}CTC_{-1}(p) = \frac{4096 \cdot (PWM_{-1}FRDH' + 1)}{1000 \cdot CLK_{1}MIE_{-1}} \end{bmatrix}$ DTC<br>More is 0 to 31, and:<br>$T_{PRH_{-1}CTCLE_{-1}(m) = \frac{4096 \cdot (PWM_{-1}FRDH' + 1)}{1000 \cdot CLK_{1}MIE_{-1}} \end{bmatrix}$ DTC<br>More is 0 to 31, and:<br>$T_{PRH_{-1}CTCLE_{-1}(m) = \frac{4096 \cdot (PWM_{-1}FRDH' + 1)}{1000 \cdot CLK_{1}MIE_{-1}} \end{bmatrix}$ DTC<br>More is 0 to 31, and:<br>$T_{PRH_{-1}CTCLE_{-1}(m) = \frac{4096 \cdot (PWM_{-1}FRDH' + 1)}{1000 \cdot CLK_{1}MIE_{-1}} \end{bmatrix}$ DTC<br>More is 0 for 0 to CL 31 values are loaded to DTC_0-DTC_31 registers<br>aginal.<br>For more information see "Advanced PWH output control".DTC<br>More is 0 for 0 to CL 31 values are loaded to DTC_0-DTC_31.DTC<br>Write76-871213DTC_29PWM high-time (duty-cycle) control for PWM29. Refer to DTC_31.DTC<br>Write88-991214DTC_29PWM high-time (duty-cycle) control for PWM22. Refer to DTC_31.DTC<br>Write112-11215DTC_26PWM high-time (duty-cycle) control for PWM22. Refer to DTC_31.DTC<br>Write126-14719DTC_21PWM high-time (duty-cycle) control for PWM22. Refer to DTC_31                                                                                                                                                                                                                                                                                                                                                                                                  |    | Register Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              | Bit Location |    | Reset<br>Value |  |  |

| 12DTC_31Sets PWH high-time (PWM output = "1") of PWM31 output pin.<br>DTC range is 0 to 4095.<br>Value written in this field is written to PWM othannel 31 one-shot down-<br>counter.<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11 | Reserved      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | 63           | 1  | N/A            |  |  |

| 13       DTC_30       PWM high-time (duty-cycle) control for PWM30. Refer to DTC_31.       Write       76-87       12         14       DTC_29       PWM high-time (duty-cycle) control for PWM29. Refer to DTC_31.       DTC<br>Write       88-99       12         15       DTC_28       PWM high-time (duty-cycle) control for PWM28. Refer to DTC_31.       DTC<br>Write       100-111       12         16       DTC_27       PWM high-time (duty-cycle) control for PWM27. Refer to DTC_31.       DTC<br>Write       112-123       12         17       DTC_26       PWM high-time (duty-cycle) control for PWM26. Refer to DTC_31.       DTC<br>Write       124-135       12         18       DTC_25       PWM high-time (duty-cycle) control for PWM25. Refer to DTC_31.       DTC<br>Write       136-147       12         19       DTC_24       PWM high-time (duty-cycle) control for PWM23. Refer to DTC_31.       DTC<br>Write       148-159       12         20       DTC_23       PWM high-time (duty-cycle) control for PWM23. Refer to DTC_31.       DTC<br>Write       160-171       12         21       DTC_22       PWM high-time (duty-cycle) control for PWM22. Refer to DTC_31.       DTC<br>Write       172-183       12         22       DTC_23       PWM high-time (duty-cycle) control for PWM22. Refer to DTC_31.       DTC<br>Write       172-183       12 <td>12</td> <td>DTC_31</td> <td>Sets PWM high-time (PWM output = "1") of PWM31 output pin.<br/>DTC range is 0 to 4095.<br/>Value written in this field is written to PWM channel 31 one-shot down-<br/>counter.<br/>Absolute high-time of PWM output is defined by the following formula:<br/><math display="block"> \frac{T_{PWM(n)="1"}[ms] = \begin{cases} \frac{DTC_{(n)}}{4096} \cdot T_{PWM_{CYCLE}}[ms] &amp; \text{if } 0 \le DTC_{(n)} \le 4094 \\ Always &amp; "1" &amp; \text{if } DTC_{(n)} = 4094 \end{cases} </math> Where: n = 0 to 31, and:<br/><math display="block"> \frac{T_{PWM_{CYCLE}}[ms] = \frac{4096 \cdot (PWM_{FRDIV} + 1)}{1000 \cdot CLK[MHz]}}{1000 \cdot CLK[MHz]} </math> Note: New DTC_0 to DTC_31 values are loaded to DTC_0-DTC_31 registers on next PWM main-counter wrap-around, after rising edge of CS_N input signal.</td> <td></td> <td>64-75</td> <td>1</td> <td>N/A</td> | 12 | DTC_31        | Sets PWM high-time (PWM output = "1") of PWM31 output pin.<br>DTC range is 0 to 4095.<br>Value written in this field is written to PWM channel 31 one-shot down-<br>counter.<br>Absolute high-time of PWM output is defined by the following formula:<br>$ \frac{T_{PWM(n)="1"}[ms] = \begin{cases} \frac{DTC_{(n)}}{4096} \cdot T_{PWM_{CYCLE}}[ms] & \text{if } 0 \le DTC_{(n)} \le 4094 \\ Always & "1" & \text{if } DTC_{(n)} = 4094 \end{cases} $ Where: n = 0 to 31, and:<br>$ \frac{T_{PWM_{CYCLE}}[ms] = \frac{4096 \cdot (PWM_{FRDIV} + 1)}{1000 \cdot CLK[MHz]}}{1000 \cdot CLK[MHz]} $ Note: New DTC_0 to DTC_31 values are loaded to DTC_0-DTC_31 registers on next PWM main-counter wrap-around, after rising edge of CS_N input signal. |              | 64-75        | 1  | N/A            |  |  |

| 14       DTC_29       PWM high-time (duty-cycle) control for PWM29. Refer to DTC_31.       Write       88-99       12         15       DTC_28       PWM high-time (duty-cycle) control for PWM28. Refer to DTC_31.       DTC<br>Write       100-111       12         16       DTC_27       PWM high-time (duty-cycle) control for PWM27. Refer to DTC_31.       DTC<br>Write       112-123       12         17       DTC_26       PWM high-time (duty-cycle) control for PWM26. Refer to DTC_31.       DTC<br>Write       124-135       12         18       DTC_25       PWM high-time (duty-cycle) control for PWM25. Refer to DTC_31.       DTC<br>Write       136-147       12         19       DTC_24       PWM high-time (duty-cycle) control for PWM23. Refer to DTC_31.       DTC<br>Write       160-171       12         20       DTC_23       PWM high-time (duty-cycle) control for PWM23. Refer to DTC_31.       DTC<br>Write       160-171       12         21       DTC_22       PWM high-time (duty-cycle) control for PWM22. Refer to DTC_31.       DTC<br>Write       172-183       12         22       DTC_21       PWM high-time (duty-cycle) control for PWM21. Refer to DTC_31.       DTC<br>Write       172-183       12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13 | DTC_30        | PWM high-time (duty-cycle) control for PWM30. Refer to DTC_31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 76-87        | 12 | N/A            |  |  |

| 15DTC_28PWM high-time (duty-cycle) control for PWM28. Refer to DTC_31.Write100-1111216DTC_27PWM high-time (duty-cycle) control for PWM27. Refer to DTC_31.DTC<br>Write112-1231217DTC_26PWM high-time (duty-cycle) control for PWM26. Refer to DTC_31.DTC<br>Write124-1351218DTC_25PWM high-time (duty-cycle) control for PWM25. Refer to DTC_31.DTC<br>Write136-1471219DTC_24PWM high-time (duty-cycle) control for PWM24. Refer to DTC_31.DTC<br>Write148-1591220DTC_23PWM high-time (duty-cycle) control for PWM23. Refer to DTC_31.DTC<br>Write160-1711221DTC_22PWM high-time (duty-cycle) control for PWM22. Refer to DTC_31.DTC<br>Write172-1831222DTC_21PWM high-time (duty-cycle) control for PWM22. Refer to DTC_31.DTC<br>Write172-18312                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14 | DTC_29        | PWM high-time (duty-cycle) control for PWM29. Refer to DTC_31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 88-99        | 12 | N/A            |  |  |

| 16DTC_27PWM high-time (duty-cycle) control for PWM27. Refer to DTC_31.Write112-1231217DTC_26PWM high-time (duty-cycle) control for PWM26. Refer to DTC_31.DTC<br>Write124-1351218DTC_25PWM high-time (duty-cycle) control for PWM25. Refer to DTC_31.DTC<br>Write136-1471219DTC_24PWM high-time (duty-cycle) control for PWM24. Refer to DTC_31.DTC<br>Write148-1591220DTC_23PWM high-time (duty-cycle) control for PWM23. Refer to DTC_31.DTC<br>Write160-1711221DTC_22PWM high-time (duty-cycle) control for PWM22. Refer to DTC_31.DTC<br>Write172-1831222DTC_21PWM high-time (duty-cycle) control for PWM21. Refer to DTC_31.DTC<br>Write172-18312                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 | DTC_28        | PWM high-time (duty-cycle) control for PWM28. Refer to DTC_31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 100-111      | 12 | N/A            |  |  |