my-d™ move my-d™ move NFC SLE 66R01P

SLE 66R01PN

Intelligent 1216 bit EEPROM with Contactless Interface compliant to ISO/IEC 14443-3 Type A and support of NFC Forum™ Type 2 Tag Operation

Data Book

2011-11-24

Chip Card & Security

Edition 2011-11-24

Published by Infineon Technologies AG 81726 Munich, Germany © 2011 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

my-d™ move / my-d™ move NFC - SLE 66R01P / SLE 66R01PN Data Book The information in this document is subject to change without notice.

**Revision History: Current Version 2011-11-24**

| Previou | Previous Release: Preliminary 2011-11-18                                                 |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Page    | Subjects (major changes since last revision)                                             |  |  |  |  |  |  |

| All     | Editorial changes; removed "Preliminary" status; update of figures (memory organization) |  |  |  |  |  |  |

| -       |                                                                                          |  |  |  |  |  |  |

|         |                                                                                          |  |  |  |  |  |  |

|         |                                                                                          |  |  |  |  |  |  |

|         |                                                                                          |  |  |  |  |  |  |

|         |                                                                                          |  |  |  |  |  |  |

|         |                                                                                          |  |  |  |  |  |  |

|         |                                                                                          |  |  |  |  |  |  |

#### **Trademarks of Infineon Technologies AG**

BlueMoon<sup>TM</sup>, COMNEON<sup>TM</sup>, C166<sup>TM</sup>, CROSSAVE<sup>TM</sup>, CanPAK<sup>TM</sup>, CIPOS<sup>TM</sup>, CoolMOS<sup>TM</sup>, CoolSET<sup>TM</sup>, CORECONTROL<sup>TM</sup>, DAVE<sup>TM</sup>, EasyPIM<sup>TM</sup>, EconoBRIDGE<sup>TM</sup>, EconoDUAL<sup>TM</sup>, EconoPACK<sup>TM</sup>, EconoPIM<sup>TM</sup>, EiceDRIVER<sup>TM</sup>, EUPEC<sup>TM</sup>, FCOS<sup>TM</sup>, HITFET<sup>TM</sup>, HybridPACK<sup>TM</sup>, ISOFACE<sup>TM</sup>, IsoPACK<sup>TM</sup>, IsoPACK<sup>TM</sup>, MIPAQ<sup>TM</sup>, ModSTACK<sup>TM</sup>, my-d<sup>TM</sup>, NovalithIC<sup>TM</sup>, OmniTune<sup>TM</sup>, OptiMOS<sup>TM</sup>, ORIGA<sup>TM</sup>, PROFET<sup>TM</sup>, PRO-SIL<sup>TM</sup>, PRIMARION<sup>TM</sup>, PrimePACK<sup>TM</sup>, RASIC<sup>TM</sup>, ReverSave<sup>TM</sup>, SatRIC<sup>TM</sup>, SensoNor<sup>TM</sup>, SIEGET<sup>TM</sup>, SINDRION<sup>TM</sup>, SMARTi<sup>TM</sup>, SmartLEWIS<sup>TM</sup>, TEMPFET<sup>TM</sup>, thinQ!<sup>TM</sup>, TriCore<sup>TM</sup>, TRENCHSTOP<sup>TM</sup>, X-GOLD<sup>TM</sup>, XMM<sup>TM</sup>, X-PMU<sup>TM</sup>, XPOSYS<sup>TM</sup>.

#### **Other Trademarks**

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, PRIMECELL™, REALVIEW™, THUMB™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth<sup>™</sup> of Bluetooth SIG Inc. CAT-iq<sup>™</sup> of DECT Forum. COLOSSUS<sup>™</sup>, FirstGPS<sup>™</sup> of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NFC Forum™ is trademark of Near Field Communication Forum, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Sattelite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Data Book 3 / 55 2011-11-24

# **Table of Contents**

| <b>1</b><br>1.1                                                                                                      | Pin description                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                                               | my-d™ Product Family                                                                                                                                                                                                                                                                                                                                                                                                                             | 10                                                                   |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3<br>3.4                                                         | Scope of my-d™ move / my-d™ move NFC  Circuit Description  Memory Principle  Service Area 1  User Area 1  User Area 2  Service Area 2  Memory Principle for NFC Forum™ Type 2 Tag  System Overview                                                                                                                                                                                                                                               | 12<br>12<br>13<br>14<br>14<br>14<br>14<br>15                         |

| 3.5<br>3.6<br>3.7                                                                                                    | UID Coding Supported Standards Command Set                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                                   |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.2.1<br>4.2.3<br>4.2.4<br>4.2.5<br>4.3<br>4.3.1<br>4.3.2<br>4.4<br>4.4.1<br>4.4.2 | Memory Organization  User Memory Area 1 and 2  Service Area 1 and 2  Unique Identifier (UID)  Configuration Byte  Locking Mechanism for the Configuration Byte  Locking mechanism  OTP Block  Manufacturer Block (25H)  Memory Principle for NFC Forum™ Type 2 Tag  NFC Forum™ Static Memory Structure  NFC Forum™ Dynamic Memory Structure  Transport Configuration  Transport Configuration my-d™ move  Transport Configuration my-d™ move NFC | 18<br>19<br>19<br>20<br>21<br>22<br>23<br>23<br>24<br>26<br>26<br>27 |

| <b>5</b><br>5.1<br>5.2<br>5.3                                                                                        | Password         Password Block         Password Retry Counter         Anti-tearing Mechanism for Password Retry Counter                                                                                                                                                                                                                                                                                                                         | 29<br>29                                                             |

| 6<br>6.1<br>6.2<br>6.3<br>6.4                                                                                        | 16-bit Value Counter Functionality  Value Counter Format  Loading and Reading of Value Counter  Decrementing Value Counter and Anti-Tearing  Protection Mechanisms for the Value Counter                                                                                                                                                                                                                                                         | 32<br>33<br>34                                                       |

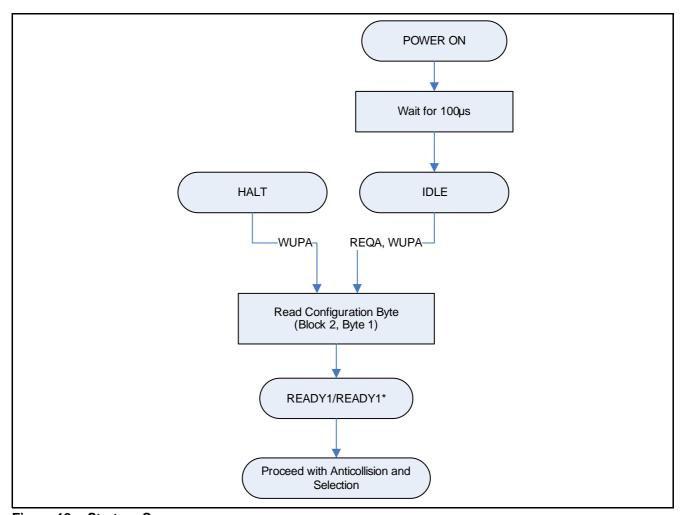

| <b>7</b><br>7.1<br>7.2<br>7.2.1<br>7.2.2                                                                             | Communication Principle Communication between a card (PICC) and a reader (PCD) State Diagram IDLE/HALT State READY1/READY1* State                                                                                                                                                                                                                                                                                                                | 35<br>35<br>35                                                       |

| 7.2.3<br>7.2.4<br>7.2.5<br>7.3<br>7.3.1<br>7.4<br>7.5 | READY2/READY2* State  ACTIVE/ACTIVE* State  HALT State  Start up  Start-up sequence of the SLE 66R01P and SLE 66R01PN  Frame Delay Time  Error Handling | 36<br>36<br>37<br>37<br>37 |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 8                                                     | Command Set                                                                                                                                             |                            |

| 8.1                                                   | Supported ISO/IEC 14443-3 Type A Command Set                                                                                                            |                            |

| 8.2                                                   | Memory Access Command Set                                                                                                                               |                            |

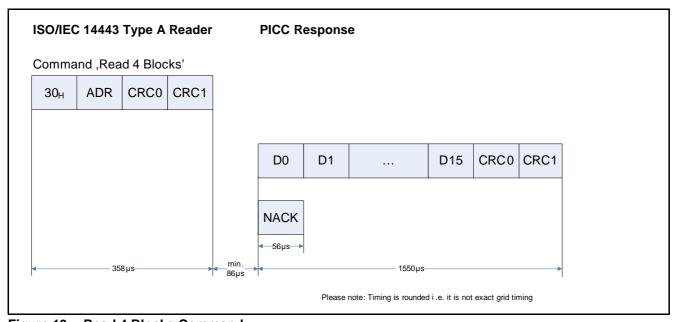

| 8.2.1                                                 | Read 4 Blocks (RD4B)                                                                                                                                    | 41                         |

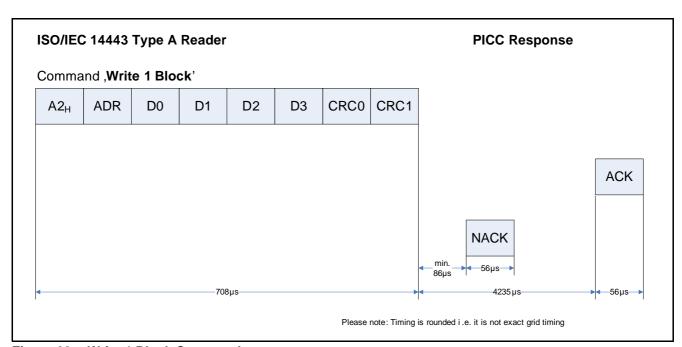

| 8.2.2                                                 | Write 1 Block (WR1B)                                                                                                                                    | 42                         |

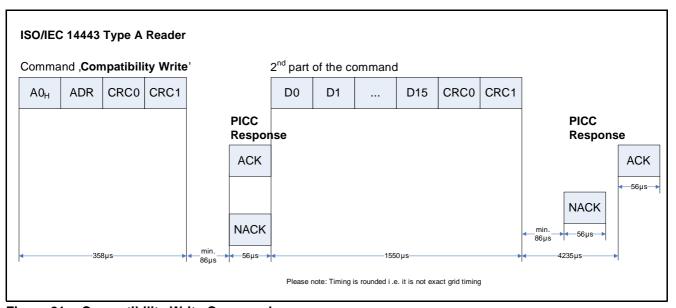

| 8.2.3                                                 | Compatibility Write Command (CPTWR)                                                                                                                     |                            |

| 8.2.4                                                 | Read 2 Blocks (RD2B)                                                                                                                                    |                            |

| 8.2.5                                                 | Write 2 Blocks (WR2B)                                                                                                                                   | 45                         |

| 8.2.6                                                 | Set Password (SPWD)                                                                                                                                     | 46                         |

| 8.2.7                                                 | Access (ACS)                                                                                                                                            | 47                         |

| 8.2.8                                                 | Decrement Command (DCR16)                                                                                                                               | 49                         |

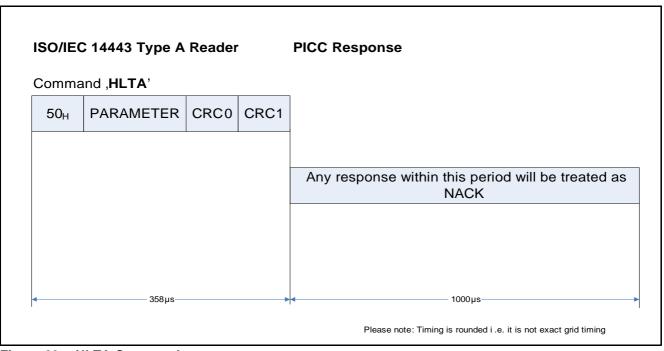

| 8.2.9                                                 | HLTA command                                                                                                                                            | 51                         |

| 8.3                                                   | my-d™ move and my-d™ move NFC responses                                                                                                                 | 52                         |

| 8.3.1                                                 | Command responses                                                                                                                                       | 52                         |

| 8.3.2                                                 | my-d™ move and my-d™ move NFC identification data                                                                                                       | 52                         |

| 9                                                     | Operational Characteristics                                                                                                                             | 53                         |

| 9.1                                                   | Electrical Characteristics                                                                                                                              | 53                         |

| 9.2                                                   | Absolute Maximum Ratings                                                                                                                                | 54                         |

# **List of Figures**

| Figure 1  | Pin configuration die                                                             | . 9 |

|-----------|-----------------------------------------------------------------------------------|-----|

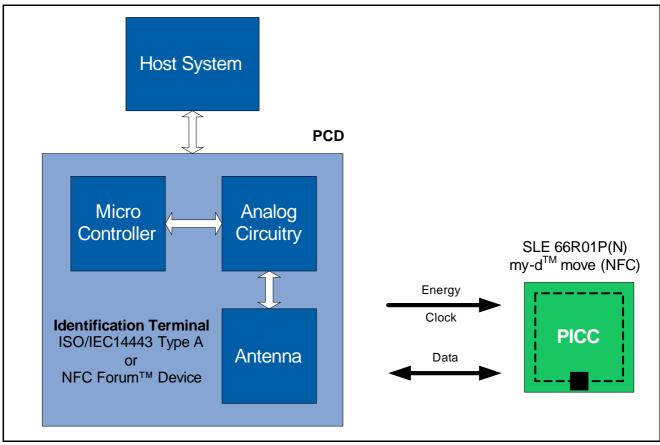

| Figure 2  | Block Diagram of the SLE 66R01P and SLE 66R01PN                                   | 12  |

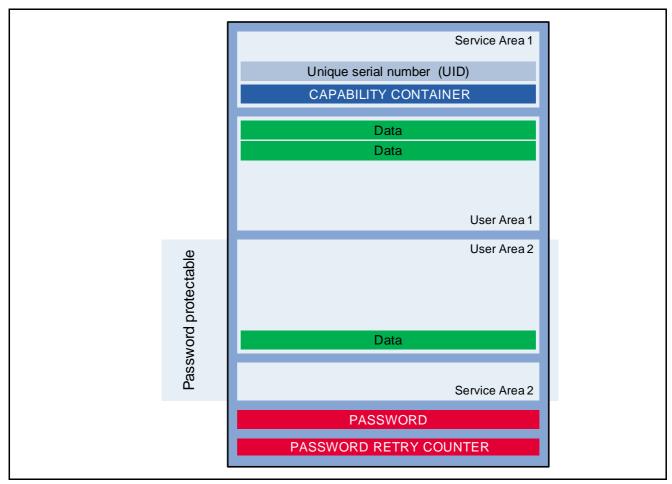

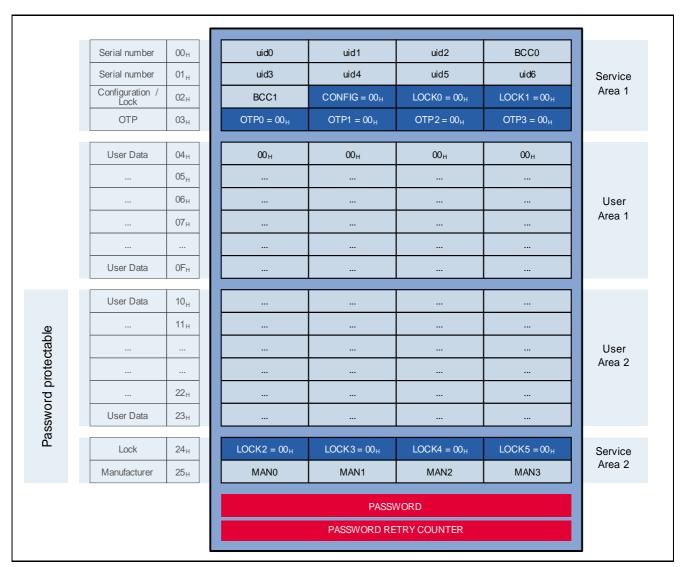

| Figure 3  | SLE 66R01P and SLE 66R01PN memory principle                                       | 13  |

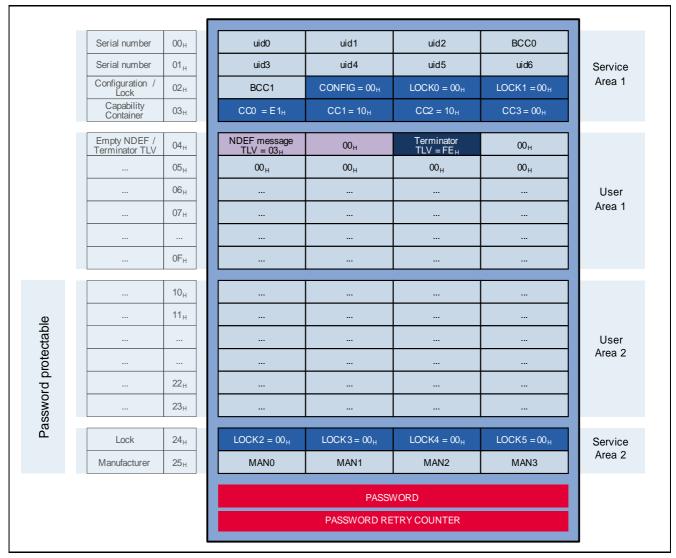

| Figure 4  | SLE 66R01P and SLE 66R01PN NFC Forum™ Type 2 Tag memory structure                 | 15  |

| Figure 5  | SLE 66R01P and SLE 66R01PN Contactless System Overview                            | 16  |

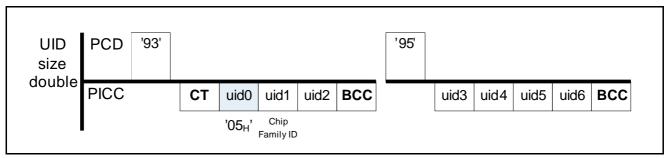

| Figure 6  | SLE 66R01P and SLE 66R01PN double-size UID                                        | 17  |

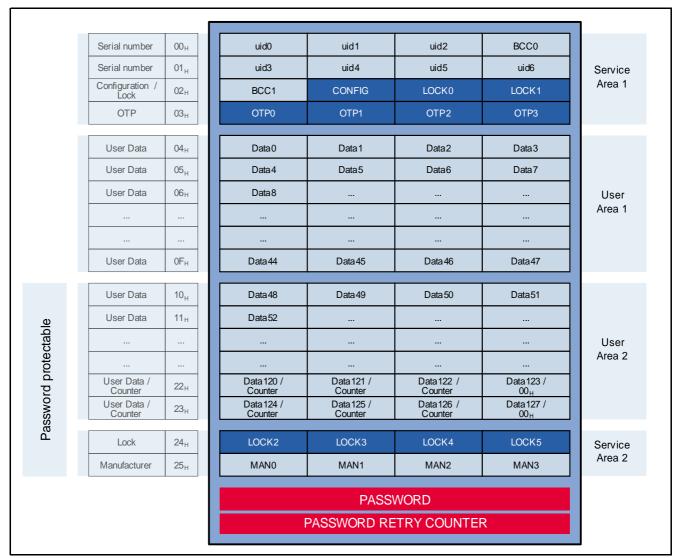

| Figure 7  | my-d™ move and my-d™ move NFC memory organization                                 | 18  |

| Figure 8  | Configuration Byte                                                                |     |

| Figure 9  | Locking and Block Locking Mechanism                                               | 21  |

| Figure 10 | Static Memory Structure                                                           | 23  |

| Figure 11 | Generic NFC Forum™ Type 2 Tag dynamic memory layout (based on SLE 66R01P(N))      | 24  |

| Figure 12 | Example of a NFC Forum™ Type 2 Tag dynamic memory layout (based on SLE 66R01P(N)) | 25  |

| Figure 13 | my-d™ move Transport Configuration                                                | 26  |

| Figure 14 | my-d™ move NFC Transport Configuration                                            | 27  |

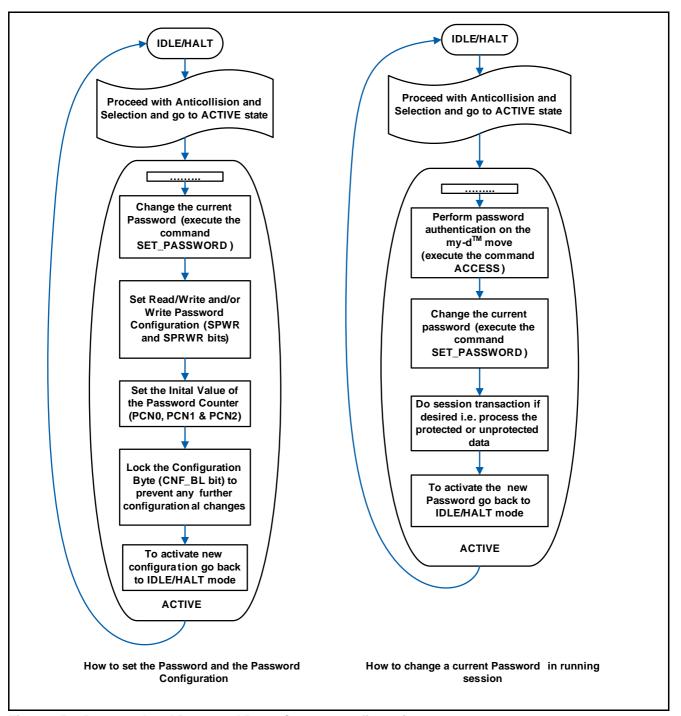

| Figure 15 | Password and Password Retry Counter configuration                                 | 30  |

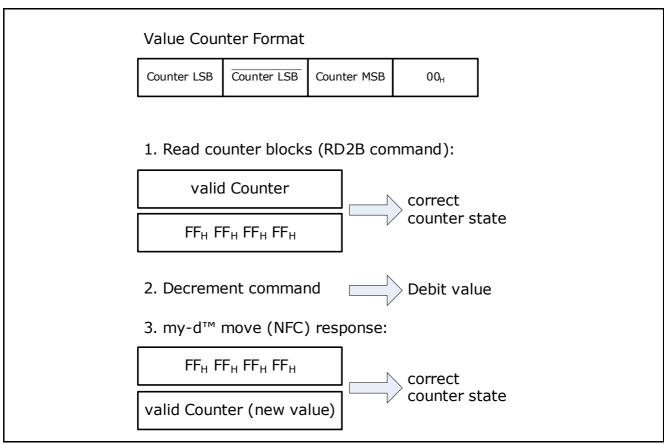

| Figure 16 | Value Counter - Principle                                                         | 32  |

| Figure 17 | Value Counter decrement example                                                   | 33  |

| Figure 18 | Start-up Sequence                                                                 | 37  |

| Figure 19 | Read 4 Blocks Command                                                             | 41  |

| Figure 20 | Write 1 Block Command                                                             | 42  |

| Figure 21 | Compatibility Write Command                                                       | 43  |

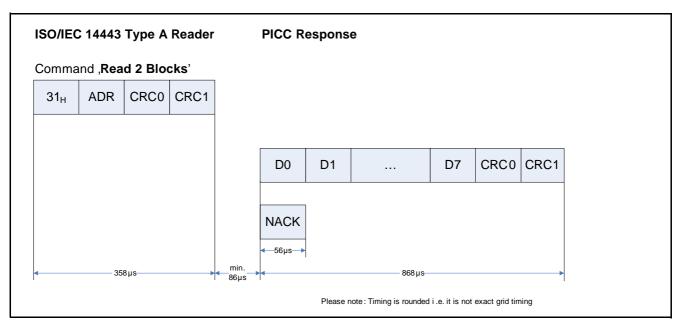

| Figure 22 | Read 2 Blocks Command                                                             | 44  |

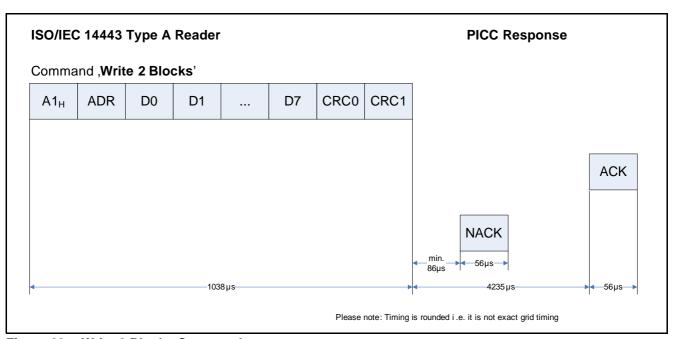

| Figure 23 | Write 2 Blocks Command                                                            | 45  |

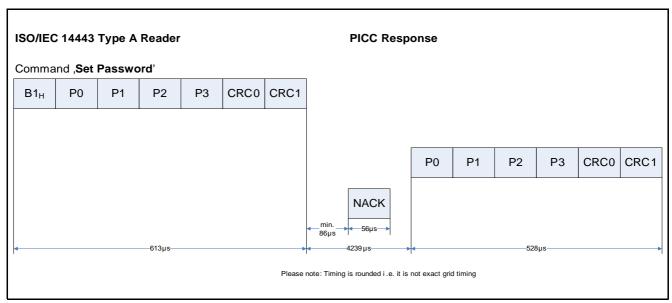

| Figure 24 | Set Password Command                                                              | 46  |

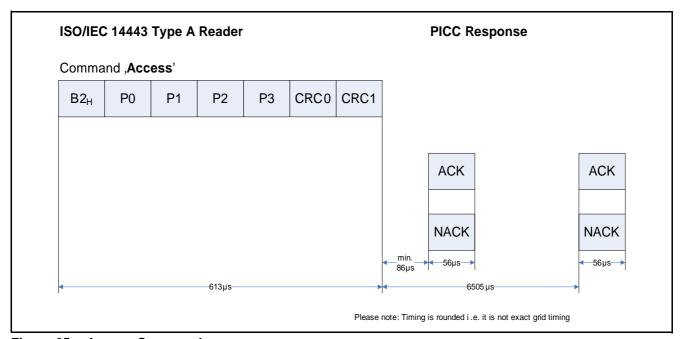

| Figure 25 | Access Command                                                                    | 47  |

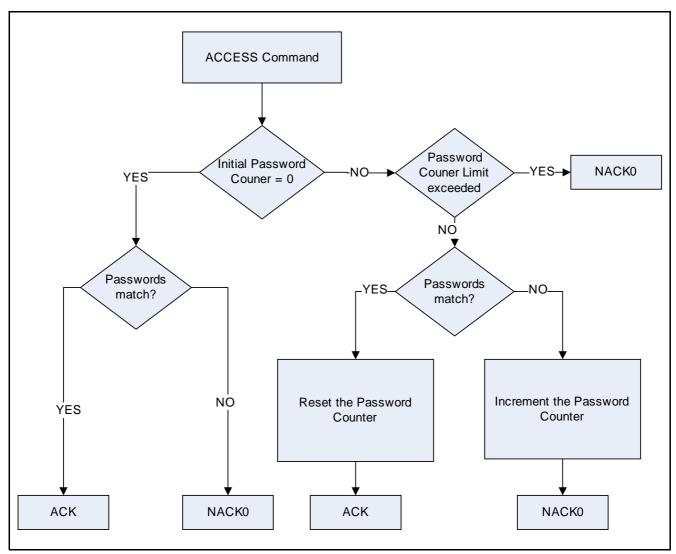

| Figure 26 | Flow Diagram of the ACS Command                                                   | 48  |

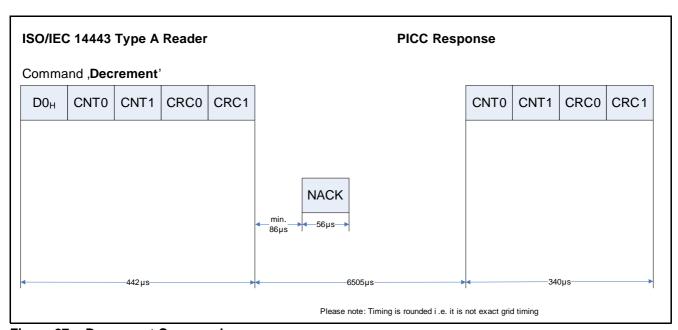

| Figure 27 | Decrement Command                                                                 | 49  |

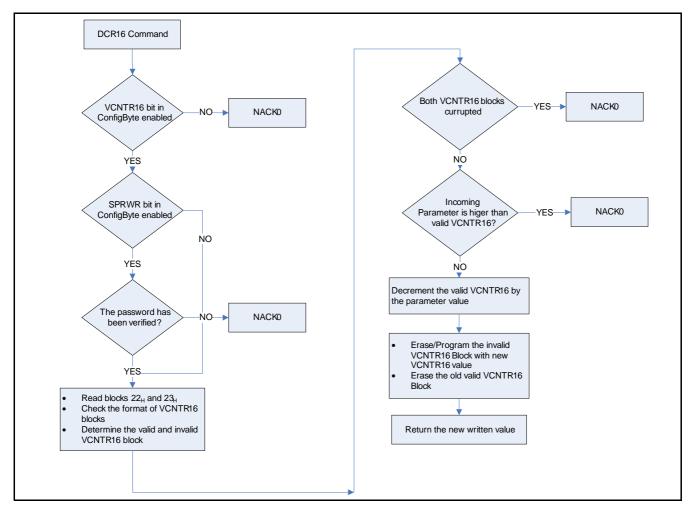

| Figure 28 | Decrement Command flow                                                            |     |

| Figure 29 | HLTA Command                                                                      | 51  |

|           |                                                                                   |     |

# **List of Tables**

| Table 1  | Ordering information                                            | 9  |

|----------|-----------------------------------------------------------------|----|

| Table 2  | Pin description and function                                    | 9  |

| Table 3  | my-d™ family product overview                                   | 11 |

| Table 4  | UID Coding                                                      | 17 |

| Table 5  | UID Description                                                 | 19 |

| Table 6  | Configuration Byte Definition                                   | 20 |

| Table 7  | Example for OTP Block Lock and Block Lock                       | 22 |

| Table 8  | Writing to OTP Block (block 03H) from the user point of view    | 22 |

| Table 9  | Capability Container settings for my-d™ move and my-d™ move NFC |    |

| Table 10 | Empty NDEF message                                              | 28 |

| Table 11 | Access Rights                                                   | 29 |

| Table 12 | Behavior in case of an Error                                    | 38 |

| Table 13 | ISO/IEC 14443-3 Type A Command Set                              | 39 |

| Table 14 | my-d™ move and my-d™ move NFC memory access command set         | 39 |

| Table 15 | Read 4 Blocks (RD4B)                                            | 41 |

| Table 16 | Write 1 Block (WR1B)                                            | 42 |

| Table 17 | Compatibility Write (CPTWR)                                     | 43 |

| Table 18 | Read 2 Block (RD2B)                                             | 44 |

| Table 19 | Write 2 Block (WR2B)                                            | 45 |

| Table 20 | Set Password (SPWD)                                             | 46 |

| Table 21 | SPWD - behaviour in error case                                  | 46 |

| Table 22 | Access (ACS)                                                    | 47 |

| Table 23 | ACS - behaviour in error case                                   | 48 |

| Table 24 | Decrement (DCR16)                                               | 49 |

| Table 25 | DCR16 - behaviour in error case                                 | 50 |

| Table 26 | Halt (HLTA)                                                     | 51 |

| Table 27 | ACK and NACK as responses                                       | 52 |

| Table 28 | Summary of SLE 66R01P and SLE 66R01PN identification data       | 52 |

| Table 29 | Electrical Characteristics                                      | 53 |

| Table 30 | Absolute Maximum Ratings                                        | 54 |

#### **Features**

Intelligent 1216 bit EEPROM with Contactless Interface compliant to ISO/IEC 14443-3 Type A and support of NFC Forum™ Type 2 Tag Operation

#### **Contactless Interface**

- Physical Interface and Anticollision compliant to ISO/IEC 14443-3 Type A

- Operation frequency 13.56 MHz

- Data rate 106 kbit/s in both direction

- Contactless transmission of data and supply energy

- Anticollision logic: several cards may be operated in the field simultaneously

- Unique IDentification number (7-byte double-size UID) according to ISO/IEC 14443-3 Type A

- · Read and Write Distance up to 10 cm and more (influenced by external circuitry i.e. reader and inlay design)

#### 152 byte EEPROM

- · Organized in 38 blocks of 4 bytes each

- 128 bytes freely programmable User Memory

- 24 bytes of Service Area reserved for UID, Configuration, LOCK Bytes, OTP Block and Manufacturer Data

- Read and Write of 128 bytes of User Memory in less than 100 ms

- Programming time per block < 4 ms</li>

- Endurance minimum 10,000 erase/write cycles<sup>1)</sup>

- Data Retention minimum 5 years<sup>1)</sup>

#### **Privacy Features**

- 32 bit of One Time Programmable (OTP) memory area

- · Locking mechanism for each block

- Block Lock mechanism

- Optional 32 bit Password for Read/Write or Write access

- Optional Password Retry Counter

- Optional 16 bit Value Counter

#### **Data Protection**

- Data Integrity supported by 16 bit CRC, parity bit, command length check

- Anti-tearing mechanism for OTP, Password Retry Counter and Value Counter

#### NFC Forum<sup>™</sup> Operation

- Compliant to NFC Forum<sup>™</sup> Type 2 Tag Operation

- Support of Static and Dynamic Memory Structure according to NFC Forum™ Type 2 Tag Operation

- SLE 66R01PN: pre-configured NFC memory with empty NDEF message (INITIALIZED state, non-reversible)

- SLE 66R01P: UNINITIALIZED state, may be configured to INITIALIZED state

#### **Electrical Characteristics**

- On-Chip capacitance 17 pF ± 5%

- ESD protection minimum 2 kV

- Ambient Temperature -25℃ ... +70℃ (for the chip)

Data Book 8 / 55 2011-11-24

<sup>1)</sup> Values are temperature dependent

Ordering and packaging information

# 1 Ordering and packaging information

Table 1 Ordering information

| Type Package                            |                          | Total Memory / User Memory <sup>1)</sup> | Ordering code |

|-----------------------------------------|--------------------------|------------------------------------------|---------------|

| SLE 66R01P C                            | wafer sawn / unsawn      |                                          | on request    |

| SLE 66R01P NB                           | NiAu Bumped (sawn wafer) | 450 / 400                                | SP000911428   |

| SLE 66R01PN C                           | wafer sawn / unsawn      | 152 / 128 bytes                          | on request    |

| SLE 66R01PN NB NiAu Bumped (sawn wafer) |                          |                                          | SP000953914   |

<sup>1)</sup> Total memory size includes the service area whereas user memory size is freely programmable for user data.

For more ordering information about the form of delivery please contact your local Infineon sales office.

# 1.1 Pin description

Figure 1 Pin configuration die

Table 2 Pin description and function

| Symbol         | Function           |

|----------------|--------------------|

| L <sub>A</sub> | Antenna Connection |

| L <sub>B</sub> | Antenna Connection |

my-d™ Product Family

# 2 my-d™ Product Family

my-d<sup>™</sup> products are available both in plain mode with open memory access and in secure mode with memory access controlled by authentication procedures. The my-d<sup>™</sup> product family provides users with different memory sizes, features NFC Forum<sup>™</sup> Type 2 Tag functionality and incorporates security features to enable considerable flexibility in the application design.

Flexible controls within the my-d<sup>™</sup> devices start with plain mode operation featuring individual page locking; for more complex applications various settings in secure mode can be set for multi user / multi application configurations.

In plain mode access to the memory is supported by both 4-byte block as well as 8-byte page structure.

In secure mode a cryptographic algorithm based on a 64-bit key is available. Mutual authentication, message authentication codes (MAC) and customized access conditions protect the memory against unauthorized access.

The functional architecture, meaning the memory organization and authentication of my-d<sup>™</sup> products is the same for both my-d<sup>™</sup> proximity (ISO/IEC 14443) and my-d<sup>™</sup> vicinity (ISO/IEC 18000-3 mode 1 or ISO/IEC 15693). This eases the system design and allows simple adaptation between applications.

Configurable Value Counters featuring anti-tearing functionality are suitable for value token applications, such as limited use transportation tickets.

Architectural interoperability of my-d™ products enables an easy migration from simple to more demanding applications.

The my-d<sup>™</sup> move family is designed for cost optimized applications and its implemented command set eases the usage in existing applications and infrastructures.

In addition, the my-d<sup>™</sup> light (ISO/IEC 18000-3 mode 1 or ISO/IEC 15693) is part of the my-d<sup>™</sup> family. Its optimized command set and memory expands the range of applications to cost sensitive segments.

# 2.1 my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC

The my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC are part of Infineon's my-d<sup>™</sup> product family and are designed to meet the requirements of the increasing NFC market demanding smart memories. They are compliant to ISO/IEC 14443-3 Type A, to ISO/IEC 18092 and to NFC Forum<sup>™</sup> Type 2 Tag Operation.

128 Bytes of memory can be arranged in static or dynamic memory structures for NFC applications.

my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC products also feature configurable Value Counters which support antitearing protection.

Privacy features like a password protection including password retry counter provide basic security to the applications.

Based on SLE 66R01P the SLE 66R01PN already contains a pre-configuration of the NFC memory indicating the INITIALIZED state according to the definition of the NFC Forum<sup>™</sup> Type 2 Tag life cycle. Due to that the my-d<sup>™</sup> move NFC is ready to be used in NFC infrastructures.

$my-d^{TM}$  move and  $my-d^{TM}$  move NFC products are suited for a broad range of applications like public transport, event ticketing or smart posters.

my-d™ Product Family

# 2.2 Application Segments

my-d™ products are optimized for personal and object identification. Please find in the following table some dedicated examples

Table 3 my-d<sup>™</sup> family product overview

| Product                                 | Application                                                                                                   |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|

| my-d™ move - SLE 66R01P                 | Public Transport, Smart Posters, NFC Device Pairing                                                           |

| my-d™ move NFC - SLE 66R01PN            | Public Transport, Smart Posters, NFC Device Pairing, NFC INITIALIZED state                                    |

| my-d™ move lean - SLE 66R01L            | Public Transport, Smart Posters, NFC Device Pairing                                                           |

| my-d™ NFC - SLE 66RxxP                  | Smart Posters and Maps, NFC Device Pairing, Loyalty Schemes, Consumer Good Information, Healthcare Monitoring |

| my-d™ proximity 2 - SLE 66RxxS          | Access Control, Entertainment, Public Transport, Customer Loyalty Schemes, Micro Payment                      |

| my-d™ proximity enhanced - SLE 55RxxE   | Access Control, Gaming, Entertainment, Customer Loyalty Schemes                                               |

| my-d™ light - SRF 55V01P                | Libraries, Laundry, Factory Automation, Media<br>Management, Event Ticketing, Leisure Park Access             |

| my-d™ vicinity plain - SRF 55VxxP       | Factory Automation, Healthcare, Ticketing, Access Control                                                     |

| my-d™ vicinity plain HC - SRF 55VxxP HC | Ticketing, Brand Protection, Loyalty Schemes, Ski passes                                                      |

| my-d™ vicinity secure - SRF 55VxxS      | Ticketing, Brand protection, Loyalty Schemes, Access Control                                                  |

Scope of my-d™ move / my-d™ move NFC

# 3 Scope of my-d<sup>™</sup> move / my-d<sup>™</sup> move NFC

The SLE 66R01P and SLE 66R01PN are part of the Infineon my-d™ product family and support Infineon's transport and ticketing strategy and are designed to meet the requirements of NFC applications.

They are compliant to ISO/IEC 14443-3 Type A, to ISO/IEC 18092 and to NFC Forum™ Type 2 Tag Operation.

# 3.1 Circuit Description

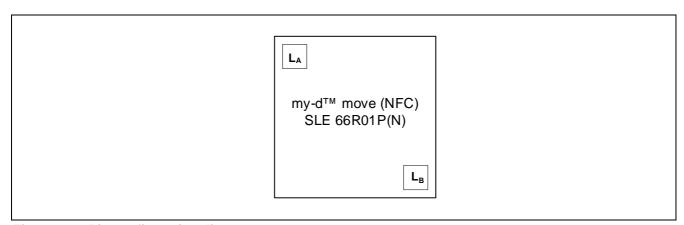

The SLE 66R01P and SLE 66R01PN are made up of an EEPROM memory unit, an analog interface for contactless operation, a data transmission path and a control unit. The following diagram shows the main blocks of the SLE 66R01P and SLE 66R01PN.

Figure 2 Block Diagram of the SLE 66R01P and SLE 66R01PN

The SLE 66R01P and SLE 66R01PN comprise the following three parts:

#### Analog Contactless Interface

The Analog Contactless Interface contains the voltage rectifier, voltage regulator and system clock to supply the IC with appropriate power. Additionally the data stream is modulated and demodulated.

### Memory Unit

The Memory Unit consists of 38 blocks of 4 bytes each.

#### Control Unit

The Control Unit decodes and executes all commands. Additionally the control unit is responsible for the correct anticollision flow.

Data Book 12 / 55 2011-11-24

Scope of my-d™ move / my-d™ move NFC

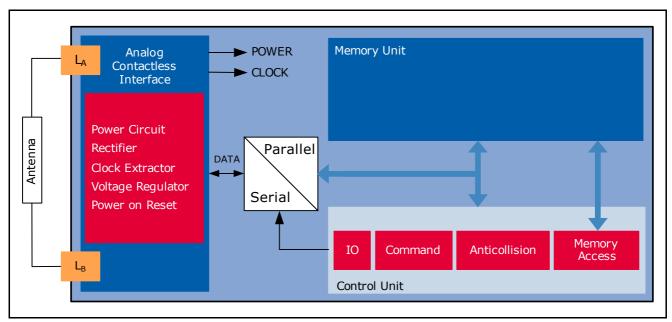

# 3.2 Memory Principle

The total amount of addressable memory is 152 bytes organized in blocks of 4 bytes each.

The general structure comprises Service Areas as well as User Areas:

- 24 bytes of service and administration data (located in Service Area 1 and 2) reserved for

- 7-byte double-size UID

- configuration data

- LOCKx bytes

- OTP memory

- Manufacturing Data

- 128 bytes of User memory (located in User Area 1 and 2) reserved for

- User Data

- Value Counter

Additionally the Password and Password Retry Counter are available and accessible via dedicated commands.

Figure 3 SLE 66R01P and SLE 66R01PN memory principle

Scope of my-d™ move / my-d™ move NFC

#### 3.2.1 Service Area 1

Service Area 1 contains

- the 7-byte UID which is programmed at manufacturing of the chip and cannot be changed

- CONFIG byte to enable the Password (incl. the Password Retry counter) and the Value Counter functionality

- LOCK0, LOCK1 bytes to enable an irreversible write-protection for the blocks located in User Area 1

- 32 bits of the One-Time-Programmable (OTP) memory block can irreversibly be programmed from 0<sub>B</sub> to 1<sub>B</sub>

#### 3.2.2 User Area 1

48 bytes (12 blocks, 4 bytes each) of memory for user data.

#### 3.2.3 User Area 2

User Area 2 contains

- 80 bytes (20 blocks, 4 bytes each) of user memory for user data. These memory blocks can be used to store user data. This portion of the memory may be protected with a 32 bit password.

- a 16-bit Value Counter may be activated providing a mechanism to store some value (points, trips, ...) on the my-d™ move and my-d™ move NFC chip.

#### 3.2.4 Service Area 2

Service Area 2 contains

- lock bytes LOCK2 to LOCK5 to enable an irreversible write-protection for the blocks loacted in User Area 2

- Manufacturing Data (programmed during manufacturing of the chip) which cannot be changed

Data Book 14 / 55 2011-11-24

Scope of my-d™ move / my-d™ move NFC

# 3.3 Memory Principle for NFC Forum™ Type 2 Tag

The memory organization is configurable according to the NFC Forum<sup>™</sup> Type 2 Tag Operation specification. Static or dynamic memory structures are supported.

**Figure 4** illustrates the principle of the SLE 66R01P and SLE 66R01PN as a NFC Forum<sup>™</sup> Type 2 Tag compatible chip. The memory can be accessed with NFC Forum<sup>™</sup> Type 2 Tag commands.

Figure 4 SLE 66R01P and SLE 66R01PN NFC Forum™ Type 2 Tag memory structure

Based on SLE 66R01P the SLE 66R01PN already contains a pre-configuration of the NFC memory indicating the INITIALIZED state according to the definition of the NFC Forum<sup>™</sup> Type 2 Tag life cycle. With this pre-configuration the my-d<sup>™</sup> move NFC can be immediately used in NFC infrastructures.

For details regarding the NFC initialization of my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC please refer the the Application Note "How to operate my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC devices in NFC Forum<sup>™</sup> Type 2 Tag infrastructures" available at Chip Card & Security security.chipcard.ics@infineon.com.

Attention: The pre-configuration of SLE 66R01PN is nonreversible and the my-d<sup>™</sup> move NFC cannot be overwritten and used as plain, standard my-d<sup>™</sup> move anymore.

Data Book 15 / 55 2011-11-24

Scope of my-d™ move / my-d™ move NFC

# 3.4 System Overview

The system consists of a host system, one or more SLE 66R01P / SLE 66R01PN tags or other ISO/IEC 14443-3 Type A compliant cards and an ISO/IEC 14443-3 Type A compatible contactless reader.

Alternatively, since the SLE 66R01P and SLE 66R01PN can be used in NFC Forum<sup>™</sup> Type 2 Tag memory structures, a NFC Forum<sup>™</sup> device in card reader/writer mode can be used to operate the chip.

Figure 5 SLE 66R01P and SLE 66R01PN Contactless System Overview

Scope of my-d™ move / my-d™ move NFC

# 3.5 UID Coding

To identify a SLE 66R01P and SLE 66R01PN chip the manufacturer code and a chip family identifier are coded into the UID as described in the **Table 4**. The chip family identifier can be used to determine the basic command set for the chip.

Figure 6 SLE 66R01P and SLE 66R01PN double-size UID

#### Table 4 UID Coding

| UID Field | Value           | Description                                                                                                                  |

|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------|

| uid0      | 05 <sub>H</sub> | IC Manufacturer Code according to ISO/IEC 7816-6                                                                             |

| uid1      | 3x <sub>H</sub> | Chip Family Identifier Higher Nibble: 0011 <sub>B</sub> : my-d™ move and my-d™ move NFC Lower Nibble: part of the UID number |

# 3.6 Supported Standards

the SLE 66R01P and SLE 66R01PN support the following standards:

- ISO/IEC 14443 Type A (Parts 1, 2 and 3) tested according to ISO/IEC 10373-6 (PICC Test & Validation)

- ISO/IEC 14443-3 Type A

- NFC Forum<sup>™</sup> Type 2 Tag Operation

#### 3.7 Command Set

The SLE 66R01P and SLE 66R01PN is compliant to the ISO/IEC 14443-3 Type A standard.

A set of standard ISO/IEC 14443-3 Type A commands is implemented to operate the chip.

Additionally NFC Forum<sup>™</sup> Type 2 Tag commands and a my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC specific command set is implemented. This facilitates the access to the on-chip integrated memory and supports the execution of password and counter functionality.

**Memory Organization**

# 4 Memory Organization

The total amount of user memory is 152 byte. It is organized in blocks of 4 bytes each.

It comprises:

- 128 bytes for user data

- 24 bytes for UID, OTP, locking information, IC configuration and manufacturer information.

Additionally the Password and Password Retry Counter are allocated in non-addresable part of the memory and are accessible via dedicated commands only.

Figure 7 shows the memory structure of the SLE 66R01P and SLE 66R01PN chip.

Figure 7 my-d™ move and my-d™ move NFC memory organization

### 4.1 User Memory Area 1 and 2

Blocks from address  $04_H$  to  $23_H$  belong to the User Memory Area (1 and 2). This part of the memory is readable / writable as well as lockable against unintentional overwriting using a locking mechanism.

Moreover the User Memory Area 2 above the address 10<sub>H</sub> can be protected with a Password against unintentional reading or reading/writing.

**Memory Organization**

#### 4.2 Service Area 1 and 2

The Service Area 1 (block address 00<sub>H</sub> to 03<sub>H</sub>) contains

- 7-byte double-size UID (plus two bytes of UID BCC information)

- Configuration Byte

- LOCK0 and LOCK1 to lock the OTP block and blocks in User Area 1

- 32 bit OTP memory

The Service Area 2 (block address 24<sub>H</sub> to 25<sub>H</sub>) contains

- LOCK2 LOCK5 to lock blocks in User Area 2

- Manufacturer Data

### 4.2.1 Unique Identifier (UID)

The 9 bytes of the UID (7 byte UID + 2 bytes BCC information) are allocated in Block  $00_H$ , Block  $01_H$  and Byte 1 of Block  $02_H$  of the my-d<sup>TM</sup> move and my-d<sup>TM</sup> move NFC memory. All bytes are programmed and locked during the manufacturing process. These bytes cannot be changed.

For the content of the UID the following definitions apply:

SLE 66R01P and SLE 66R01PN support Cascade Level 2 UID according to the ISO/IEC 14443-3 Type A

which is a 7 byte unique number

The table below describes the content of the UID including the BCC information.

#### Table 5 UID Description

| Cascade Level 2 - double-size UID |                  |                    |                    |      |                    |      |      |      |      |                    |

|-----------------------------------|------------------|--------------------|--------------------|------|--------------------|------|------|------|------|--------------------|

| UID Byte                          | CT <sup>1)</sup> | uid0 <sup>2)</sup> | uid1 <sup>3)</sup> | uid2 | BCC0 <sup>4)</sup> | uid3 | uid4 | uid5 | uid6 | BCC1 <sup>4)</sup> |

CT is the Cascade Tag and designates CL2. It has a value of 88<sub>H</sub>. Please note that CT is hardwired and not stored in the memory.

- 2) uid0 is the Manufacturer Code: 05<sub>H</sub> according to ISO/IEC 7816-6

- uid1 is the Chip Family Identifier.

The higher significant nibble identifies a my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC chip (0011<sub>B</sub>).

The lower significant nibble of uid1 is part of the serial number.

- 4) BCCx are the UID CLn checkbytes calculated as Exclusive-OR over the four previous bytes (as described in ISO/IEC 14443-3 Type A). BCCx is stored in the memory and read-out during the anti-collision.

**Memory Organization**

# 4.2.2 Configuration Byte

The Configuration Byte defines the configurable functionality of the my-d<sup>TM</sup> move and my-d<sup>TM</sup> move NFC. It is allocated in Byte 1 of Block  $02_H$ . At delivery all bits of the Configuration Byte are set to  $0_B$ . Note that the Configuration Byte is One Time Programmable (OTP) byte. Bits allocated in this byte can only be logically set to  $1_B$ , which is an irreversible process i.e. bits can not be reset to  $0_B$  afterwards.

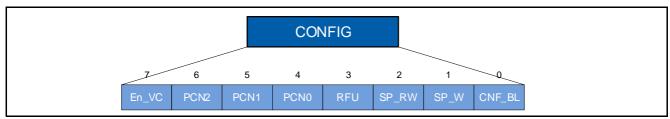

Figure 8 Configuration Byte

Table 6 Configuration Byte Definition

| Configuration Bit                           | Abbreviation         | Description                                                                                                                                                                                                                               |

|---------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration Byte Lock                     | CNF_BL               | 0 <sub>B</sub> Configuration Byte programmable 1 <sub>B</sub> Configuration Byte locked                                                                                                                                                   |

| Set Password for Write access               | SP-W                 | 0 <sub>B</sub> The Write Password is not active<br>1 <sub>B</sub> The Write Password is active for Write<br>Commands which are applied to all blocks starting<br>from the address 10 <sub>H</sub>                                         |

| Set Password for Read and Write access      | SP_WR                | $0_{\rm B}$ The Read and Write Password is not active $1_{\rm B}$ The Read and Write Password is active for read, write and decrement commands for all blocks above address $0F_{\rm H}$                                                  |

| RFU                                         | RFU                  | Reserved for the future use                                                                                                                                                                                                               |

| Initial value of the Password Retry Counter | PCN2<br>PCN1<br>PCN0 | $000_{\rm B}$ Default setting $111_{\rm B}$ Maximal initial value ( $7_{\rm D}$ ) Password Retry Counter is only active if the initial value is different than $0_{\rm D}$ .                                                              |

| 16-bit Value Counter                        | En_VC                | 0 <sub>B</sub> Value Counter is not configured, blocks 22 <sub>H</sub> and 23 <sub>H</sub> are User Data blocks 1 <sub>B</sub> Value Counter is set, blocks 22 <sub>H</sub> and 23 <sub>H</sub> are reserved for the 16-bit Value Counter |

Note: The CNF\_BL bit is active immediately active after writing. To activate the new configuration of SP-W, SP-WR and VCRN16 bits the execution of REQA or WUPA commands is required. The new value of the Password Retry Counter (PCN2, PCN1 and PCN0 bits) is active immediately, i.e. is read each time the information is required (during the execution of the Access command).

### 4.2.2.1 Locking Mechanism for the Configuration Byte

The my-d<sup>TM</sup> move and my-d<sup>TM</sup> move NFC is delivered with all bits of Configuration Byte set to 0<sub>B</sub>. The issuer should define the functionality of a chip as required (set e.g. Write and/or Read/Write Password, the Password Retry Counter, the 16-bit Value Counter etc.) and lock the Configuration Byte. Once the Configuration Byte is locked no further changes to the Configuration Byte are possible.

Note: If all three BL Bits in the LOCK0 Byte are set to  $1_B$ , block  $02_H$  is locked. It is then not possible to change the value of this particular block  $(02_H)$  any more.

**Memory Organization**

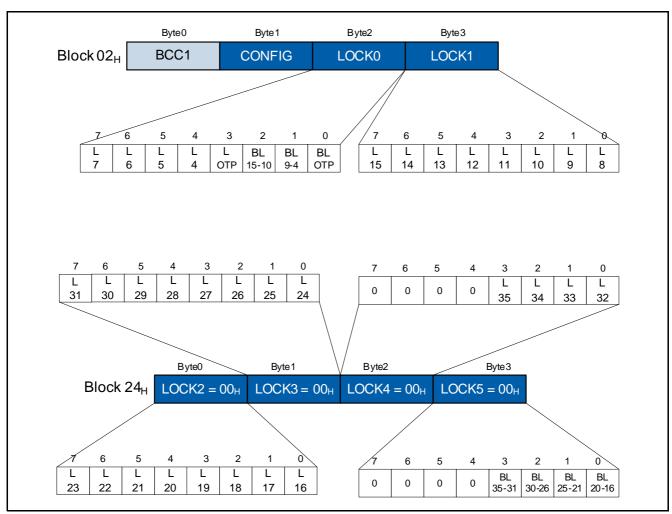

# 4.2.3 Locking mechanism

Bytes LOCK0, LOCK1 allocated in Block  $02_{\rm H}$  and LOCK2, LOCK3, LOCK4 and LOCK5 allocated in Block  $24_{\rm H}$  represent the one time field programmable bits which are used to lock the blocks in the specified address range from block  $03_{\rm H}$  (OTP Block) to  $23_{\rm H}$ .

Each block in this range can be individually locked to prevent further write access. A locking mechanism of each block is irreversible, i.e. once the locking information of a particular block (Lx) is set to  $1_B$  it can not be reset back to  $0_B$  any more. Figure 9 illustrates the locking bytes with the corresponding locking bits.

Furthermore, it is possible to freeze the locking information of some memory areas by setting Block Locking (BL) bits e.g. if the bit BL 15-10 is set to  $1_B$  then the locking information for the corresponding area (L10 to L15) is not changeable any more. See the example in the **Table 7** below.

Figure 9 Locking and Block Locking Mechanism

The Write One Block (WR1B) command should be used to set the locking or block locking information of a certain block.

If WR1B is applied to Block 02<sub>H</sub> then:

- the Byte 0 (BCC1) will not be changed

- the Byte 1 (Configuration Byte) will be changed only if it is not locked

If WR1B is applied to Block 24<sub>H</sub> then:

- the Byte2 [7..4] = Lock4[7..4] and

- the Byte3 [7..4] = Lock5[7..4] will not be changed neither.

Data Book 21 / 55 2011-11-24

**Memory Organization**

The locking and block locking for a certain block is active immediately after writing. That means that it is not necessary to execute the REQA or WUPA command in order to activate the locking.

Note: If all three BL bits in the LOCK0 byte are set to 1<sub>B</sub> then Block 02<sub>H</sub> is locked. It is not possible to change the locking bits of this block any more. The same applies for block 24<sub>H</sub>. If BL bits of the LOCK5 byte are set to 1<sub>B</sub> then this block is locked. In this case the SLE 66R01P and SLE 66R01PN responds with NACK to a corresponding Write command.

Table 7 Example for OTP Block Lock and Block Lock

| BL OTP         | L OTP          | OTP BLOCK STATE                                    |

|----------------|----------------|----------------------------------------------------|

| 0 <sub>B</sub> | 0 <sub>B</sub> | OTP Block Unlocked                                 |

| 0 <sub>B</sub> | 1 <sub>B</sub> | OTP Block Locked                                   |

| 1 <sub>B</sub> | 0 <sub>B</sub> | OTP Block Unlocked and can not be locked ever more |

| 1 <sub>B</sub> | 1 <sub>B</sub> | OTP Block Locked                                   |

An Anti-Tearing mechanism is implemented for Lock bytes on the SLE 66R01P and SLE 66R01PN. This mechanism prevents a stored value to be lost in case of a tearing event. This increases the level of data integrity and it is transparent to the customer.

### 4.2.4 OTP Block

The Block  $03_{H}$  is a One Time Programmable (OTP) Block. Bits allocated in this block can only be logically set to  $1_{B}$ , which is an irreversible process i.e. bits can not be reset to  $0_{B}$  afterwards.

The Write One Block (WR1B) command should be used to program a specific OTP value. Incoming data of the WR1B command are bit-wise OR-ed with the current content of the OTP Block and the result is written back to the OTP Block.

Table 8 Writing to OTP Block (block 03<sub>H</sub>) from the user point of view

| OTP Block                     | Representation bit-wise                              | Description                                                  |

|-------------------------------|------------------------------------------------------|--------------------------------------------------------------|

| Initial value                 | 0000 0000 0000 0000 0000 0000 0000 0000 <sub>B</sub> | Production setting                                           |

| Write [55550003] <sub>H</sub> | 0101 0101 0101 0101 0000 0000 0000 0011 <sub>B</sub> | Bit-wise "OR" with previous content of block 03 <sub>H</sub> |

| Write [AA55001C] <sub>H</sub> | 1111 1111 0101 0101 0000 0000 0001 1111 <sub>B</sub> | Bit-wise "OR" with previous content of block 03 <sub>H</sub> |

An Anti-Tearing mechanism is implemented for the OTP Block on the my-d™ move and my-d™ move NFC. This mechanism prevents the stored value to be lost in case of a tearing event. This increases the level of data integrity and is transparent to the customer.

### 4.2.5 Manufacturer Block (25<sub>H</sub>)

The Manufacturer Block is used to store the my-d™ move and my-d™ move NFC internal on-chip configuration data and the manufacturing data such as Week and Year of production, Lot and Wafer Counter etc. This block is programmed and locked at manufacturing.

**Memory Organization**

# 4.3 Memory Principle for NFC Forum™ Type 2 Tag

This section desribes how to map the my-d™ move and my-d™ move NFC memory into the memory structures defined in the NFC Forum™ Type 2 Tag technical specification. This enables the usage of the my-d™ move and my-d™ move NFC as a NFC Forum™ Type 2 Tag compatible chip.

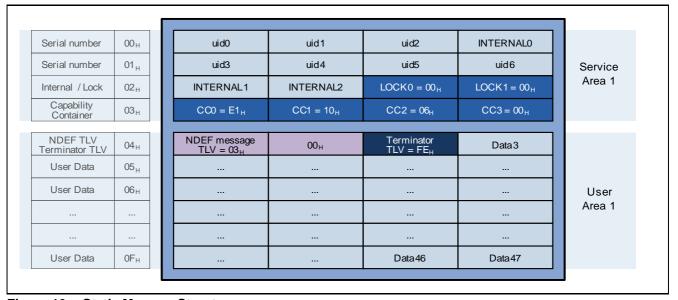

### 4.3.1 NFC Forum™ Static Memory Structure

The Static Memory Structure is applied to a NFC Forum<sup>TM</sup> Type 2 Tag with a memory size equal to 64 bytes (see Figure 10). Blocks  $04_H$  to  $0F_H$  are available to store user data.

Figure 10 Static Memory Structure

The Static Memory Structure is characterized by the NDEF message TLV  $(03_H)$  starting at block address  $04_H$ . The NFC data shown in **Figure 10** is an empty NDEF message (see **Table 10**).

**Memory Organization**

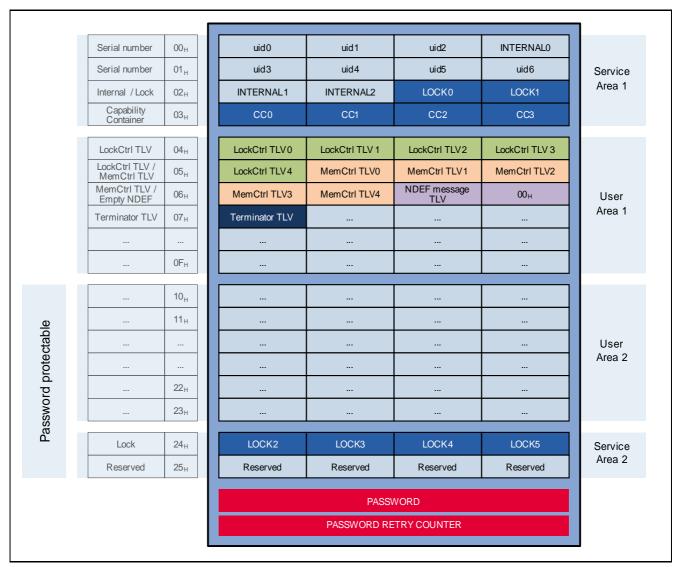

# 4.3.2 NFC Forum™ Dynamic Memory Structure

The Dynamic Memory Structure can be applied to NFC Forum<sup>TM</sup> Type 2 Tags with bigger memories than 64 bytes. **Figure 11** shows a generic memory layout with a Dynamic Memory Structure (based on the my- $d^{TM}$  move NFC chip).

Figure 11 Generic NFC Forum™ Type 2 Tag dynamic memory layout (based on SLE 66R01P(N))

Compared to the Static Memory Structure the Dynamic Memory Structure is characterized by the NDEF message TLV starting after the Lock Control TLV and Memory Control TLV (the Lock Control TLV starts at Block 04<sub>H</sub>).

Within a Dynamic Memory Structure dynamic lock bytes and reserved bytes might be located at any address in the data area (see LOCK2 - LOCK5, Reserved shown in **Figure 11**). The location and the number of bytes used for these purposes is defined by the settings of the Lock Control TLV respectively Memory Control TLV.

Following example for a Dynamic Memory Structure (shown in Figure 12) focusses on my- $d^{TM}$  move and my- $d^{TM}$  move NFC.

**Memory Organization**

|                      |                               | 1               |                                            |                                                        |                                                        |                                                        |                |

|----------------------|-------------------------------|-----------------|--------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|----------------|

|                      | Serial number                 | 00н             | uid0                                       | uid1                                                   | uid2                                                   | INTERNAL0                                              |                |

|                      | Serial number                 | 01 <sub>H</sub> | uid3                                       | uid4                                                   | uid5                                                   | uid6                                                   | Service        |

|                      | Internal / Lock               | 02 <sub>H</sub> | INTERNAL1                                  | INTERNAL2                                              | LOCK0 = 00 <sub>H</sub>                                | LOCK1 = 00 <sub>H</sub>                                | Area 1         |

|                      | Capability<br>Container       | 03н             | CC0 = E1 <sub>H</sub>                      | CC1 = 10 <sub>H</sub>                                  | CC2 = 10 <sub>H</sub>                                  | CC3 = 00 <sub>H</sub>                                  |                |

|                      | LockCtrl TLV                  | 04 <sub>H</sub> | LockCtrl                                   | LockCtrl                                               | LockCtrl                                               | LockCtrl                                               |                |

|                      | LockCtrl TLV /<br>MemCtrl TLV | 05 <sub>H</sub> | $TLV0 = 01_{H}$ $LockCtrl$ $TLV4 = 24_{H}$ | TLV1 = 03 <sub>H</sub> MemCtrl  TLV0 = 02 <sub>H</sub> | TLV2 = 90 <sub>H</sub> MemCtrl  TLV1 = 03 <sub>H</sub> | TLV3 = 14 <sub>H</sub> MemCtrl  TLV2 = 93 <sub>H</sub> |                |

|                      | MemCtrl TLV /<br>Empty NDEF   | 06 <sub>H</sub> | MemCtrl<br>TLV3 = 05 <sub>H</sub>          | MemCtrl<br>TLV4 = 04 <sub>H</sub>                      | NDEF message<br>TLV = 03 <sub>H</sub>                  | 00 <sub>H</sub>                                        | User           |

|                      | Terminator TLV                | 07 <sub>H</sub> | Terminator<br>TLV = FE <sub>H</sub>        |                                                        |                                                        |                                                        | Area 1         |

|                      |                               |                 |                                            |                                                        |                                                        |                                                        |                |

|                      |                               | 0F <sub>H</sub> |                                            |                                                        |                                                        |                                                        |                |

|                      |                               | 10 <sub>H</sub> |                                            |                                                        |                                                        |                                                        |                |

|                      |                               | 10 <sub>H</sub> |                                            |                                                        |                                                        |                                                        |                |

| able                 |                               |                 | ***                                        |                                                        |                                                        |                                                        |                |

| tecta                |                               |                 |                                            |                                                        |                                                        |                                                        | User<br>Area 2 |

| pro                  |                               |                 |                                            |                                                        |                                                        |                                                        |                |

| ord                  |                               | 22 <sub>H</sub> |                                            |                                                        |                                                        |                                                        |                |

| Password protectable |                               | 23 <sub>H</sub> |                                            |                                                        |                                                        |                                                        |                |

| <u>Q</u>             | Lock /<br>Reserved            | 24 <sub>H</sub> | LOCK2                                      | LOCK3                                                  | LOCK4                                                  | Reserved0                                              | Service        |

|                      | Reserved                      | 25н             | Reserved1                                  | Reserved2                                              | Reserved3                                              | Reserved4                                              | Area 2         |

|                      |                               |                 |                                            | PASSI                                                  | WORD                                                   |                                                        |                |

|                      |                               |                 |                                            | PASSWORD RE                                            | TRY COUNTER                                            |                                                        |                |

Figure 12 Example of a NFC Forum™ Type 2 Tag dynamic memory layout (based on SLE 66R01P(N))

If a NFC Forum™ Type 2 Tag compliant chip with Lock Control TLV and Memory Control TLV is required, NFC Forum™ Type 2 Tag specific data such as Capability Container, Lock Control TLV, Memory Control TLV, NDEF Message and Terminator TLV should be written to the memory according to the given hardware configuration.

**Figure 12** holds valid Lock Control TLV and the Memory Control TLV settings within a Dynamic Memory Structure specially suited for the my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC devices. For my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC the position of the static and dynamic lock bytes is hard-wired and it is not possible to change their position in the memory.

- Static lock bytes LOCK0 and LOCK1 are allocated in block 2, bytes 2 and 3. LOCK0 and LOCK1 are used to lock blocks from address 00<sub>H</sub> to 0F<sub>H</sub>.

- Dynamic lock bytes LOCK2 to LOCK5 are allocated in block 24<sub>H</sub>. These LOCKx bytes are used to lock blocks starting from address 10<sub>H</sub>. The position and the number of dynamic lock bits is coded into the Lock Control TLV as shown above. In this example 20 lock bits are required to lock the User Memory blocks 10<sub>H</sub> to 23<sub>H</sub>. Furthermore the Memory Control TLV defines the location and number of reserved bytes in the memory.

**Memory Organization**

# 4.4 Transport Configuration

**Figure 11** shows the memory principle of SLE 66R01P and SLE 66R01PN. Following sections provide details about the initial memory content of these devices.

### 4.4.1 Transport Configuration my-d™ move

The transport configuration of SLE 66R01P contains following information:

Figure 13 my-d™ move Transport Configuration

- Service Area 1 contains

- predefined UID (incl. BCC bytes); read-only

- CONFIG, LOCK0, LOCK1 set to 00<sub>H</sub>

- LOCK0, LOCK1 set to 00<sub>H</sub>

- OTP0 OTP3 set to 00<sub>H</sub>

- User Area 1

- all Data bytes set to 00<sub>H</sub>

- User Area 2

- all Data bytes set to 00<sub>H</sub>

- Service Area 2 contains

**Memory Organization**

- LOCK2 LOCK5 set to 00<sub>H</sub>

- Manufacturer Data; read-only

- Password set to  $00_{H}$   $00_{H}$   $00_{H}$   $00_{H}$

- Password Retry Counter

- deactivated by the setting of the CONFIG byte

The SLE 66R01P may be configured to INITIALIZED state according to the definition to the NFC Forum™ Type 2 Tag life cycle by writing

- Capability Container bytes (see Table 9) to Block 03<sub>H</sub>

- empty NDEF message TLV incl. Terminator TLV (see Table 10) to Block 04<sub>H</sub>

#### Transport Configuration my-d™ move NFC 4.4.2

SLE 66R01PN is delivered in INITIALIZED state (life cycle) according to the NFC Forum™ Type 2 Tag specification.

my-d™ move NFC Transport Configuration Figure 14

- Service Area 1 contains

- predefined UID, read-only

- CONFIG, LOCK0 and LOCK1 set to 00<sub>H</sub>

Data Book 27 / 55 2011-11-24

**Memory Organization**

- OTP0 OTP3 contains the CAPABILITY CONTAINER (see Table 9)

- User Area 1:

- contains empty NDEF message TLV including Terminator TLV (= FE<sub>H</sub>) as indicated in Table 10

- all other data bytes set to 00<sub>H</sub>

- User Area 2

- all data bytes set to 00<sub>H</sub>

- · Service Area 2 contains

- LOCK2 LOCK5 set to 00<sub>H</sub>

- Manufacturer Data; read-only

- Password set to 00<sub>H</sub> 00<sub>H</sub> 00<sub>H</sub> 00<sub>H</sub>

- · Password Retry Counter

- deactivated by the setting of the CONFIG byte

Table 9 Capability Container settings for my-d™ move and my-d™ move NFC

| Chip Type   | CC0             | CC1 <sup>1)</sup>                                                   | CC2 <sup>2)</sup> | CC3             |

|-------------|-----------------|---------------------------------------------------------------------|-------------------|-----------------|

| SLE 66R01PN | E1 <sub>H</sub> | 10 <sub>H</sub><br>(may be changed to<br>11 <sub>H</sub> if needed) | 10 <sub>H</sub>   | 00 <sub>H</sub> |

<sup>1)</sup> my-d™ move and my-d™ move NFC also support Version 1.1 of the NFC Forum™ Type 2 Tag specification.

**Table 10** defines the empty NDEF Message TLV (identified with the Tag field value of  $03_{\rm H}$ ). The Length field value is set to  $00_{\rm H}$ ; due to that the Value field is not present.

The Terminator TLV (FE<sub>H</sub>) is the last TLV block in the data area.

Table 10 Empty NDEF message

| NDEF Message TL | V               |             | Terminator TLV  |              |             |

|-----------------|-----------------|-------------|-----------------|--------------|-------------|

| Tag field       | Length field    | Value field | Tag Field       | Length field | Value field |

| 03 <sub>H</sub> | 00 <sub>H</sub> | -           | FE <sub>H</sub> | -            | -           |

Note: The pre-configuration of SLE 66R01PN is nonreversible and the my- $d^{TM}$  move NFC cannot be overwritten and used as plain, standard my- $d^{TM}$  move anymore.

<sup>2)</sup> CC2 indicates the memory size of the data area of the Type 2 Tag; the given values represent the maximum values for the chips

**Password**

### 5 Password

An issuer can protect the blocks above address 0F<sub>H</sub> with a 32 bit Write and/or Read/Write Password by enabling the password functionality.

The issuer can enable the password functionality by setting the Bit 1 (SP-W) of the Configuration Byte<sup>1)</sup> for Write Password access and/or bit 2 (SP-WR) of the Configuration Byte for Read/Write Password access (see Chapter 4.2.2).

The new configuration is activated after the next transition to IDLE/HALT state is executed.

The my-d<sup>TM</sup> move and my-d<sup>TM</sup> move NFC is delivered without Password protection i.e. default value of the SP-W and SP-WR bits is  $0_B$ .

Table 11 Access Rights

| SP-WR          | SP-W           | Access Right                               |

|----------------|----------------|--------------------------------------------|

| 0 <sub>B</sub> | O <sub>B</sub> | Read Plain / Write Plain (default setting) |

| 0 <sub>B</sub> | 1 <sub>B</sub> | Read Plain / Write Protected               |

| 1 <sub>B</sub> | X <sub>B</sub> | Read Protected / Write Protected           |

There is only one 32-bit Password value for both read and/or read/write access.

### 5.1 Password Block

The Password Block holds 32 bit of Password data and is stored in a memory location which is accessible with dedicated commands only. The initial value of the Password Block is  $00_{\rm H}$   $00_{\rm H}$   $00_{\rm H}$   $00_{\rm H}$  and should be changed after delivery. The Set Password SPWD<sup>2)</sup> command is used to change the content of the Password Block.

- If the my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC is not configured for a password protection i.e. bits for SP-W or SP-WR are not set, the Password Block will be overwritten with new Password data.

- If the my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC is configured for password protection i.e. if SP-W and/or SP-WR bits are set, the Password Block will be overwritten with new Password data only after the chip has been successfully verified with the Access ACS<sup>3)</sup> command.

### 5.2 Password Retry Counter

A Password Retry Counter counts the number of incorrect accesses to a password protected my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC. The number of incorrect accesses can be predefined by setting the bits [6:4] of the Configuration Byte. This number is called the initial value of the Password Retry Counter.

The Password Retry Counter is active if the number of incorrect accesses is higher than  $0_D$  i.e. bit[6:4] of the Configuration Byte are NOT all set to zero. The Write One Block (WR1B) command should be used to overwrite the Password Retry Counter value. The Initial value of the Password Retry Counter is active immediately after it is written.

To prevent any further changes on a predefined Password Retry Counter value it is recommended to lock the Configuration Byte. Once the Configuration Byte is locked, the status of an initial counter value is locked, i.e. are no further changes to these bits are possible.

The my-d<sup>TM</sup> move and my-d<sup>TM</sup> move NFC is delivered with a disabled Password Retry Counter i.e. the Initial value of the Password Retry Counter is equal to  $000_b$ . The maximum value of the Password Retry Counter is  $7_D$ , and valid values which activate the usage of the Password Retry Counter are in the range from  $1_D$  to  $7_D$ .

<sup>1)</sup> For more information about Configuration Byte see Section 4.2.2.

<sup>2)</sup> For more information about SPWD command see Section 8.2.6

<sup>3)</sup> For more information about ACS command see Section 8.2.7

**Password**

Figure 15 shows how to configure the Password functionality on the my-d™ move and my-d™ move NFC.

Figure 15 Password and Password Retry Counter configuration

**Password**

# 5.3 Anti-tearing Mechanism for Password Retry Counter

The Password Retry Counter block is stored in the non-directly accessible part of the memory and for data protection reasons stored redundantly (anti-tearing). This mechanism prevents a stored value of being lost in case of a tearing event. This increases the level of data integrity and is transparent to the customer.

During the execution of the Access command the my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC performs the following actions:

- compares the incoming Password and the Password stored in the my-d™ move and my-d™ move NFC

- Pass Retry Counter enabled:

- resets the Password Retry Counter if the password matches. The my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC responds with an ACK

- increments the Password Retry Counter if the passwords do not match and if the Password Counter has not reached the highest possible value and my-d™ move and my-d™ move NFC responds with a NACK

- if the Password Retry Counter has already reached the highest possible value (Initial Password Retry Counter value), then no further increase is done. The my-d™ move and my-d™ move NFC responds with a NACK.

Depending on the setting of the access bits the access to the memory above block 0F<sub>H</sub> is granted:

$SP-W = 1_B$ : read access only, no write access

$SP-RW = 1_B$ : no read and no write access

**16-bit Value Counter Functionality**

# 6 16-bit Value Counter Functionality

The Value Counter is a 16-bit value, which provides a mechanism to store some value (points, money...) on a my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC chip. Normally it is only possible to decrement this value, however if certain conditions are met it is also possible to reload the counter to an arbitrary 16-bit value. The availability of the Value Counter in the my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC is configurable by setting the bit 7 of the Configuration Byte.

### 6.1 Value Counter Format

If configured two 4-byte blocks,  $22_H$  and  $23_H$ , are reserved for the storage of the Value Counter value. The my-d<sup>TM</sup> move and my-d<sup>TM</sup> move NFC supports the detection of an interrupted or corrupted (teared) counter programming operation of the Value Counter. For the purpose the concept of **redundant saving** of the Value Counter as well as **temporarily double saving** of the Value Counter value during the programming process is implemented.

The redundant saving means, that the Value Counter is represented in the dedicated block by a 3-byte value: Counter LSB, inverted Counter LSB and Counter MSB. The fourth byte of the block is not used for the counter and carries 00<sub>H</sub> data. Counter LSB carries the lower value and Counter MSB carries the higher value of the Value Counter in hexadecimal representation.

Figure 16 Value Counter - Principle

#### **16-bit Value Counter Functionality**

For an example: the value  $1000_D = 03E8_H$  -> Value Counter LS Byte =  $E8_H$  and Value Counter MS Byte =  $E8_H$  and Val

The temporarily double saving means that Value Counter is stored twice in two different memory blocks. Figure 17 shows an example for the Value Counter representation and the decrementing of the value  $1000_D$  by  $1_D$ .

During the programming process of the new Value Counter, one block holds the current valid value and the other block is used to write the new counter value. At the end of programming cycle the current valid value, becomes an invalid value while it is erased (all bytes set to FF<sub>H</sub>) and the other one holds the new valid value.

| _                        |                 | rement ex       |                 |                 |                                |

|--------------------------|-----------------|-----------------|-----------------|-----------------|--------------------------------|

| 1 <sup>st</sup> step     |                 |                 |                 |                 | _                              |

| Block<br>22 <sub>H</sub> | E8 <sub>H</sub> | 17 <sub>H</sub> | 03 <sub>H</sub> | 00н             | valid counter<br>(start value) |

| Block<br>23 <sub>H</sub> | FF <sub>H</sub> | FF <sub>H</sub> | FF <sub>H</sub> | FF <sub>H</sub> |                                |

|                          |                 |                 |                 |                 |                                |

| 2 <sup>nd</sup> step     |                 |                 |                 |                 | _                              |

| Block<br>22 <sub>H</sub> | E8 <sub>H</sub> | 17 <sub>H</sub> | 03н             | 00н             | valid counter<br>(start value) |

| Block<br>23 <sub>H</sub> | E7 <sub>H</sub> | 18 <sub>H</sub> | 03 <sub>H</sub> | 00 <sub>H</sub> | valid counter<br>(new value)   |

|                          |                 |                 |                 |                 | _                              |

| 3 <sup>rd</sup> step     |                 |                 |                 |                 |                                |

| Block<br>22 <sub>H</sub> | FF <sub>H</sub> | FF <sub>H</sub> | FF <sub>H</sub> | FF <sub>H</sub> | erase                          |

| Block<br>23 <sub>H</sub> | E7 <sub>H</sub> | 18 <sub>H</sub> | 03н             | 00н             | valid counte<br>(new value)    |

Figure 17 Value Counter decrement example

### 6.2 Loading and Reading of Value Counter

Loading of the Value Counter is done by either:

- Using WR2B command to address 22<sub>µ</sub>:

- [A1<sub>H</sub>] [22<sub>H</sub>] [CNT0<sub>H</sub>, CNT0<sub>H</sub>, CNT1<sub>H</sub>, 00<sub>H</sub>, FF<sub>H</sub>, FF<sub>H</sub>, FF<sub>H</sub>, FF<sub>H</sub>] [CRC0<sub>H</sub>, CRC1<sub>H</sub>]

- Using two WR1B commands to address 22<sub>H</sub> and 23<sub>H</sub>:

- [A2<sub>H</sub>] [22<sub>H</sub>] [CNT0<sub>H</sub>,CNT0<sub>H</sub>,CNT1<sub>H</sub>, 00<sub>H</sub>] [CRC0<sub>H</sub>, CRC1<sub>H</sub>]

- [A2<sub>H</sub>] [23<sub>H</sub>] [FF<sub>H</sub>,FF<sub>H</sub>,FF<sub>H</sub>,FF<sub>H</sub>] [CRC0<sub>H</sub>, CRC1<sub>H</sub>]

- It is also possible to use Compatibility Write command to initialize the counter, but this is not recommended.

It is crucial to initialize both Value Counter blocks for the correct counter operation.

Reading of Value Counter is done by either:

- Using RD2Bcommand to addresses 22<sub>H</sub>:

- [31<sub>H</sub>] [22<sub>H</sub>] [CRC0<sub>H</sub>, CRC1<sub>H</sub>]

- Using RD4B command to addresses 22<sub>H</sub>:

- $[30_{H}] [22_{H}] [CRC0_{H}, CRC1_{H}]$

- Using DCR16 command with parameter 0000<sub>H</sub>:

- $[D0_H] [0000_H] [CRC0_H, CRC1_H]$

**16-bit Value Counter Functionality**

# 6.3 Decrementing Value Counter and Anti-Tearing

The DCR16 command is used to decrement the Value Counter value. For more details refer to the command description in the **Chapter 8.2.8**.

During the execution of the DCR16 command the my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC performs following actions:

- Read both Value Counter blocks:

- Determine the correct valid Value Counter state. Therefore the values stored in blocks 22<sub>H</sub> and 23<sub>H</sub> are compared.

- Normally one of the counter value blocks is erased or has an incorrect format and the other block holds the valid counter value.

- If both counter values are correctly formatted, the higher value is chosen as the valid counter value.

Note that at least one of the counters must be formatted correctly. Otherwise the Value Counter block is corrupted and no further decrement of the Value Counter is possible.

- If both blocks carry invalid values (incorrect format) no further decrement of Value Counter is possible. The

my-d™ move and my-d™ move NFC then responds with a NACK.

- · Compares the received parameter and the valid counter value.

- If the received parameter is equal or lower than the valid counter value the my-d™ move and my-d™ move NFC decrements the valid value by the received parameter, programs this value to the previous invalid value, erases the previous valid value and replies the new written value.

- If the received parameter is higher then the valid value no decrement is possible and the my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC responds with a NACK

### 6.4 Protection Mechanisms for the Value Counter

The my-d<sup>™</sup> move and my-d<sup>™</sup> move NFC offers some methods to protect the Value Counter. Following measures should be considered to prevent unauthorized changes.