#### **GENERAL DESCRIPTION**

The MC3635 is an ultra-low power, lownoise, integrated digital output 3-axis accelerometer with a feature set optimized for wearables and consumer product motion sensing. Applications include wearable consumer products, IoT devices, user interface control, gaming motion input, electronic compass tilt compensation for cell phones, game controllers, remote controls and portable media products.

Low noise and low power are inherent in the monolithic fabrication approach, where the MEMS accelerometer is integrated in a single-chip with the electronics integrated circuit.

In the MC3635 the internal sample rate can be set from 14 to 1300 samples / second. Specific tap or sample acquisition conditions can trigger an interrupt to a remote MCU. Alternatively, the device supports the reading of sample and event status via polling.

#### **FEATURES**

#### Range, Sampling & Power

- ±2, 4, 8, 12 or 16g ranges

- 8, 10 or 12-bit resolution with FIFO

- 14-bit single samples

- Sample rate 14 1300 samples/sec

- Sample trigger via internal oscillator, clock pin or software command

- Sniff and Wake modes

- 0.3 µA Sniff current @ 1Hz

- Separate or combined sniff/wake

- Ultra-Low Power with 32 sample FIFO

- 0.9 µA typical current @ 25Hz

- 1.6 μA typical current @ 50Hz

- 2.8 μA typical current @ 100Hz

- 36 μA typical current @ 1300Hz

## Simple System Integration

- I2C interface, up to 1 MHz

- SPI Interface, up to 8 MHz

- 1.6 × 1.6 × 0.94 mm 10-pin package

- Single-chip 3D silicon MEMS

- Low noise to 2.3mgRMS

- ROHS Compliant

Information furnished by MEMSIC is believed to be accurate and reliable. However, no responsibility is assumed by MEMSIC for its use, or for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of MEMSIC.

© MEMSIC Semiconductor (Tianjin) Co., Ltd.

Room 4-501, Financial Center, No. 158, West Third Road, Tianjin Airport Economic Zone, Tianjin, China, 300308

Formal release date: 2020/07/08

Tel: +86 022-59896226 www.memsic.com

# TABLE OF CONTENTS

| 1 |     | Ord  | ler Information                               | 5    |

|---|-----|------|-----------------------------------------------|------|

| 2 |     | Fun  | nctional Block Diagram                        | 6    |

| 3 |     | Pac  | kaging and Pin Description                    | 7    |

|   | 3.1 |      | Package Outline                               | 7    |

|   | 3.2 |      | Package Orientation                           | 8    |

|   | 3.3 |      | Pin Description                               |      |

|   | 3.4 |      | Typical Application Circuits                  |      |

|   | 3.5 |      | Tape and Reel                                 | . 13 |

|   | 3.6 |      | Soldering Profile                             |      |

|   | 3.7 |      | Shipping and Handling Guidelines              | . 15 |

|   | 3.8 |      | Moisture Sensitivity Level Control            | . 15 |

| 4 |     | Spe  | ecifications                                  | 16   |

|   | 4.1 |      | Absolute Maximum Ratings                      | . 16 |

|   | 4.2 |      | Sensor Characteristics                        |      |

|   | 4.3 |      | Electrical and Timing Characteristics         | . 18 |

|   | 4.3 | 3.1  | Electrical Power and Internal Characteristics | . 18 |

|   | 4.3 | 3.2  | Electrical Characteristics                    | . 19 |

|   | 4.3 | 3.3  | I2C Timing Characteristics                    | . 20 |

|   | 4.3 | 3.4  | SPI Timing Characteristics                    | . 21 |

| 5 |     | Ger  | neral Operation                               | 22   |

|   | 5.1 |      | Sensor Sampling                               | . 22 |

|   | 5.2 |      | Offset and Gain Calibration                   | . 22 |

|   | 5.3 |      | Reset                                         | . 22 |

|   | 5.4 |      | Reload                                        | . 23 |

|   | 5.5 |      | Operational Modes                             | . 24 |

|   | 5.6 |      | Mode State Machine Flow                       | . 25 |

| 6 |     | Inte | rfaces                                        | 26   |

|   | 6.1 |      | SPI vs I2C Operation Modes                    | . 26 |

|   | 6.2 |      | I2C Physical Interface                        | . 26 |

|   | 6.3 |      | I2C Message Format                            | . 27 |

| 6.4  | SPI Physical Interface                                | . 28 |

|------|-------------------------------------------------------|------|

| 6.5  | SPI 3-Wire Mode                                       | . 28 |

| 6.6  | SPI Protocol                                          | . 28 |

| 6.7  | SPI Register Write Cycle - Single                     | . 29 |

| 6.8  | SPI Register Write Cycle - Burst                      | . 29 |

| 6.9  | SPI Register Read Cycle - Single                      |      |

| 6.10 | SPI Register Read Cycle - Burst                       | . 30 |

| 6.11 | SPI Status Option                                     |      |

| 6.12 | SPI High-Speed Mode                                   |      |

| 7 Re | gister Interface                                      |      |

| 7.1  | Register Summary                                      | . 33 |

| 7.2  | (0x00) Extended Status Register 1                     | . 35 |

| 7.3  | (0x01) Extended Status Register 2                     | . 36 |

| 7.4  | (0x02 - 0x07) XOUT, YOUT & ZOUT Data Output Registers |      |

| 7.5  | (0x08) Status Register 1                              |      |

| 7.6  | (0x09) Status Register 2                              |      |

| 7.7  | (0x0D) Feature Register 1                             |      |

| 7.8  | (0x0E) Feature Register 2                             |      |

| 7.9  | (0x0F) Initialization Register 1                      |      |

| 7.10 | (0x10) Mode Control Register                          | . 48 |

| 7.11 | (0x11) Rate Register 1                                | . 50 |

| 7.12 | (0x12) Sniff Control Register                         | . 52 |

| 7.13 | (0x13) Sniff Threshold Control Register               | . 55 |

| 7.14 | (0x14) Sniff Configuration Register                   | . 58 |

| 7.15 | (0x15) Range and Resolution Control Register          | . 60 |

| 7.16 | (0x16) FIFO Control Register                          | . 62 |

| 7.17 | (0x17) Interrupt Control Register                     | . 63 |

| 7.18 | (0x1A) Initialization Register 3                      | . 65 |

| 7.19 | (0x1B) Scratchpad Register                            | . 66 |

| 7.20 | (0x1C) Power Mode Control Register                    | . 67 |

| 7.21 | (0x20) Drive Motion X Register                        |      |

| 7.22 | (0x21) Drive Motion Y Register                        |      |

| 7.23 | (0x22) Drive Motion Z Register                        | . 71 |

| 7.24 | (0x24) Reset Register                                 | 72   |

| 7. | .25 | (0x28) Initialization Register 2      | 73   |

|----|-----|---------------------------------------|------|

| 7. | .26 | (0x29) Trigger Count Register         | 74   |

| 7. | .27 | (0x2A - 0x2B) X-Axis Offset Registers | 75   |

| 7. | .28 | (0x2C - 0x2D) Y-Axis Offset Registers | 76   |

| 7. | .29 | (0x2E – 0x2F) Z-Axis Offset Registers | 77   |

| 7. | .30 | (0x2B & 0x30) X-Axis Gain Registers   | 78   |

| 7. | .31 | (0x2D & 0x31) Y-Axis Gain Registers   | 79   |

| 7. | .32 | (0x2F & 0x32) Z-Axis Gain Registers   | 80   |

| 8  |     | Index of Tables                       | . 81 |

| 9  |     | Revision History                      | . 83 |

# 1 ORDER INFORMATION

**Table 1. Order Information**

| Part Number | Resolution  | Order Number | Package | Shipping         |

|-------------|-------------|--------------|---------|------------------|

| MC3635      | 8 to 14-bit | MC3635       | LGA-10  | Tape & Reel, 5Ku |

**Table 2. Top Marking Specification**

| Row | Marking           |

|-----|-------------------|

| CCC | Factory lot code  |

| XX  | Device identifier |

| •   | Pin1 identifier   |

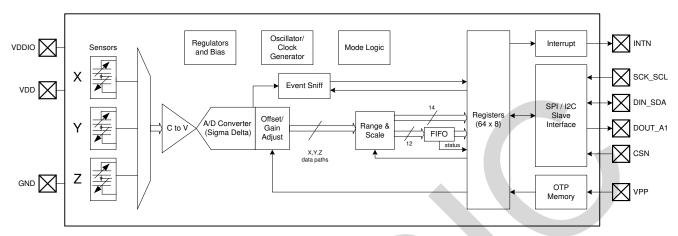

# **2 FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Block Diagram

# 3 PACKAGING AND PIN DESCRIPTION

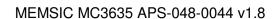

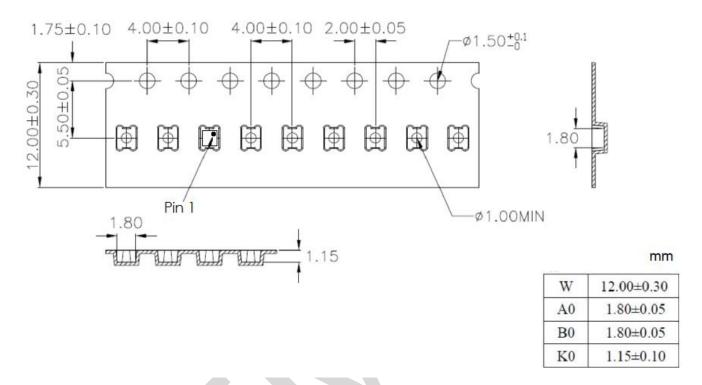

#### 3.1 PACKAGE OUTLINE

Figure 2. Package Outline and Mechanical Dimensions

#### 3.2 PACKAGE ORIENTATION

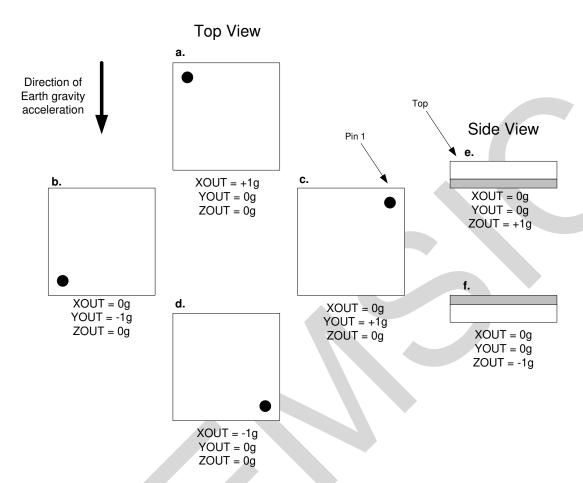

Figure 3. Package Orientation

Figure 4. Package Axis Reference

#### 3.3 PIN DESCRIPTION

| Pin | Name              | Function                                    |

|-----|-------------------|---------------------------------------------|

| 1   | DOUT_A1           | SPI data output<br>I2C address bit 1        |

| 2   | DIN_SDA 1         | SPI data In<br>I2C serial data input/output |

| 3   | NC                | No connect                                  |

| 4   | VPP               | Connect to GND                              |

| 5   | INTN <sup>2</sup> | Interrupt active LOW 3                      |

| 6   | VDDIO             | Power supply for interface                  |

| 7   | VDD               | Power supply for internal                   |

| 8   | GND               | Ground                                      |

| 9   | CSN               | SPI Chip Select                             |

| 10  | SCK_SCL 1         | SPI Clock<br>I2C serial clock input         |

**Table 3. Pin Description**

#### Notes:

- 1) When using the I2C interface, this pin requires a pull-up resistor, typically 4.7k $\Omega$  to pin VDDIO. Refer to I2C Specification for Fast-Mode devices. Higher resistance values can be used (typically done to reduce current leakage) but such applications are outside the scope of this datasheet.

- 2) This pin can be configured by software to operate either as an open-drain output or push-pull output. If set to open-drain, then it requires a pull-up resistor, typically  $4.7k\Omega$  to pin VDDIO.

- 3) INTN pin polarity is programmable.

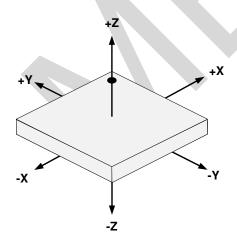

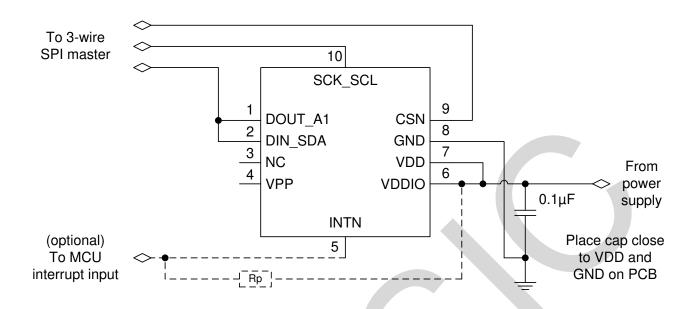

#### 3.4 TYPICAL APPLICATION CIRCUITS

NOTE<sup>1</sup>: Rp are typically  $4.7k\Omega$  pullup resistors to VDDIO, per I2C specification. When VDDIO is powered down, DIN\_SDA and SCK\_SCL will be driven low by internal ESD diodes. NOTE<sup>2</sup>: Attach typical  $4.7k\Omega$  pullup resistor if INTN is defined as open-drain.

Figure 5. Typical I2C Application Circuit

In typical applications, the interface power supply may contain significant noise from external sources and other circuits which should be kept away from the device. Therefore, for some applications a lower-noise power supply might be desirable to power the device.

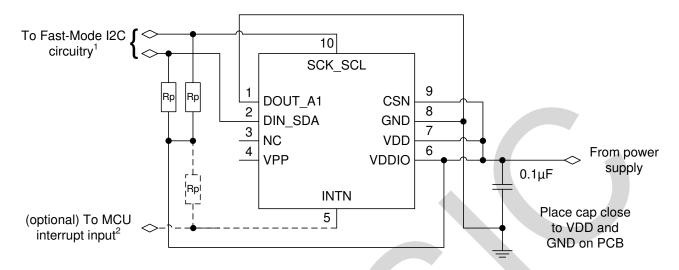

NOTE Rp: Attach typical  $4.7k\Omega$  pullup resistor if INTN is defined as open-drain.

Figure 6. Typical 4-wire SPI Application Circuit

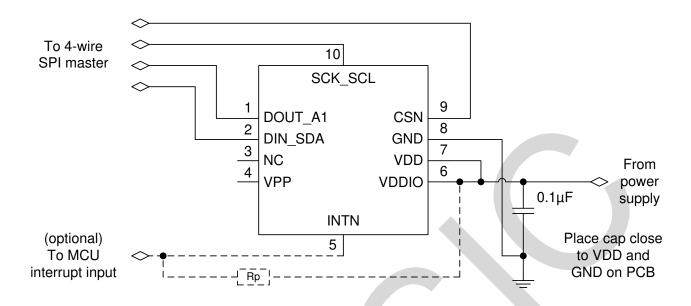

NOTE Rp: Attach typical  $4.7k\Omega$  pullup resistor if INTN is defined as open-drain.

Figure 7. Typical 3-wire SPI Application Circuit

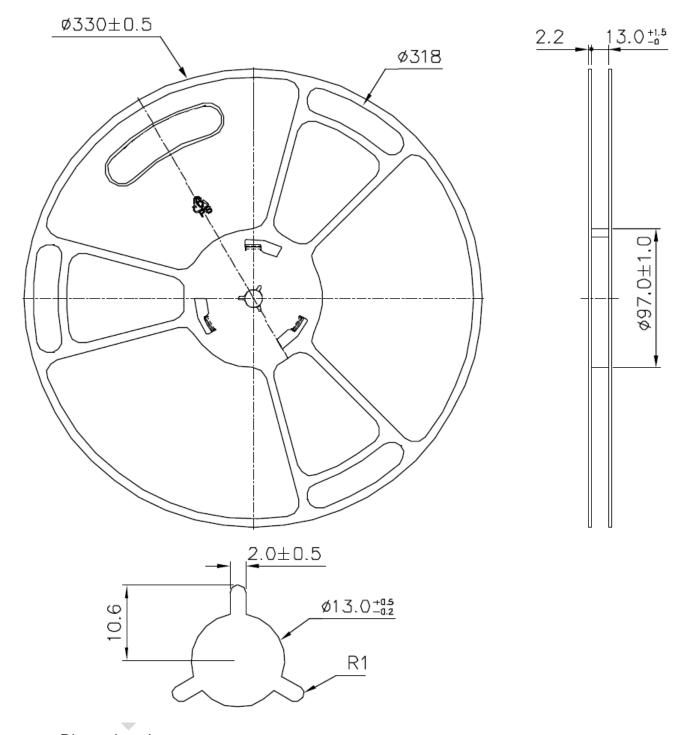

#### 3.5 TAPE AND REEL

Devices are shipped in reels, in standard cardboard box packaging. See <u>Figure 8. MC3635 Tape Dimensions</u> and <u>Figure 9. MC3635 Reel Dimensions</u>.

Figure 8. MC3635 Tape Dimensions

Dimensions in mm.

Figure 9. MC3635 Reel Dimensions

#### 3.6 SOLDERING PROFILE

The LGA package follows the reflow soldering classification profiles described in *Joint Industry Standard, Moisture/Reflow Sensitivity Classification for Nonhermetic Surface Mount Devices*, document number J-STD-020E. Reflow soldering has a peak temperature (T<sub>p</sub>) of 260°C

#### 3.7 SHIPPING AND HANDLING GUIDELINES

Shipping and handling follow the standards described in *Joint Industry Standard*, *Handling*, *Packing*, *Shipping and Use of Moisture/Reflow Sensitive Surface Mount Devices*, document number J-STD-033C.

The following are additional handling guidelines (refer to the MEMSIC document, PCB Design, Device Handling and Assembly Guidelines, for more information):

- While the mechanical sensor is designed to handle high-g shock events, direct mechanical shock to the package should be avoided.

- SMT assembly houses should use automated assembly equipment with either plastic nozzles or nozzles with compliant tips (for example, soft rubber or silicone).

- Avoid g-forces beyond the specified limits during transportation.

- Handling and mounting of sensors should be done in a defined and qualified installation.

#### 3.8 MOISTURE SENSITIVITY LEVEL CONTROL

The Moisture Sensitivity Level, MSL, for MC3635 (10-pin LGA package) is MSL3.

Refer to IPC/JEDEC J-STD-020D.1 "Joint Industry Standard: Moisture/Reflow Sensitivity

Classification for Non-hermetic Solid State Surface Mount Devices" and IPC/JEDEC J

STD033A "Joint Industry Standard: Handling, Packing, Shipping and Use of Moisture/Reflow Sensitive Surface Mount Devices."

The following are storage recommendations (refer to the MEMSIC document, PCB Design, Device Handling and Assembly Guidelines, for more information):

- Store the tape and reel in the *unopened* dry pack, until required on the assembly floor.

- If the dry pack has been opened or the reel has been removed from the dry pack, reseal

the reel inside of the dry pack with a black protective belt. Avoid crushing the tape and

reel.

- Store the cardboard box in a vertical position.

# **4 SPECIFICATIONS**

# 4.1 ABSOLUTE MAXIMUM RATINGS

Parameters exceeding the Absolute Maximum Ratings may permanently damage the device.

| Rating                         | Symbol                                                    | Minimum / Maximum<br>Value                        | Unit |

|--------------------------------|-----------------------------------------------------------|---------------------------------------------------|------|

| Supply Voltages                | Pins VDD,<br>VDDIO                                        | -0.3 / +3.6                                       | V    |

| Acceleration, any axis, 100 μs | <b>9</b> мах                                              | 10000                                             | g    |

| Ambient operating temperature  | T <sub>OP</sub>                                           | -40 / +85                                         | °C   |

| Storage temperature            | T <sub>STG</sub>                                          | -40 / +125                                        | °C   |

| ESD human body model           | НВМ                                                       | ± 2000                                            | V    |

| Input voltage to non-power pin | Pins CSN,<br>DIN_SDA,<br>DOUT_A1,<br>INTN, and<br>SCK_SCL | -0.3 / (VDDIO + 0.3) or<br>3.6 whichever is lower | V    |

**Table 4. Absolute Maximum Ratings**

#### 4.2 SENSOR CHARACTERISTICS

VDD = VDDIO = 1.8V,  $T_{op}$  = 25  $^{0}$ C unless otherwise noted

| Parameter                                                | Conditions                     | Min | Тур                          | Max  | Unit               |

|----------------------------------------------------------|--------------------------------|-----|------------------------------|------|--------------------|

| Acceleration range                                       |                                |     | ±2<br>±4<br>±8<br>±12<br>±16 |      | g                  |

| Sensitivity                                              |                                | 8   |                              | 4096 | LSB/g              |

| Sensitivity<br>Temperature<br>Coefficient <sup>1</sup>   |                                |     | 0.015                        |      | %/°C               |

| Zero-g Offset                                            | Post-board mount, ODR <= 400Hz |     | ± 40                         |      | mg                 |

| Zero-g Offset<br>Temperature<br>Coefficient <sup>1</sup> |                                |     | ±1                           |      | mg/ <sup>0</sup> C |

|                                                          | WAKE MODES:                    |     |                              |      |                    |

|                                                          | Ultra-Low Power, Avg X&Y&Z:    |     | 6.5                          |      |                    |

|                                                          | Low Power, Avg X&Y&Z:          |     | 4.4                          |      |                    |

| Noise 1 @                                                | Precision, Avg X&Y&Z:          |     | 1.7                          |      | mg                 |

| 100Hz                                                    | SNIFF MODES:                   |     |                              |      | RMS                |

|                                                          | Ultra-Low Power, Avg X&Y&Z:    |     | 40                           |      |                    |

|                                                          | Low Power, Avg X&Y&Z:          |     | 25                           |      |                    |

|                                                          | Precision, Avg X&Y&Z:          |     | 5                            |      |                    |

| Nonlinearity 1                                           |                                |     | 1                            |      | % FS               |

| Cross-axis<br>Sensitivity 1                              | Between any two axes           |     | 2                            |      | %                  |

**Table 5. Sensor Characteristics**

<sup>&</sup>lt;sup>1</sup> Values are based on device characterization, not tested in production.

### 4.3 ELECTRICAL AND TIMING CHARACTERISTICS

#### 4.3.1 ELECTRICAL POWER AND INTERNAL CHARACTERISTICS

| Parameter                     | Conditions         | Symbol | Min | Тур | Max | Unit |

|-------------------------------|--------------------|--------|-----|-----|-----|------|

| Internal voltage 2            | Pin VDD            | VDD    | 17  | 1.0 | 0.0 |      |

| Internal voltage <sup>2</sup> | Rise-time < 40mSec | VDD    | 1.7 | 1.8 | 3.6 | V    |

| I/O alka a a                  | Pin VDDIO          | VDDIO  | 1.7 | 1.0 | 0.0 | V    |

| I/O voltage                   | Rise-time < 40mSec | VDDIO  | 1.7 | 1.8 | 3.6 | V    |

Test condition: VDD = VDDIO = 1.8V, T<sub>op</sub> = 25 <sup>o</sup>C unless otherwise noted

| Parameter                | Conditions                               | Symbol                 | Min | Тур  | Max  | Unit |

|--------------------------|------------------------------------------|------------------------|-----|------|------|------|

| Sleep<br>current         | Conditions                               | I ddslp                |     | 0.1  | Wida | μΑ   |

|                          | 1Hz                                      |                        |     | 0.3  |      | μA   |

| Sniff current            | 6Hz                                      | ddsnf                  |     | 0.4  |      | μΑ   |

|                          | Precision, 14Hz                          | I <sub>dd14p</sub>     |     | 5    |      |      |

|                          | Ultra-Low Power, 25Hz                    | l <sub>dd25ulp</sub>   |     | 0.9  |      |      |

|                          | Ultra-Low Power, 50Hz<br>Low Power, 54Hz | l <sub>dd50ulp</sub>   |     | 1.6  |      |      |

| Selected                 |                                          | I <sub>dd54lp</sub>    |     | 2.7  |      |      |

| wake supply current (see | Precision, 55Hz                          | I <sub>dd55p</sub>     |     | 18   |      | μΑ   |

| also 7.11)               | Ultra-Low Power, 100Hz                   | I <sub>dd100ulp</sub>  |     | 2.8  |      |      |

|                          | Precision, 100Hz                         | l <sub>dd100p</sub>    |     | 36   |      |      |

|                          | Low Power, 210Hz                         | I <sub>dd210lp</sub>   |     | 11   |      |      |

|                          | Ultra-Low Power, 1300Hz                  | I <sub>dd1300ulp</sub> |     | 36   |      |      |

| Pad<br>Leakage           | Per I/O pad                              | I pad                  |     | 0.01 |      | μΑ   |

Table 6. Electrical Characteristics – Voltage and Current

<sup>&</sup>lt;sup>2</sup> Min and Max limits are hard limits without additional tolerance.

#### 4.3.2 ELECTRICAL CHARACTERISTICS

| Parameter                                                                                   | Symbol | Min        | Max       | Unit |

|---------------------------------------------------------------------------------------------|--------|------------|-----------|------|

| LOW level input voltage                                                                     | VIL    | -0.5       | 0.3*VDDIO | V    |

| HIGH level input voltage                                                                    | VIH    | 0.7*VDDIO  | -         | V    |

| Hysteresis of Schmitt trigger inputs                                                        | Vhys   | 0.05*VDDIO | -         | V    |

| Output voltage, pin INTN, Iol ≤ 2 mA                                                        | Vol    | 0          | 0.4       | V    |

|                                                                                             | Voh    | 0          | 0.9*VDDIO | V    |

| Output voltage, pin DIN_SDA (open drain),<br>Iol ≤ 1 mA                                     | Vols   | -          | 0.1*VDDIO | V    |

| Input current, pins DIN_SDA and SCK_SCL (input voltage between 0.1*VDDIO and 0.9*VDDIO max) | li     | -10        | 10        | μΑ   |

| Capacitance, pins DIN_SDA and SCK_SCL <sup>3</sup>                                          | Ci     |            | 10        | pF   |

**Table 7. Electrical Characteristics – Interface**

#### NOTES:

- If multiple slaves are connected to the I2C signals in addition to this device, only 1 pull-up resistor on each of SDA and SCL should exist. Also, care must be taken to not violate the I2C specification for capacitive loading.

- When pin VDDIO is not powered and set to 0V, INTN, DIN\_SDA and SCK\_SCL will be held to VDDIO plus the forward voltage of the internal static protection diodes, typically about 0.6V.

- When pin VDDIO is disconnected from power or ground (e.g. Hi-Z), the device may become inadvertently powered up through the ESD diodes present on other powered signals.

MEMSIC MC3635 APS-048-0044 v1.8

<sup>&</sup>lt;sup>3</sup> Values are based on device characterization, not tested in production.

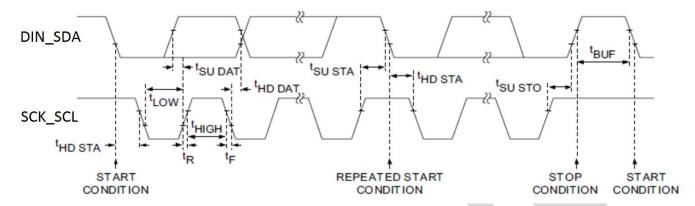

#### 4.3.3 I2C TIMING CHARACTERISTICS

Figure 10. I2C Interface Timing

|                      |                                            | Standard<br>Mode |     | Fast Mode |     | Fast Mode<br>Plus |      | Units |

|----------------------|--------------------------------------------|------------------|-----|-----------|-----|-------------------|------|-------|

| Parameter            | Description                                | Min              | Max | Min       | Max |                   |      |       |

| f <sub>SCL</sub>     | SCL clock frequency                        | 0                | 100 | 0         | 400 | 0                 | 1000 | kHz   |

| t <sub>HD; STA</sub> | Hold time (repeated) START condition       | 4.0              | -   | 0.6       | ı   | 0.26              | -    | μs    |

| t <sub>LOW</sub>     | LOW period of the SCL clock                | 4.7              | -   | 1.3       | -   | 0.5               | -    | μs    |

| t <sub>HIGH</sub>    | HIGH period of the SCL clock               | 4.0              | -   | 0.6       | -   | 0.26              | -    | μs    |

| t <sub>SU;STA</sub>  | Set-up time for a repeated START condition | 4.7              | -   | 0.6       | 1   | 0.26              | -    | μs    |

| t <sub>HD;DAT</sub>  | Data hold time                             | 5.0              | -   | -         | -   | -                 | -    | μs    |

| t <sub>SU;DAT</sub>  | Data set-up time                           | 250              | -   | 100       | -   | 50                | -    | ns    |

| t <sub>SU;STO</sub>  | Set-up time for STOP condition             | 4.0              | -   | 0.6       | -   | 0.26              | -    | μs    |

| t <sub>BUF</sub>     | Bus free time between a STOP and START     | 4.7              | -   | 1.3       | -   | 0.5               | -    | μs    |

**Table 8. I2C Timing Characteristics**

NOTE: Values are based on I2C Specification requirements, not tested in production.

#### 4.3.4 SPI TIMING CHARACTERISTICS

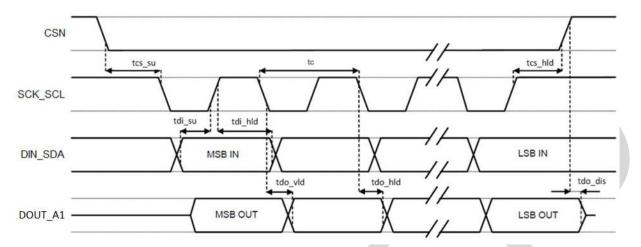

Figure 11. SPI Interface Timing Waveform

| Symbol  | Parameter                       |     |                | Units |     |

|---------|---------------------------------|-----|----------------|-------|-----|

|         |                                 | Min | Тур            | Max   |     |

| tc      | SPI SCK_SCL Clock Cycle         | 500 |                |       | ns  |

| fc      | SPI SCK_SCL Clock Frequency     |     | 8 <sup>4</sup> |       | MHz |

| tcs_su  | SPI CSN Setup Time              | 6   |                |       | ns  |

| tcs_hld | SPI CSN Hold Time               | 8   |                |       | ns  |

| tdi_su  | SPI DIN_SDA Input Setup Time    | 5   |                |       | ns  |

| tdi_hld | SPI DIN_SDA Input Hold Time     | 15  |                |       | ns  |

| tdo_vld | SPI DOUT_A1 Valid Output Time   |     |                | 50    | ns  |

| tdo_hld | SPI DOUT_A1 Output Hold Time    | 9   |                |       | ns  |

| tdo_dis | SPI DOUT_A1 Output Disable Time |     |                | 50    | ns  |

**Table 9. SPI Interface Timing Parameters**

<sup>&</sup>lt;sup>4</sup> Values are based on device characterization.

# 5 GENERAL OPERATION

The device supports the reading of samples and device status upon interrupt or via polling. It contains a 12-bit 32 sample FIFO with programmable watermark. The device is internally clocked but also includes a manual trigger mode. It can be put into several low power modes, depending upon the desired sensing application. The device can run in full-featured mode from its fast internal clock or from a slower heartbeat clock, with limited functionality and at lower power. The device can connect as a slave to either a SPI or I2C master.

#### 5.1 SENSOR SAMPLING

X, Y and Z accelerometer data is stored in registers XOUT, YOUT, and ZOUT registers. The data is represented as 2's complement format.

The desired resolution and full scale acceleration range are set in the RANGE C register.

#### 5.2 OFFSET AND GAIN CALIBRATION

The default digital offset and gain calibration data can be read from the device, if necessary, in order to reduce the effects of post-assembly influences and stresses which may cause the sensor readings to be offset from their factory values.

#### 5.3 RESET

The device can be completely reset via an I2C or SPI instruction. Writing register 0x24 with 0x40 (bit 6) causes a power-on reset operation to execute. No attempt should be made to access registers within 1mSec after issuing this operation. The device must be placed in STANDBY mode before executing the reset. The pin DOUT\_A1 is sampled for the purposes of setting the I2C device address after this reset operation.

NOTE: Immediately after a RESET or power-up event, several registers must be written with initialization values as shown below. The recommended sequence for I2C interface is:

| Step | Address | Value which must be written        | Comment                    |  |  |

|------|---------|------------------------------------|----------------------------|--|--|

| 1    | 0x10    | 0x01                               | Go to standby              |  |  |

| 2    | 0x24    | 0x40                               | Reset (or Power-On)        |  |  |

| 3    | NA      | Wait at least 1mSec                | Wait for reset to complete |  |  |

| 4    | 0x0D    | 0x40                               | I2C mode enabled           |  |  |

| 5    | 0x0F    | 0x42                               | Initialization             |  |  |

| 6    | 0x20    | 0x01                               | Initialization             |  |  |

| 7    | 0x21    | 0x80                               | Initialization             |  |  |

| 8    | 0x28    | 0x00                               | Initialization             |  |  |

| 9    | 0x1A    | 0x00                               | Initialization             |  |  |

| 10   | Coi     | nfigure remaining registers and us | se sensor as normal        |  |  |

Table 10. Recommended Initialization Sequence for I2C Interface

And the recommended sequence for SPI interface is:

| Step | Address | Value which must be written      | Comment                              |  |  |

|------|---------|----------------------------------|--------------------------------------|--|--|

| 1    | 0x10    | 0x01                             | Go to standby                        |  |  |

| 2    | 0x24    | 0x40                             | Reset (or Power-On)                  |  |  |

| 3    | NA      | Wait at least 1mSec              | Wait for reset to complete           |  |  |

| 4    | 0x18    | Read                             | Non-zero value                       |  |  |

| 5    | 0x0D    | 0x80                             | SPI mode enabled                     |  |  |

| 6    | 0x0D    | Read                             | Repeat steps 5 & 6 till 0x80 is read |  |  |

| 7    | 0x0F    | 0x42                             | Initialization                       |  |  |

| 8    | 0x10    | 0x01                             | Go to Standby from Sleep             |  |  |

| 9    | NA      | Wait at least 10mSec             | Wait for state machine               |  |  |

| 10   | 0x20    | 0x01                             | Initialization                       |  |  |

| 11   | 0x21    | 0x80                             | Initialization                       |  |  |

| 12   | 0x28    | 0x00                             | Initialization                       |  |  |

| 13   | 0x1A    | 0x00                             | Initialization                       |  |  |

| 14   |         | Configure remaining registers an | d use sensor as normal               |  |  |

Table 11. Recommended Initialization Sequence for SPI Interface

#### 5.4 RELOAD

The device registers can be reloaded from OTP via an I2C or SPI instruction. Writing register 0x24 with 0x80 (bit 7) causes a reload operation to execute. The contents of OTP are reloaded into the register set. However any non-loaded register locations will not be affected. No attempt should be made to access registers within 1mSec after issuing this operation. The device must be placed in STANDBY mode before executing the reset.

The pin DOUT\_A1 is sampled for the purposes of setting the I2C device address after this reload operation.

# 5.5 OPERATIONAL MODES

The device has various modes of operation as described below:

| Mode    | Description and Comments                                                                                                                                                                                                                                                                                                                                   |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLEEP   | SLEEP is the lowest power mode. The internal regulators are enabled, and much of the chip is disabled. The SLEEP mode is the default POR mode. This command is available at any time, although up to three periods of the internal heartbeat clock may be required to complete the transition.                                                             |

| STANDBY | STANDBY is a low power mode. All internal regulators are enabled, and internal main and heartbeat clocks are enabled. The default STANDBY frequency for the heartbeat clock is ~500 Hz. TRIG mode operation can be executed only from this mode.  Software must change the mode to SLEEP or STANDBY in register 0x10 before writing to any other register. |

| SNIFF   | SNIFF is a lower power, limited activity detection mode; Sniff circuitry is enabled and sniff-only sampling is enabled. There are no FIFO operations, and hardware will automatically transition to CWAKE mode upon activity detection.                                                                                                                    |

| CWAKE   | CWAKE or continuous wake is the typical XYZ sampling mode. Sample data is written to the output registers, or the FIFO when enabled. Hardware will automatically transition to CWAKE mode upon SNIFF activity detection.                                                                                                                                   |

| SWAKE   | SNIFF and CWAKE circuitry are both active simultaneously. Sniff circuitry is enabled and XYZ samples are written to the output registers, or the FIFO when enabled.                                                                                                                                                                                        |

| TRIG    | The device produces a fixed number of samples, between 1 and 254, or continuously. This mode ignores the setting in the ODR, but uses the STB_RATE[2:0] clock setting as the sampling rate. The trigger can be set to come from the external pin INTN or a write to register bit 0x10[7].                                                                  |

**Table 12. Operational Modes**

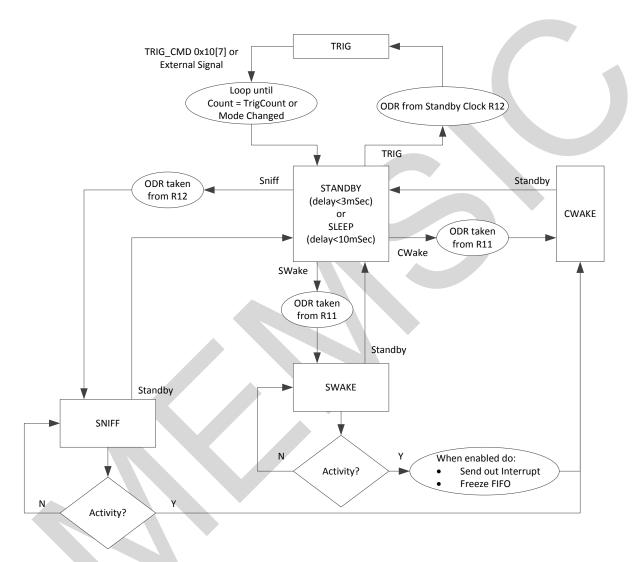

#### 5.6 MODE STATE MACHINE FLOW

Figure 12. Mode Operational Flow shows the operational mode flow for the device. The device defaults to SLEEP mode following power-on. Mode transitions occur at an approximate rate of ~500Hz. Depending on the operation, the MODE State Machine may trigger events that autoclear or set the MCTRL[2:0] bits in register 0x10 after a particular command is chosen.

Figure 12. Mode Operational Flow

# 6 INTERFACES

#### 6.1 SPI VS I2C OPERATION MODES

The device contains both I2C and SPI slave interfaces which share common pins. However, only one interface can be active for correct device operation. Once the device completes POR or a hard reset, both interfaces are active.

After power-up and any reset of the device, the first transaction to the device must be writing to the selected enable bit, either "I2C\_EN" or "SPI\_EN" in register 0x0D. The situation where bits are set at the same time must be avoided or unstable device operation could occur.

To keep the "disabled" interface from interfering in future transactions, the corresponding "enable" bit must be set in the register set. For example, if the 4-wire SPI interface is to be active, write a value of 0x80 to register 0x0D.

#### 6.2 I2C PHYSICAL INTERFACE

The I2C slave interface operates at a maximum speed of 1 MHz in I2C "Fast Mode Plus". The SDA (data) is an open-drain, bi-directional pin and the SCL (clock) is an input pin.

## The device always operates as an I2C slave.

An I2C master initiates all communication and data transfers and generates the SCK\_SCL clock that synchronizes the data transfer. The I2C device address depends upon the settings of various registers and pins as shown in the table below.

An I2C master initiates all communication and data transfers and generates the SCK\_SCL clock that synchronizes the data transfer. The I2C device address depends upon the state of pin DOUT\_A1 during power-up as shown in the table below.

| 7-bit Device ID     | 8-bit Address<br>(Write) | 8-bit Address<br>(Read) | DOUT A1 level upon power-up |  |

|---------------------|--------------------------|-------------------------|-----------------------------|--|

| 0x4C<br>(0b1001100) | 0x98                     | 0x99                    | GND                         |  |

| 0x6C<br>(0b1101100) | 0xD8                     | 0xD9                    | VDD                         |  |

**Table 13. I2C Address Selection**

The I2C interface remains active as long as power is applied to the VDDIO pin. In STANDBY mode the device responds to I2C read and write cycles, but interrupts cannot be cleared. All registers can be written in the SLEEP or STANDBY modes, but in CWAKE only the (0x10) Mode Control Register can be modified.

Internally, the registers which are used to store samples are clocked by the sample clock and gated by I2C activity. Therefore, in order to allow the device to collect and present samples in the sample registers at least one I2C STOP condition must be present between samples.

Refer to the I2C specification for a detailed discussion of the protocol. Per I2C requirements, when the I2C interface is enabled, DIN\_SDA is an open drain, bi-directional pin. Pins SCK SCL and DIN SDA each require an external pull-up resistor, typically  $4.7k\Omega$ .

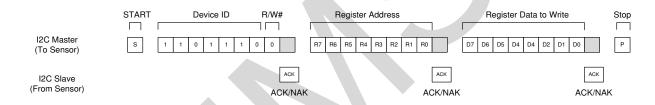

#### 6.3 I2C MESSAGE FORMAT

# NOTE: At least one I2C STOP condition must be present between samples in order for the device to update the sample data registers.

The device uses the following general format for writing to the internal registers. The I2C master generates a START condition, and then supplies the 7-bit device ID. The 8th bit is the R/W# flag (write cycle = 0). The device pulls DIN\_SDA low during the 9th clock cycle indicating a positive ACK.

The second byte is the 8-bit register address of the device to access, and the last byte is the data to write.

Figure 13. I2C Message Format, Write Cycle, Single Register Write

In a read cycle, the I2C master writes the device ID (R/W#=0) and register address to be read. The master issues a RESTART condition and then writes the device ID with the R/W# flag set to '1'. The device shifts out the contents of the register address.

Figure 14. I2C Message Format, Read Cycle, Single Register Read

The I2C master may write or read consecutive register addresses by writing or reading additional bytes after the first access. The device will internally increment the register address.

NOTE: See (0x0E) Feature Register 2 for address wrap details.

#### 6.4 SPI PHYSICAL INTERFACE

The device always operates as an SPI slave. An SPI master must initiate all communication and data transfers and generate the SCK\_SCL clock that synchronizes the data transfer. The CSN pin must be pulled up to VDDIO when the SPI interface is not in use. The SPI interface can operate in 3-wire or 4-wire mode.

#### 6.5 SPI 3-WIRE MODE

SPI 3-wire mode is disabled by default. To enable 3-wire mode, the first write to the device should immediately enable this feature in register (0x0D) Feature Register 1. In 3-wire mode the pins DOUT\_A1 and DIN\_SDA must be connected on the PCB. Anytime there is a reset to the device, a POR event, or a power cycle the SPI 3-wire configuration will reset to 4-wire mode.

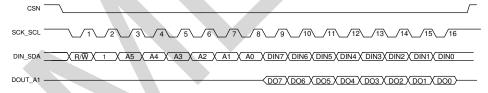

#### 6.6 SPI PROTOCOL

The general protocol for the SPI interface is shown in the figures below. The falling edge of CSN initiates the start of the SPI bus cycle. The first byte of the transaction is the command/address byte. Because the register address space is 64 locations, a total of 6 address bits are required for each SPI bus cycle. During clock '1', the R/W# bit is set to '0' for a write cycle or '1' for a read cycle.

The interface supports 2 types of addressing: 1-byte (typically used) and 2-byte (to support legacy hardware). In the case of 2-byte addressing, the bits occurring during clocks 2 and 9-16 must be driven to '0' for the address to be correctly decoded. Each read or write transaction always requires a minimum of 16 or 24 cycles of the SCK\_SCL pin.

When the SPI master is writing data, data may change when the clock is low, and must be stable on the clock rising edge. Similarly, output data written to the SPI master is shifted out on the falling edge of clock and can be latched by the master on the rising edge of the clock. Serial data in or out of the device is always MSB first.

Figure 15. General SPI Protocol, 1-Byte Address

Figure 16. General SPI Protocol, 2-Byte Address (legacy)

NOTE: Either 1-byte or 2-byte addressing may be used for any SPI transaction, although for simplicity, the remaining timing diagrams show only 1-byte addressing.

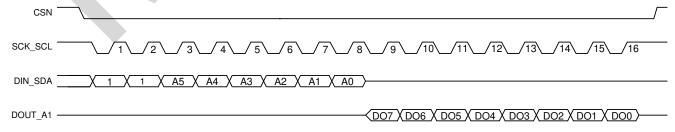

#### 6.7 SPI REGISTER WRITE CYCLE - SINGLE

A single register write consists of a 16-clock transaction. As described above, the first bit is set to '0' indicating a register write followed by the register address.

Figure 17. SPI Register Write Cycle - Single

#### 6.8 SPI REGISTER WRITE CYCLE - BURST

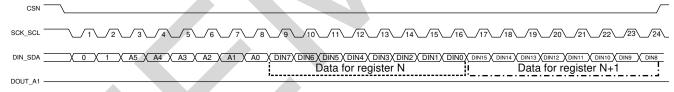

A burst (multi-byte) register write cycle uses the address specified at the beginning of the transaction as the starting register address. Internally the address will auto-increment to the next consecutive address for each additional byte (8-clocks) of data written beyond clock 8.

# NOTE: See (0x0E) Feature Register 2 for address wrap details.

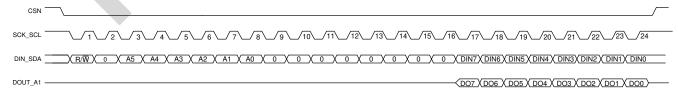

Figure 18.SPI Register Write Cycle - Burst (2-register burst example)

#### 6.9 SPI REGISTER READ CYCLE - SINGLE

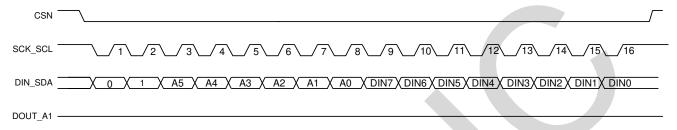

A single register read consists of a 16-clock transaction. As described above, the first bit is set to '1' indicating a register read followed by the register address.

Figure 19. SPI Register Read Cycle - Single

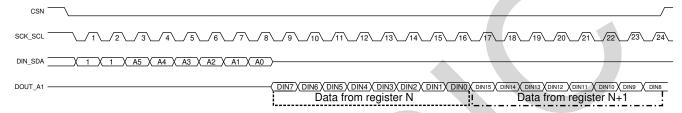

#### 6.10 SPI REGISTER READ CYCLE - BURST

A burst (multi-byte) register read cycle uses the address specified at the beginning of the transaction as the starting register address. Internally the address will auto-increment to the next consecutive address for each additional byte (8-clocks) of data read beyond clock 8.

# NOTE: See (0x0E) Feature Register 2 for address wrap details.

Figure 20. SPI Register Read Cycle - Burst (2 register burst example)

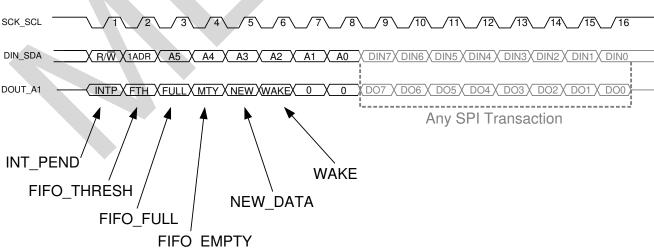

#### **6.11 SPI STATUS OPTION**

The device supports an optional SPI status feature, only in SPI 4-wire mode. This feature is enabled in register (0x0E) Feature Register 2. During the first 6-bits of any SPI transaction (immediately after the falling edge of CSN), the DOUT\_A1 pin will output six status bits related to the device. Following the 6th clock cycle, the device will float the DOUT\_A1 pin before a possible read cycle begins. The status bits sent are shown below:

| Bit 7<br>(First Out) | Bit6        | Bit5      | Bit 4      | Bit 3    | Bit 2 | Bit 1 | Bit 0<br>(Last Out) |  |  |

|----------------------|-------------|-----------|------------|----------|-------|-------|---------------------|--|--|

| INT_PEND             | FIFO_THRESH | FIFO_FULL | FIFO_EMPTY | NEW_DATA | WAKE  | 0     | 0                   |  |  |

| CSN                  | CSN         |           |            |          |       |       |                     |  |  |

| SCK_SCL              |             |           |            |          |       |       |                     |  |  |

Figure 21. SPI Status bits

#### 6.12 SPI HIGH-SPEED MODE

To achieve SPI speed greater than 2MHz, use the following sequence:

- Start SPI at low speed (less than 2MHz)

- Enable SPI mode -

- "SPI\_EN" in section 7.7 (0x0D) Feature Register 1

- Enable high speed SPI mode

- o "SPI\_HS\_EN" in section 7.20 (0x1C) Power Mode Control Register

- Increase SPI speed up to 8MHz

# 7 REGISTER INTERFACE

The device has a simple register interface which allows an SPI or I2C master to configure and monitor all aspects of the device. This section lists an overview of user programmable registers. By convention, bit 0 is the least significant bit (LSB) of a byte register.

# 7.1 REGISTER SUMMARY

| Addr | Name       | Description                | Bit 7            | Bit 6               | Bit 5             | Bit 4              | Bit 3            | Bit 2              | Bit 1              | Bit 0              | POR<br>Value  | R/W <sup>4</sup> |

|------|------------|----------------------------|------------------|---------------------|-------------------|--------------------|------------------|--------------------|--------------------|--------------------|---------------|------------------|

| 0x00 | EXT_STAT_1 | Extended Status 1          | RESV             | RESV                | RESV              | RESV               | 12C_AD0          | RESV               | RESV               | RESV               | 0x00          | R                |

| 0x01 | EXT_STAT_2 | Extended Status 2          | SNIFF_<br>DETECT | SNIFF_EN            | OTP_<br>BUSY      | RESV               | RESV             | RESV               | PD_CLK_<br>STAT    | OVR_<br>DATA       | 0x04          | R                |

| 0x02 | XOUT_LSB   | XOUT_LSB                   | XOUT[7]          | XOUT[6]             | XOUT[5]           | XOUT[4]            | XOUT[3]          | XOUT[2]            | XOUT[1]            | XOUT[0]            | 0x00          | R                |

| 0x03 | XOUT_MSB   | XOUT_MSB                   | XOUT[15]         | XOUT[14]            | XOUT[13]          | XOUT[12]           | XOUT[11]         | XOUT[10]           | XOUT[9]            | XOUT[8]            | 0x00          | R                |

| 0x04 | YOUT_LSB   | YOUT_LSB                   | YOUT[7]          | YOUT[6]             | YOUT[5]           | YOUT[4]            | YOUT[3]          | YOUT[2]            | YOUT[1]            | YOUT[0]            | 0x00          | R                |

| 0x05 | YOUT_MSB   | YOUT_MSB                   | YOUT[15]         | YOUT[14]            | YOUT[13]          | YOUT[12]           | YOUT[11]         | YOUT[10]           | YOUT[9]            | YOUT[8]            | 0x00          | R                |

| 0x06 | ZOUT_LSB   | ZOUT_LSB                   | ZOUT[7]          | ZOUT[6]             | ZOUT[5]           | ZOUT[4]            | ZOUT[3]          | ZOUT[2]            | ZOUT[1]            | ZOUT[0]            | 0x00          | R                |

| 0x07 | ZOUT_MSB   | ZOUT_MSB                   | ZOUT[15]         | ZOUT[14]            | ZOUT[13]          | ZOUT[12]           | ZOUT[11]         | ZOUT[10]           | ZOUT[9]            | ZOUT[8]            | 0x00          | R                |

| 0x08 | STATUS_1   | Status 1                   | INT_PEND         | FIFO_<br>THRESH     | FIFO_FULL         | FIFO_<br>EMPTY     | NEW_<br>DATA     | MODE[2]            | MODE[1]            | MODE[0]            | 0x00          | R                |

| 0x09 | STATUS_2   | Status 2                   | INT_<br>SWAKE    | INT_FIFO_<br>THRESH | INT_FIFO_<br>FULL | INT_FIFO_<br>EMPTY | INT_ACQ          | INT_WAKE           | RESV               | RESV               | 0x00          | R                |

| 0x   | (0A – 0x0C |                            |                  |                     |                   | RESER'             | VED              |                    |                    |                    |               |                  |

| 0x0D | FREG_1     | Feature 1                  | SPI_EN           | I2C_EN              | SPB_EN            | INTSC_EN           | FREEZE           | 0                  | 0                  | 0                  | 0x00          | W                |

| 0x0E | FREG_2     | Feature 2                  | EXT_<br>TRIG_EN  | EXT_<br>TRIG_POL    | FIFO_<br>STREAM   | I2CINT_<br>WRCLRE  | FIFO_<br>STAT_EN | SPI_<br>STAT_EN    | FIFO_<br>BURST     | WRAPA              | 0x00          | W                |

| 0x0F | INIT_1     | Initialization 1           | 0                | 1                   | 0                 | 0                  | 0                | 0                  | 1                  | 0                  | (See<br>note) | wo               |

| 0x10 | MODE_C     | Mode Control               | TRIG_<br>CMD     | Z_AXIS_<br>PD       | Y_AXIS_<br>PD     | X_AXIS_<br>PD      | RESV             | MCTRL[2]           | MCTRL[1]           | MCTRL[0]           | 0x00          | W                |

| 0x11 | RATE_1     | Rate 1                     | 0                | 0                   | 0                 | 0                  | RR[3]            | RR[2]              | RR[1]              | RR[0]              | 0x00          | W                |

| 0x12 | SNIFF_C    | Sniff Control              | STB_RATE<br>[2]  | STB_RATE<br>[1]     | STB_RATE<br>[0]   | 0                  | SNIFF_SR<br>[3]  | SNIFF_SR<br>[2]    | SNIFF_SR<br>[1]    | SNIFF_SR<br>[0]    | 0x00          | W                |

| 0x13 | SNIFFTH_C  | Sniff Threshold<br>Control | SNIFF_<br>MODE   | SNIFF_<br>AND_OR    | SNIFF_<br>TH[5]   | SNIFF_<br>TH[4]    | SNIFF_<br>TH[3]  | SNIFF_<br>TH[2]    | SNIFF_<br>TH[1]    | SNIFF_<br>TH[0]    | 0x00          | W                |

| 0x14 | SNIFFCF_C  | Sniff<br>Configuration     | SNIFF_<br>RESET  | SNIFF_<br>MUX[2]    | SNIFF_<br>MUX[1]  | SNIFF_<br>MUX[0]   | SNIFF_<br>CNTEN  | SNIFF_<br>THADR[2] | SNIFF_<br>THADR[1] | SNIFF_<br>THADR[0] | 0x00          | W                |

| 0x15 | RANGE_C    | Range Resolution Control   | RESV             | RANGE [2]           | RANGE[1]          | RANGE[0]           | RESV             | RES[2]             | RES[1]             | RES[0]             | 0x00          | W                |

| 0x16 | FIFO_C     | FIFO Control               | FIFO_<br>RESET   | FIFO_EN             | FIFO_<br>MODE     | FIFO_TH[4]         | FIFO_TH[3]       | FIFO_TH[2]         | FIFO_TH[1]         | FIFO_TH[0]         | 0x00          | W                |

| 0x17 | INTR_C     | Interrupt Control          | INT_<br>SWAKE    | INT_FIFO_<br>THRESH | INT_FIFO_<br>FULL | INT_FIFO_<br>EMPTY | INT_ACQ          | INT_<br>WAKE       | IAH                | IPP                | 0x00          | R                |

| 0)   | x18 – 0x19 |                            |                  |                     |                   | RESER'             | VED              |                    |                    |                    |               |                  |

| 0x1A | INIT_3     | Initialization 3           | 0                | 0                   | 0                 | 0                  | 0                | 0                  | 0                  | 0                  | 0x00          | RW               |

| 0x1B | SCRATCH    | Scratchpad                 | 0                | 0                   | 0                 | 0                  | 0                | 0                  | 0                  | 0                  | 0x00          | RW               |

| Addr | Name       | Description                  | Bit 7     | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    | POR<br>Value | R/W <sup>4</sup> |  |

|------|------------|------------------------------|-----------|----------|----------|----------|----------|----------|----------|----------|--------------|------------------|--|

| 0x1C | PMCR       | Pow er Mode<br>Control       | SPI_HS_EN | SPM[2]   | SPM[1]   | SPM[0]   | RESV     | CSPM[2]  | CSPM[1]  | CSPM[0]  | 0x00         | W                |  |

| 0>   | (1D – 0x1F |                              |           |          |          | RESE     | SERVED   |          |          |          |              |                  |  |

| 0x20 | DMX        | Drive Motion X               | 0         | 0        | 0        | 0        | DNX      | DPX      | 0        | 1        | 0x00         | W                |  |

| 0x21 | DMY        | Drive Motion Y               | 1         | 0        | 0        | 0        | DNY      | DPY      | 0        | 0        | (See table)  | W                |  |

| 0x22 | DMZ        | Drive Motion Z               | 0         | 0        | 0        | 0        | DNZ      | DPZ      | 0        | 0        | 0x00         | W                |  |

|      | 0x23       |                              | RESERVED  |          |          |          |          |          |          |          |              |                  |  |

| 0x24 | RESET      | Reset                        | RELOAD    | RESET    | RESV     | RESV     | RESV     | RESV     | RESV     | RESV     | 0x00         | W                |  |

| 0:   | x25 – 0x27 | RESERVED                     |           |          |          |          |          |          |          |          |              |                  |  |

| 0x28 | INIT_2     | Initialization<br>Register 2 | 0         | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0x00         | W                |  |

| 0x29 | TRIGC      | Trigger Count                | TRIGC[7]  | TRIGC[6] | TRIGC[5] | TRIGC[4] | TRIGC[3] | TRIGC[2] | TRIGC[1] | TRIGC[0] | 0x00         | W                |  |

| 0x2A | XOFFL      | X-Offset LSB                 | XOFF[7]   | XOFF[6]  | XOFF[5]  | XOFF[4]  | XOFF[3]  | XOFF[2]  | XOFF[1]  | XOFF[0]  | Per chip     | W                |  |

| 0x2B | XOFFH      | X-Offset MSB                 | XGAIN[8]  | XOFF[14] | XOFF[13] | XOFF[12] | XOFF[11] | XOFF[10] | XOFF[9]  | XOFF[8]  | Per chip     | W                |  |

| 0x2C | YOFFL      | Y-Offset LSB                 | YOFF[7]   | YOFF[6]  | YOFF[5]  | YOFF[4]  | YOFF[3]  | YOFF[2]  | YOFF[1]  | YOFF[0]  | Per chip     | W                |  |

| 0x2D | YOFFH      | Y-Offset MSB                 | YGAIN[8]  | YOFF[14] | YOFF[13] | YOFF[12] | YOFF[11] | YOFF[10] | YOFF[9]  | YOFF[8]  | Per chip     | W                |  |

| 0x2E | ZOFFL      | Z-Offset LSB                 | ZOFF[7]   | ZOFF[6]  | ZOFF[5]  | ZOFF[4]  | ZOFF[3]  | ZOFF[2]  | ZOFF[1]  | ZOFF[0]  | Per chip     | W                |  |

| 0x2F | ZOFFH      | Z-Offset MSB                 | ZGAIN[8]  | ZOFF[14] | ZOFF[13] | ZOFF[12] | ZOFF[11] | ZOFF[10] | ZOFF[9]  | ZOFF[8]  | Per chip     | W                |  |

| 0x30 | XGAIN      | X Gain                       | XGAIN[7]  | XGAIN[6] | XGAIN[5] | XGAIN[4] | XGAIN[3] | XGAIN[2] | XGAIN[1] | XGAIN[0] | Per chip     | W                |  |

| 0x31 | YGAIN      | Y Gain                       | YGAIN[7]  | YGAIN[6] | YGAIN[5] | YGAIN[4] | YGAIN[3] | YGAIN[2] | YGAIN[1] | YGAIN[0] | Per chip     | W                |  |

| 0x32 | ZGAIN      | Z Gain                       | ZGAIN[7]  | ZGAIN[6] | ZGAIN[5] | ZGAIN[4] | ZGAIN[3] | ZGAIN[2] | ZGAIN[1] | ZGAIN[0] | Per chip     | W                |  |

| 0;   | x33 – 0x3F |                              |           |          |          | RESE     | RVED     |          |          |          |              |                  |  |

# **Table 14. Register Summary**

$<sup>^{\</sup>rm 4}$  'R' registers are read-only. 'W' registers are read-write. 'WO' registers are write only.

# 7.2 (0X00) EXTENDED STATUS REGISTER 1

This register contains status for the I2C address of the device.

| Addr | Name       | Bit  |      |      |      |         |      | POR  | R/W  |          |         |

|------|------------|------|------|------|------|---------|------|------|------|----------|---------|

| Addi | Addr Name  | 7    | 6    | 5    | 4    | 3       | 2    | 1    | 0    | Value R/ | III/ VV |

| 0x00 | EXT_STAT_1 | RESV | RESV | RESV | RESV | I2C_AD0 | RESV | RESV | RESV | 00000000 | R       |

| Bit   | Name        | Description                                                                                                                                                     |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2:0] | RESV        | Reserved                                                                                                                                                        |

| 3     | I2C_ADO_BIT | Value of I2C slave address obtained from reading the DOUT_A1 pin at POR. If this bit is '1', the 7-bit base address of the I2C slave changes from 0x4C to 0x6C. |

| [7:4] | RESV        | Reserved                                                                                                                                                        |

Table 15. Extended Status Register 1 Settings

# 7.3 (0X01) EXTENDED STATUS REGISTER 2

The device status register reports various conditions of the device data, clock and sniff circuitry.

|      |            |                  | Bit      |          |      |      |      |                 |              |              |     |

|------|------------|------------------|----------|----------|------|------|------|-----------------|--------------|--------------|-----|

| Addr | Name       | 7                | 6        | 5        | 4    | 3    | 2    | 1               | 0            | POR<br>Value | R/W |

| 0x01 | EXT_STAT_2 | SNIFF_<br>DETECT | SNIFF_EN | OTP_BUSY | RESV | RESV | RESV | PD_CLK_<br>STAT | OVR_<br>DATA | 0x04         | RO  |

| Bit   | Name         | Description                                                                                                                                                     |

|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | OVR_DATA     | O: Previous acceleration sample has not been overwritten before read by host     1: Previous acceleration sample was not read by host and has been overwritten. |

| 1     | PD_CLK_STAT  | Returns the power-down status of the clocks.  0: Clocks are enabled.  1: Clocks are disabled.                                                                   |

| [4:2] | RESV         | Reserved                                                                                                                                                        |

| 5     | OTP_BUSY     | OTP VDD status bit: 0: OTP_VDD supply is not enabled, OTP is powered down. 1: OTP_VDD supply is enabled, OTP is powered.                                        |

| 6     | SNIFF_EN     | SNIFF mode enable flag: 0: SNIFF mode is not active. 1: SNIFF mode is active.                                                                                   |

| 7     | SNIFF_DETECT | SNIFF wakeup or detect flag: 0: No sniff event detected. 1: Sniff event detected, move to CWAKE mode.                                                           |

Table 16. Extended Status Register 2 Settings

#### 7.4 (0X02 - 0X07) XOUT, YOUT & ZOUT DATA OUTPUT REGISTERS

The measurements from sensors for the 3-axes are available in these 3 registers. The most-significant bit of the value is the sign bit, and is sign extended to the higher bits.

Software must set only one of the bits SPI\_EN or I2C\_EN in register 0x0D to '1', depending upon if the I2C or SPI interface will be used for external communications. No data will appear in XOUT, YOUT and ZOUT registers if both the I2C\_EN bit and SPI\_EN bit are set to 0 (default).

When the FIFO is enabled, the output of the FIFO is mapped to registers 0x02 to 0x07, and the data has a maximum resolution of 12-bits.

During FIFO reads, software must start a read at address 0x02 and complete a read to address 0x07 for the FIFO pointers to increment correctly.

Once an I2C start bit has been recognized by the device, registers will not be updated until an I2C stop bit has occurred. Therefore, if software desires to read the low and high byte registers 'atomically', knowing that the values have not been changed, it should do so by issuing a start bit, reading one register, then reading the other register then issuing a stop bit. Note that all 6 registers may be read in one burst with the same effect.

| Addr | Name          | Description          | Bit 7        | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0       | POR<br>Value | R/<br>W |

|------|---------------|----------------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|--------------|---------|

| 0x02 | XOUT<br>_LSB  | XOUT LSB<br>Register | XOUT<br>[7]  | XOUT<br>[6]  | XOUT<br>[5]  | XOUT<br>[4]  | XOUT<br>[3]  | XOUT<br>[2]  | XOUT<br>[1] | XOUT<br>[0] | 0x00         | R       |

| 0x03 | XOUT<br>_MSB  | XOUT MSB<br>Register | XOUT<br>[15] | XOUT<br>[14] | XOUT<br>[13] | XOUT<br>[12] | XOUT<br>[11] | XOUT<br>[10] | XOUT<br>[9] | XOUT<br>[8] | 0x00         | R       |

| 0x04 | YOUT<br>_LSB  | YOUT LSB<br>Register | YOUT<br>[7]  | YOUT<br>[6]  | YOUT<br>[5]  | YOUT<br>[4]  | YOUT<br>[3]  | YOUT<br>[2]  | YOUT<br>[1] | YOUT<br>[0] | 0x00         | R       |

| 0x05 | YOUT<br>_MSB  | YOUT MSB<br>Register | YOUT<br>[15] | YOUT<br>[14] | YOUT<br>[13] | YOUT<br>[12] | YOUT<br>[11] | YOUT<br>[10] | YOUT<br>[9] | YOUT<br>[8] | 0x00         | R       |

| 0x06 | ZOUT<br>_LSB( | ZOUT LSB<br>Register | ZOUT<br>[7]  | ZOUT<br>[6]  | ZOUT<br>[5]  | ZOUT<br>[4]  | ZOUT<br>[3]  | ZOUT<br>[2]  | ZOUT<br>[1] | ZOUT<br>[0] | 0x00         | R       |

| 0x07 | ZOUT<br>_MSB  | ZOUT MSB<br>Register | ZOUT<br>[15] | ZOUT<br>[14] | ZOUT<br>[13] | ZOUT<br>[12] | ZOUT<br>[11] | ZOUT<br>[10] | ZOUT<br>[9] | ZOUT<br>[8] | 0x00         | R       |

Table 17. XOUT, YOUT, ZOUT Data Output Registers

### 7.5 (0X08) STATUS REGISTER 1

This register reports the operational mode of the device. Note that the lower 3-bits, the MODE[2:0] field, do not immediately change once a command is written to the MODE register, but may take up to 3 transitions of the heartbeat clock.

|      |          |          | Bit             |           |                |              |         |         |         | 200          |     |

|------|----------|----------|-----------------|-----------|----------------|--------------|---------|---------|---------|--------------|-----|

| Addr | Name     | 7        | 6               | 5         | 4              | 3            | 2       | 1       | 0       | POR<br>Value | R/W |

| 0x08 | STATUS_1 | INT_PEND | FIFO_<br>THRESH | FIFO_FULL | FIFO_<br>EMPTY | NEW_<br>DATA | MODE[2] | MODE[1] | MODE[0] | 00000000     | RO  |

| Bit   | Name      |           | Desc    | ription                                                                                                                                                      |

|-------|-----------|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2:0] | MODE[2:0] | Bit Field | Mode    | Comments                                                                                                                                                     |

|       |           | 000       | SLEEP   | Lowest power mode, regulators on, no clock activity, partial chip power-down                                                                                 |

|       |           | 001       | STANDBY | Low power mode, no sampling, clocks active.                                                                                                                  |

|       |           | 010       | SNIFF   | Sniff activity detection mode,<br>sniff enabled, sniff sampling, no<br>FIFO operations, automatically<br>transition to CWAKE mode upon<br>activity detection |

|       |           | 011       | RESV    | Reserved                                                                                                                                                     |

|       |           | 100       | RESV    | Reserved                                                                                                                                                     |

|       |           | 101       | CWAKE   | Continuous wake. Active XYZ sampling. Sniff circuitry not active.                                                                                            |

|       |           | 110       | SWAKE   | Use Sniff logic, main XYZ pipeline and optional FIFO at the same time; highest power consumption                                                             |

|   |             | 111                                                                                                                                                                                                                       | TRIG                                    | Trigger mode, 1 to 254 samples or continuous, return to sleep upon completion |  |  |  |  |

|---|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| 3 | NEW_DATA    | 0: No new sample data has arrived since last read.  1: New sample data has arrived and has been written to FIFO/registers. This bit is always enabled and valid, regardless of the settings of any interrupt enable bits. |                                         |                                                                               |  |  |  |  |

| 4 | FIFO_EMPTY  | 0: FIFO has one or more samples in storage (level) 1: FIFO is empty (level) (default). This bit is set to 1 immediately after device power-up or device reset.                                                            |                                         |                                                                               |  |  |  |  |

| 5 | FIFO_FULL   |                                                                                                                                                                                                                           | e or 1 or more sam<br>32 samples are us | uples (up to 32) (level).<br>ed (level).                                      |  |  |  |  |

| 6 | FIFO_THRESH | 0: Amount of data in FIFO is less than the threshold (level) 1: Amount of data in FIFO is equal to or greater than the threshold (level)                                                                                  |                                         |                                                                               |  |  |  |  |

| 7 | INT_PEND    |                                                                                                                                                                                                                           |                                         | register 0x09 (level)<br>pending in register 0x09 (logical                    |  |  |  |  |

**Table 18. Status Register 1 Settings**

#### 7.6 (0X09) STATUS REGISTER 2

This register reports the state of the interrupts ('0' means not pending; '1' means pending). A bit in this register will only be set if the corresponding interrupt enable is set to '1' in (0x17) Interrupt Control Register. Interrupts can be cleared in the following ways using (0x0E) Feature Register 2 bit 4:

InterfaceMethodI2C clearing method (default)Read Register 0x09I2C clearing method (optional)Write Register 0x09SPI clearing methodWrite Register 0x09

|      |          |               | Bit                 |                   |                    |         |          |      |      |              |     |

|------|----------|---------------|---------------------|-------------------|--------------------|---------|----------|------|------|--------------|-----|

| Addr | Name     | 7             | 6                   | 5                 | 4                  | 3       | 2        | 1    | 0    | POR<br>Value | R/W |

| 0x09 | STATUS_2 | INT_<br>SWAKE | INT_FIFO_<br>THRESH | INT_FIFO_<br>FULL | INT_FIFO_<br>EMPTY | INT_ACQ | INT_WAKE | RESV | RESV | 00000000     | RO  |

| Bit   | Name           | Description                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [1:0] | Reserved       | Reserved.                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 2     | INT_WAKE       | This interrupt will transition when the accelerometer automatically moves from SNIFF to CWAKE. Once cleared, another SNIFF to CWAKE event must take place to retrigger it.                                                                                                                     |  |  |  |  |  |

| 3     | INT_ACQ        | This interrupt will transition when a new sample is acquired. This flag stays high upon the first sample acquired and will not rearm unless cleared. Only active in CWAKE and TRIG modes.                                                                                                      |  |  |  |  |  |

| 4     | INT_FIFO_EMPTY | This interrupt will transition when the FIFO is empty. This flag stays high upon the first empty condition and will not rearm unless cleared. The FIFO empty condition must be negated (e.g. the FIFO must become 'not' empty), and then empty again for the INT_FIFO_EMPTY flag to retrigger. |  |  |  |  |  |

| 5 | INT_FIFO_FULL   | This interrupt will transition when the FIFO is full (32 XYZ samples). This flag stays high upon the first full condition and will not rearm unless cleared. The FIFO full condition must be negated (e.g. the FIFO must become 'not' full), and then full again for the INT_FIFO_FULL flag to retrigger.                                                                             |

|---|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | INT_FIFO_THRESH | This interrupt will transition when the FIFO sample count is equal to or greater than the threshold count 0x16[4:0]. This flag stays high upon the first threshold condition and will not rearm unless cleared.                                                                                                                                                                       |

| 7 | INT_SWAKE       | This interrupt will transition when the SNIFF block has detected an event only when the device is in SWAKE mode. Once an SWAKE interrupt is generated, the SNIFF block stops processing new events until the interrupt is cleared and the SNIFF block is reset. Optionally, the SNIFF block can be reset at the same time INT_SWAKE is cleared – see (0x0D) Feature Register 1 bit 4. |

**Table 19. Status Register 2 Settings**

#### 7.7 (0X0D) FEATURE REGISTER 1

This register is used to select the interface mode as well as the operation style of the FIFO and interrupt in SWAKE mode.

NOTE: Software must set only one of the bits SPI\_EN or I2C\_EN in register 0x0D to '1', depending upon if the I2C or SPI interface will be used for external communications. No data will appear in XOUT, YOUT and ZOUT registers if both the I2C\_EN bit and SPI\_EN bit are set to 0 (default).

|      |        |        | Bit    |         |          |        |   |   |   |              |     |

|------|--------|--------|--------|---------|----------|--------|---|---|---|--------------|-----|

| Addr | Name   | 7      | 6      | 5       | 4        | 3      | 2 | 1 | 0 | POR<br>Value | R/W |

| 0x0D | FREG_1 | SPI_EN | I2C_EN | SPI3_EN | INTSC_EN | FREEZE | 0 | 0 | 0 | 00000000     | RO  |

| Bit   | Name                            | Description                                                                                                                                                                                                |

|-------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2:0] | <must '000'="" write=""></must> | Software must always write '000' to these 3 bits                                                                                                                                                           |

| 3     | FREEZE                          | This bit is designed to be used with "FIFO stream mode" (register 0x0E bit 5) where the FIFO is configured to continuously capture new samples and flush the oldest after reaching a FIFO full state.      |

|       |                                 | 0: FIFO operates in standard mode, does not stop capturing data in SWAKE interrupt (default).                                                                                                              |

|       |                                 | 1: FIFO stops capturing on SWAKE interrupt, software can examine the conditions which generated the SWAKE event.                                                                                           |

| 4     | INTSC_EN                        | Once an SWAKE interrupt is generated, the SNIFF block stops processing new events until cleared. Enabling this bit allows the SNIFF block to be reset at the same time the INT_SWAKE interrupt is cleared. |

|       |                                 | 0: Do not re-arm SNIFF block following a SWAKE event (requires the SNIFF block to be reset by exiting SWAKE mode). (default)                                                                               |

|       |                                 | 1: Clearing the SWAKE interrupt clears and rearms the SNIFF block for subsequent detections (device may stay in SWAKE mode and continuing processing subsequent SWAKE events once interrupt is cleared).   |

| 5 | SPI3_EN | 0: SPI interface is 4-wire 1: SPI interface is 3-wire (DOUT_A1 is the bidirectional pin)                                                                                                                     |

|---|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6 | I2C_EN  | O: Device interface is still defined as it was at power-up but no data will appear in XOUT, YOUT and ZOUT registers if both this bit and SPI_EN are set to 0 (default).  1: Disables any SPI communications. |

| 7 | SPI_EN  | O: Device interface is still defined as it was at power-up but no data will appear in XOUT, YOUT and ZOUT registers if both this bit and I2C_EN are set to 0 (default).  1: Disables any I2C communications. |

**Table 20. Feature Register 1 Settings**

## 7.8 (OX0E) FEATURE REGISTER 2

This register allows selection of various features for the FIFO, external trigger input, method of interrupt clearing and burst address wrapping.

|      |        |                 | Bit              |                 |                   |                  |                 |                |       |              |     |

|------|--------|-----------------|------------------|-----------------|-------------------|------------------|-----------------|----------------|-------|--------------|-----|

| Addr | Name   | 7               | 6                | 5               | 4                 | 3                | 2               | 1              | 0     | POR<br>Value | R/W |

| 0x0E | FREG_2 | EXT_<br>TRIG_EN | EXT_<br>TRIG_POL | FIFO_<br>STREAM | I2CINT_<br>WRCLRE | FIFO_<br>STAT_EN | SPI_<br>STAT_EN | FIFO_<br>BURST | WRAPA | 00000000     | RO  |

| Bit | Name       | Description                                                                                                                                                                                                                                  |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|