## Freescale Semiconductor Data Sheet: Technical Data

Document Number: SCF5250EC Rev. 1.3, 07/2006

SCF5250

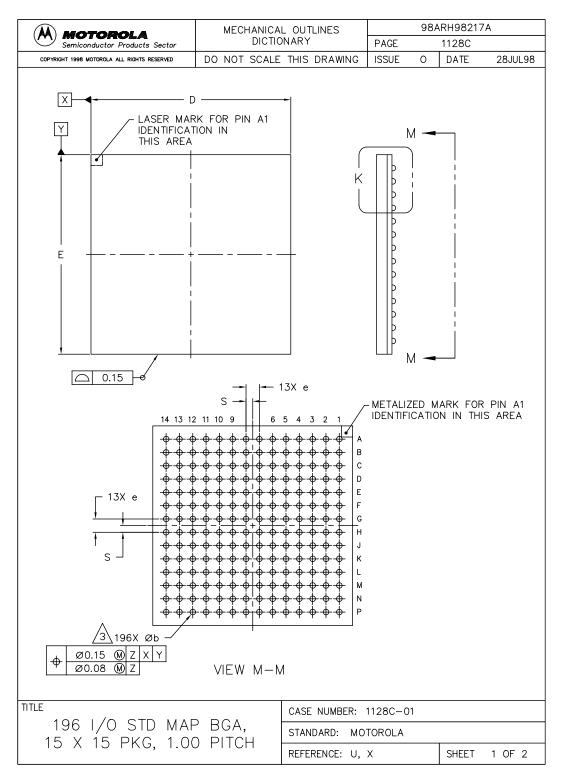

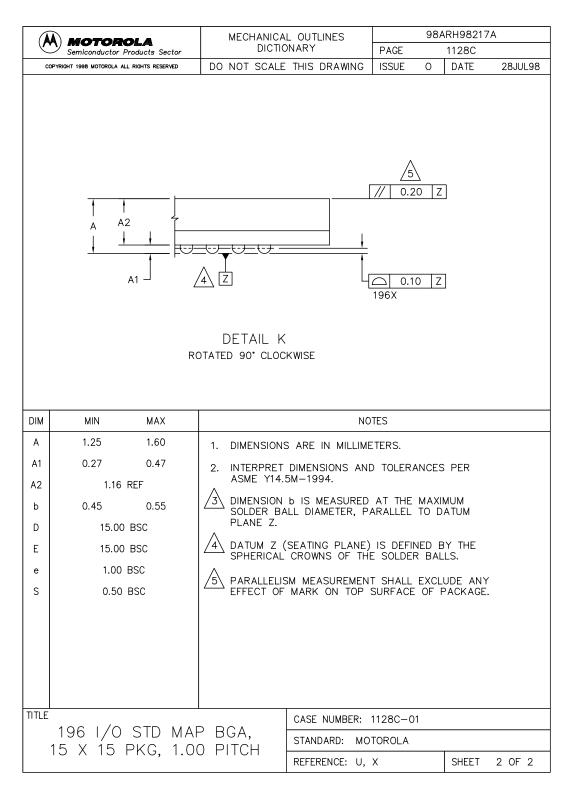

Package Information MAPBGA–196 LQFP-144

Ordering Information: See Table 1 on page 2

# SCF5250 Integrated ColdFire® Microprocessor Data Sheet

# 1 Introduction

This document provides an overview of the SCF5250 ColdFire<sup>®</sup> processor and general descriptions of SCF5250 features and its various modules.

The SCF5250 was designed as a system controller/decoder for compressed audio music players, especially portable and automotive CD and hard disk drive players. The 32-bit ColdFire core with Enhanced Multiply Accumulate (EMAC) unit provides optimum performance and code density for the combination of control code and signal processing required for audio decoding and post processing, file management, and system control.

Low power features include a hardwired CD ROM decoder, advanced 0.13um CMOS process technology, 1.2V core power supply, and on-chip 128KByte SRAM that enables Windows Media Audio (WMA) decoding without the need for external DRAM in CD applications.

The SCF5250 is also an excellent general purpose system controller with over 110 Dhrystone 2.1 MIPS @ 120MHz performance at a very competitive price. The

#### Contents

| 1 | Introduction 1                     |   |

|---|------------------------------------|---|

| 2 | SCF5250 Block Diagram 8            | 3 |

| 3 | Signal Descriptions 8              | 3 |

| 4 | Electrical Characteristics 21      |   |

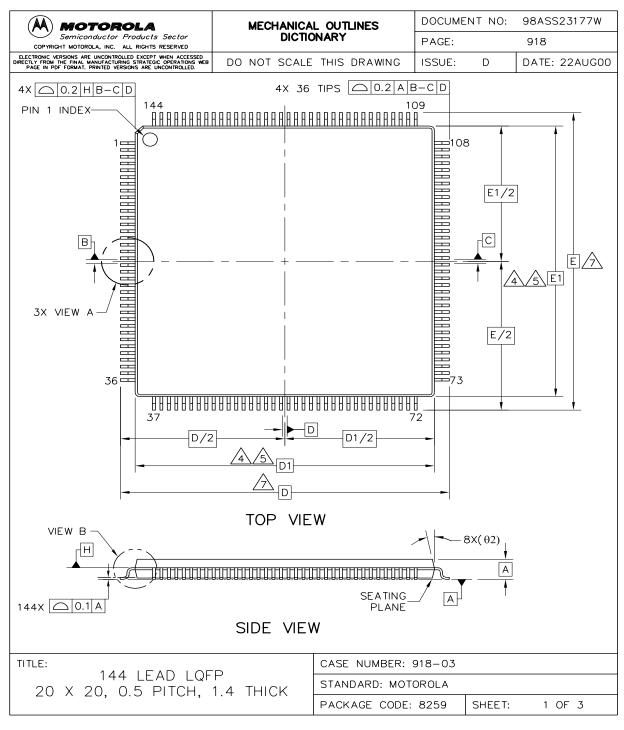

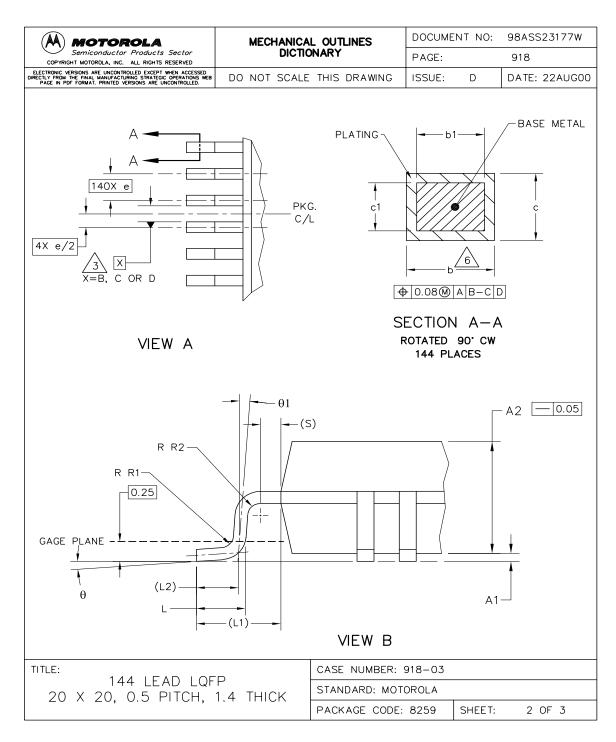

| 5 | Pin-Out and Package Information 36 | ; |

6 Product Documentation ..... 55

This document contains information on a product under development. Freescale reserves the right to change or discontinue this product without notice. © Freescale Semiconductor, Inc., 2006. All rights reserved.

integrated peripherals and enhanced MAC unit allow the SCF5250 to replace both the microcontroller and the DSP in certain applications. Most peripheral pins can also be remapped as General Purpose I/O pins.

# 1.1 Orderable Part Numbers

Table 1 lists the orderable part numbers for the SCF5250 processor.

| Orderable Part<br>Number   | Maximum Clock<br>Frequency | Package Type    | Operating Temperature<br>Range | Part Status |

|----------------------------|----------------------------|-----------------|--------------------------------|-------------|

| SCF5250LPV100              | 100 MHz                    | 144 pin QFP     | -20°C to 70°C                  | Leaded      |

| SCF5250LAG100              | 100 MHz                    | 144 pin QFP     | -20°C to 70°C                  | Lead Free   |

| SCF5250PV120               | 120 MHz                    | 144 pin QFP     | -20°C to 70°C                  | Leaded      |

| SCF5250AG120               | 120 MHz                    | 144 pin QFP     | -20°C to 70°C                  | Lead Free   |

| SCF5250DAG120 <sup>1</sup> | 120 MHz                    | 144 pin QFP     | -20°C to 70°C                  | Lead Free   |

| SCF5250EAG120 <sup>2</sup> | 120 MHz                    | 144 pin QFP     | -20°C to 70°C                  | Lead Free   |

| SCF5250CPV120              | 120 MHz                    | 144 pin QFP     | -40°C to 85°C                  | Leaded      |

| SCF5250CAG120              | 120 MHz                    | 144 pin QFP     | -40°C to 85°C                  | Lead Free   |

| SCF5250VM120               | 120 MHz                    | 196 ball MAPBGA | -20°C to 70°C                  | Lead Free   |

Table 1. Orderable Part Numbers

SCF5250DAG120—This device has the same feature set, pin assignment and specification as SCF5250AG120 with the addition of including the cost of the MP3 decoder royalty to be paid to Thomson Licensing S.A. for use of the MP3 patent rights described at <u>http://mp3licensing.com/patents/index.html</u>.

<sup>2</sup> SCF5250EAG120—This device has the same feature set, pin assignment and specification as SCF5250AG120 with the addition of including the cost of the MP3 encoder and decoder royalty to be paid to Thomson Licensing S.A. for use of the MP3 patent rights described at <a href="http://mp3licensing.com/patents/index.html">http://mp3licensing.com/patents/index.html</a>.

# 1.2 SCF5250 Features

This section provides brief descriptions of the features of the SCF5250 processor.

# 1.2.1 ColdFire V2 Core

The ColdFire processor Version 2 core consists of two independent, decoupled pipeline structures to maximize performance while minimizing core size. The instruction fetch pipeline (IFP) is a two-stage pipeline for prefetching instructions. The prefetched instruction stream is then gated into the two-stage operand execution pipeline (OEP), which decodes the instruction, fetches the required operands, and then executes the required function. Because the IFP and OEP pipelines are decoupled by an instruction buffer that serves as a FIFO queue, the IFP can prefetch instructions in advance of their actual use by the OEP, which minimizes time stalled waiting for instructions. The OEP is implemented in a two-stage pipeline featuring a traditional RISC data path with a dual-read-ported register file feeding an arithmetic/logic unit (ALU).

# 1.2.2 DMA Controller

The SCF5250 provides four fully programmable DMA channels for quick data transfer. Single and dual address mode is supported with the ability to program bursting and cycle stealing. Data transfer is selectable as 8, 16, 32, or 128-bits. Packing and unpacking is supported.

Two internal audio channels and the dual UART can be used with the DMA channels. All channels can perform memory to memory transfers. The DMA controller has a user-selectable, 24- or 16-bit counter and a programmable DMA exception handler.

External requests are not supported.

## 1.2.3 Enhanced Multiply and Accumulate Module (EMAC)

The integrated EMAC unit provides a common set of DSP operations and enhances the integer multiply instructions in the ColdFire architecture. The EMAC provides functionality in three related areas:

- 1. Faster signed and unsigned integer multiplies

- 2. New multiply-accumulate operations supporting signed and unsigned operands

- 3. New miscellaneous register operations

Multiplies of 16x16 and 32x32 with 48-bit accumulates are supported in addition to a full set of extensions for signed and unsigned integers plus signed, fixed-point fractional input operands. The EMAC has a single-clock issue for 32x32-bit multiplication instructions and implements a four-stage execution pipeline.

### 1.2.4 Instruction Cache

The instruction cache improves system performance by providing cached instructions to the execution unit in a single clock. The SCF5250 processor uses a 8K-byte, direct-mapped instruction cache to achieve 107 MIPS at 120 MHz. The cache is accessed by physical addresses, where each 16-byte line consists of an address tag and a valid bit. The instruction cache also includes a bursting interface for 16-bit and 8-bit port sizes to quickly fill cache lines.

### 1.2.5 Internal 128-KByte SRAM

The 128-KByte on-chip SRAM is available in two banks, SRAM0 (64K) and SRAM1 (64K). It provides one clock-cycle access for the ColdFire core. This SRAM can store processor stack and critical code or data segments to maximize performance. Memory in SRAM1 can be accessed under DMA.

# 1.2.6 SDRAM Controller

The SCF5250 SDRAM controller provides a glueless interface for one bank of SDRAM up to 32 MB (256 Mbits). The controller supports a 16-bit data bus. A unique addressing scheme allows for increases in system memory size without rerouting address lines and rewiring boards. The controller operates in page mode, non-page mode, and burst-page mode and supports SDRAMS.

### 1.2.7 System Interface

The SCF5250 provides a glueless interface to 16-bit port size SRAM, ROM, and peripheral devices with independent programmable control of the assertion and negation of chip-select and write-enable signals.

The SCF5250 also supports bursting ROMs.

### 1.2.8 External Bus Interface

The bus interface controller transfers information between the ColdFire core or DMA and memory, peripherals, or other devices on the external bus. The external bus interface provides 23 bits of address bus space, a 16-bit data bus, Output Enable, and Read/Write signals. This interface implements an extended synchronous protocol that supports bursting operations.

### 1.2.9 Serial Audio Interfaces

The SC5250 digital audio interface provides three serial Philips IIS/Sony EIAJ interfaces. One interface is a 4-pin (1 bit clock, 1 word clock, 1 data in, 1 data out), the other two interfaces are 3-pin (1 bit clock, 1 word clock, 1 data in or out). The serial interfaces have no limit on minimum sampling frequency. Maximum sampling frequency is determined by maximum frequency on bit clock input. This is 1/3 the frequency of the internal system clock.

### 1.2.10 IEC958 Digital Audio Interfaces

The SCF5250 has one digital audio input interface, and one digital audio output interface. The single output carries the consumer "c" channel.

### 1.2.11 Audio Bus

The audio interfaces connect to an internal bus that carries all audio data. Each receiver places its received data on the audio bus and each transmitter takes data from the audio bus for transmission. Each transmitter has a source select register.

In addition to the audio interfaces, there are six CPU accessible registers connected to the audio bus. Three of these registers allow data reads from the audio bus and allow selection of the audio source. The other three register provide a write path to the audio bus and can be selected by transmitters as the audio source. Through these registers, the CPU has access to the audio samples for processing.

Audio can be routed from a receiver to a transmitter without the data being processed by the core so the audio bus can be used as a digital audio data switch. The audio bus can also be used for audio format conversion.

### 1.2.12 CD-ROM Encoder/Decoder

The SCF5250 is capable of processing CD-ROM sectors in hardware. Processing is compliant with CD-ROM and CD-ROM XA standards.

The CD-ROM decoder performs following functions in hardware:

- Sector sync recognition

- Descrambling of sectors

- Verification of the CRC checksum for Mode 1, Mode 2 Form 1, and Mode 2 Form 2 sectors

- Third-layer error correction is not performed

The CD-ROM encoder performs following functions in hardware:

- Sector sync recognition

- Scrambling of sectors

- Insertion of the CRC checksum for Mode 1, Mode 2 Form 1, and Mode 2 Form 2 sectors.

- Third-layer error encoding needs to be done in software. This can use approximately 5–10 MHz of performance for single-speed.

### 1.2.13 Dual UART Module

Two full-duplex UARTs with independent receive and transmit buffers are in this module. Data formats can be 5, 6, 7, or 8 bits with even, odd, or no parity, and up to 2 stop bits in 1/16 increments. Four-byte receive buffers and two-byte transmit buffers minimize CPU service calls. The Dual UART module also provides several error-detection and maskable-interrupt capabilities. Modem support includes request-to-send (RTS) and clear-to-send (CTS) lines.

The system clock provides the clocking function from a programmable prescaler. You can select full duplex, auto-echo loopback, local loopback, and remote loopback modes. The programmable Dual UARTs can interrupt the CPU on various normal or error-condition events.

### 1.2.14 Queued Serial Peripheral Interface QSPI

The QSPI module provides a serial peripheral interface with queued transfer capability. It supports up to 16 stacked transfers at a time, making CPU intervention between transfers unnecessary. Transfers of up to 15 Mbits/second are possible at a CPU clock of 120 MHz. The QSPI supports master mode operation only.

### 1.2.15 Timer Module

The timer module includes two general-purpose timers, each of which contains a free-running 16-bit timer. Timer0 has an external pin TOUT0, which can be used in Output Compare mode. This mode triggers an external signal or interrupts the CPU when the timer reaches a set value, and can also generate waveforms on TOUT0.

The timer unit has an 8-bit prescaler that allows programming of the clock input frequency, which is derived from the system clock. In addition to the  $\div 1$  and  $\div 16$  clock derived from the bus clock (CPU clock / 2), the programmable timer-output pins either generate an active-low pulse or toggle the outputs.

## 1.2.16 IDE and SmartMedia Interfaces

The SCF5250 system bus allows connection of an IDE hard disk drive or SmartMedia flash card with a minimum of external hardware. The external hardware consists of bus buffers for address and data and are intended to reduce the load on the bus and prevent SDRAM and Flash accesses to propagate to the IDE bus. The control signals for the buffers are generated in the SCF5250.

Low cost version SCF5250LPV100 and SCF5250LAG100 does not run production test for the IDE/CF/SD/MMC interfaces. Freescale does not guarantee these interfaces will work on these two devices.

### 1.2.17 Analog/Digital Converter (ADC)

The six channel ADC is a based on the Sigma-Delta concept with 12-bit resolution. Both the analogue comparator and digital sections of the ADC are provided internally. An external integrator circuit (resistor/capacitor) is required, which is driven by the ADC output. A software interrupt is provided when the ADC measurement cycle is complete.

# 1.2.18 I<sup>2</sup>C Module

The two-wire  $I^2C$  bus interface, which is compliant with the Philips  $I^2C$  bus standard, is a bidirectional serial bus that exchanges data between devices. The  $I^2C$  bus minimizes the interconnection between devices in the end system and is best suited for applications that need occasional bursts of rapid communication over short distances among several devices. Bus capacitance and the number of unique addresses limit the maximum communication length and the number of devices that can be connected.

### 1.2.19 Chip-Selects

Up to four programmable chip-select outputs provide signals that enable glueless connection to external memory and peripheral circuits. The base address, access permissions and automatic wait-state insertion are programmable with configuration registers. These signals also interface to 16-bit ports.

CS0 is active after reset to provide boot-up from external FLASH/ROM.

### 1.2.20 GPIO Interface

A total of 60 General Purpose inputs and 57 General Purpose outputs are available. These are multiplexed with various other signals. Seven of the GPIO inputs have edge sensitive interrupt capability.

### 1.2.21 Interrupt Controller

The interrupt controller provides user-programmable control of a total of 57 interrupts. There are 49 internal interrupt sources. In addition, there are 7 GPIOs where interrupts can be generated on the rising or falling edge of the pin. All interrupts are autovectored and interrupt levels are programmable.

# 1.2.22 JTAG

To help with system diagnostics and manufacturing testing, the SCF5250 includes dedicated user-accessible test logic that complies with the IEEE 1149.1A standard for boundary scan testability, often referred to as Joint Test Action Group, or JTAG. For more information, refer to the IEEE 1149.1A standard. Freescale provides BSDL files for JTAG testing.

## 1.2.23 System Debug Interface

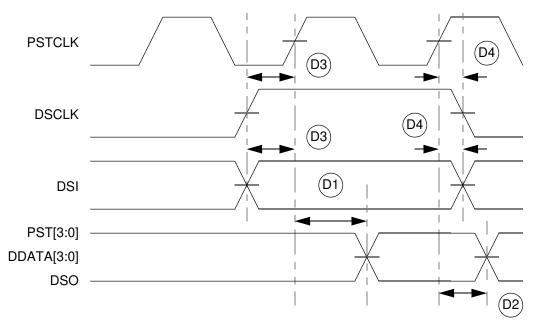

The ColdFire processor core debug interface supports real-time instruction trace and debug, plus background-debug mode. A background-debug mode (BDM) interface provides system debug.

In real-time instruction trace, four status lines provide information on processor activity in real time (PST pins). A four-bit wide debug data bus (DDATA) displays operand data and change-of-flow addresses, which helps track the machine's dynamic execution path.

# 1.2.24 Crystal and On-Chip PLL

Typically, an external 16.92 MHz or 33.86 MHz clock input is used for CD R/W applications, while an 11.2896 MHz clock is more practical for Portable CD player applications. However, the on-chip programmable PLL, which generates the processor clock, allows the use of almost any low frequency external clock (5-35 MHz).

Two clock outputs (MCLK1 and MCLK2) are provided for use as Audio Master Clock. The output frequencies of both outputs are programmable to Fxtal, Fxtal/2, Fxtal/3, and Fxtal/4. The Fxtal/3 option is only available when the 33.86 MHz crystal is connected.

The SCF5250 supports VCO operation of the oscillator by means of a 16-bit pulse density modulation output. Using this mode, it is possible to lock the oscillator to the frequency of an incoming IEC958 or IIS signal. The maximum trim depends on the type and design of the oscillator. Typically a trim of +/- 100 ppm can be achieved with a crystal oscillator and over +/- 1000 ppm with an LC oscillator.

### 1.2.25 Boot ROM

The boot ROM on the SCF5250 serves to boot the CPU in designs which do not have external Flash memory or ROM. Typically this occurs in systems which have a separate MCU to control the system, and/or the SCF5250 is used as a stand-alone decoder.

The SCF5250 can be booted in one of three modes:

- External ROM

- Internal ROM Master mode boots from I2C, SPI, or IDE

- Internal ROM Slave mode boots from I2C or UART

### 1.2.26 Voltage Regulator

The SCF5250 contains an on-chip linear regulator that generates 1.2V from a 3.3V input. The regulator is self-contained and drives the 1.2V core voltage out on one pin that can be used to power the core supply

pins at the board level. In battery powered portable applications, it is recommended that an external dc-dc converter be used to generate the 1.2V core voltage to minimize power consumption.

# 2 SCF5250 Block Diagram

**CD ROM** Flash I<sup>2</sup>S Rx I<sup>2</sup>S Tx block encode Media Int **x2 x**3 & decode IDE SPDIF 12-bit **UART x2** Interface ADC Тх DMAs / SPDIF I<sup>2</sup>C x2 **QSPI Timers** Rx 1.2V GPI/O PLL **BDM** Regulator Boot **JTAG** 128K ROM SRAM **8K** Oscillator I-Cache **V2** EMAC **System SDRAM Ctr ColdFire**<sup>®</sup> Bus Core Controller **Chip Selects**

Figure 1 illustrates the functional block diagram of the SCF5250 processor.

Figure 1. SCF5250 Block Diagram

# 3 Signal Descriptions

This section describes the SCF5250 processor's input and output signals. The signal descriptions shown in Table 2 are grouped according to relevant functionality.

#### Table 2. SCF5250 Signal Index

| Signal Name                          | Signal Name Mnemonic Function              |                                                                                                                               | Input/<br>Output | Reset<br>State |

|--------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|

| Address                              | A[24:1]<br>A[23]/GPO54                     | 24 address lines, address line 23<br>multiplexed with GPO54 and address 24<br>is multiplexed with A20 (SDRAM access<br>only). | Out              | Х              |

| Read-write control                   | R/W                                        | Bus write enable - indicates if read or write cycle in progress                                                               | Out              | Н              |

| Output enable                        | OE                                         | Output enable for asynchronous<br>memories connected to chip selects                                                          | Out              | negated        |

| Data                                 | D[31:16]                                   | Data bus used to transfer word data                                                                                           | In/Out           | Hi-Z           |

| Synchronous row address strobe       | SDRAS/GPIO59                               | Row address strobe for external SDRAM.                                                                                        | Out              | negated        |

| Synchronous column<br>address strobe | SDCAS/GPIO39                               | Column address strobe for external SDRAM                                                                                      | Out              | negated        |

| SDRAM write enable                   | SDWE/GPIO38                                | Write enable for external SDRAM                                                                                               | Out              | negated        |

| SDRAM upper byte enable              | SDUDQM/GPO53                               | Indicates during write cycle if high byte is written                                                                          | Out              | -              |

| SDRAM lower byte enable              | SDLDQM/GPO52                               | Indicates during write cycle if low byte is written                                                                           | Out              | -              |

| SDRAM chip selects                   | SD_CS0/GPIO60                              | SDRAM chip select                                                                                                             | In/Out           | negated        |

| SDRAM clock enable                   | BCLKE/GPIO63                               | SDRAM clock enable                                                                                                            | Out              | -              |

| System clock                         | BCLK/GPIO40                                | SDRAM clock output                                                                                                            | In/Out           | _              |

| ISA bus read strobe                  | IDE-DIOR/GPIO31<br>(CS2)                   | There is 1 ISA bus read strobe and 1 ISA bus write strobe. They allow connection                                              | In/Out           | -              |

| ISA bus write strobe                 | IDE-DIOW/GPIO32<br>(CS2)                   | of one independent ISA bus peripherals,<br>e.g. an IDE slave device.                                                          | In/Out           | -              |

| ISA bus wait signal                  | IDE-IORDY/GPIO33                           | ISA bus wait line - available for both busses                                                                                 | In/Out           | _              |

| Chip Selects[2:0]                    | CS0/CS4<br>CS1/QSPI_CS3/GPIO28             | Enables peripherals at programmed<br>addresses.<br>CS[0] provides boot ROM selection                                          | Out<br>In/Out    | negated        |

| Buffer enable 1                      | BUFENB1/GPIO29                             | Two programmable buffer enables allow                                                                                         | In/Out           | _              |

| Buffer enable 2                      | BUFENB2/GPIO30                             | seamless steering of external buffers to split data and address bus in sections.                                              | In/Out           | -              |

| Transfer acknowledge                 | TA/GPIO12                                  | Transfer Acknowledge signal                                                                                                   | In/Out           | -              |

| Wake Up                              | WAKE_UP/GPIO21                             | Wake-up signal input                                                                                                          | In               | -              |

| Serial Clock Line                    | SCL0/SDATA1_BS1/GPIO41<br>SCL1/TXD1/GPIO10 | Clock signal for Dual I <sup>2</sup> C module operation                                                                       | In/Out           | _              |

| Serial Data Line                     | SDA0/SDATA3/GPIO42<br>SDA1/RXD1/GPIO44     | Serial data port for second I <sup>2</sup> C module operation                                                                 | In/Out           | -              |

| Receive Data                         | SDA1/RXD1/GPIO44<br>RXD0/GPIO46            | Signal is receive serial data input for DUART                                                                                 | In               | -              |

| Signal Name          | Mnemonic                                                                                     | Function                                                    | Input/<br>Output | Reset<br>State |  |

|----------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|----------------|--|

| Transmit Data        | SCL1/TXD1/GPIO10<br>TXD0/GPIO45                                                              | Signal is transmit serial data output for DUART             | Out              | -              |  |

| Request-To-Send      | DDATA3/RTS0/GPIO4<br>DDATA1/RTS1/SDATA2_BS2/GPIO2                                            | DUART signals a ready to receive data query                 | Out              | Out –          |  |

| Clear-To-Send        | DDATA2/CTSO/GPIO3<br>DDATA0/CTS1/SDATA0_SDIO1/GPIO1                                          | Signals to DUART that data can be transmitted to peripheral | In               | In –           |  |

| Timer Output         | SDATAO1/TOUT0/GPIO18                                                                         | Capable of output waveform or pulse generation              | Out              | _              |  |

| IEC958 inputs        | EBUIN1/GPIO36<br>EBUIN2/SCLK_OUT/GPIO13<br>EBUIN3/CMD_SDIO2/GPIO14<br>QSPI_CS0/EBUIN4/GPIO15 | audio interfaces IEC958 inputs                              | In               | -              |  |

| IEC958 outputs       | EBUOUT1/GPIO37<br>QSPI_CS1/EBUOUT2/GPIO16                                                    | audio interfaces IEC958 outputs                             | Out              | -              |  |

| Serial data in       | SDATAI1/GPIO17<br>SDATAI3/GPIO8                                                              | audio interfaces serial data inputs                         | In               | -              |  |

| Serial data out      | SDATAO1/TOUT0/GPIO18<br>SDATAO2/GPIO34                                                       | audio interfaces serial data outputs                        | In/Out<br>Out    | -              |  |

| Word clock           | LRCK1/GPI019<br>LRCK2/GPI023<br>LRCK3/GPI043/AUDI0_CLOCK                                     | audio interfaces serial word clocks                         | In/Out           | -              |  |

| Bit clock            | SCLK1/GPIO20<br>SCLK2/GPIO22<br>SCLK3/GPIO35                                                 | audio interfaces serial bit clocks                          | In/Out           | -              |  |

| Serial input         | EF/GPIO6                                                                                     | error flag serial in                                        | In/Out           | _              |  |

| Serial input         | CFLG/GPIO5                                                                                   | C-flag serial in                                            | In/Out           | _              |  |

| Subcode clock        | RCK/QSPI_DIN/QSPI_DOUT/<br>GPIO26                                                            | audio interfaces subcode clock                              | In/Out           | -              |  |

| Subcode sync         | QSPI_DOUT/SFSY/GPIO27                                                                        | audio interfaces subcode sync                               | In/Out           | _              |  |

| Subcode data         | QSPI_CLK/SUBR/GPIO25                                                                         | audio interfaces subcode data                               | In/Out           | _              |  |

| Clock frequency trim | XTRIM/GPIO0                                                                                  | clock trim control                                          | Out              | _              |  |

| Audio clocks out     | MCLK1/GPIO11<br>QSPI_CS2/MCLK2/GPIO24                                                        | DAC output clocks                                           | Out              | -              |  |

| Audio clock in       | LRCK3/GPIO43/AUDIO_CLOCK                                                                     | Optional Audio clock Input                                  | _                | _              |  |

#### Table 2. SCF5250 Signal Index (continued)

| Signal Name                               | Mnemonic                                                                                                 | Function                                                                                   | Input/<br>Output | Reset<br>State |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------|----------------|

| Memory Stick/<br>Secure Digital interface | EBUIN3/CMD_SDIO2/GPIO14                                                                                  | Secure Digital command lane<br>Memory Stick interface 2 data I/O                           | In/Out           | _              |

|                                           | EBUIN2/SCLK_OUT/GPIO13                                                                                   | Clock out for both Memory Stick<br>interfaces and for Secure Digital                       | In/Out           | _              |

|                                           | DDATA0/CTS1/SDATA0_SDIO1/GPIO1                                                                           | Secure Digital serial data bit 0<br>Memory Stick interface 1 data I/O                      | In/Out           | _              |

|                                           | SCL0/SDATA1_BS1/GPIO41                                                                                   | Secure Digital serial data bit 1<br>Memory Stick interface 1 strobe                        | In/Out           | _              |

|                                           | DDATA1/RTS1/SDATA2_BS2/GPIO2                                                                             | Secure Digital serial data bit 2<br>Memory Stick interface 2 strobe<br>Reset output signal | In/Out           | _              |

|                                           | SDA0/SDATA3/GPIO42                                                                                       | Secure Digital serial data bit 3                                                           | In/Out           | -              |

| ADC IN                                    | ADIN0/GPI52<br>ADIN1/GPI53<br>ADIN2/GPI54<br>ADIN3/GPI55<br>ADIN4/GPI56<br>ADIN5/GPI57                   | Analog to Digital converter input signals                                                  | In               | _              |

| ADC OUT                                   | ADREF<br>ADOUT/SCLK4/GPIO58                                                                              | Analog to digital convertor output signal.<br>Connect to ADREF via integrator<br>network.  | In/Out           | _              |

| QSPI clock                                | QSPI_CLK/SUBR/GPIO25 QSPI clock signal                                                                   |                                                                                            | In/Out           | _              |

| QSPI data in                              | RCK/QSPI_DIN/QSPI_DOUT/GPIO26                                                                            | QSPI data input                                                                            | In/Out           | _              |

| QSPI data out                             | RCK/QSPI_DIN/QSPI_DOUT/GPIO26<br>QSPI_DOUT/SFSY/GPIO27                                                   | QSPI data out                                                                              | In/Out           | _              |

| QSPI chip selects                         | QSPI_CS0/EBUIN4/GPI015<br>QSPI_CS1/EBUOUT2/GPI016<br>QSPI_CS2/MCLK2/GPI024<br>CS1/QSPI_CS3/GPI028        | QSPI chip selects                                                                          | In/Out           | _              |

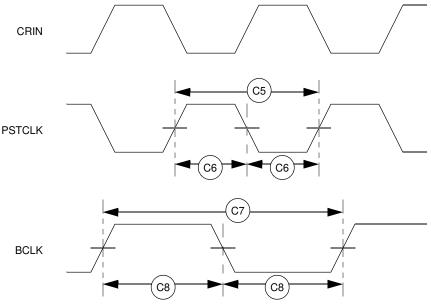

| Crystal in                                | CRIN                                                                                                     | Crystal input                                                                              | In               | _              |

| Crystal out                               | CROUT                                                                                                    | Crystal Out                                                                                | Out              | -              |

| Reset In                                  | RSTI                                                                                                     | Processor Reset Input                                                                      | In               | -              |

| Freescale Test Mode                       | TEST[2:0]                                                                                                | TEST pins.                                                                                 | In               | _              |

| Linear regulator output                   | LINOUT                                                                                                   | outputs 1.2 V to supply core                                                               | Out              | _              |

| Linear regulator input                    | LININ                                                                                                    | Input, typically I/O supply (3.3V)                                                         | In               | _              |

| Linear regulator ground                   | LINGND                                                                                                   | -                                                                                          | -                | _              |

| High Impedance                            | HI-Z                                                                                                     | Assertion Tri-states all output signal pins.                                               | In               | _              |

| Debug Data                                | DDATA0/CTS1/SDATA0_SDIO1/GPIO1<br>DDATA1/RTS1/SDATA2_BS2/GPIO2<br>DDATA2/CTS0/GPIO3<br>DDATA3/RTS0/GPIO4 | Displays captured processor data and break-point status.                                   | In/Out           | Hi-Z           |

#### Table 2. SCF5250 Signal Index (continued)

| Signal Name                                      | Mnemonic                                                                 | Function                                                                                                 | Input/<br>Output | Reset<br>State |

|--------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------|----------------|

| Processor Status                                 | PST0/GPIO50<br>PST1/GPIO49<br>PST2/INTMON2/GPIO48<br>PST3/INTMON1/GPIO47 | Indicates internal processor status.                                                                     | In/Out           | Hi-Z           |

| Processor Clock                                  | PSTCLK/GPIO51                                                            | processor clock output                                                                                   | Out              | -              |

| Test Clock                                       | тск                                                                      | Clock signal for IEEE 1149.1A JTAG.                                                                      | In               | _              |

| Test Reset/Development<br>Serial Clock           | TRST/DSCLK                                                               | Multiplexed signal that is asynchronous reset for JTAG controller. Clock input for debug module.         | In               | -              |

| Test Mode Select/ Break<br>Point                 | TMS/BKPT                                                                 | Multiplexed signal that is test mode select<br>in JTAG mode and a hardware<br>break-point in debug mode. | In               | -              |

| Test Data Input /<br>Development Serial Input    | TDI/DSI                                                                  | Multiplexed serial input for the JTAG or background debug module.                                        | In               | _              |

| Test Data<br>Output/Development<br>Serial Output | TDO/DSO                                                                  | Multiplexed serial output for the JTAG or background debug module.                                       | Out              | -              |

#### Table 2. SCF5250 Signal Index (continued)

### 3.1 GPIO

Many pins have an optional GPIO function.

- General purpose input is always active, regardless of state of pin.

- General purpose output or primary output is determined by the appropriate setting of the Pin Multiplex Control Registers, GPIO-FUNCTION, GPIO1-FUNCTION and PIN-CONFIG.

- At Power-on reset, all pins are set to their primary function.

### 3.2 SCF5250 Bus Signals

These signals provide the external bus interface to the SCF5250 processor.

### 3.2.1 Address Bus

- The address bus provides the address of the byte or most significant byte of the word or longword being transferred. The address lines also serve as the DRAM address pins, providing multiplexed row and column address signals.

- Bits 23 down to 1 and 24 of the address are available. A24 is intended to be used with 256 Mbit DRAM's. Signals are named:

- A[23:1]

- A20/24

### 3.2.2 Read-Write Control

This signal indicates during any bus cycle whether a read or write is in progress. A low is write cycle and a high is a read cycle.

### 3.2.3 Output Enable

The  $\overline{OE}$  signal is intended to be connected to the output enable of asynchronous memories connected to chip selects. During bus read cycles, the ColdFire processor will drive  $\overline{OE}$  low.

### 3.2.4 Data Bus

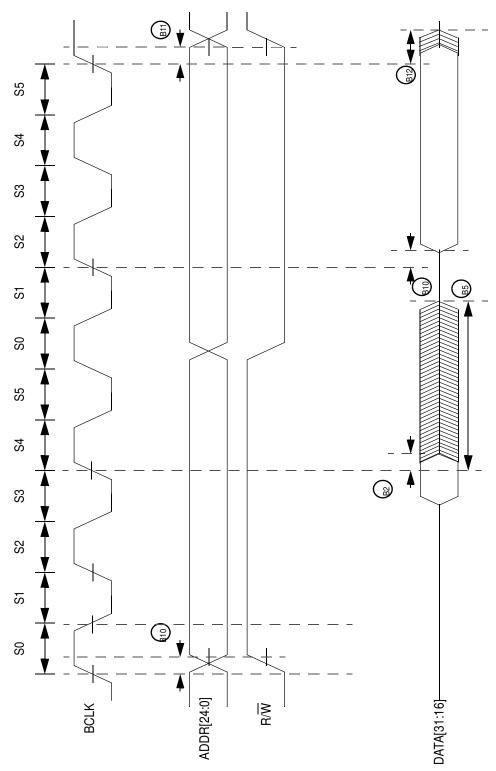

The data bus (D[31:16]) is bi-directional and non-multiplexed. Data is registered by the SCF5250 on the rising clock edge. The data bus uses a default configuration if none of the chip-selects or DRAM bank match the address decode. All 16 bits of the data bus are driven during writes, regardless of port width or operand size.

### 3.2.5 Transfer Acknowledge

The  $\overline{TA}$ /GPIO12 pin is the transfer acknowledge signal.

## 3.3 SDRAM Controller Signals

The following SDRAM signals provide a glueless interface to external SDRAM. An SDRAM width of 16 bits is supported and can access as much as 32MB of memory. ADRAMs are not supported.

| SDRAM Signal                              | Description                                                                                                                                                                      |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synchronous DRAM row address strobe       | The $\overline{\text{SDRAS}}/\text{GPIO59}$ active low pin provides a seamless interface to the RAS input on synchronous DRAM                                                    |

| Synchronous DRAM Column Address<br>Strobe | The SDCAS/GPIO39 active low pin provides a seamless interface to CAS input on synchronous DRAM.                                                                                  |

| Synchronous DRAM Write                    | The $\overline{\text{SDWE}}/\text{GPIO38}$ active-low pin is asserted to signify that a SDRAM write cycle is underway. This pin outputs logic '1' during read bus cycles.        |

| Synchronous DRAM Chip Enable              | The $\overline{\text{SD}_{CS0}}$ /GPIO60 active-low output signal is used during synchronous mode to route directly to the chip select of a SDRAM device.                        |

| Synchronous DRAM UDQM and LQDM signals    | The DRAM byte enables UDMQ and LDQM are driven by the SDUDQM/GPO53 and SDLDQM/GPO52 byte enable outputs.                                                                         |

| Synchronous DRAM clock                    | The DRAM clock is driven by the BCLK/GPIO40 signal                                                                                                                               |

| Synchronous DRAM Clock Enable             | The BCLKE active high output signal is used during synchronous mode to route directly to the SCKE signal of external SDRAMs. This signal provides the clock enable to the SDRAM. |

Table 3. SDRAM Controller Signals

# 3.4 Chip Selects

There are three chip select outputs on the SCF5250 device.  $\overline{CS0}/\overline{CS4}$  and  $\overline{CS1}/QSPI_CS3/GPIO28$  and CS2 which is associated with the IDE interface read and write strobes - IDE-DIOR and IDE-DIOW.

CS0 and CS4 are multiplexed. The SCF5250 has the option to boot from an internal Boot ROM. The function of the CS0/CS4 pin is determined by the boot mode. When the device is booted from internal ROM, the internal ROM is accessed with CS0 (required for boot) and the CS0/CS4 pin is driven by CS4. When the device is booted from external ROM / Flash, the CS0/CS4 pin is driven by CS0 and the internal ROM is disabled.

The active low chip selects can be used to access asynchronous memories. The interface is glueless.

## 3.5 ISA Bus

The SCF5250 supports an ISA bus. Using the ISA bus protocol, reads and writes for one ISA bus peripheral is possible. <u>IDE-DIOR/GPIO31</u> and <u>IDE-DIOW/GPIO32</u> are the read and write strobe. The peripheral can insert wait states by pulling IDE-IORDY/GPIO33.

CS2 is associated with the IDE-DIOR and IDE-DIOW.

# 3.6 Bus Buffer Signals

As the SCF5250 has a complicated slave bus, which allows SDRAM, asynchronous memories, and ISA peripherals on the bus, it may become necessary to introduce a buffer on the bus in certain applications. The SCF5250 has a glueless interface to steer these bus buffers with two bus buffer output signals BUFENB1/GPIO29 and BUFENB2/GPIO30.

# 3.7 I<sup>2</sup>C Module Signals

There are two  $I^2C$  interfaces on this device as described in Table 4.

The I<sup>2</sup>C module acts as a two-wire, bidirectional serial interface between the SCF5250 processor and peripherals with an I<sup>2</sup>C interface (e.g., LED controller, A-to-D converter, D-to-A converter). When devices connected to the I<sup>2</sup>C bus drive the bus, they will either drive logic-0 or high-impedance. This can be accomplished with an open-drain output.

| I <sup>2</sup> c Module Signal | Description                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sup>2</sup> C Serial Clock  | The SCL0/SDATA1_BS1/GPIO41 and SCL1/TXD1/GPIO10 bidirectional signals are the clock signal for first and second I <sup>2</sup> C module operation. The I <sup>2</sup> C module controls this signal when the bus is in master mode; all I <sup>2</sup> C devices drive this signal to synchronize I <sup>2</sup> C timing. Signals are multiplexed |

| I <sup>2</sup> C Serial Data   | The SDA0/SDATA3/GPIO42 and SDA1/RXD1/GPIO44 bidirectional signals are the data input/output for the first and second serial I <sup>2</sup> C interface. Signals are multiplexed                                                                                                                                                                    |

| Table 4 | . I <sup>2</sup> C | Module | Signals |

|---------|--------------------|--------|---------|

|---------|--------------------|--------|---------|

# 3.8 Serial Module Signals

The signals described in Table 5 transfer serial data between the two UART modules and the external peripherals.

| Serial Module Signal | Description                                                                                                                                                                                                                                                                                                                                                                |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Data         | The RXD0/GPIO46 and SDA1/RXD1/GPIO44 are the inputs on which serial data is received by the DUART. Data is sampled on RxD[1:0] on the rising edge of the serial clock source, with the least significant bit received first.                                                                                                                                               |

| Transmit Data        | The DUART transmits serial data on the TXD0/GPIO45 and SCL1/TXD1/GPIO10 output signals. Data is transmitted on the falling edge of the serial clock source, with the least significant bit transmitted (LSB) first. When no data is being transmitted or the transmitter is disabled, these two signals are held high. TxD[1:0] are also held high in local loopback mode. |

| Request To Send      | The DDATA3/RTS0/GP104 and DDATA1/RTS1/SDATA2_BS2/GPIO2 request-to-send outputs indicate to the peripheral device that the DUART is ready to send data and requires a clear-to-send signal to initiate transfer.                                                                                                                                                            |

| Clear To Send        | Peripherals drive the DDATA2/CTS0/GPIO3 and DDATA0/CTS1/SDATA0_SDIO1/GPIO1 inputs to indicate to the SCF5250 serial module that it can begin data transmission.                                                                                                                                                                                                            |

#### Table 5. Serial Module Signals

## 3.9 Timer Module Signals

Table 6 describes the Timer module signal which provides an external interface to Timer0.

#### Table 6. Timer Module Signals

| Serial Module Signal | Description                                                                           |

|----------------------|---------------------------------------------------------------------------------------|

| Timer Output         | The SDATAO1/TOUT0/GPIO18 programmable output pulse or toggle on various timer events. |

# 3.10 Serial Audio Interface Signals

Table 7 describes the signals that provide the external audio interface.

| Serial Module Signal    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Audio Bit Clock  | The SCLK1/GPIO20, SCLK2/GPIO22 and SCLK3/GPIO35,<br>multiplexed pins can serve as general purpose I/Os or serial audio bit clocks. As bit clocks, these<br>bidirectional pins can be programmed as outputs to drive their associated serial audio (IIS) bit clocks.<br>Alternately, these pins can be programmed as inputs when the serial audio bit clocks are driven<br>internally. The functionality is programmed within the Audio module. During reset, these pins are<br>configured as input serial audio bit clocks.                                                                                                                     |

| Serial Audio Word Clock | The LRCK1/GPIO19, LRCK2/GPIO23 and LRCK3/GPIO43/AUDIO_CLOCK multiplexed pins can serve as general purpose I/Os or serial audio word clocks. As word clocks, the bidirectional pins can be programmed as inputs to drive their associated serial audio word clock. Alternately, these pins can be programmed as outputs when the serial audio word clocks are derived internally. The functionality is programmed within the Audio module. During reset, these pins are configured as input serial audio word clocks. LRCK3/GPIO43/AUDIO_CLOCK can be used as the external audio clock input. If the core clock chosen to be non-audio specific. |

| Serial Audio Data In    | The SDATAI1/GPIO17 and SDATAI3/GPIO8 multiplexed pins can serve as general purpose I/Os or serial audio inputs. As serial audio inputs the data is sent to interfaces 1 and 3 respectively. During reset, the pins are configured as serial data inputs.                                                                                                                                                                                                                                                                                                                                                                                        |

| Serial Audio Data Out   | SDATO1/TOUT0/GPIO18 AND SDATAO2/GPIO34 multiplexed pins can serve as general purpose I/Os or serial audio outputs. During reset, the pins are configured as serial data outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Serial audio error flag | The EF/GPIO6 multiplexed pin can serve as general purpose I/Os or error flag input. As error flag input, this pin will input the error flag delivered by the CD-DSP. EF/GPIO6 is only relevant for serial interface SDATAI1.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Serial audio CFLG       | The CFLG/GPIO5 multiplexed pin can serve as general purpose I/O or CFLG input. As CFLG input, the pin will input the CFLG flag delivered by the CD-DSP. CFLG/GPIO5 is only relevant for serial interface SDATAI1.                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Table 7. Serial Audio Interface Signals

# 3.11 Digital Audio Interface Signals

Table 8 describes the signals for the digital audio interface.

#### Table 8. Digital Audio Interface Signals

| Serial Module Signal | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Audio In     | The EBUIN1/GPIO36, EBUIN2/SCLK_OUT/GPIO13, EBUIN3/CMD_SDIO2/GPIO14, and QSPI_CS0/EBUIN4/GPIO15 multiplexed signals can serve as general purpose input or can be driven by various digital audio (IEC958) input sources. Both functions are always active. Input chosen for IEC958 receiver is programmed within the audio module. Input value on the 4 pins can always be read from the appropriate GPIO register. |

| Digital Audio Out    | The EBUOUT1/GPIO37 and QSPI_CS1/EBUOUT2/GPIO16 multiplexed pins can serve as general purpose I/O or as digital audio (IEC958) output. EBUOUT1 is digital audio out for consumer mode, EBUOUT2 is digital audio out for professional mode. During reset, the pin is configured as a digital audio output.                                                                                                           |

# 3.12 Subcode Interface

There is a 3-line subcode interface on the SCF5250 processor. This 3-line subcode interface allows the device to format and transmit subcode in EIAJ format to a CD channel encoder device. The three signals are described in Table 9.

| Signal name                   | Description                                                                                                 |

|-------------------------------|-------------------------------------------------------------------------------------------------------------|

| RCK/QSPI_DIN/QSPI_DOUT/GPIO26 | Subcode clock input. When pin is used as subcode clock, this pin is driven by the CD channel encoder.       |

| QSPI_DOUT/SFSY/GPIO27         | Subcode sync output<br>This signal is driven high if a subcode sync needs to be inserted in the EFM stream. |

| QSPI_CLK/SUBR/GPIO25          | Subcode data output<br>This signal is a subcode data out pin.                                               |

#### Table 9. Subcode Interface Signal

# 3.13 Analog to Digital Converter (ADC)

The ADOUT signal on the ADOUT/SCLK4/GPIO58 pin provides the reference voltage in PWM format. This output requires an external integrator circuit (resistor/capacitor) to convert it to a DC level to be input to the ADREF pin.

The six AD inputs are each fed to their own comparator. The reference input to each (ADREF) is then multiplexed as only one AD comparison can be made at any one time.

#### NOTE

To use the ADINx as General Purpose inputs (rather than there analogue function) it is necessary to generate a fixed comparator voltage level of VDD/2. This can be accomplished by a potential divider network connected to the ADREF pin. However in portable applications where stand-by power consumption is important the current taken by the divider network (in stand-by mode) could be excessive. Therefore it is possible to generate a VDD/2 voltage by selecting SCLK4 output mode and feeding this clock signal (which is 50% duty cycle) through an external integration circuit. This would generate a voltage level equal to VDD/2 but would be disabled when stand-by mode was selected.

# 3.14 Secure Digital/Memory Stick Card Interface

The device has a versatile flash card interface that supports both Secure Digital and Memory Stick cards. The interface can either support one Secure Digital or two Memory Stick cards. No mixing of card types is possible. Table 10 gives the pin descriptions.

| Flash Memory Signal     | Description                                                       |

|-------------------------|-------------------------------------------------------------------|

| EBUIN2/SCLKOUT/GPIO13   | Clock out for both Memory Stick interfaces and for Secure Digital |

| EBUIN3/CMD_SDIO2/GPIO14 | Secure Digital command line<br>Memory Stick interface 2 data I/O  |

| Flash Memory Signal            | Description                                                                                                                                                                             |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDATAO/CTS1/SDATA0_SDIO1/GPIO1 | Secure Digital serial data bit 0<br>Memory Stick interface 1 data I/O                                                                                                                   |

| SCL0/SDATA1_BS1/GPIO41         | Secure Digital serial data bit 1<br>Memory Stick interface 1 strobe                                                                                                                     |

| DDATA1/RTS1/SDATA2_BS2/GPIO2   | Secure Digital serial data bit 2<br>Memory Stick interface 2 strobe<br>Reset output signal<br>Selection between Reset function and SDATA2_BS2 is done by programming PLLCR<br>register. |

| SDA0/SDATA3/GPIO42             | Secure Digital serial data bit 3                                                                                                                                                        |

#### Table 10. Flash Memory Card Signals (continued)

# 3.15 Queued Serial Peripheral Interface (QSPI)

The QSPI interface is a high-speed serial interface allowing transmit and receive of serial data. Pin descriptions are given in Table 11.

| Serial Module Signal                                   | Description                                                                                             |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| QSPICLK/SUBR/GPIO25                                    | Multiplexed signal IIC interface clock or QSPI clock output Function select is done via PLLCR register. |

| RCK/QSPIDIN/QSPI_DOUT/GPIO26                           | Multiplexed signal IIC interface data or QSPI data input. Function select is done via PLLCR register.   |

| RCK/QSPI_DIN/QSPI_DOUT/GPI026<br>QSPI_DOUT/SFSY/GPI027 | QSPI data output.                                                                                       |

| QSPICS0/EBUIN4GPIO15                                   |                                                                                                         |

| QSPICS1/EBUOUT2/GPIO16                                 | 4 different QSPI chip selects.                                                                          |

| QSPICS2/MCLK2/GPIO24                                   |                                                                                                         |

| CS1/QSPICS3/GPIO28                                     |                                                                                                         |

Table 11. Queued Serial Peripheral Interface (QSPI) Signals

# 3.16 Crystal Trim

The XTRIM/GPIO0 output produces a pulse-density modulated phase/frequency difference signal to be used after low-pass filtering to control varicap-voltage to control crystal oscillation frequency. This will lock the crystal to the incoming digital audio signal.

# 3.17 Clock Out

The MCLK1/GPIO11 and QSPI\_CS2/MCLK2/GPIO24 can serve as DAC clock outputs. When programmed as DAC clock outputs, these signals are directly derived from the crystal oscillator or clock Input (CRIN).

# 3.18 Debug and Test Signals

These signals interface with external I/O to provide processor debug and status signals.

### 3.18.1 Test Mode

The TEST[2:0] inputs are used for various manufacturing and debug tests. For normal mode TEST [2:1] should be ways be tied low. TEST0 should be set high for BDM debug mode and set low for JTAG mode.

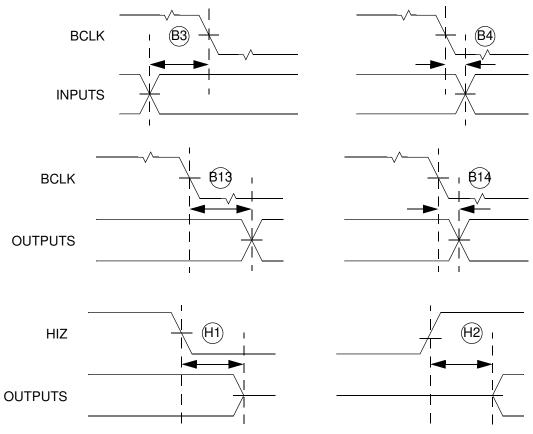

### 3.18.2 High Impedance

The assertion of  $\overline{\text{HI}}_{Z}$  will force all output drivers to a high-impedance state. The timing on  $\overline{\text{HI}}_{Z}$  is independent of the clock.

#### NOTE

JTAG operation will override the  $\overline{\text{HI}}_{Z}$  pin.

### 3.18.3 Processor Clock Output

The internal PLL generates this PSTCLK/GPIO51 and output signal, and is the processor clock output that is used as the timing reference for the Debug bus timing (DDATA[3:0] and PST[3:0]). The PSTCLK/GPIO51 is at the same frequency as the core processor.

### 3.18.4 Debug Data

The debug data pins, DDATA0/CTS1/SDATA0\_SDIO1/GPIO1, DDATA1/RTS1/SDATA2\_BS2/GPIO2, DDATA2/CTS0/GPIO3, and DDATA3/RTS0/GPIO4, are four bits wide. This nibble-wide bus displays captured processor data and break-point status.

### 3.18.5 Processor Status

The processor status pins, PST0/GPIO50, PST1/GPIO49, PST2/INTMON/GPIO48, and PST3/INTMON/GPIO47, indicate the SCF5250 processor status. During debug mode, the timing is synchronous with the processor clock (PSTCLK) and the status is not related to the current bus transfer. Table 12 shows the encodings of these signals.

| PST[3:0] |          |                                                          |  |

|----------|----------|----------------------------------------------------------|--|

| (HEX)    | (BINARY) | - Definition                                             |  |

| \$0      | 0000     | Continue execution                                       |  |

| \$1      | 0001     | Begin execution of an instruction                        |  |

| \$2      | 0010     | Reserved                                                 |  |

| \$3      | 0011     | Entry into user-mode                                     |  |

| \$4      | 0100     | Begin execution of PULSE and WDDATA instructions         |  |

| \$5      | 0101     | Begin execution of taken branch or Synch_PC <sup>1</sup> |  |

| \$6      | 0110     | Reserved                                                 |  |

| \$7      | 0111     | Begin execution of RTE instruction                       |  |

| \$8      | 1000     | Begin 1-byte data transfer on DDATA                      |  |

| \$9      | 1001     | Begin 2-byte data transfer on DDATA                      |  |

| \$A      | 1010     | Begin 3-byte data transfer on DDATA                      |  |

| \$B      | 1011     | Begin 4-byte data transfer on DDATA                      |  |

| \$C      | 1100     | Exception processing <sup>2</sup>                        |  |

| \$D      | 1101     | Emulator mode entry exception processing <sup>2</sup>    |  |

| \$E      | 1110     | Processor is stopped, waiting for interrupt <sup>2</sup> |  |

| \$F      | 1111     | Processor is halted <sup>2</sup>                         |  |

<sup>1</sup> Rev. B enhancement.

<sup>2</sup> These encodings are asserted for multiple cycles.

# 3.19 BDM/JTAG Signals

The SCF5250 complies with the IEEE 1149.1A JTAG testing standard. The JTAG test pins are multiplexed with background debug pins.

# 3.20 Clock and Reset Signals

The clock and reset signals configure the SCF5250 processor and provide interface signals to the external system.

### 3.20.1 Reset In

Asserting  $\overline{\text{RSTI}}$  causes the SCF5250SCF5250 to enter reset exception processing. When  $\overline{\text{RSTI}}$  is recognized, the data bus is tri-stated.

### 3.20.2 Clock Input

SCF5250 includes an on-chip crystal oscillator. The crystal should be connected between CRIN and CROUT. An externally generated clock signal can also be used and should be connected directly to the CRIN pin.

## 3.21 Wake-Up Signal

To exit power down mode, apply a LOW level to the WAKE\_UP/GPIO21 input pin.

# 3.22 On-Chip Linear Regulator

The SCF5250 includes an on-chip linear regulator. This regulator provides an 1.2 V output which is intended to be used to power the SCF5250 core. Three pins are associated with this function. LININ, LINOUT and LINGND. Typically LININ would be fed by the I/O (PAD) supply (3.3 V) with separate filtering recommended to provide some isolation between the I/O and the core.

In portable solutions this linear regulator may not be efficient enough and in this case we would expect the 1.2 V supply to be generated externally, possibly by a highly efficient DC-DC convertor.

If not used leave pins not connected.

# 4 Electrical Characteristics

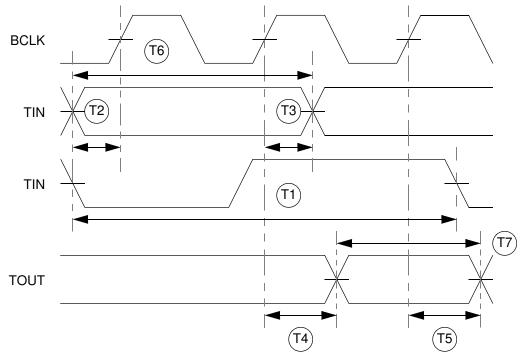

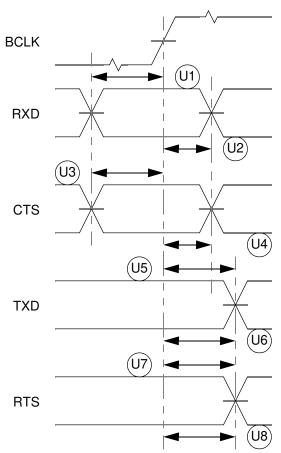

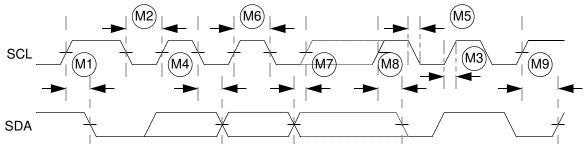

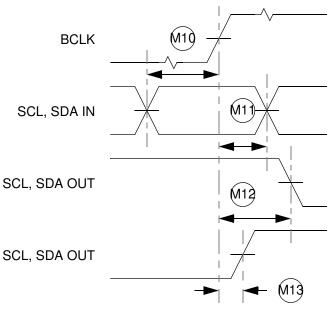

Table 14 through Table 19 provide the electrical characteristics for the SCF5250 processor. The remaining figures and tables in this section provide the timing diagrams and the timing parameters for the SCF5250 processor.

| For                                                              | See                 |

|------------------------------------------------------------------|---------------------|

| Maximum Ratings                                                  | Table 14 on page 22 |

| Operating Temperature                                            | Table 15 on page 22 |

| Recommended<br>Operating Supply<br>Voltages                      | Table 16 on page 22 |

| Linear Regulator<br>Operating Specification                      | Table 17 on page 23 |

| DC Electrical<br>Specifications                                  | Table 18 on page 23 |

| Operating Parameters<br>for ADC DC Electrical<br>Characteristics | Table 19 on page 24 |

| Table 13. | Quick Reference    | for Electrical | Characteristics |

|-----------|--------------------|----------------|-----------------|

|           | Guion ficici chioc |                |                 |

| Rating                         | Symbol           | Value        | Units |

|--------------------------------|------------------|--------------|-------|

| Supply Core Voltage            | V <sub>cc</sub>  | -0.5 to +2.5 | V     |

| Maximum Core Operating Voltage | V <sub>cc</sub>  | +1.32        | V     |

| Minimum Core Operating Voltage | V <sub>cc</sub>  | +1.08        | V     |

| Supply I/O Voltage             | V <sub>cc</sub>  | -0.5 to +4.6 | V     |

| Maximum I/O Operating Voltage  | V <sub>cc</sub>  | +3.6         | V     |

| Minimum I/O Operating Voltage  | V <sub>cc</sub>  | +3.0         | V     |

| Input Voltage                  | V <sub>in</sub>  | -0.5 to +6.0 | V     |

| Storage Temperature Range      | T <sub>stg</sub> | -65 to150    | °C    |

#### Table 14. Maximum Ratings

Table 15 provides the recommended operating temperatures for the SCF5250 processor.

#### Table 15. Operating Temperature

| Characteristic                        | Symbol            | Value           | Units |

|---------------------------------------|-------------------|-----------------|-------|

| Maximum Operating Ambient Temperature | T <sub>Amax</sub> | 85 <sup>1</sup> | °C    |

| Minimum Operating Ambient Temperature | T <sub>Amin</sub> | -40             | °C    |

This published maximum operating ambient temperature should be used only as a system design guideline. All device operating parameters are guaranteed only when the junction temperature does not exceed 105°C.

Table 16 provides the recommended operating supply voltages for the SCF5250 processor.

Table 16. Recommended Operating Supply Voltages

| Pin Name    | Min   | Тур  | Max   |

|-------------|-------|------|-------|

| CORE-VDD    | 1.08V | 1.2V | 1.32V |

| CORE-VSS    | _     | gnd  | _     |

| PAD-VDD     | 3.0V  | 3.3v | 3.6V  |

| PAD-VSS     | _     | gnd  | _     |

| ADVDD       | 3.0V  | 3.3v | 3.6V  |

| ADGND       | _     | gnd  | _     |

| OSCPAD-VDD  | 3.0V  | 3.3v | 3.6V  |

| OSCPAD-GND  | _     | gnd  | _     |

| PLLCORE1VDD | 1.08V | 1.2V | 1.32V |

| PLLCORE1GND | _     | gnd  | _     |

| PLLCORE2VDD | 1.08V | 1.2v | 1.32V |

| PLLCORE2GND | -     | gnd  | -     |

| LIN         | 3.0v  | 3.3V | 3.6V  |

1

Table 17 provides the linear regulator operating specifications for the SCF5250 processor.

| Characteristic                            | Symbol | Min   | Тур   | Мах   |

|-------------------------------------------|--------|-------|-------|-------|

| Input Voltage                             | Vin    | 3.0V  | 3.3V  | 3.6   |

| Output Voltage (LINOUT)                   | Vout   | 1.14V | 1.2V  | 1.26V |

| Output Current                            | lout   | -     | 100mA | 150mA |

| Power Dissipation                         | Pd     | -     | -     | 436uW |

| Load Regulation (10% lout $\ge$ 90% lout) | -      | 40mV  | 50mV  | 60mV  |

| Power Supply Rejection                    | PSRR   | _     | 40dB  | _     |

#### Table 17. Linear Regulator<sup>1</sup> Operating Specification

A pmos regulator is employed as a current source in this Linear regulator, so a 10µF capacitor (ESR 0 ... 5 Ohm) is needed on the output pin (LINOUT) to integrate the current. Typically this will require the use of a Tantalum type capacitor.

#### Table 18 provides the DC electrical specifications.

#### Table 18. DC Electrical Specifications (I/O Vcc = 3.3 Vdc ± 0.3 Vdc)

| Characteristic                                                                                                                                                                                                            | Symbol           | Min  | Max | Units |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----|-------|

| Operation Voltage Range for I/O                                                                                                                                                                                           | V <sub>cc</sub>  | 3.0  | 3.6 | V     |

| Input High Voltage                                                                                                                                                                                                        | V <sub>IH</sub>  | 2    | 5.5 | V     |

| Input Low Voltage                                                                                                                                                                                                         | V <sub>IL</sub>  | -0.3 | 0.8 | V     |

| Input Leakage Current @ 0.0 V /3.3 V During Normal Operation                                                                                                                                                              | l <sub>in</sub>  | -    | ±1  | μμΑ   |

| Hi-Impedance (Three-State) Leakage Current<br>@ 0.0 V/3.3 V During Normal Operation                                                                                                                                       | I <sub>TSI</sub> | -    | ±1  | μμΑ   |

| Output High Voltage I <sub>OH</sub> = 8mA <sup>1</sup> , 4mA <sup>2</sup> , 2mA <sup>3</sup>                                                                                                                              | V <sub>OH</sub>  | 2.4  | -   | V     |

| Output Low Voltage I <sub>OL</sub> = 8mA <sup>1</sup> , 4mA <sup>2</sup> , 2mA <sup>3</sup>                                                                                                                               | V <sub>OL</sub>  | -    | 0.4 | V     |

| Schmitt Trigger Low to High Threshold Point <sup>6</sup>                                                                                                                                                                  | V <sub>T+</sub>  | 1.47 | -   | V     |

| Schmitt Trigger High to Low Threshold Point <sup>6</sup>                                                                                                                                                                  | V <sub>T-</sub>  | -    | .95 | V     |

| Load Capacitance (DATA[31:16], SCLK[4:1], SCLKOUT, EBUOUT[2:1],<br>LRCK[3:1], SDATAO[2:1], CFLG, EF, DDATA[3:0], PST[3:0], PSTCLK,<br>IDE-DIOR, IDE-DIOW, IORDY)                                                          | CL               | -    | 50  | pF    |

| Load Capacitance (ADDR[24:9], BCLK)                                                                                                                                                                                       | CL               | -    | 40  | pF    |

| Load Capacitance (BCLKE, SDCAS, SDRAS, SDLDQM, SD_CS0, SDUDQM, SDWE, BUFENB[2:1])                                                                                                                                         | CL               | -    | 30  | pF    |

| Load Capacitance (SDA0, SDA1, SCL0, SCL1, CMD_SDIO2, SDATA2_BS2,<br>SDATA1_BS1, SDATA0_SDIO1, CS0/CS4, CS1, OE, R/W, TA, TXD[1:0], XTRIM,<br>TDO/DSO, RCK, SFSY, SUBR, SDATA3, TOUT0, QSPID_OUT, QSPICS[3:0],<br>GP[6:5]) | CL               | -    | 20  | pF    |

| Characteristic                                                                                                                                                                                                                                                                                                          | Symbol          | Min      | Max | Units |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-----|-------|

| Capacitance <sup>5</sup> , V <sub>in</sub> = 0 V, f = 1 MHz                                                                                                                                                                                                                                                             | C <sub>IN</sub> | -        | 6   | pF    |

| DATA[31:16], ADDR[24:9], PSTCLK, BCLK<br>SCL, SDA, PST[3:0], DDATA[3:0], TDSO, SDRAS, SDCAS, SDWE, SD_CS0, SE<br>TOUT0, RTS[1:0], TXD[1:0], SCLK[4:1]<br>BKPT/TMS, DSI/TDI, DSCLK/TRST<br>Capacitance C <sub>IN</sub> is periodically sampled rather than 100% tested.<br>SCLK[4:1], SCL0, SCL1, SDA0, SDA1, CRIN, RSTI | DLDQM, SDUE     | DQM, R/W | ;   |       |

Table 18. DC Electrical Specifications (I/O Vcc = 3.3 Vdc ± 0.3 Vdc) (continued)

Table 19 provides the operating parameters for the ADC DC electrical characteristics.

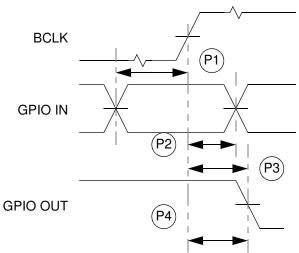

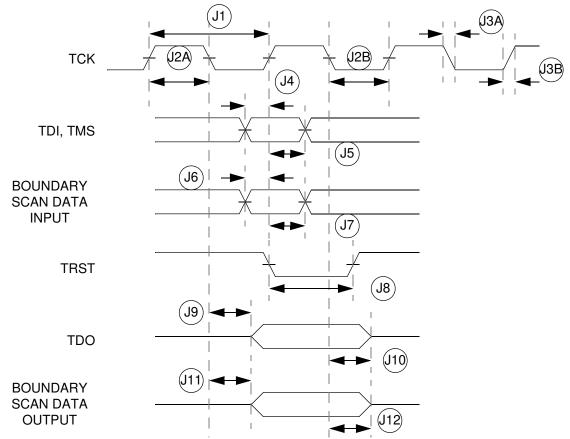

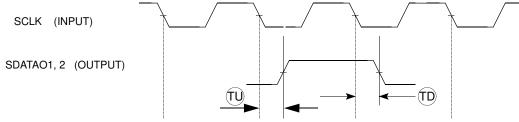

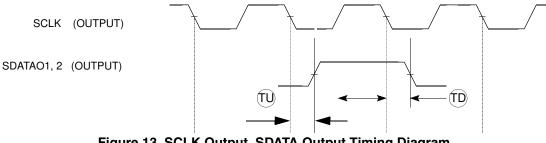

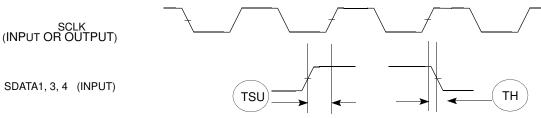

| 1 5                                |                     |      |      |           |       |