# HTMS1x01; HTMS8x01

### HITAG µ transponder IC

Rev. 3.4 — 21 May 2015 152934

Product data sheet COMPANY PUBLIC

### 1. General description

The HITAG product line is well known and established in the contactless identification market.

Due to the open marketing strategy of NXP Semiconductors there are various manufacturers well established for both the transponders/cards as well as the read/write devices. All of them supporting HITAG 1, HITAG 2 and HITAG S transponder ICs.

With the new HITAG  $\mu$  family, this existing infrastructure is extended with the next generation of ICs being substantially smaller in mechanical size, lower in cost, offering more operation distance and speed, but still being operated with the same reader infrastructure and transponder manufacturing equipment.

The protocol and command structure for HITAG  $\mu$  is design to support Reader Talks First (RTF) operation, including anti-collision algorithm.

Different memory sizes are offered and can be operated using exactly the same protocol.

### 1.1 Target markets

### 1.1.1 Animal identification

The ISO standards ISO 11784 and ISO 11785 are well established in this market and HITAG  $\mu$  is especially designed to deliver the optimum performance compliant to these standards. The HITAG  $\mu$  advanced ICs are offering additional memory for storage of customized offline data like further breeding details.

#### 1.1.2 Laundry automation

- Identify 200 pcs of garment with one read/write device

- · Long operation distance with typical small shaped laundry button transponders

- · Insensitive to harsh conditions like pressure, heat and water

#### 1.1.3 Beer keg and gas cylinder logistic

- · Recognizing a complete pallet of gas cylinders at one time

- · Long writing distance

- Voluntarily change between TTF Mode with user defined data length and read/write modes without changing the configuration on the transponder

- Authenticity check at the beer pubs between beer bumper and supplied beer keg, provides a safe protection of the beer brand

### 1.1.4 Brand protection

Authenticity check for high level brands or for original refilling e.g. toner for fax machines.

### 2. Features and benefits

#### 2.1 Features

- Integrated circuit for contactless identification transponders and cards

- Integrated resonance capacitor of 210 pF with ±3 % tolerance or 280 pF with ±5 % tolerance over full production

- Frequency range 100 kHz to 150 kHz

#### 2.2 Protocol

- Modulation read/write device → transponder: 100 % ASK and binary pulse length coding

- Modulation transponder → read/write device: Strong ASK modulation with anti-collision, Manchester and Biphase coding

- Fast anti-collision protocol

- Cyclic Redundancy Check (CRC)

- Transponder Talks First (TTF) mode

- Temporary switch from Transponder Talks First into Reader Talks First (RTF) Mode

- Data rate read/write device to transponder: 5.2 kbit/s

- Data rates transponder to read/write device: 2 kbit/s, 4 kbit/s, 8 kbit/s

### 2.3 Memory

- Different memory options

- Up to 10000 erase/write cycles

- 10 years non-volatile data retention

- Memory Lock functionality

- 32-bit password feature

### 2.4 Supported standards

- Full compliant to ISO 11784 and ISO 11785 Animal ID

- Designed to support ISO/IEC 14223 Animal ID with anticollision and read/write functionality

HTMS1x01\_8x01

### 2.5 Security features

■ 48-bit Unique Identification Number (UID)

### 2.6 Delivery types

- Sawn, gold-bumped 8" wafer

- HVSON2

- SOT-1122

## 3. Applications

- Animal identification

- Laundry automation

- Beer keg and gas cylinder logistic

- Brand protection

### 4. Quick reference data

Table 1. Quick reference data

| Symbol                       | Parameter         | Conditions               |        | Min    | Тур | Max   | Unit  |

|------------------------------|-------------------|--------------------------|--------|--------|-----|-------|-------|

| Wafer EEPROM characteristics |                   |                          |        |        |     |       |       |

| t <sub>ret</sub>             | retention time    | T <sub>amb</sub> ≤ 55 °C |        | 10     | -   | -     | year  |

| N <sub>endu(W)</sub>         | write endurance   |                          |        | 100000 | -   | -     | cycle |

| Interface characteristics    |                   |                          |        |        |     |       |       |

| Ci                           | input capacitance | between LA and LB        |        |        |     |       |       |

|                              |                   | HTMS1x01                 | [1][2] | 203.7  | 210 | 216.3 | pF    |

|                              |                   | HTMS8x01                 | [1][3] | 266    | 280 | 294   | pF    |

<sup>[1]</sup> Measured with an HP4285A LCR meter at 125 kHz/room temperature (25  $^{\circ}$ C);  $V_{IN1-IN2}$  = 0.5 V (RMS)

<sup>[2]</sup> Integrated Resonance Capacitor: 210 pF  $\pm$  3 %

<sup>[3]</sup> Integrated Resonance Capacitor: 280 pF  $\pm$  5 %

# 5. Ordering information

Table 2. Ordering information

| Type number    | Package |                                                                                                                      |                              |          |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------|------------------------------|----------|

|                | Name    | Description                                                                                                          | Туре                         | Version  |

| HTMS1001FUG/AM | Wafer   | sawn, megabumped wafer, 150 μm, 8 inch, UV                                                                           | HITAG μ, 210 pF              | -        |

| HTMS8001FUG/AM | Wafer   | sawn, megabumped wafer, 150 μm, 8 inch, UV                                                                           | HITAG μ, 280pF               | -        |

| HTMS8101FUG/AM | Wafer   | sawn, megabumped wafer, 150 μm, 8 inch, UV                                                                           | HITAG μ Advanced,<br>280 pF  | -        |

| HTMS8201FUG/AM | Wafer   | sawn, megabumped wafer, 150 μm, 8 inch, UV                                                                           | HITAG μ Advanced+,<br>280 pF | -        |

| HTMS8001FTB/AF | XSON3   | plastic extremely thin small outline package; no leads; 4 terminals; body 1 $\times$ 1.45 $\times$ 0.5 mm            | HITAG μ, 280 pF              | SOT1122  |

| HTMS8101FTB/AF | XSON3   | plastic extremely thin small outline package; no leads; 4 terminals; body 1 $\times$ 1.45 $\times$ 0.5 mm            | HITAG μ Advanced,<br>280 pF  | SOT1122  |

| HTMS8201FTB/AF | XSON3   | plastic extremely thin small outline package; no leads; 4 terminals; body 1 $\times$ 1.45 $\times$ 0.5 mm            | HITAG μ Advanced+,<br>280 pF | SOT1122  |

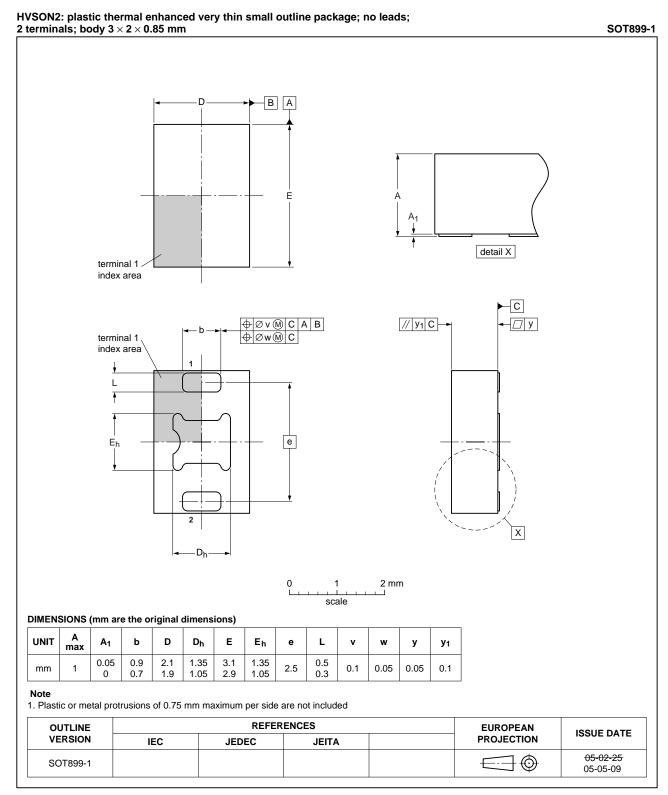

| HTMS8001FTK/AF | HVSON2  | plastic thermal enhanced very thin small outline package; no leads; 2 terminals; body $3\times2\times0.85~\text{mm}$ | HITAG μ, 280 pF              | SOT899-1 |

| HTMS8101FTK/AF | HVSON2  | plastic thermal enhanced very thin small outline package; no leads; 2 terminals; body 3 $\times$ 2 $\times$ 0.85 mm  | HITAG μ Advanced,<br>280 pF  | SOT899-1 |

| HTMS8201FTK/AF | HVSON2  | plastic thermal enhanced very thin small outline package; no leads; 2 terminals; body 3 $\times$ 2 $\times$ 0.85 mm  | HITAG μ Advanced+,<br>280 pF | SOT899-1 |

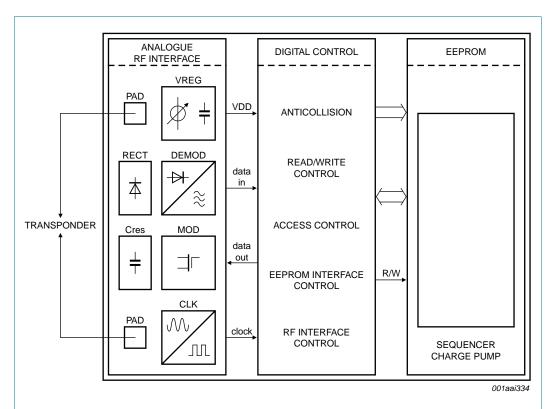

## 6. Block diagram

The HITAG  $\mu$  transponder ICs require no external power supply. The contactless interface generates the power supply and the system clock via the resonant circuitry by inductive coupling to the Read/Write Device (RWD). The interface also demodulates data transmitted from the RWD to the HITAG  $\mu$  transponder IC, and modulates the magnetic field for data transmission from the HITAG  $\mu$  transponder IC to the RWD.

Data are stored in a non-volatile memory (EEPROM). The EEPROM has a capacity of up to 1760 bit and is organized in blocks.

Fig 1. Block diagram of HITAG  $\mu$  transponder IC

# 7. Pinning information

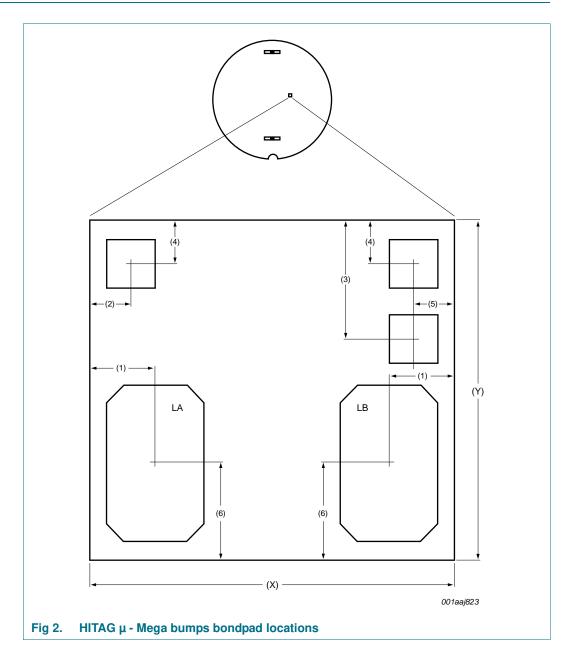

Table 3. HITAG  $\mu$  - Mega bumps dimensions

| Description                 | Dimension |

|-----------------------------|-----------|

| (X) chip size               | 550 μm    |

| (Y) chip size               | 550 μm    |

| (1) pad center to chip edge | 100.5 μm  |

| (2) pad center to chip edge | 48.708 μm |

| (3) pad center to chip edge | 180.5 μm  |

| (4) pad center to chip edge | 55.5 μm   |

| (5) pad center to chip edge | 48.508 μm |

HTMS1x01\_8x01

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2015. All rights reserved.

Table 3. HITAG  $\mu$  - Mega bumps dimensions

| Description                 | Dimension    |

|-----------------------------|--------------|

| (6) pad center to chip edge | 165.5 μm     |

| Bump Size:                  |              |

| LA, LB                      | 294 x 164 μm |

| Remaining pads              | 60 x 60 μm   |

Note: All pads except LA and LB are electrically disconnected after dicing.

# 8. Mechanical specification

### 8.1 Wafer specification

See Ref. 2 "General specification for 8" wafer on UV-tape with electronic fail die marking".

Table 4. Wafer specification

| varer specification      | ··                                                       |

|--------------------------|----------------------------------------------------------|

| Wafer                    |                                                          |

| Designation              | each wafer is scribed with batch number and wafer number |

| Diameter                 | 200 mm (8 inches)                                        |

| Thickness                | 150 μm ± 15 μm                                           |

| Process                  | CMOS 0.14 μm                                             |

| Batch size               | 25 wafers                                                |

| PGDW                     | 91981                                                    |

| Wafer backside           |                                                          |

| Material                 | Si                                                       |

| Treatment                | ground and stress release                                |

| Roughness                | $R_a$ max. 0.5 $\mu$ m, $R_t$ max. 5 $\mu$ m             |

| Chip dimensions          |                                                          |

| Die size without scribe  | 550 μm x 550 μm = 302500 μm <sup>2</sup>                 |

| Scribe line width        |                                                          |

| X-dimension              | 15 μm (scribe line width measured between nitride edges) |

| Y-dimension              | 15 μm (scribe line width measured between nitride edges) |

| Number of pads           | 5                                                        |

| Passivation on front     |                                                          |

| Туре                     | sandwich structure                                       |

| Material                 | PE-nitride (on top)                                      |

| Thickness                | 1.75 μm total thickness of passivation                   |

| Au bump                  |                                                          |

| Material                 | >99.9 % pure Au                                          |

| Hardness                 | 35 HV to 80 HV 0.005                                     |

| Shear strength           | >70 MPa                                                  |

| Height                   | 18 μm                                                    |

| Height uniformity        |                                                          |

| within a die             | ±2 μm                                                    |

| within a wafer           | ±3 μm                                                    |

| wafer to wafer           | ±4 μm                                                    |

| Bump flatness            | ±1.5 μm                                                  |

| Bump size                |                                                          |

| LA, LB                   | 294 μm × 164 μm                                          |

| TEST, GND, VDD           | 60 μm × 60 μm                                            |

| variation                | ±5 μm                                                    |

| Under bump metallization | sputtered TiW                                            |

HTMS1x01; HTMS8x01

HITAG μ transponder IC

### 8.1.1 Fail die identification

No inkdots are applied to the wafer.

Electronic wafer mapping (SECS II format) covers the electrical test results and additionally the results of mechanical/visual inspection.

See Ref. 2 "General specification for 8" wafer on UV-tape with electronic fail die marking".

### 8.1.2 Map file distribution

See Ref. 2 "General specification for 8" wafer on UV-tape with electronic fail die marking".

### 9. Functional description

### 9.1 Memory organization

The EEPROM has a capacity of up to 1760 bit and is organized in blocks of 4 bytes each (1 block = 32 bits). A block is the smallest access unit.

The HITAG  $\mu$  transponder IC is available with different memory sizes as shown in <u>Table 5</u> "Memory organization HITAG m (128-bit)", <u>Table 6 "Memory organization HITAG  $\mu$  Advanced (512 bit)" and <u>Table 7 "Memory organization HITAG  $\mu$  Advanced+ (1760 bit)".</u></u>

For permanent lock of blocks please refer to Section 14.9 "LOCK BLOCK".

### 9.1.1 Memory organization HITAG $\mu$ transponder ICs

Table 5. Memory organization HITAG μ (128-bit)

| Block address | Content                              | Password Access |

|---------------|--------------------------------------|-----------------|

| FFh           | User Config                          |                 |

| FEh           | PWD                                  |                 |

| 03h           |                                      |                 |

| 02h           | ISO 11784/ISO 11785 128 bit TTF data | bit3=0 R/W[2]   |

| 01h           | 150 11784/150 11785 128 bit 11F data | bit3=1 RO[1]    |

| 00h           |                                      |                 |

<sup>[1]</sup> RO: Read without password, write with password

<sup>[2]</sup> R/W: Read and write without password

### 9.1.2 Memory organization HITAG μ Advanced

Table 6. Memory organization HITAG μ Advanced (512 bit)

| Block address | Content                              | Password Access |

|---------------|--------------------------------------|-----------------|

| FFh           | User Config                          |                 |

| FEh           | PWD                                  |                 |

| 0Fh           |                                      |                 |

| 0Eh           |                                      |                 |

| 0Dh           |                                      |                 |

| 0Ch           |                                      |                 |

| 0Bh           |                                      |                 |

| 0Ah           | User Memory                          | bit4=0 R/W[2]   |

| 09h           | Oser Memory                          | bit4=1 RO[1]    |

| 08h           |                                      |                 |

| 07h           |                                      |                 |

| 06h           |                                      |                 |

| 05h           |                                      |                 |

| 04h           |                                      |                 |

| 03h           |                                      |                 |

| 02h           | ISO 11784/ISO 11785 128-bit TTF data | bit3=0 R/W[2]   |

| 01h           | 100 11704/100 11703 120-bit 111 data | bit3=1 RO[1]    |

| 00h           |                                      |                 |

<sup>[1]</sup> RO: Read without password, write with password

<sup>[2]</sup> R/W: Read and write without password

### 9.1.3 Memory organization HITAG μ Advanced +

Table 7. Memory organization HITAG μ Advanced+ (1760 bit)

| Block address | Content                              | Password Access                             |

|---------------|--------------------------------------|---------------------------------------------|

| FFh           | User Config                          |                                             |

| FEh           | PWD                                  |                                             |

| 36h           |                                      |                                             |

| 35h           |                                      |                                             |

|               |                                      |                                             |

| 14h           | User Memory                          | bit6=0 bit5=0 R/W[2]<br>bit6=0 bit5=1 RO[1] |

| 13h           | Oser Memory                          | bit6=1 bit5=0 R/W(P)[3]                     |

| 12h           |                                      | bit6=1 bit5=1 R/W(P)[3]                     |

| 11h           |                                      |                                             |

| 10h           |                                      |                                             |

| 0Fh           |                                      |                                             |

| 0Eh           |                                      |                                             |

| 0Dh           |                                      |                                             |

| 0Ch           |                                      |                                             |

| 0Bh           |                                      |                                             |

| 0Ah           | User Memory                          | bit4=0 R/W[2]                               |

| 09h           | Oser Memory                          | bit4=1 RO[1]                                |

| 08h           |                                      |                                             |

| 07h           |                                      |                                             |

| 06h           |                                      |                                             |

| 05h           |                                      |                                             |

| 04h           |                                      |                                             |

| 03h           |                                      |                                             |

| 02h           | ISO 11784/ISO 11785 128-bit TTF data | bit3=0 R/W[2]                               |

| 01h           | 100 11704/100 11700 120-bit 111 data | bit3=1 RO[1]                                |

| 00h           |                                      |                                             |

<sup>[1]</sup> RO: Read without password, write with password

<sup>[2]</sup> R/W: Read and write without password

<sup>[3]</sup> R/W(P): Read and write with password

### 9.2 Memory configuration

The user configuration block consists of one configurable byte (Byte0) and three reserved bytes (Byte1 to Byte3)

The bits in the user configuration block enable a customized configuration of the HITAG  $\mu$  transponder ICs. In TTF mode the user can choose Bi-phase or Manchester encoding and also the data rate for the return link (bit0 to bit2). In RTF mode data rate and coding are fixed with 4 kbit/s Manchester encoding.

Fitting to ISO 11785 standard the default values are set for 4 kbit/s Bi-Phase encoding. The next four bits (bit 3 to bit 6) are used for password settings.

Three areas (TTF area(128bit), lower 512 bits and upper memory) can be restricted to read/write access.

The user configuration block (User Config) is programmable by using WRITE SINGLE BLOCK command at address FFh. Bits 7 to 31 (Byte1 to Byte3) are reserved for further usage.

The user configuration block (block address FFh) and the password block (block address FEh) can be locked with the LOCK BLOCK command.

#### Attention:

- · Pre-programmed default values are not locked!

- · Configuration block has to be locked to make data unalterable!

- The lock of the blocks is permanently and therefore irreversible!

Table 8. User configuration block to Byte0

| Byte0                       |                           |                           |                         |          | Description  |               |

|-----------------------------|---------------------------|---------------------------|-------------------------|----------|--------------|---------------|

| bit6                        | bit5                      | bit4                      | bit3                    | bit2     | bit1 0       | Bit-no.       |

| PWD (r/w) [2]<br>Bit512 Max | PWD (w) [1]<br>Bit512 Max | PWD (w) [1]<br>Bit128 511 | PWD (w) [1]<br>Bit0 127 | Encoding | Data rate    |               |

|                             |                           |                           |                         | 0 MCH    | '00' 2kbit/s | Value/meaning |

|                             |                           |                           |                         | 1 Bi-Ph. | '01' 4kbit/s |               |

|                             |                           |                           |                         |          | '10' 8kbit/s |               |

- [1] PWD(w)=1: read without password and write with password

- [2] PWD(r/w)=1: read and write with password

### 10. General requirements

The HITAG  $\mu$  transponder ICs are compatible with ISO 11785. At the time a HITAG  $\mu$  transponder IC is in the interrogator field it will respond according to ISO 11785.

A HITAG  $\mu$  advanced/advanced+ can be identified as a transponder being in the data exchange mode (advanced mode) by the type information in the reserved bit field sent to the RWD.

- Bit 15 of the ISO 11784 frame shall be set to '1' indicating that this is an HITAG  $\mu$  advanced/advanced+ in data exchange mode.

- Bit 16 of the ISO 11784 frame (additional data flag set to '1', indicating that the HITAG μ advanced/advanced+ in data exchange mode contains additional data in the user memory area.

To bring the HITAG  $\mu$  transponder ICs into the data exchange mode, the RWD needs to send a valid request or a valid switch command within the defined listening window.

A HITAG  $\mu$  transponder IC in data exchange mode only responds when requested by the RWD (RTF mode).

The identification code, all communication from reader to HITAG  $\mu$  transponder ICs and vice versa and the CRC error detection bits (if applicable) are transmitted starting with LSB first.

In the case that multiple HITAG  $\mu$  advanced/advanced+ in data exchange mode are in the interrogation field which cause collisions the RWD has to start the anticollision procedure as described in this document. Depending in which part of the ISO 11785 timing frame the collision is detected the RWD will start with the anticollision request.

The HITAG  $\mu$  transponder IC in data exchange mode switches back to the standard ISO 11785 mode when it :

- · is no longer in the interrogation field

- has terminated the data exchange mode operations and the interrogation field was switched off for at least 5 ms afterwards

## 11. HITAG μ transponder IC air interface

### 11.1 Downlink description

To transfer the HITAG  $\mu$  transponder ICs into the data exchange mode, the RWD's interrogation field needs be switched off. After this off-period, the interrogation field is switched on again, and either the SOF at the start of a valid request or the special switch command needs to be sent to the HITAG  $\mu$  transponder IC within the specified switch time window. The HITAG  $\mu$  transponder IC switches itself into the data exchange mode upon reception of any of the switch commands. In this mode, the HITAG  $\mu$  transponder IC respond when requested by the RWD (reader driven protocol).

The HITAG  $\mu$  transponder IC in data exchange mode switches back to the ISO 11785 mode after the interrogation field has been switched off for at least 5 ms.

HTMS1x01\_8x01

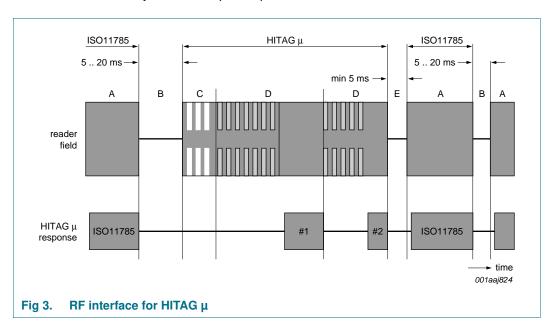

The steps necessary to transfer the HITAG  $\mu$  transponder IC into the data exchange mode are shown in Figure 3. The downlink communication takes place in period C and D. The example in Figure 3 shows two data blocks (#1 and #2) being selected by the RWD, which then are transmitted by the HITAG  $\mu$  transponder IC.

Table 9. RF interface for HITAG μ

| Cycle A: | The RWD reads the ISO 11785 frame.                                                                                                                                                                                                                                                             |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cycle B: | The RWD switches off the interrogation field for at least 5 ms in order to reset the HITAG $\boldsymbol{\mu}$ transponder IC.                                                                                                                                                                  |

| Cycle C: | The RWD sends either the SOF at the start of a valid request or the SWITCH command to the HITAG $\mu$ transponder IC in order to put it into the data exchange mode. Any of these has to be issued within the switch window after reset - as defined in Section 11.2 "Mode switching protocol" |

| Cycle D: | Read/Write (for HITAG $\mu$ transponder ICs) or Inventory (HITAG $\mu$ advanced/advanced+ transponder ICs) operation in the data exchange mode.                                                                                                                                                |

| Cycle E: | After all operations are finished or the HITAG $\mu$ transponder IC left the antenna field, the RWD switches off the field for at least 5 ms in order to poll for new incoming HITAG $\mu$ or HITAG $\mu$ advanced/advanced+.                                                                  |

### 11.2 Mode switching protocol

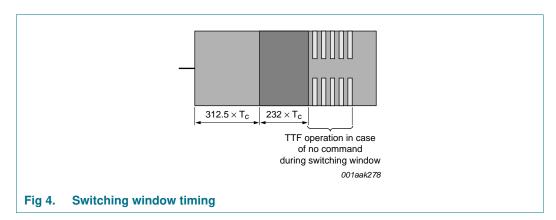

After powering the HITAG  $\mu$  transponder IC switches to the data exchange mode after receiving one of the two possible switch commands from the RWD during the specified switch window (see <u>Table 10</u> and <u>Figure 4</u> for details).

Table 10. HITAG μ transponder IC air interface parameters [1]

| Parameter                      | Description                                                                                                                                                                                               |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrogation field modulation | Amplitude modulation (ASK), 90 - 100%                                                                                                                                                                     |

| Encoding                       | Pulse Interval Encoding; Least Significant Bit (LSB) first                                                                                                                                                |

| Bit rate                       | 5.2 kbit/s typically                                                                                                                                                                                      |

| Mode switching                 | Either a specific 5 bit switch command or the detection of the SOF as part of a valid HITAG $\mu$ transponder IC command, transmitted after the interruption of the interrogation field for at least 5 ms |

| Mode switch timing             | HITAG $\mu$ transponder IC settling time: 312.5 $\times$ T $_C$ switch command window after HITAG $\mu$ transponder IC settling: 232.5 $\times$ T $_C$                                                    |

|                                | All within cycle C in Figure 3.                                                                                                                                                                           |

| Mode switch command            | 00011 or SOF sequence                                                                                                                                                                                     |

<sup>[1]</sup>  $T_{C...}$ Carrier period time (1/<sub>134.2</sub> kHz = 7.45 µs nominal)

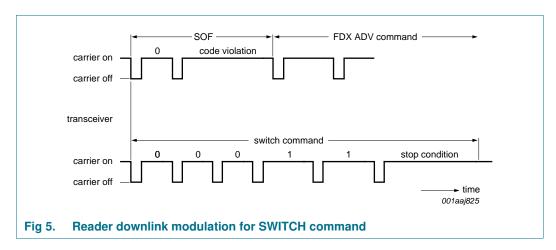

The RWD sends either the SOF at the start of a valid request or a special switch command to the HITAG  $\mu$  (as shown in <u>Figure 5</u>) in order to transfer it into the data exchange mode.

### 11.2.1 SWITCH

Setting the transponder into data exchange mode (advanced mode) is done by sending SOF pattern or the switch command within the listening window (232.5 x  $T_C$ ). The SWITCH command itself does not contain SOF and EOF.

Table 11. SWITCH Command

| Command | Description |

|---------|-------------|

| 5       | No. of bits |

| 00011   |             |

# 11.3 Downlink communication signal interface - RWD to HITAG $\mu$ transponder IC

### 11.3.1 Modulation parameters

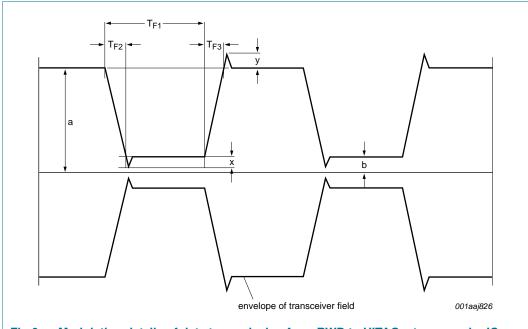

Communications between RWD and HITAG  $\mu$  transponder IC takes place using ASK modulation with a modulation index of m > 90%.

Fig 6. Modulation details of data transmission from RWD to HITAG  $\mu$  transponder IC

Table 12. Modulation coding times [1][2]

| Symbol          | Min            | Max                         |

|-----------------|----------------|-----------------------------|

| m = (a-b)/(a+b) | 90%            | 100%                        |

| T <sub>F1</sub> | $4 \times T_c$ | $10 \times T_c$             |

| T <sub>F2</sub> | 0              | $0.5 \times T_{F1}$         |

| T <sub>F3</sub> | 0              | $0.5 \times T_{\text{Fd0}}$ |

| Х               | 0              | 0.05 × a                    |

| у               | 0              | 0.05 × a                    |

<sup>[1]</sup>  $T_{F3}$  shall not exceed  $T_{Fd0}$  -  $T_{F1}$  -  $3 \times T_c$

<sup>[2]</sup>  $T_{C...}$ Carrier period time (1/<sub>134.2</sub> kHz = 7.45  $\mu$ s nominal)

### 11.3.2 Data rate and data coding

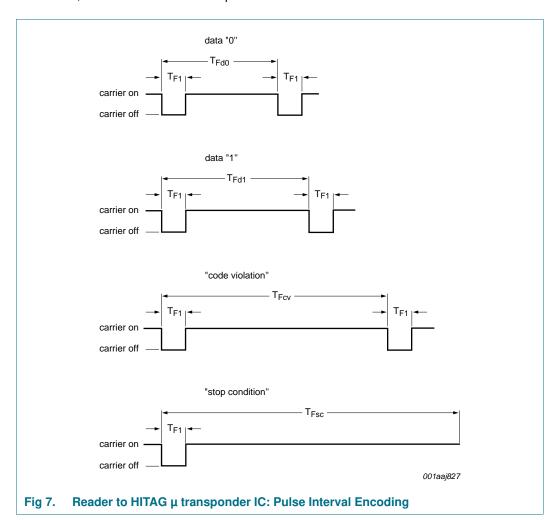

The RWD to HITAG  $\mu$  transponder IC communication uses Pulse Interval Encoding. The RWD creates pulses by switching the carrier off as described in <u>Figure 7</u>. The time between the falling edges of the pulses determines either the value of the data bit '0', the data bit '1', a code violation or a stop condition.

Assuming equal distributed data bits '0' and '1', the data rate is in the range of about 5.2 kbit/s.

Table 13. Data coding times [1]

| Meaning             | Symbol           | Min                      | Max             |

|---------------------|------------------|--------------------------|-----------------|

| Carrier off time    | T <sub>F1</sub>  | $4 \times T_c$           | $10 \times T_c$ |

| Data "0" time       | T <sub>Fd0</sub> | $18 \times T_c$          | $22 \times T_c$ |

| Data "1" time       | T <sub>Fd1</sub> | $26 \times T_c$          | $30 \times T_c$ |

| Code violation time | T <sub>Fcv</sub> | $34 \times T_{\text{c}}$ | $38 \times T_c$ |

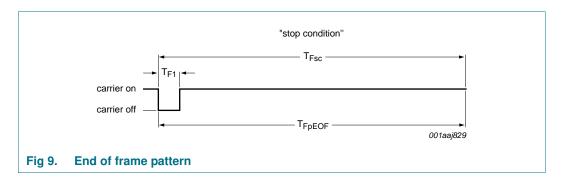

| Stop condition time | T <sub>Fsc</sub> | $\geq 42 \times T_c$     | n/a             |

[1]  $T_{C...}$ Carrier period time ( $1/_{134.2}$  kHz = 7.45  $\mu$ s nominal)

HTMS1x01\_8x01

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2015. All rights reserved.

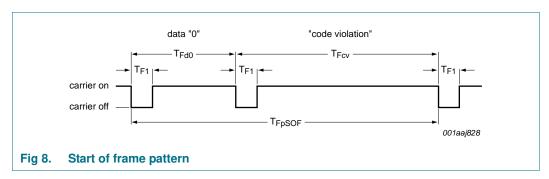

### 11.3.3 RWD - Start of frame pattern

The RWD requests in the data exchange mode always a start with a SOF pattern for ease of synchronization. The SOF pattern consists of an encoded data bit '0' and a 'code violation'.

The HITAG  $\mu$  advanced/advanced+ is ready to receive a SOF from the RWD within 1.2 ms after having sent a response to the RWD.

The HITAG  $\mu$  advanced/advanced+ is ready to receive a SOF or switch command from the RWD within 2.33 ms after the RWD has established the powering field.

### 11.3.4 RWD - End of frame pattern

For slot switching during a multi-slot anticollision sequence, the RWD request is an EOF pattern. The EOF pattern is represented by a RWD 'Stop condition'.

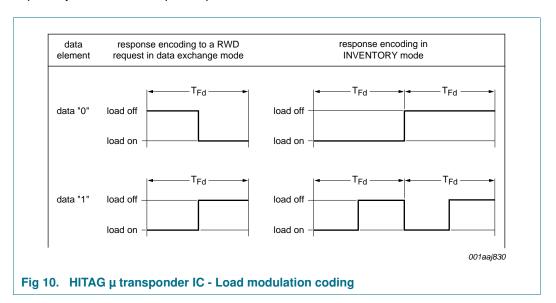

### 11.4 Communication signal interface - HITAG μ transponder IC to RWD

### 11.4.1 Data rate and data coding

The HITAG  $\mu$  transponder IC accepts the following data rates and encoding schemes:

- 1/T<sub>Fd</sub> Differential bi-phase coded data signal in the ISO 11785 mode, without SOF and EOF

- 1/T<sub>Fd</sub> Manchester coded data signal on the response to the HITAG μ advanced/advanced+ commands in data exchange mode

- 1/(2 ×T<sub>Fd</sub>) dual pattern data coding when responding within the inventory process

- TTF mode (not ISO 11785 compliant): 1/(2 × T<sub>Fd</sub>), 2/T<sub>Fd</sub> Manchester or bi-phase coded

$$T_{Fd} = 32 / f_c = 32 \times T_c$$

**Remark:** The slower data rate used during the inventory process allows for improving the collision detection when several HITAG  $\mu$  transponder ICs are present in the RWD field, especially if some HITAG  $\mu$  transponder ICs are in the near field and others in the far field.

data 1 0 1 1 1 0 0 1

Bi-phase 001aaj831

Fig 11. HITAG  $\mu$  transponder IC - Differential Bi-Phase Modulation

Differential Bi-phase (or FM0 respectively) contains a transition in the center of bit conversion representing Data '0' and no one for Data '1'. At the beginning of every bit modulation a level transition must be performed.

HTMS1x01\_8x01

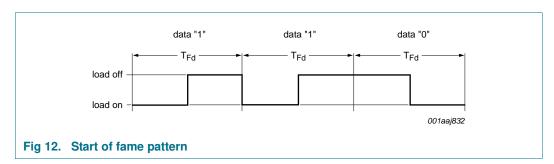

### 11.4.2 Start of frame pattern

The HITAG  $\mu$  transponder IC response - if not in ISO 11785 compliant mode - always starts with a SOF pattern. The SOF is a Manchester encoded bit sequence of '110'.

### 11.4.3 End of frame pattern

A specific EOF pattern is neither used nor specified for the HITAG  $\mu$  transponder IC response. An EOF is detected by the reader if there is no load modulation for more than two data bit periods ( $T_{Ed}$ ).

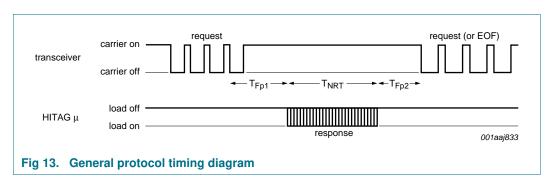

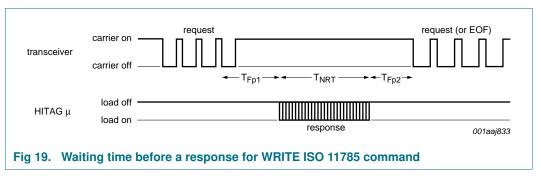

### 12. General protocol timing specification

For requests where an EEPROM erase and/or programming operation is required, the transponder IC returns its response when it has completed the write/lock operation. This will be after 20 ms upon detection of the last falling edge of the interrogator request or after the interrogator has switched off the field.

# 12.1 Waiting time before transmitting a response after an EOF from the RWD

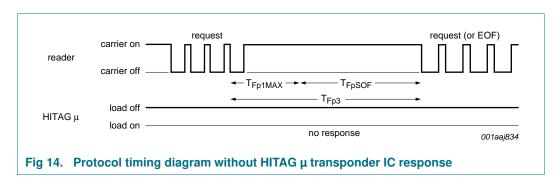

When the HITAG advanced/advanced+ in data exchange mode has detected an EOF of a valid RWD request or when this EOF is in the normal sequence of a valid RWD request, it waits for  $T_{\text{Fp1}}$  before starting to transmit its response to a RWD request or when switching to the next slot in an inventory process.

T<sub>Ep1</sub> starts from the detection of the falling edge of the EOF received from the RWD.

**Remark:** The synchronization on the falling edge from the RWD to the EOF of the HITAG  $\mu$  transponder ICs is necessary to ensure the required synchronization of the HITAG  $\mu$  transponder IC responses.

The minimum value of  $T_{p1}$  is  $T_{p1min} = 204 \times T_{C}$

The typical value of  $T_{Fp1}$  is  $T_{Fp1typ} = 209 \times T_{C}$

The maximum value of  $T_{Fp1}$  is  $T_{Fp1max} = 213 \times T_{C}$

If the HITAG  $\mu$  transponder IC detects a carrier modulation during this time ( $T_{Fp1}$ ), it shall reset its  $T_{Fp1}$ -timer and wait for a further time ( $T_{Fp1}$ ) before starting to transmit its response to a RWD request or to switch to the next slot when in an inventory process.

### 12.2 RWD waiting time before sending a subsequent request

- When the RWD has received a HITAG  $\mu$  advanced/advanced+ response to a previous request other than inventory and quiet, it needs to wait  $T_{Fp2}$  before sending a subsequent request.  $T_{Fp2}$  starts from the time the last bit has been received from the HITAG  $\mu$  advanced/advanced+.

- When the RWD has sent a quiet request, it needs to wait  $T_{Fp2}$  before sending a subsequent request.  $T_{Fp2}$  starts from the end of the quiet request's EOF (falling edge of EOF pulse +  $42 \times T_C$ ). This results in awaiting time of  $(150 \times T_C + 42 \times T_C)$  before the next request.

The minimum value of  $T_{Fp2}$  is  $T_{Fp2min} = 150 \times T_C$  ensures that the HITAG  $\mu$  advanced/advanced+ ICs are ready to receive a subsequent request.

**Remark:** The RWD needs to wait at least 2.33 ms after it has activated the electromagnetic field before sending the first request, to ensure that the HITAG  $\mu$  transponder ICs are ready to receive a request.

· When the RWD has sent an inventory request, it is in an inventory process.

### 12.3 RWD waiting time before switching to next inventory slot

An inventory process is started when the RWD sends an inventory request. For a detailed explanation of the inventory process refer to Section 14.3 and Section 14.4.

To switch to the next slot, the RWD sends an EOF after waiting a time period specified in the following sub-clauses.

#### 12.3.1 RWD started to receive one or more HITAG μ transponder IC responses

During an inventory process, when the RWD has started to receive one or more HITAG  $\mu$  advanced/advanced+ transponder IC responses (i.e. it has detected a HITAG  $\mu$  advanced+ transponder IC SOF and/or a collision), it shall

- wait for the complete reception of the HITAG μ advanced/advanced+ transponder IC responses (i.e. when a last bit has been received or when the nominal response time T<sub>NRT</sub> has elapsed),

- wait an additional time T<sub>Fp2</sub> and then send an EOF to switch to the next slot, if a 16 slot anticollision request is processed, or send a subsequent request (which could be again an inventory request).

$T_{\text{Fp2}}$  starts from the time the last bit has been received from the HITAG  $\mu$  advanced/advanced+ transponder IC.

The minimum value of  $T_{Fp2}$  is  $T_{Fp2min} = 150 \times T_C$ .

$T_{\text{NRT}}$  is dependant on the anticollisions current mask value and on the setting of the CRCT flag.

### 12.3.2 RWD receives no HITAG μ transponder IC response

During an inventory process, when the RWD has received no HITAG  $\mu$  advanced/advanced+ transponder IC response, it needs to wait  $T_{Fp3}$  before sending a subsequent EOF to switch to the next slot, if a 16 slot anticollision request is processed, or sending a subsequent request (which could be again an inventory request).

T<sub>Fp3</sub> starts from the time the RWD has generated the falling edge of the last sent EOF.

The minimum value of  $T_{Fp3}$  is  $T_{Fp3min} = T_{Fp1max} + T_{FpSOF}$ .

$T_{\text{FpSOF}}$  is the time duration for a HITAG  $\mu$  advanced/advanced+ transponder to transmit an SOF to the reader.

Table 14. Overview timing parameters [1]

| Symbol             | Min                                      | Max                  |

|--------------------|------------------------------------------|----------------------|

| T <sub>FpSOF</sub> | $3 \times T_{Fd}$                        | $3\times T_{Fd}$     |

| T <sub>Fp1</sub>   | 204 ×T <sub>C</sub>                      | 213 × T <sub>C</sub> |

| T <sub>Fp2</sub>   | 150 × T <sub>C</sub>                     | -                    |

| T <sub>Fp3</sub>   | T <sub>Fp1max</sub> + T <sub>FpSOF</sub> | -                    |

[1]  $T_{C...}$ Carrier period time ( $1/_{134.2}$  kHz = 7.45 µs nominal)

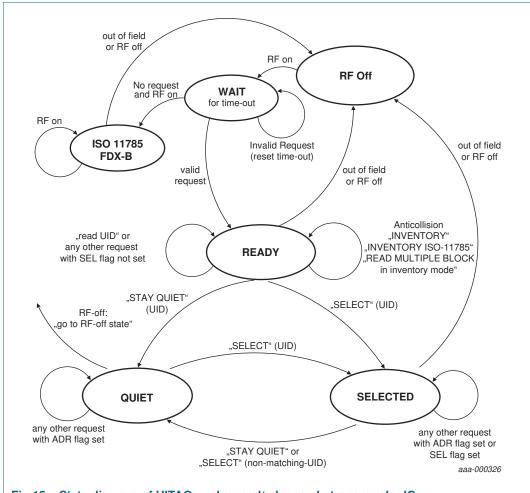

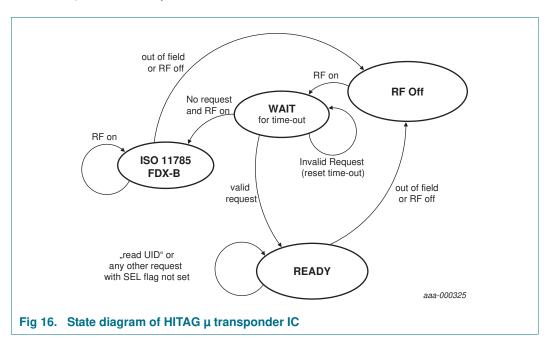

### 13. State diagram

### 13.1 General description of states

#### **RF Off**

The powering magnetic field is switched off or the HITAG  $\mu$  transponder IC is out of the field.

#### **WAIT**

After start up phase, the HITAG μ transponder IC is ready to receive the first command.

#### **READY**

The HITAG  $\mu$  transponder IC enters this state after a valid command, except of the STAY QUIET, SELECT or WRITE-ISO11785 command. If there are several HITAG  $\mu$  transponder ICs at the same time in the field of the RWD antenna, the anticollision sequence can be started to determine the UID of every HITAG  $\mu$  transponder IC.

#### **SELECTED**

The HITAG  $\mu$  transponder IC enters the Selected state after receiving the SELECT command with a matching UID. In the Selected state the respective commands with SEL=1 are valid only for selected transponder.

Only one HITAG  $\mu$  transponder IC can be selected at one time. If one transponder is selected and a second transponder receives the SELECT Command, the first transponder will automatically change to Quiet state.

#### **QUIET**

The HITAG  $\mu$  transponder IC enters this state after receiving a STAY QUIET command or when he was in selected state and receives a SELECT command addressed to another transponder.

In this state, the HITAG  $\boldsymbol{\mu}$  transponder IC reacts to any request commandos where the ADR flag is set.

#### **ISO 11785 STATE**

In this state the HITAG  $\mu$  transponder IC replies according to the ISO 11785 protocol.

#### Remark:

In case of an invalid command the transponder will remain in his actual state.

### 13.2 State diagram HITAG $\mu$ advanced/advanced+

Fig 15. State diagram of HITAG μ advanced/advanced+ transponder ICs

### 13.3 State diagram HITAG $\mu$

#### 13.4 Modes

#### 13.4.1 ISO 11785 Mode

This mode is also named TTF (Transponder Talks First).

Every time a transponder IC is activated by the field it starts executing this mode. After waiting the maximum listening window time (see <u>Section 11.2</u>) the transponder IC sends continuously its TTF data (128-bit).

The TTF data stored in the memory will be not checked for ISO compliance, therefore data will be sent as stored in the EEPROM.

Receiving a valid command or a switch command within the listening window sets the transponder IC into RTF (Reader Talks First) mode.

#### 13.4.2 RTF Mode

In this mode the transponder IC reacts only to RWD request commands as presented in <u>Section 14</u>. A valid request consists of a command sent to the transponder IC being in matching state (therefore see tables in <u>Section 14</u> and transponder ICs state machine in <u>Section 13</u>).

#### 13.4.3 Anticollision

The RWD is the master of the communication with one or multiple transponder ICs. It starts the anticollision sequence by issuing the inventory request (see <u>Section 14.3</u>). Within the RWD command the NOS flag must be set to the desired setting (1 or 16 slots) and add the mask length and the mask value after the command field.

The mask length n indicates the number of significant bits of the mask value. It can have any value between 0 and 44 when 16 slots are used and any value between 0 and 48 when 1 slot is used.

The next two subsections summarize the actions done by the transponder IC during an inventory round.

#### 13.4.3.1 Anticollision with 1 slot

The transponder IC will receive one ore more inventory commands with NOS = '1'. Every time the transponder ICs fractional or whole UID matches the mask value of RWD's request it responses with remaining UID without mask value.

Transponder ICs responses are modulated by dual pattern data coding as described in Section 11.4.

#### 13.4.3.2 Anticollision with 16 slots

The transponder IC will receive several inventory commands with NOS = '0' defining an amount of 16 slots. Within the request there is the mask specified by length and value (sent LSB first).

In case of mask length = '0' the four least significant bits of transponder ICs UID become the starting value of transponder IC's slot counter.

In case of mask length  $\neq$  '0' the received fractional mask is compared to transponder IC's UID. If it matches the starting value for transponder IC's slot number will be calculated. Starting at last significant bit of the sent mask the next four less significant bits of UID are used for this value. At the same time transponder IC's slot counter is reset to '0'.

Now the RWD begins its anticollision algorithm. Every time the transponder IC receives an EOF it increments slot-counter. Now if mask value and slot-counter value are matching the transponder IC responses with the remaining UID without mask value but with slot number

In case of collision within one slot the RWD changes the mask value and starts again running its algorithm.

### 14. Command set

The first part of this section (Section 14.1) describes the flags used in every RWD command. The following subsections (Section 14.3 until Section 14.13) explain all implemented commands and their suitable transponder IC responses which are done with tables showing the command itself and suitable responses.

Within tables flags, parameter bits and parts of a response written in braces are optional. That means if the suitable flag is set resulting transponder IC's action will be performed according to Section 14.1.

Every command except the Switch command is embedded in SOF and EOF pattern. As described in <u>Table 15</u> and <u>Table 16</u> sending and receiving data is done with the least significant bit of every field on first position.

#### Important information:

In this document the fields (i.e. command codes) are written with most significant bit first.

Table 15. Reader - Transponder IC transmission [1][2]

| SOF | Flags   | Commands | Parameters | Data    | CRC-16  | EOF |

|-----|---------|----------|------------|---------|---------|-----|

| -   | 5       | 6        | var.       | var.    | (16)    | -   |

| -   | LSB MSB | LSB MSB  | LSB MSB    | LSB MSB | LSB MSB | -   |

<sup>[1]</sup> values in braces are optional

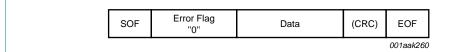

Table 16. Transponder IC - Reader transmission [1][2]

| SOF | Error flag | Data/Error code | CRC-16  | EOF |

|-----|------------|-----------------|---------|-----|

| -   | 1          | var.            | (16)    | -   |

| -   | -          | LSB MSB         | LSB MSB | -   |

<sup>[1]</sup> values in braces are optional

<sup>[2]</sup> data is sent with least significant bit first

<sup>[2]</sup> data is sent with least significant bit first

### 14.1 Flags

Every request command contains five flags which are sent in order Bit 1 (LSB) to Bit 5 (MSB). The specific meaning depends on the context.

**Table 17. Command Flags**

| Bit | Flag            | Full name               | Value | Description                                    |

|-----|-----------------|-------------------------|-------|------------------------------------------------|

| 1   | PEXT            | Protocol EXTension      | 0     | No protocol format extension                   |

|     |                 |                         | 1     | RFU                                            |

| 2   | INV             | INVentory               | 0     | Flag 4 and Flag 5 are 'SEL' and 'ADR' Flag     |

|     |                 |                         | 1     | Flag 4 and Flag 5 are 'RFU' and 'NOS' Flag     |

| 3   | CRCT            | CRC-Transponder         | 0     | Transponder IC respond without CRC             |

|     |                 |                         | 1     | Transponder IC respond contains CRC            |

| 4   | SEL<br>(INV==0) | SELect                  |       | in combination with ADR (see <u>Table 19</u> ) |

| 5   | ADR<br>(INV==0) | ADdRess                 |       | in combination with SEL (see <u>Table 19</u> ) |

| 4   | RFU<br>(INV==1) | Reserved for future use | 0     | this flag is not used and set to '0'           |

| 5   | NOS             |                         | 0     | 16 slots while performing anti-collision       |

|     | (INV==1)        |                         | 1     | 1 slot while performing anti-collision         |

Table 18. Command Flags - Bit order

|        | MSB<br>bit5 | bit4 | bit3 | bit2 | LSB<br>bit1 |

|--------|-------------|------|------|------|-------------|

| INV==0 | ADR         | SEL  | CRCT | INV  | PEXT        |

| INV==1 | NOS         | RFU  | CRCT | INV  | PEXT        |

Table 19. Meaning of ADR and SEL flag

| ADR | SEL | Meaning                                                                         |

|-----|-----|---------------------------------------------------------------------------------|

| 0   | 0   | Request without UID, all transponder ICs in READY state shall respond           |

| 1   | 0   | Request contains UID, one transponder IC (with corresponding UID) shall respond |

| 0   | 1   | Request without UID, the transponder IC in SELECTED state shall respond         |

| 1   | 1   | Reserved for future use                                                         |

#### Note:

For HITAG μ inventory (INV) flag and select (SEL) flag must be set to '0'

### 14.2 Error handling

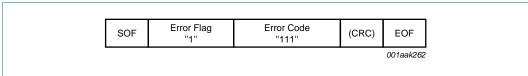

In case an error has been occurred the transponder IC responses with the set error flag and the three bit code '111' (meaning 'unknown error').

The general response format in case of an error response is shown in <u>Table 20</u> whereas commands not supporting error responses are excluded. In case of an unsupported command there will be no response. The format is embedded into SOF and EOF.

Table 20. Response format in error case

| Error flag | Error code | CRC-16 | Description |

|------------|------------|--------|-------------|

| 1          | 3          | (16)   | No. of bits |

| 1          | 111        |        |             |

Fig 17. HITAG  $\mu$  transponder IC response - in case of no error

Fig 18. HITAG  $\mu$  transponder IC response - in error case

#### 14.3 INVENTORY

### [Advanced, Advanced+]

Upon reception of this command without error, all transponder ICs in the ready state shall perform the anticollision sequence. The inventory (INV) flag shall be set to '1'. The NOS flag determines whether 1 or 16 slots are used.

If a transponder IC detects any error, it shall remain silent.

Table 21. INVENTORY - Request format (00h)

| Flags   | Command | Mask length        | Mask value | CRC-16 | Description         |

|---------|---------|--------------------|------------|--------|---------------------|

| 5       | 6       | 6                  | n          | (16)   | No. of bits         |

| 10(1)10 | 000000  | 0 ≤ n ≤ UID length | UID Mask   |        | AC with 1 timeslot  |

| 00(1)10 | 000000  | 0 ≤ n ≤ UID length | UID Mask   |        | AC with 16 timeslot |

Table 22. Response to a successful INVENTORY request [1][2]

| Error Flag | Data                             | CRC-16 | Description |

|------------|----------------------------------|--------|-------------|

| 1          | 48 - n                           | (16)   | No. of bits |

| 0          | Remaining UID without mask value |        |             |

<sup>[1]</sup> Error and CRC are Manchester coded, UID is dual pattern coded

Error Flag set to '0' indicates no error.

<sup>[2]</sup> Response within the according time slot

#### **14.4 INVENTORY ISO 11785**

#### [Advanced, Advanced+]

Upon reception of this command without error, all transponder ICs in the ready state are performing the anticollision sequence. The inventory (INV) flag is set to '1'. The NOS flag determines whether 1 or 16 slots are used.

In contrast to INVENTORY command the transponder IC (holding requested slot) sends the 64-bit ISO 11785 number in addition to remaining UID. The 64-bit number is taken from a fixed area of EEPROM. It will not be checked on ISO 11785 compliance before sending.

If a transponder IC detects any error, it remains silent.

Table 23. INVENTORY ISO 11785 - request format (23h)

| Flags   | Command | Mask length              | Mask value | CRC-16 | Description         |

|---------|---------|--------------------------|------------|--------|---------------------|

| 5       | 6       | 6                        | n          | (16)   | No. of bits         |

| 10(1)10 | 100011  | $0 \le n \le UID$ length | UID Mask   |        | AC with 1 timeslot  |

| 00(1)10 | 100011  | $0 \le n \le UID$ length | UID Mask   |        | AC with 16 timeslot |

Table 24. Response to a successful INVENTORY ISO 11785 request[1]

| Error Flag | Data 1                           | Data 2           | CRC-16 | Description |

|------------|----------------------------------|------------------|--------|-------------|

| 1          | 48 - n                           | 64               | (16)   | No. of bits |

| 0          | Remaining UID without mask value | ISO 11785 number |        |             |

<sup>[1]</sup> Error, CRC and ISO 11785 number are Manchester coded, UID is dual pattern coded

### 14.5 STAY QUIET

#### [Advanced, Advanced+]

Upon reception of this command without error, a transponder IC in either ready state or selected state enters the quiet state and shall not send back a response.

The STAY QUIET command with both SEL and ADR flag set to '0' or both set to '1' is not allowed.

There is no response to the STAY QUIET request, even if the transponder detects an error

Table 25. STAY QUIET - request format(01h)

| Flags   | Command | Data | CRC-16 | Description  |

|---------|---------|------|--------|--------------|

| 5       | 6       | (48) | (16)   | No. of bits: |

| 00(1)00 | 000001  | -    |        | without UID  |

| 11(1)00 | 000001  | UID  |        | with UID     |

### **14.6 READ UID**

### [μ, Advanced, Advanced+]

Upon reception of this command without error all transponder ICs in the ready state are sending their UID.

The addressed (ADR), the select (SEL), the inventory (INV) and the (PEXT) flag are set to '0'.

Table 26. READ UID - request format (02h)

| Flags   | Command | CRC-16 | Description |

|---------|---------|--------|-------------|

| 5       | 6       | (16)   | No. of bits |

| 00(1)00 | 000010  |        |             |

#### Table 27. Response to a successful READ UID request

| Error flag | Data | CRC-16 | Description |

|------------|------|--------|-------------|

| 1          | 48   | (16)   | No. of bits |

| 0          | UID  |        |             |

Error flag set to '0' indicates no error.

#### 14.7 READ MULTIPLE BLOCK

#### [µ, Advanced, Advanced+]

Upon reception of this command without error, the transponder reads the requested block(s) and sends back their value in the response. The blocks are numbered from 0 to 255.

The number of blocks in the request is one less than the number of blocks that the transponder returns in its response i.e. a value of '6' in the 'Number of blocks' field requests to read 7 blocks. A value '0' requests to read a single block.

Table 28. READ MULTIPLE BLOCKS (advanced/advanced+) - request format (12h)

| Flags   | Command | Data 1 | Data 2                | Data 3           | CRC-16 | Description                   |

|---------|---------|--------|-----------------------|------------------|--------|-------------------------------|

| 5       | 6       | (48)   | 8                     | 8                | (16)   | No. of bits                   |

| 00(1)00 | 010010  | -      | First block<br>number | Number of blocks |        | without UID in READY state    |

| 10(1)00 | 010010  | UID    | First block<br>number | Number of blocks |        | with UID in<br>READY<br>state |

| 01(1)00 | 010010  | -      | First block<br>number | Number of blocks |        | without UID in SELECTED state |

Table 29. READ MULTIPLE BLOCKS ( $\mu$ ) - request format (12h)

| Flags   | Command | Data 1 | Data 2                | Data 3           | CRC-16 | Description                   |

|---------|---------|--------|-----------------------|------------------|--------|-------------------------------|

| 5       | 6       | (48)   | 8                     | 8                | (16)   | No. of bits                   |

| 00(1)00 | 010010  | -      | First block<br>number | Number of blocks |        | without UID in READY state    |

| 10(1)00 | 010010  | UID    | First block<br>number | Number of blocks |        | with UID in<br>READY<br>state |

Table 30. Response to a successful READ MULTIPLE BLOCKS request

| Error Flag | Data                   | CRC-16 | Description |

|------------|------------------------|--------|-------------|

| 1          | 32 x Number of blocks  | (16)   | No. of bits |

| 0          | User memory block data |        |             |

### 14.7.1 READ MULTIPLE BLOCKS in INVENTORY mode

### [Advanced, Advanced+]

The READ MULTIPLE BLOCK command can also be sent in inventory mode (which is marked by INV-Flag = '1' within the request). Here request and response will change as shown in following tables.

If the transponder detects an error during the inventory sequence, it shall remain silent.

Table 31. READ MULTIPLE BLOCKS - request format (12h)

| Flags   | Command | Mask<br>length           | Mask<br>value | Parameter 1        | Parameter 2      | CRC-16 | Description         |

|---------|---------|--------------------------|---------------|--------------------|------------------|--------|---------------------|

| 5       | 6       | 6                        | n             | 8                  | 8                | (16)   | No. of bits         |

| 10(1)10 | 010010  | $0 \le n \le UID$ length |               | First block number | Number of blocks |        | AC with 1 timeslot  |

| 00(1)10 | 010010  | $0 \le n \le UID$ length |               | First block number | Number of blocks |        | AC with 16 timeslot |

After receiving RWD's command without error the transponder IC transmits the remaining section of the UID in dual pattern code. The following data (Error Flag, Data 2, optional CRC in no error case; Error Flag, Error Code, optional CRC in error case) is transmitted in Manchester Code.

Table 32. READ MULTIPLE BLOCKS in INVENTORY mode Response format [1]

| Error Flag | Data 1                                        | Data 2                 | CRC-16 | Description |

|------------|-----------------------------------------------|------------------------|--------|-------------|

| 1          | 48 - n                                        | 32 x number of blocks  | (16)   | No.of bits  |

| 0          | Remaining section of UID (without mask value) | User memory block data |        |             |

[1] Error, CRC and Data are Manchester coded, UID is dual pattern coded

### 14.8 WRITE SINGLE BLOCK

### [µ, Advanced, Advanced+]

Upon reception of this command without error, the transponder IC writes 32-bit of data into the requested user memory block and report the success of the operation in the response.

Table 33. WRITE SINGLE BLOCK (advanced/advanced+) - request format (14h)

| Flags     | Command | Data 1 | Data 2       | Data 3     | CRC-16 | Description                   |

|-----------|---------|--------|--------------|------------|--------|-------------------------------|

| 5         | 6       | (48)   | 8            | 32         | (16)   | No. of bits                   |

| (1)0(1)00 | 010100  | -      | block number | block data |        | without UID in READY state    |

| 0(1)(1)00 | 010100  | UID    | block number | block data |        | with UID in<br>READY<br>state |

| 01(1)00   | 010100  | -      | block number | block data |        | without UID in SELECTED state |

#### Table 34. WRITE SINGLE BLOCK (μ) - request format (14h)

| Flags   | Command | Data 1 | Data 2       | Data 3     | CRC-16 | Description                      |

|---------|---------|--------|--------------|------------|--------|----------------------------------|

| 5       | 6       | (48)   | 8            | 32         | (16)   | No. of bits                      |

| 00(1)00 | 010100  | -      | block number | block data |        | without UID<br>in READY<br>state |

| 10(1)00 | 010100  | UID    | block number | block data |        | with UID in<br>READY<br>state    |

Table 35. Response to a successful WRITE SINGLE BLOCK request

| Error Flag | CRC-16 | Description |

|------------|--------|-------------|

| 1          | (16)   | No. of bits |

| 0          |        |             |

#### 14.9 LOCK BLOCK

#### [µ, Advanced, Advanced+]

Upon reception of this command without error, the transponder IC is write locking the requested block (block size = 32-bit) permanently.

Blocks within the block address range from 00h to 17h as well as FEh and FFh can be locked individually.

For HITAG  $\mu$  advanced+ transponder IC a LOCK BLOCK command with a block number value between 18h to 36h will lock all blocks within the block address range 18h to 36h.

In case a password is applied to the memory a lock is only possible after a successful login.

Table 36. LOCK BLOCK (advanced/advanced+) - request format (16h)

| Flags   | Command | Data 1 | Data 2       | CRC-16 | Description                      |

|---------|---------|--------|--------------|--------|----------------------------------|

| 5       | 6       | (48)   | 8            | (16)   | No. of bits                      |

| 00(1)00 | 010110  | -      | block number |        | without UID<br>in READY<br>state |

| 10(1)00 | 010110  | UID    | block number |        | with UID in<br>READY<br>state    |

| 01(1)00 | 010110  | -      | block number |        | without UID in SELECTED state    |

Table 37. LOCK BLOCK (μ) - request format (16h)

| Flags   | Command | Data 1 | Data 2       | CRC-16 | Description                   |

|---------|---------|--------|--------------|--------|-------------------------------|

| 5       | 6       | (48)   | 8            | (16)   | No. of bits                   |

| 00(1)00 | 010110  | UID    | block number |        | without UID in READY state    |

| 10(1)00 | 010110  | -      | block number |        | with UID in<br>READY<br>state |

Table 38. Response to a successful LOCK BLOCK request

| Error flag | CRC-16 | Description |

|------------|--------|-------------|

| 1          | (16)   | No. of bits |

| 0          |        |             |

#### **14.10 SELECT**

#### [Advanced, Advanced+]

The SELECT command is always be executed with SEL flag set to '0' and ADR flag set to '1'. There are several possibilities upon reception of this command without error:

- If the UID, received by the transponder IC, is equal to its own UID, the transponder IC enters the Selected state and shall send a response.

- · If the received UID is different there are two possibilities

- A transponder IC in a non-selected state (QUIET or READY) is keeping its state and not sending a response.

- The transponder IC in the Selected state enters the Quiet state and does not send a response.

#### Table 39. SELECT - request format (18h)

| Flags   | Command | Data 1 | CRC-16 | Description |

|---------|---------|--------|--------|-------------|

| 5       | 6       | 48     | (16)   | No. of bits |

| 10(1)00 | 011000  | UID    |        |             |

#### Table 40. Response to a successful SELECT request

| Error flag | CRC-16   | Description |

|------------|----------|-------------|

| 1          | (16-bit) | No. of bits |

| 0          |          |             |

### 14.11 WRITE ISO 11785 (custom command)

#### [μ, Advanced, Advanced+]

Upon reception of this command without error, the transponder IC (in Ready state) writes 128-bit of ISO 11785 TTF data into suitable reserved memory block and report the success of the operation in the response. The user does not have to attend whether the data is compliant to ISO 11785 or not. The command data block is sent exactly the same way as it is sent by the transponder IC in TTF mode (Header, 64-bit ID, CRC...) after entering the field again.

There are two different command codes one for locking the TTF area after successful write command and one without locking.

The command must be completed by a reset of the IC. After entering the RF field the ISO 11785 data is sent when the transponder is in ISO 11785 state.

Table 41. WRITE ISO 11785 - request format (38h, 39h)

| Flags   | Command | Data 1             | CRC-16 | Description |

|---------|---------|--------------------|--------|-------------|

| 5       | 6       | 128                | (16)   | No. of bits |

| 00(1)00 | 111000  | ISO 11785 TTF data |        |             |

| 00(1)00 | 111001  | ISO 11785 TTF data |        | inc. LOCK   |

Table 42. Response to a successful WRITE ISO 11785 request

| Error flag | CRC-16 | Description |

|------------|--------|-------------|

| 1          | (16)   | No. of bits |

| 0          |        |             |

Error Flag set to '0' indicates no error.

The minimum value of  $T_{Fp1}$  is 20 ms.

### 14.12 GET SYSTEM INFORMATION

### [Advanced, Advanced+]

Upon reception of this command without error, the transponder IC reads the requested system memory block(s) and sends back their values in the response.

Table 43. GET SYSTEM INFORMATION - request format (17h)

| Flags   | Command | Data 1 | CRC-16 | Description |

|---------|---------|--------|--------|-------------|

| 5       | 6       | (48)   | (16)   | No. of bits |

| 00(1)00 | 010111  |        |        | without UID |

| 10(1)00 | 010111  | UID    |        | with UID    |

Table 44. GET SYSTEM INFORMATION - response format

| Error<br>flag | Data |                          |                    |   |   |   |   |   |   | CRC-16 | Description |

|---------------|------|--------------------------|--------------------|---|---|---|---|---|---|--------|-------------|

| 1             | 40   | 8                        | 8                  | 8 | 8 | 8 | 8 | 8 | 8 | (16)   | No. of bits |

| 0             |      | system memory block data |                    |   |   |   |   |   |   |        |             |

|               | MSN  | MFC                      | ICR <sup>(1)</sup> | 0 | 0 | 0 | 0 | 0 | 0 |        |             |

[1] ICR: Hitag  $\mu$ : 10h, Hitag  $\mu$  advanced: 20h, Hitag  $\mu$  advanced+: 30h

### 14.13 LOGIN

#### [μ, Advanced, Advanced+]

Upon reception of this command without error, the transponder IC compares received password with PWD in memory block (FEh) and if correct it permits write (opt. read) access to the protected memory area (defined in User config, see <a href="Table 8">Table 8</a>) and reports the success of the operation in the response. In case a wrong password is issued in a further login request no access to protected memory blocks will be granted.

Default password: FFFFFFFh

Table 45. LOGIN (advanced/advanced+) - request format

| Flags   | Command | IC MFC | Parameter 1 | Password | CRC-16 | Description                   |

|---------|---------|--------|-------------|----------|--------|-------------------------------|

| 5       | 6       | 8      | (48)        | 32       | (16)   | No. of bits                   |

| 00(1)00 | 101000  | MFC    | -           | password |        | without UID in READY state    |

| 10(1)00 | 101000  | MFC    | UID         | password |        | with UID in<br>READY state    |

| 01(1)00 | 101000  | MFC    | -           | password |        | without UID in SELECTED state |

### Table 46. LOGIN (μ) - request format

| Flags   | Command | IC MFC | Parameter 1 | Password | CRC-16 | Description                |

|---------|---------|--------|-------------|----------|--------|----------------------------|

| 5       | 6       | 8      | (48)        | 32       | (16)   | No. of bits                |

| 00(1)00 | 101000  | MFC    | -           | password |        | without UID in READY state |

| 10(1)00 | 101000  | MFC    | UID         | password |        | with UID in<br>READY state |

#### Table 47. Response to a successful LOGIN request

| Error flag | CRC-16 | Description |

|------------|--------|-------------|

| 1          | (16)   | No. of bits |

| 0          |        |             |

# 15. Transponder Talks First (TTF) mode

This mode of the HITAG  $\mu$  transponder enables data transmission to a RWD without sending any command. Every time the transponder IC is activated by the field it starts executing this mode.

The transponder in TTF mode sends the data stored in the EEPROM independent if the data is ISO compliant or not.

If the transponder IC is configured in TTF mode a SWITCH command or SOF sent by the RWD within the defined listening window sets the transponder into RTF mode.

# 16. Data integrity/calculation of CRC

The following explanations show the features of the HITAG  $\mu$  protocol to protect read and write access to transponders from undetected errors. The CRC is an 16-bit CRC according to ISO 11785.

# 16.1 Data transmission: RWD to HITAG μ transponder IC

Data stream transmitted by the RWD to the HITAG  $\mu$  transponder may include an optional 16-bit Cyclic Redundancy Check (CRC-16).

The data stream is first verified for data errors by the HITAG  $\mu$  transponder IC and then executed.

The generator polynomial for the CRC-16 is:

$$u^{16} + u^{12} + u^{5} + 1 = 1021h$$

The CRC pre set value is: 0000h

# 16.2 Data transmission: HITAG μ transponder IC to RWD

The HITAG  $\mu$  transponder calculates the CRC on all received bits of the request. Whether the HITAG  $\mu$  transponder IC calculated CRC is appended to the response depends on the setting of the CRCT flag.

# 17. Limiting values

### Table 48. Limiting values<sup>[1][2]</sup>

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                       | Conditions                                | Min | Max  | Unit |

|---------------------|---------------------------------|-------------------------------------------|-----|------|------|

| T <sub>stg</sub>    | storage temperature             |                                           | -55 | +125 | °C   |

| V <sub>ESD</sub>    | electrostatic discharge voltage | JEDEC JESD 22-A114-AB<br>Human Body Model | ±2  | -    | kV   |

| I <sub>i(max)</sub> | maximum input current           | IN1-IN2                                   | -   | ±20  | mA   |

| Tj                  | junction temperature            |                                           | -40 | +85  | °C   |

- [1] Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the Operating Conditions and Electrical Characteristics section of this specification is not implied.

- [2] This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions should be taken to avoid applying values greater than the rated maxima

### 18. Characteristics

Table 49. Characteristics

| Symbol            | Parameter           | Conditions      |        | Min   | Тур | Max   | Unit |

|-------------------|---------------------|-----------------|--------|-------|-----|-------|------|

| f <sub>oper</sub> | operating frequency |                 |        | 100   | 125 | 150   | kHz  |

| VI                | input voltage       | IN1-IN2         |        | 4     | 5   | 6     | V    |

| I                 | input current       | IN1-IN2         |        | -     | -   | ±10   | mA   |

| Ci                | input capacitance   | between IN1-IN2 |        |       |     |       |      |

|                   |                     | HTMS1x01        | [2][3] | 203.7 | 210 | 216.3 | pF   |

|                   |                     | HTMS8x01        | [2][4] | 266   | 280 | 294   | pF   |

- [1] Typical ratings are not guaranteed. Values are at 25  $^{\circ}$ C.

- [2] Measured with an HP4285A LCR meter at 125 kHz/room temperature (25 °C);  $V_{IN1-IN2}$  = 0.5 V (RMS)

- [3] Integrated Resonance Capacitor: 210pF ±3%

- [4] Integrated Resonance Capacitor: 280pF ±5%

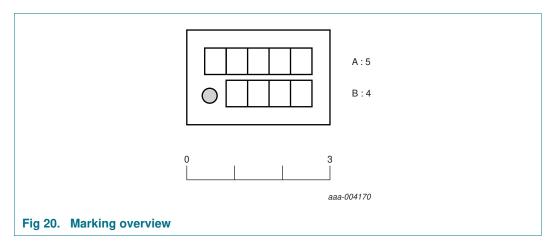

# 19. Marking

# **19.1 Marking SOT1122**

### Table 50. Marking SOT1122

| Туре           | Type code |

|----------------|-----------|

| HTMS8001FTB/AF | 80        |

| HTMS8101FTB/AF | 81        |

| HTMS8201FTB/AF | 82        |

### Table 51. Pin description SOT1122

| Pin | Description       |

|-----|-------------------|

| 1   | IN 1              |

| 2   | IN 2              |

| 3   | n.c not connected |

# 19.2 Marking HVSON2

Only two lines are available for marking (Figure 20).

First line consists on five digits and contains the diffusion lot number. Second line consists on four digits and describes the product type, HTMS8001FTK, HTMS8101FTK or HTMS8201FTK (see example in Table 52).

Table 52. Marking example

| Line | Marking | Description                                            |

|------|---------|--------------------------------------------------------|

| Α    | 70960   | 5 digits, Diffusion Lot Number, First letter truncated |

| В    | HM80    | 4 digits, Type: Table 53 "Marking HVSON2"              |

Table 53. Marking HVSON2

| Туре           | Type code |

|----------------|-----------|

| HTMS8001FTK/AF | HM80      |

| HTMS8101FTK/AF | HM81      |

| HTMS8201FTK/AF | HM82      |

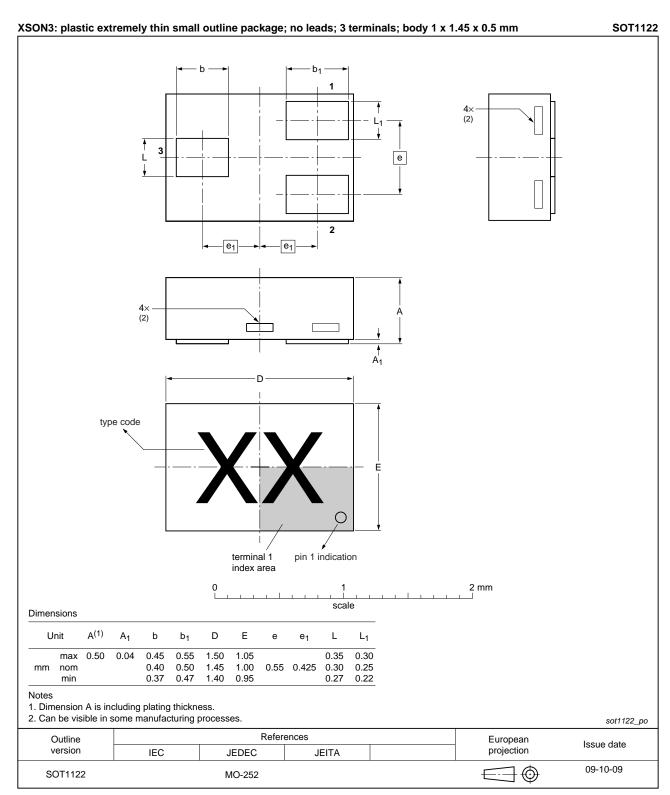

# 20. Package outline

Fig 21. Package outline SOT1122

HTMS1x01\_8x01

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2015. All rights reserved.

Fig 22. Package outline HVSON2

# 21. Abbreviations

Table 54. Abbreviations

| Abbreviation | Definition                                          |

|--------------|-----------------------------------------------------|

| AC           | Anticollision Code                                  |

| ASK          | Amplitude Shift Keying                              |

| BC           | Bi-phase Code                                       |

| BPLC         | Binary Pulse Length Coding                          |

| CRC          | Cyclic Redundancy Check                             |

| DSFID        | Data Storage Format Identifier                      |

| EEPROM       | Electrically Erasable Programmable Read-Only Memory |

| EOF          | End Of Frame                                        |

| IC           | Integrated Circuit                                  |

| ICR          | Integrated Circuit Reference number                 |

| LSB          | Least Significant Bit                               |

| LSByte       | Least Significant Byte                              |

| m            | Modulation Index                                    |

| MC           | Manchester Code                                     |

| MFC          | integrated circuit Manufacturer Code                |

| MSB          | Most Significant Bit                                |

| MSByte       | Most Significant Byte                               |

| MSN          | Manufacturer Serial Number                          |

| NA           | No Access                                           |

| NOB          | Number Of Block                                     |

| NOP          | Number Of Pages                                     |

| NOS          | Number Of Slots                                     |

| NSS          | Number Of Sensors                                   |