#

# Wireless Infrastructure Solutions to Enhance the Digital Media Experience IDT ADDRESSES NEXT GENERATION WIRELESS BY ACCELERATING THE DATA PATH AND OFFLOADING FUNDAMENTAL PROCESSING TASKS

The consumer of wireless communication devices demands higher performance to gain faster access to their desired digital media content, while expecting error-free accuracy at ever-decreasing price points. To achieve success in the marketplace, today's system designer must balance the demand for increased performance with continued focus on reliability, predictability and quality of service as well as reducing power and lowering product costs.

#### **FEATURED PRODUCTS**

Serial RapidIO<sup>®</sup> switches Functional InterConnect (FIC) devices Serial buffers SAW filters Timing solutions Digital logic The highly competitive nature of the wireless communications field makes time-to-market and evolving industry standards critical components of a successful design.

System designers need a partner who works to identify, understand and resolve system bottlenecks one-by-one and throughout the whole system. IDT helps designers gain a significant edge by applying our years of experience in innovative, low-power, mixed signal integrated circuit design to optimize the performance of Serial RapidIO<sup>®</sup> (S-RIO) switches, serial buffers, Functional InterConnects, SAW filters, timing solutions and digital logic system components in wireless applications.

Because IDT technology can perform fundamental core tasks such as offloading packet-and byte-level data manipulation functions, FPGAs, ASICs and ASPs become increasingly more efficient. IDT pre-processing switches and central packet switches, based on Serial RapidIO technology, efficiently process the quality of service (QoS), prioritization and multicasting tasks that have historically slowed down (and heated up) processors. This allows the processor to concentrate on what it does best: process higher-level content. Add our wide array of timing solutions, filter devices and advanced digital logic elements and today's system designer has an unparalleled set of choices from one company they can rely on to deliver higher performance systems to market more rapidly, using less power while reducing system costs.

## Serial RapidIO<sup>®</sup> switches

Serial RapidIO interconnect switches have become the standard in communication systems, but there are a number of considerations which govern the particular type of switch appropriate to each system design. Optimized for wireless baseband processing applications, the IDT pre-processing switch (PPS) is an advanced semiconductor solution which complements its high performance Serial RapidIO switching by integrating an innovative suite of byte-and packet-level manipulation capabilities designed to offload specific bandwidth-intensive tasks from the DSP.

IDT currently offers several Serial RapidIO switches for baseband applications: PPS, PPS Gen 2, central packet switch (CPS) and the recently introduced CPS-10/6Q, so the designer can pick the combination of port count, performance and functionality most pertinent to their system design.

|                                         | PPS devices                   |                              | CPS devices               |                           |                           |                            |                           |

|-----------------------------------------|-------------------------------|------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|---------------------------|

| Device                                  | PPS<br>70K2000                | PPS Gen 2<br>80KSW0001       | CPS-16<br>80KSW0002       | CPS-12<br>80KSW0004       | CPS-8<br>80KSW0003        | CPS-10Q<br>80KSW0005       | CPS-6Q<br>80KSW0006       |

| Ports                                   | 22 1x ports                   | 12 1x ports                  | 16 1x ports               | 12 1x ports               | 8 1x ports                | 16 1x ports                | 16 1x ports               |

|                                         | 10 4x ports<br>Mix of both    | 3 4x ports<br>Mix of both    | 4 4x ports<br>Mix of both | 3 4x ports<br>Mix of both | 2 4x ports<br>Mix of both | 10 4x ports<br>Mix of both | 6 4x ports<br>Mix of both |

| Package                                 |                               |                              |                           |                           |                           |                            |                           |

| 27 x 27 mm, 676 pin                     | $\checkmark$                  | √                            |                           |                           |                           | $\checkmark$               | $\checkmark$              |

| 19 x 19 mm, 324 pin                     |                               | $\checkmark$                 | √                         | $\checkmark$              | $\checkmark$              |                            |                           |

| Features                                |                               |                              |                           |                           |                           |                            |                           |

| Store and forward                       | $\checkmark$                  | √                            | √                         | √                         |                           | $\checkmark$               | √                         |

| Cut through                             |                               |                              | √                         | √                         |                           | $\checkmark$               | √                         |

| Multicast                               | $\checkmark$                  | √                            | √                         | √                         |                           | $\checkmark$               | √                         |

| Non-blocking within each S-RIO priority | √                             | √                            | √                         | √                         | √                         | $\checkmark$               | √                         |

| No. of pre-processing scenarios         | 10                            | 4                            |                           |                           |                           |                            |                           |

| Error Handling                          | $\checkmark$                  | √                            | √                         | √                         |                           | $\checkmark$               | $\checkmark$              |

| Packet Trace/Mirror                     |                               | $\checkmark$                 | V                         | √                         | $\checkmark$              | $\checkmark$               | $\checkmark$              |

| Packet Filter/Kill                      |                               | √                            | √                         | √                         | √                         | $\checkmark$               | √                         |

| SerDes BIST                             | V                             | √                            | V                         | V                         | $\checkmark$              | $\checkmark$               | V                         |

| Aggregate Peak Throughput               | 100 G pre-<br>processing      | 30 G pre-<br>processing      | 40 G                      | 30 G                      | 20 G                      | 100 G                      | 60 G                      |

|                                         | 10 G switch                   | 30 G switch                  |                           |                           |                           |                            |                           |

|                                         | 100 G combined (port limited) | 30 G combined (port limited) |                           |                           |                           |                            |                           |

#### Serial RapidIO Switch Comparison Matrix

| Serial RapidIO benefits                                    | Features                                                                                                    |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| IDT has just the part you need                             | PPS, CPS or CPS-10/6Q                                                                                       |

| Port speed, width and reach can be individually configured | Up to 22 1x or 10 4x ports with 3.125 Gbps performance                                                      |

| PPS frees the DSP to run differentiating algorithms        | Performs end-point functions (e.g., lower level data operations)                                            |

| Enhances DSP and other end point connectivity              | Optimally distributes data to multiple DSPs during Serial RapidIO switch interface                          |

| Eases system design implementation                         | Off-the-shelf components supports base station system bring-up and debug;<br>CPS is pin-compatible with PPS |

| Diverse design implementations are possible                | Scalable to address wide range of wireless and non-wireless applications                                    |

| Minimizes FPGA and ASIC costs                              | Standard component with Serial RapidIO connectivity                                                         |

| Eases and speeds design-in                                 | Dedicated hardware/software development platform                                                            |

For additional information about IDT Serial RapidIO products and parts, visit <a href="https://www.IDT.com/go/SRIO">www.IDT.com/go/SRIO</a>.

## Functional InterConnect (FIC) devices

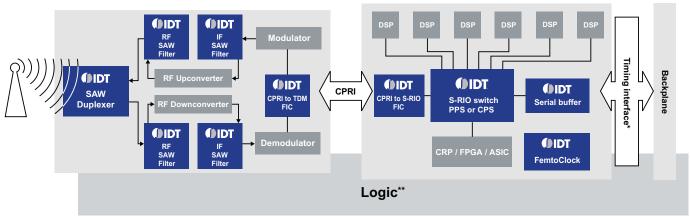

As new high-performance interfaces are adopted in Wireless Infrastructure applications, such as Serial RapidIO and CPRI<sup>™</sup> (Common Public Radio Interface), there is a requirement for cost-effective, off-the-shelf solutions that provide translation between these interfaces and legacy or less expensive ASICs and FPGAs. IDT meets this need with their family of Functional InterConnect (FIC) devices that offer low-cost connectivity between Serial RapidIO, CPRI, TDM (Time Division Multiplexor) and standard parallel interfaces.

IDT FIC devices provide full-functional translation between the interfaces, eliminating the need for designers to implement this functionality in an ASIC or FPGA. Utilizing FIC off-the-shelf components allows the designer to use valuable programmable logic resources on the high-value processing tasks that will differentiate his product in the marketplace. This also reduces design time and risk, saving development expenses and improving overall time-to-market, as well as minimizing system cost by off-loading the ASIC or FPGA of logic gate or serial transceiver requirements that can drive up their cost.

The block diagram in Figure 1 demonstrates how the IDT CPRI-FIC devices provide the connection between the RF card and the baseband processing system in the wireless base station. Translation options supported by the FIC devices include CPRI-to-Serial RapidIO, CPRI-to-TDM and Serial RapidIO-to-Parallel Interface.

| FIC benefits                             | Features                                                                                                                                 |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Reduces design time                      | Standards based interfaces (Serial RapidIO rev 1.3, CPRI v2.1, QDRII) are used to seamlessly<br>connect to other components to save time |

| Dramatically reduces FPGA and ASIC costs | Elimination of transceivers and extra logic provides up to 90 percent cost savings in FPGA expense                                       |

| Eases system design complexity and risk  | Proven, off-the-shelf components for shorter time-to-market                                                                              |

| Simplifies overall design architecture   | Pre-processing capabilities of PPS can be combined with FIC devices to do all translation and<br>initial sample processing               |

| Provides system flexibility              | Data translation and formatting options available for sample manipulation                                                                |

| Complete system solution                 | When combined with the PPS and Serial Buffer, the FIC devices form the complete core solution for<br>baseband processing applications    |

For additional information about FIC products and parts from IDT, visit www.IDT.com/go/wireless.

#### Figure 1: Typical Wireless Infrastructure Block Diagram

\* IDT has the industry's widest array of timing devices. Visit <u>www.IDT.com/go/timing</u> for more information.

\*\* For additional information about IDT digital logic products and parts, visit www.IDT.com/go/logic.

## **Serial buffers**

With tech-savvy consumers now demanding high value-added services such as mobile video at attractive price points, designers understand that wireless networks for 3G (third generation) and beyond require higher performance and lower cost base station systems. To satisfy the demands of both service providers and consumers, low-cost, high-throughput implementations are needed.

The high-throughput environments of 3G wireless base stations, for example, rely on multiple digital signal processors (DSPs) to deliver value-added services, which require high speed and large amounts of memory to execute consecutive sample-compare functions.

The IDT 10 G serial buffer, when coupled with the IDT pre-processing switch (PPS) and FICs, forms a chipset solution for wireless base station applications (see figure 1). The combination provides customers with a complete processing and storage solution enabling scalable, flexible and cost-effective systems. According to base station designers, the combination of the 10 G serial buffer and the PPS not only reduces DSP loading by up to 20 percent, but also slashes bill of material (BOM) cost by 50 to 75 percent, as compared to alternative solutions.

The 10 G serial buffer is a recent offering in the IDT ongoing commitment to provide leading-edge wireless baseband solutions. In addition to cellular base stations, IDT Serial RapidIO solutions provide excellent support for other DSP-intensive applications, such as medical imaging and high-speed communications applications, as well as radar, data-acquisition and sampling.

| Serial buffer benefits                                                                                     | Features                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Dramatically improve performance                                                                           | Eliminates local memory bottlenecks                                                                                                        |

| Reduces silicon area (board space)                                                                         | Eliminates or reduces the need for local memory entirely                                                                                   |

| Significantly simplifies design                                                                            | Eliminates complex memory management schemes                                                                                               |

| Dramatically reduces the BOM (bill of materials)                                                           | Only 16 I/Os are needed, compared to alternative approaches requiring 100 I/Os                                                             |

| Maintains data synchronicity                                                                               | Contains intelligent monitoring and control circuitry which automatically identifies and compensates<br>for dropped data packets           |

| Provides a complete processing and storage solution enabling scalable, flexible and cost-effective systems | 10 G serial buffer solves the sample-compare problem—and the PPS solves the throughput-intensive<br>data processing and switching problems |

| Reduces DSP loading by up to 20% and slashes BOM by 50 to 75%, as compared to alternative solutions        | Combined chipset solution of 10 G serial buffer and PPS                                                                                    |

For additional information about IDT serial buffer products and parts, visit www.IDT.com/go/serialbuffer.

#### Functional InterConnect (FIC) and Serial Buffer Matrix

|             | FIC devices                            |                                                                                             |                                                          | Serial buffer devices                                                      |

|-------------|----------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------|

| Device      | FIC 80HFC1000                          | FIC 80HFC1001                                                                               | FIC 80KFC1002                                            | Serial buffer 80KSBR201                                                    |

| Ports       | 3 CPRI                                 | 3 CPRI                                                                                      | 1 S-RIO (1x or 4x)                                       | 2 S-RIO (1x or 4x)                                                         |

|             | 1 S-RIO (1x or 4x)                     | 2 TDM (16 bit ports)                                                                        | 1 Parallel<br>(QDRII burst of 2)                         | 1 Parallel<br>(QDRII burst of 2)                                           |

| Package     | 19 x 19 mm, 324 pin                    | 19 x 19 mm, 324 pin                                                                         | 23 x 23 mm, 484 pin                                      | 23 x 23 mm, 484 pin                                                        |

| Features    | CPRI v2.1 compliant                    | CPRI v2.1 compliant                                                                         | S-RIO 1.3 compliant                                      | S-RIO 1.3 compliant                                                        |

|             | CPRI Master mode                       | Each CPRI port configurable as<br>Master or Slave to support chain<br>configurations        | Parallel port for external processor,<br>FPGA, or memory | 18 Mbits on-chip memory,<br>expandable to 90 Mbits with<br>external memory |

|             | S-RIO 1.3 compliant                    | TDM interfaces support dual<br>channel configurations                                       | 10 Gbps throughput                                       | 10 Gbps throughput                                                         |

|             | Programmable mapping                   | TDM control pins provided for<br>seamless connection to popular<br>ADC/DAC, DUC/DDC devices | Status flags and water marks                             | Status flags and water marks                                               |

|             | Supports S-RIO maintenance operations  | Multiplexing mode options                                                                   |                                                          | Configurable queue sizes                                                   |

| Performance | CPRI:<br>614.4 / 1228.8 / 2457.6 Mbaud | CPRI:<br>614.4 / 1228.8 / 2457.6 Mbaud                                                      | S-RIO ports:<br>1.25 / 2.5 / 3.125 Gbaud                 | S-RIO ports:<br>1.25 / 2.5 / 3.125 Gbaud                                   |

|             | S-RIO:<br>1.25 / 2.5 / 3.125 Gbaud     | TDM:<br>up to 150 MHz per port                                                              | Parallel:<br>64-bits up to 200 MHz per port              | Parallel:<br>64-bits up to 200 MHz per port                                |

IDT® WIRELESS INFRASTRUCTURE SOLUTIONS

### **SAW filters**

Today's crowded radio frequency spectrum from baseband through 3 GHz requires system designers to meet stringent regulatory requirements without sacrificing performance. Filter requirements demand high selectivity, low insertion loss, flat passbands, and uniform group delay to meet performance criteria. In addition, these filters must be highly repeatable, small size, low cost, and operate in adverse environmental conditions. Surface acoustic wave (SAW) filters are a perfect match to such requirements.

There are a multitude of commercial applications of SAW filters. They include, but are not limited to, telecommunications (base station and handheld), WiMAX, set top box and cable modems, navigation (GIS/GPS), automotive, and medical. There are also space and military applications, including functions from simple time delay to dispersive devices for complex matched filtering applications.

Early CDMA (code division multiple access) filters were very high-performance devices, demanding high selectivity and out-of-band rejection as well as very low phase and amplitude ripple. These requirements resulted in large filters having insertion losses between 20 dB and 25 dB. The costly filters were packaged in large through-hole metal packages up to 3 inches in length.

As base station design progressed, the selectivity and out-of-band requirements placed on the SAW filters were relaxed. Lowering insertion loss and size of the filters, and therefore cost, became the driving forces in filter design. IDT developed "low loss" filter design capability to meet the needs of the 3G (third generation) IF base station market.

IDT SAW filters have been used as IF (intermediate frequency) filters in wireless base stations for many years. Today, IDT designs and manufactures SAW filters utilizing advanced state-of-the-art semiconductor manufacturing techniques to meet the demanding criteria expected by their customers. SAW filters can easily be integrated by the RF designer as part of the front-end solution to provide duplex operation, RF filtering, and IF filtering after down conversion, or can be combined in a single hybrid module with the appropriate amplifiers and mixers to provide a complete front-end solution. (See figure 1.)

A SAW filter design may be geared to any number of applications, such as:

- · Bandpass filters for high-volume commercial applications

- · Duplexers to meet stringent operational and regulatory requirements, or

- More complex silicon on ceramic (SOC) hybrids, combining SAW filters with various other devices in a single hybrid package to meet specific requirements and functionality

A number of IDT SAW filters meet the requirements for 3G infrastructure protocols. With so many SAW filters available from IDT, and each with custom capabilities, IDT can provide the proper solution to meet customer requirements.

| SAW filter benefits                                                                  | Features                                                                               |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Meets the needs of the 3G IF base station market                                     | "Low loss" filter design capability, highly reliable, low cost, excellent shape factor |

| Used in high volume commercial applications                                          | Bandpass filters                                                                       |

| Meets the needs of the 3G IF base station market                                     | Very low passband distortion                                                           |

| Families of filters of various bandwidths will meet most 3G infrastructure protocols | Center frequencies from 70 MHz to 350 MHz are available                                |

| Easier implementation in a single hybrid package                                     | More complex SOC hybrids combining SAW filters with other devices                      |

| Families of filters of various bandwidths will meet most 3G infrastructure protocols | RF SAW filters operate in the 800–900 MHz and 1800–1900 MHz bands                      |

For additional information about IDT SAW filter products and parts, visit www.IDT.com/go/SAWfilters.

| Examples of wireless output clock frequencies supported by IDT integrated clock synthesizers |

|----------------------------------------------------------------------------------------------|

| 15.36 MHz                                                                                    |

| 30.72 MHz                                                                                    |

| 122.88 MHz                                                                                   |

| 153.6 MHz                                                                                    |

| 156.25 MHz                                                                                   |

| 491.52 MHz                                                                                   |

| 614.4 MHz                                                                                    |

## **Timing solutions**

A low phase noise clock design is critical in order to minimize serial link bit error rate and DAC/ADC (digital to analog / analog to digital converters) errors for wireless infrastructure equipment. IDT offers a family of integrated circuits designed to generate and distribute the clock frequency for synchronous components in wireless infrastructure systems, such as SerDes, ADC/DAC circuits, local oscillators, DSPs and control processors. Optimized for low phase noise, the IDT FemtoClock<sup>®</sup> clock synthesizers and jitter attenuation devices are flexible solutions that support high level integration, while replacing the more traditional (and more expensive) VCXO circuits.

In contrast to competitive solutions, the IDT FemtoClock devices integrate the clock oscillator and offer configuration flexibility. As seen in the wireless output frequencies table, even more integrated solutions have the capability to generate several output frequencies and include fan-out buffers, reducing the component count for more effective board designs.

Wireless infrastructure applications with digitally synthesized or recovered clock signals require jitter attenuation to meet the low phase jitter requirements of the Serial RapidIO transceivers or ADC/DAC devices. Traditionally this was achieved by expensive VCXO circuits. The family of IDT jitter-attenuation and frequency generation devices based on the IDT FemtoClock technology offers a more effective and higher integrated solution, and consists of several devices, such as ICS813076i, ICS814075i, ICS813076i-02, ICS813076i-30 and ICS813076i-31. These devices support the common reference clock frequencies of 2G, 3G (RP3, CPRI) and LTE systems.

The IDT WAN-PLL family supports wireless applications with demanding clock synchronization needs. WAN-PLL devices are optimized single-chip solutions for synchronization between time division multiplexer (TDM), synchronous optical network/ synchronous digital hierarchy (SONET/SDH) and common baseband system frequencies and can function as effective frequency translators. The WAN-PLL devices offer Stratum-compliance, holdover and master/slave support.

| Timing solutions benefits                                | Features                                                                   |

|----------------------------------------------------------|----------------------------------------------------------------------------|

| Efficiency: IDT is your one-stop clock shop              | Large portfolio of optimized timing solutions                              |

| Easy to use, standard compliant, frequency translators   | Family of WAN-PLL devices optimized for system synchronization             |

| Reduce jitter design problems                            | Dedicated jitter attenuation solutions for baseband and RF                 |

| Support a high integration level                         | Low-phase noise reference clock solutions for low bit-error rates designs  |

| Reduces component count for more effective board designs | More integrated solutions capable of generating several output frequencies |

| More flexible clock solutions than oscillators           | Higher integration level                                                   |

For additional information about IDT timing products and parts, visit www.IDT.com/go/timing.

## **Digital logic**

The IDT high-performance, low-voltage standard logic ICs and bus switch logic ICs are key to high-speed computing and communications systems, including wireless base stations. The advanced portfolio offered by IDT of advanced low-voltage CMOS (ALVC/ALVCH), low-voltage CMOS (LVC/LVCH), and fast CMOS TTL-compatible (FCT) digital logic families allows designers to reduce power consumption, increase data throughput and shrink form factors—while providing needed functions and speeds in cost-effective space-saving packages.

For additional information about IDT digital logic products and parts, visit www.IDT.com/go/logic.

## Conclusion

IDT wireless infrastructure solutions are an integral part of the worldwide communications network. From core routers enabling the network upon which the Internet operates to base stations and mobile devices that allow wireless communications, IDT devices enable a faster, more powerful digital media experience.

For more detailed information about how IDT can help you solve your wireless infrastructure solutions needs, technical documentation, press releases, as well as comprehensive information on the wide variety of related parts that IDT offers, please visit <u>www.IDT.com/go/wireless</u>.

You can also receive IDT product-related newsletters and updates and find local distributors by registering at my.IDT.com. Select the myIDT menu on the upper right tab of the www.IDT.com web page, and select "Register for myIDT" or go directly to <a href="https://www.IDT.com/go/register">www.IDT.com/go/register</a>.

## Applications **Associated product lines**

| Enterprise                | <ul> <li>Clocks/Timing</li> <li>FIFO products</li> <li>Multi-Port memories</li> <li>PCI Express<sup>®</sup> switches</li> </ul> | <ul> <li>Search engines &amp; Accelerator</li> <li>Serial RapidIO<sup>®</sup> solutions</li> <li>Telecommunication ICs</li> </ul> |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Telecom                   | <ul> <li>Clocks/Timing</li> <li>FIFO products</li> <li>Multi-Port memories</li> <li>Physical layer devices</li> </ul>           | <ul> <li>Search engines &amp; Accelerator</li> <li>SRAMs</li> <li>Telecommunication ICs</li> </ul>                                |

| Wireless<br>Base Stations | <ul> <li>Clocks/Timing</li> <li>FIFO products</li> <li>Multi-Port memories</li> </ul>                                           | <ul> <li>SAW filters</li> <li>Serial RapidIO<sup>®</sup> solutions</li> <li>Telecommunication ICs</li> </ul>                      |

| Computing |                                                                 | _                                                                                |

|-----------|-----------------------------------------------------------------|----------------------------------------------------------------------------------|

| Desktops  | <ul><li>Advanced Memory Buffers</li><li>Clocks/Timing</li></ul> | <ul> <li>PC Audio solutions</li> <li>PCI Express<sup>®</sup> switches</li> </ul> |

| Embedded  | <ul><li>Clocks/Timing</li><li>Multi-Port memories</li></ul>     | <ul> <li>PC Audio solutions</li> <li>PCI Express<sup>®</sup> switches</li> </ul> |

| Notebooks | <ul><li>Clocks/Timing</li><li>PC Audio solutions</li></ul>      | Video interfaces                                                                 |

| Servers   | <ul><li>Advanced Memory Buffers</li><li>Clocks/Timing</li></ul> | PCI Express <sup>®</sup> switches                                                |

| Consumer    |                                                       |                     |

|-------------|-------------------------------------------------------|---------------------|

| Digital TV  | Clocks/Timing                                         | Video interfaces    |

| Gaming      | Clocks/Timing                                         | PC Audio solutions  |

| Handsets    | <ul><li>Clocks/Timing</li><li>FIFO products</li></ul> | Multi-Port memories |

| Set Top Box | Clocks/Timing                                         |                     |

## Discover what IDT know-how can do for you.

# www.IDT.com/go/wireless

© 2008 Integrated Device Technology, Inc. All rights reserved. Product specifications are subject to change without notice. IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA 10-08/MG/BWD/HOP/500