### Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

November 2012

# FL6300A Quasi-Resonant Current Mode PWM Controller for Lighting

#### **Features**

- High-Voltage Startup

- Quasi-Resonant Operation

- Cycle-by-Cycle Current Limiting

- Peak-Current-Mode Control

- Leading-Edge Blanking (LEB)

- Internal Minimum t<sub>OFF</sub>

- Internal 5 ms Soft-Start

- Over-Power Compensation

- GATE Output Maximum Voltage

- Auto-Recovery Over-Current Protection (FB Pin)

- Auto-Recovery Open-Loop Protection (FB Pin)

- Latch Protection V<sub>DD</sub> Pin and Output Voltage (DET Pin) OVP

- Frequency Operation Below 100 kHz

# **Applications**

- General LED Lighting

- Industrial, Commercial, and Residential Fixtures

- Outdoor Lighting: Street, Roadway, Parking, Construction, and Ornamental LED Lighting Fixtures

## **Description**

The FL6300A lighting power controller includes a highly integrated PWM controller and provides several features to enhance the performance of flyback converters in medium- to high-power lumens applications.

The FL6300A is applied on quasi-resonant flyback converters, where maximum operating frequency is limited to below 100 kHz. A built-in HV startup circuit can provide more startup current to reduce the startup time of the controller. Once the V<sub>DD</sub> voltage exceeds the turn-on threshold voltage, the HV startup function is disabled to reduce power consumption. An internal valley voltage detector ensures that the power system operates at quasi-resonant operation over a wide-range of line voltage and load conditions, as well as reducing switching loss to minimize switching voltage on the drain of the power MOSFET.

To minimize standby power consumption and improve light-load efficiency, a proprietary Green-Mode function provides off-time modulation to decrease switching frequency and perform extended valley voltage switching to keep to a minimum switching pulse. The operating frequency is limited by minimum  $t_{\text{OFF}}$  time, which is 38  $\mu s$  to 8  $\mu s$ .

FL6300A also provides many protection functions. Pulse-by-pulse current limiting ensures the fixed-peak current-limit level, even when a short circuit occurs. Once an open-circuit failure occurs in the feedback loop, the internal protection circuit disables PWM output immediately. When  $V_{\rm DD}$  drops below the turn-off threshold voltage, the controller disables PWM output. The gate output is clamped at 18 V to protect the power MOSFET from high gate-source voltage conditions. The minimum  $t_{\rm OFF}$  time limit prevents the system frequency from being too high. When over-voltage protection (OVP) is triggered by DET or when internal over-temperature protection (OTP) is triggered, the power system enters Latch Mode until AC power is removed.

# **Ordering Information**

| Part Number Operating Temperature Range |                           | . • | Package                             | Packing Method |  |

|-----------------------------------------|---------------------------|-----|-------------------------------------|----------------|--|

|                                         | FL6300AMY -40°C to +125°C |     | 8-Lead, Small Outline Package (SOP) | Tape & Reel    |  |

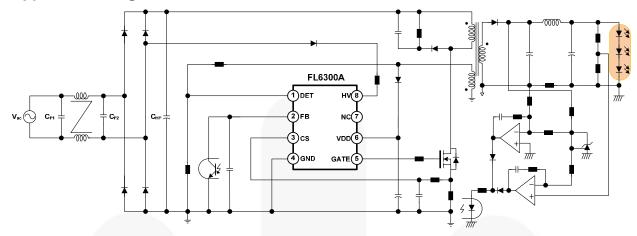

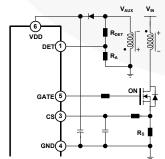

# **Application Diagram**

Figure 1. Typical Application Circuit for Flyback Converter

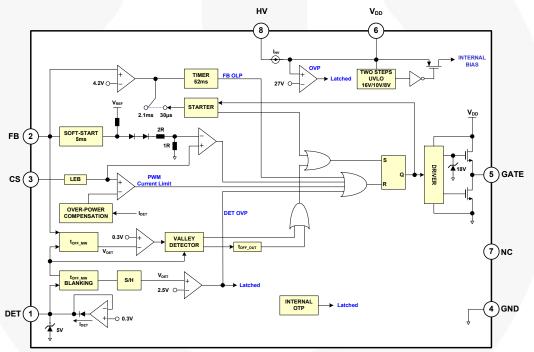

# **Internal Block Diagram**

Figure 2. Functional Block Diagram

# **Marking Information**

- **f**: Fairchild Logo

- Z: Plant Code

- X: Year Code

- Y: Week Code

- TT: Die Run Code

- T: Package Type (M = SOP)

- P: Y = Green Package

- M: Manufacture Flow Code

Figure 3. Marking Diagram

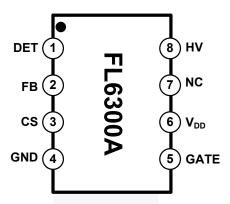

# **Pin Configuration**

Figure 4. Pin Assignments

# **Pin Definitions**

| Pin# | Name                                                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | DET                                                                                                                                                                                                                                     | <ul> <li>This pin is connected to an auxiliary winding of the transformer via resistors of the divider for the following purposes:</li> <li>Generates a zero-current detection (ZCD) signal once the secondary-side switching current falls to zero.</li> <li>Produces an offset voltage to compensate the threshold voltage of the peak current limit to provide a constant power limit. The offset is generated in accordance with the input voltage when PWM signal is enabled.</li> <li>Detects the valley voltage of the switching waveform to achieve the valley voltage switching and minimize the switching losses.</li> <li>A voltage comparator and a 2.5 V reference voltage develop an output OVP protection. The ratio of the divider determines what output voltage to stop gate, as an optical coupler and secondary shunt regulator are used.</li> </ul> |  |  |

| 2    | FB                                                                                                                                                                                                                                      | The feedback pin should to be connected to the output of the error amplifier for achieving the voltage control loop. The FB pin should be connected to the output of the optical coupler if the error amplifier is equipped at the secondary-side of the power converter. For primary-side control applications, FB is applied to connect a RC network to the ground for feedback-loop compensation. The input impedance of this pin is a 5 k $\Omega$ equivalent resistance. A one-third (1/3) attenuator connected between the FB and the PWM circuit is used for the loop-gain attenuation. FL6300A performs an open-loop protection (OLP) once the FB voltage is higher than a threshold voltage (around 4.2 V) for more than 55ms.                                                                                                                                  |  |  |

| 3    | CS                                                                                                                                                                                                                                      | Input to the comparator of the over-current protection. A resistor senses the switching current and the resulting voltage is applied to this pin for the cycle-by-cycle current limit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 4    | 4 GND The power ground and signal ground. A 0.1 μF decoupling capacitor placed between GND is recommended.  5 GATE Totem-pole output generates the PWM signal to drive the external power MOSFET. Totamped gate output voltage is 18 V. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 5    |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 6    | $V_{\text{DD}}$                                                                                                                                                                                                                         | Power supply. The threshold voltages for startup and turn-off are 16 V and 10 V, respectively. The startup current is less than 20 µA and the operating current is lower than 4.5 mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 7    | NC                                                                                                                                                                                                                                      | No connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 8    | HV                                                                                                                                                                                                                                      | High-voltage startup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol                                                 | Parameter                                            | Min. | Max. | Unit |

|--------------------------------------------------------|------------------------------------------------------|------|------|------|

| $V_{VDD}$                                              | DC Supply Voltage                                    |      | 30   | V    |

| $V_{HV}$                                               | HV                                                   |      | 500  | V    |

| V <sub>H</sub>                                         | GATE                                                 | -0.3 | 25.0 | V    |

| V <sub>L</sub>                                         | V <sub>FB</sub> , V <sub>CS</sub> , V <sub>DET</sub> | -0.3 | 7.0  | V    |

| P <sub>D</sub>                                         | Power Dissipation                                    |      | 400  | mW   |

| TJ                                                     | Operating Junction Temperature                       |      | +150 | °C   |

| T <sub>STG</sub>                                       | Storage Temperature Range                            | -55  | +150 | °C   |

| T <sub>L</sub> Lead Temperature (Soldering 10 Seconds) |                                                      |      | +270 | °C   |

| ESD                                                    | Human Body Model, JEDEC:JESD22-A114                  |      | 3.0  | KV   |

| ESD                                                    | Charged Device Model, JEDEC:JESD22-C101              |      | 1.5  | r\ V |

#### Notes:

- 1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

- 2. All voltage values, except differential voltages, are given with respect to GND pin.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol | Parameter                     | Min. | Max. | Unit |

|--------|-------------------------------|------|------|------|

| $T_A$  | Operating Ambient Temperature | -40  | +125 | °C   |

## **Electrical Characteristics**

Unless otherwise specified,  $V_{DD}$ =10~25 V,  $T_A$ =-40°C~125°C ( $T_A$ = $T_J$ ).

| Symbol                                                             | Parameter                                           | Conditions                                                             | Min.   | Тур.   | Max.   | Unit |

|--------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------|--------|--------|--------|------|

| V <sub>DD</sub> Section                                            |                                                     |                                                                        | •      | •      |        |      |

| V <sub>OP</sub>                                                    | Continuously Operating Voltage                      |                                                                        |        |        | 25     | V    |

| $V_{\text{DD-ON}}$                                                 | Turn-On Threshold Voltage                           |                                                                        | 15     | 16     | 17     | V    |

| V <sub>DD-PWM-OFF</sub>                                            | PWM Off Threshold Voltage                           |                                                                        | 9      | 10     | 11     | V    |

| $V_{DD-OFF}$                                                       | Turn-Off Threshold Voltage                          |                                                                        | 7      | 8      | 9      | V    |

| I <sub>DD-ST</sub>                                                 | Startup Current                                     | V <sub>DD</sub> =V <sub>DD-ON</sub> -0.16 V<br>GATE Open               |        | 10     | 20     | μA   |

| I <sub>DD-OP</sub>                                                 | Operating Current                                   | $V_{DD}$ =15 V, $f_S$ =60 kHz, $C_L$ =2 nF                             |        | 4.5    | 5.5    | mA   |

| I <sub>DD-GREEN</sub>                                              | Green-Mode Operating Supply Current (Average)       | $V_{DD}$ =15 V, $f_S$ =2 kHz, $C_L$ =2 nF                              |        |        | 3.5    | mA   |

| I <sub>DD-PWM-OFF</sub>                                            | Operating Current at PWM-Off Phase                  | V <sub>DD</sub> =V <sub>DD-PWM-OFF</sub> -0.5 V                        | 70     | 80     | 90     | μA   |

| $V_{DD\text{-}OVP}$                                                | V <sub>DD</sub> Over-Voltage Protection (Latch-Off) |                                                                        | 26     | 27     | 28     | V    |

| t <sub>VDD-OVP</sub>                                               | V <sub>DD</sub> OVP Debounce Time                   |                                                                        | 100    | 150    | 200    | μs   |

| I <sub>DD-LATCH</sub> V <sub>DD</sub> OVP Latch-Up Holding Current |                                                     | V <sub>DD</sub> =5 V                                                   |        | 42     |        | μA   |

| HV Startup C                                                       | Current Source Section                              |                                                                        |        |        |        |      |

| $V_{HV-MIN}$                                                       | Minimum Startup Voltage on Pin HV                   |                                                                        |        |        | 50     | V    |

| $I_{HV}$                                                           | Supply Current Drawn from Pin HV                    | V <sub>AC</sub> =90 V (V <sub>DC</sub> =120 V)<br>V <sub>DD</sub> =0 V | 1.5    |        | 4.0    | mA   |

| I <sub>HV-LC</sub>                                                 | Leakage Current After Startup                       | HV=500 V,<br>V <sub>DD</sub> =V <sub>DD-OFF</sub> +1 V                 |        | 1      | 20     | μΑ   |

| Feedback In                                                        | put Section                                         |                                                                        |        |        |        |      |

| Av                                                                 | Input-Voltage to Current Sense Attenuation          | $A_V = \Delta V_{CS} / \Delta V_{FB},$ $0 < V_{CS} < 0.9$              | 1/2.75 | 1/3.00 | 1/3.25 | V/V  |

| Z <sub>FB</sub>                                                    | Input Impedance                                     |                                                                        | 3      | 5      | 7      | ΚΩ   |

| I <sub>OZ</sub>                                                    | Bias Current                                        | FB=V <sub>OZ</sub>                                                     |        | 1.2    | 2.0    | mA   |

| V <sub>OZ</sub>                                                    | Zero Duty Cycle Input Voltage                       |                                                                        | 0.8    | 1.0    | 1.2    | V    |

| $V_{FB\text{-}OLP}$                                                | Open-Loop Protection Threshold Voltage              |                                                                        | 3.9    | 4.2    | 4.5    | V    |

| t <sub>D-OLP</sub>                                                 | Debounce Time for Open-Loop/Overload Protection     |                                                                        | 46     | 52     | 62     | ms   |

| t <sub>ss</sub>                                                    | Internal Soft-Start Time                            |                                                                        |        | 5      |        | ms   |

Continued on the following page...

# **Electrical Characteristics** (Continued)

Unless otherwise specified,  $V_{DD}$ =10~25 V,  $T_A$ =-40°C ~125°C ( $T_A$ = $T_J$ ).

| Symbol                    | Parameter                                                                | Conditions                                       | Min. | Тур. | Max. | Unit |

|---------------------------|--------------------------------------------------------------------------|--------------------------------------------------|------|------|------|------|

| DET Pin OVF               | and Valley Detection Section                                             | •                                                | 1    | •    |      |      |

| V <sub>DET-OVP</sub>      | Comparator Reference Voltage                                             |                                                  | 2.45 | 2.50 | 2.55 | V    |

| Av                        | Open-Loop Gain <sup>(3)</sup>                                            |                                                  |      | 60   |      | dB   |

| Bw                        | Gain Bandwidth <sup>(3)</sup>                                            |                                                  |      | 1    |      | MHz  |

| $V_{V-HIGH}$              | Output High Voltage                                                      |                                                  | 4.5  |      |      | V    |

| $V_{V-LOW}$               | Output Low Voltage                                                       |                                                  |      |      | 0.5  | V    |

| t <sub>DET-OVP</sub>      | Output OVP (Latched) Debounce Time                                       |                                                  | 100  | 150  | 200  | μs   |

| I <sub>DET-SOURCE</sub>   | Maximum Source Current                                                   | V <sub>DET</sub> =0 V                            |      |      | 1    | mA   |

| V <sub>DET-HIGH</sub>     | Upper Clamp Voltage                                                      | I <sub>DET</sub> =-1 mA                          |      |      | 5    | V    |

| $V_{DET\text{-}LOW}$      | Lower Clamp Voltage                                                      | I <sub>DET</sub> =1 mA                           | 0.1  | 0.3  |      | V    |

| t <sub>VALLEY-DELAY</sub> | Delay Time from Valley Signal Detected to Output Turn-On <sup>(3)</sup>  |                                                  |      | 200  |      | ns   |

| t <sub>OFF-BNK</sub>      | Leading-Edge-Blanking Time for DET when PWM MOS Turns Off <sup>(3)</sup> |                                                  |      | 4    |      | μs   |

| t <sub>TIME-OUT</sub>     | Time-Out After t <sub>OFF-MIN</sub>                                      |                                                  |      | 9    |      | μs   |

| Oscillator Se             | ection                                                                   |                                                  | •    | \    |      |      |

| t <sub>ON-MAX</sub>       | Maximum On-Time                                                          |                                                  | 38   | 45   | 54   | μs   |

|                           | Minimum Off-Time                                                         | $V_{FB} \ge V_{N,}$                              |      | 8    |      | μs   |

| t <sub>OFF-MIN</sub>      |                                                                          | V <sub>FB</sub> =V <sub>G</sub>                  |      | 38   |      |      |

| $V_N$                     | Beginning of Green-On Mode at FB<br>Voltage Level                        |                                                  | 1.95 | 2.10 | 2.25 | V    |

| $V_{G}$                   | Beginning of Green-Off Mode at FB<br>Voltage Level                       |                                                  | 1.0  | 1.2  | 1.4  | V    |

| $\Delta V_{FBG}$          | Green-Off Mode V <sub>FB</sub> Hysteresis Voltage                        |                                                  | 0.05 | 0.10 | 0.20 | V    |

|                           | Otart Times (Times Out Times)                                            | V <sub>FB</sub> <v<sub>G</v<sub>                 | 1.8  | 2.1  | 2.4  | ms   |

| t <sub>STARTER</sub>      | Start Timer (Time-Out Timer)                                             | V <sub>FB</sub> >V <sub>FB-OLP</sub>             | 25   | 30   | 45   | μs   |

| Output Secti              | on                                                                       |                                                  |      |      |      |      |

| V <sub>OL</sub>           | Output Voltage Low                                                       | V <sub>DD</sub> =15 V,<br>I <sub>O</sub> =150 mA |      |      | 1.5  | V    |

| V <sub>OH</sub>           | Output Voltage High                                                      | V <sub>DD</sub> =12 V,<br>I <sub>O</sub> =150 mA | 7.5  |      | y a  | V    |

| t <sub>R</sub>            | Rising Time                                                              |                                                  |      | 145  | 200  | ns   |

| t <sub>F</sub>            | Falling Time                                                             |                                                  |      | 55   | 120  | ns   |

| V <sub>CLAMP</sub>        | Gate Output Clamping Voltage                                             |                                                  | 16.7 | 18.0 | 19.3 | V    |

Continued on the following page...

# **Electrical Characteristics** (Continued)

Unless otherwise specified,  $V_{DD}$ =10~25 V,  $T_A$ =-40°C ~125°C ( $T_A$ = $T_J$ ).

| Symbol                                       | Parameter                                                 | Conditions                  | Min.  | Тур.  | Max.  | Unit |

|----------------------------------------------|-----------------------------------------------------------|-----------------------------|-------|-------|-------|------|

| Current Sen                                  | se Section                                                |                             |       |       |       |      |

| t <sub>PD</sub>                              | Delay to Output                                           |                             | 20    | 150   | 200   | ns   |

| \/                                           | Limit Voltage on CS Pin for Over-Power Compensation       | I <sub>DET</sub> < 74.41 μA | 0.82  | 0.85  | 0.88  | V    |

| $V_{LIMIT}$                                  |                                                           | I <sub>DET</sub> =550 μA    | 0.380 | 0.415 | 0.450 |      |

| \/                                           | Slope Compensation <sup>(3)</sup>                         | t <sub>ON</sub> =45 μs      |       | 0.3   |       | V    |

| $V_{SLOPE}$                                  |                                                           | t <sub>ON</sub> =0 μs       |       | 0.1   |       |      |

| t <sub>BNK</sub>                             | Leading-Edge-Blanking Time<br>(MOS Turns ON)              |                             | 525   | 625   | 725   | ns   |

| V <sub>CS-H</sub>                            | V <sub>CS</sub> Clamped High Voltage once CS Pin Floating | CS Pin Floating             | 4.5   |       | 5.0   | V    |

| t <sub>CS-H</sub>                            | Delay Time Once CS Pin Floating                           | CS Pin Floating             | f.    | 150   |       | μs   |

| Internal Over-Temperature Protection Section |                                                           |                             |       |       |       |      |

| T <sub>OTP</sub>                             | Internal Threshold Temperature for OTP <sup>(3)</sup>     |                             |       | +140  |       | °C   |

| T <sub>OTP-HYST</sub>                        | Hysteresis Temperature for Internal OTP <sup>(3)</sup>    |                             |       | +15   |       | °C   |

#### Note:

3. This parameter, although guaranteed by design, is not tested in production.

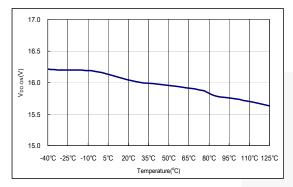

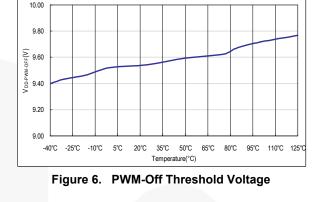

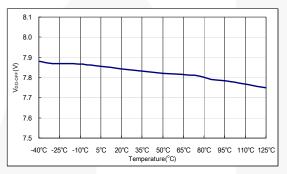

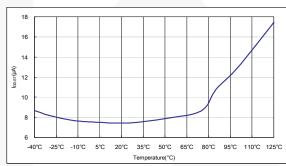

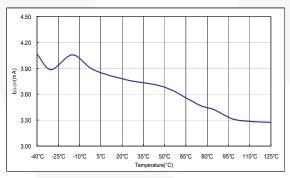

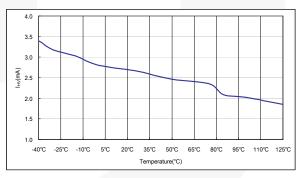

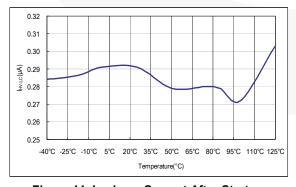

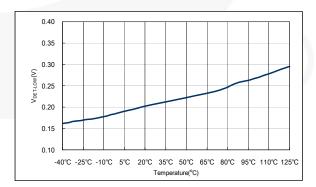

# **Typical Performance Characteristics**

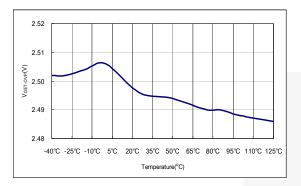

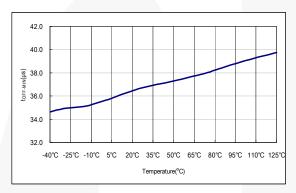

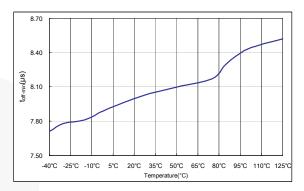

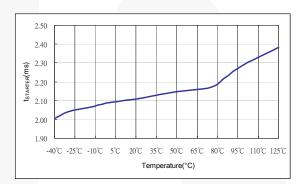

Graphs are normalized at T<sub>A</sub>=25°C.

Figure 5. Turn-On Threshold Voltage

Figure 7. Turn-Off Threshold Voltage

Figure 8. Startup Current

Figure 9. Operating Current

Figure 10. Supply Current Drawn From HV Pin

Figure 11. Leakage Current After Startup

Figure 12. Lower Clamp Voltage

# **Typical Performance Characteristics** (Continued)

These characteristic graphs are normalized at  $T_A = 25$ °C.

Figure 13. Comparator Reference Voltage

Figure 15. Minimum Off Time (V<sub>FB</sub>=V<sub>G</sub>)

Figure 14. Minimum Off Time (V<sub>FB</sub>>V<sub>N</sub>)

Figure 16. Start Timer (V<sub>FB</sub><V<sub>G</sub>)

### **Operation Description**

The FL6300A PWM controller integrates features to enhance the performance of flyback converters. An internal valley voltage detector ensures Quasi-Resonant (QR) operation across a wide range of line voltage.

#### **Startup Current**

For startup, the HV pin is connected to the line input or bulk capacitor through an external diode and resistor,  $R_{HV}$ , which are recommended as 1N4007 and 100 k $\Omega$ . Typical startup current drawn from the HV pin is 1.2 mA and it charges the hold-up capacitor through the diode and resistor. When the  $V_{DD}$  voltage level reaches  $V_{DD\text{-}ON}$ , the startup current switches off. At this point, the  $V_{DD}$  capacitor only supplies the FL6300A to maintain  $V_{DD}$  until the auxiliary winding of the main transformer provides the operating current.

#### **Valley Detection**

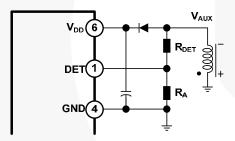

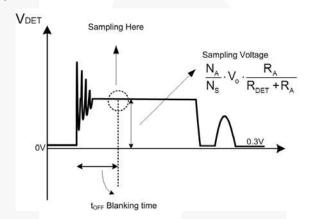

The DET pin is connected to an auxiliary winding of the transformer via resistors of the divider to generate a valley signal once the secondary-side switching current discharges to zero. It detects the valley voltage of the switching waveform to achieve the valley voltage switching. This ensures QR operation, minimizes switching losses, and reduces EMI. Figure 17 shows divider resistors  $R_{\text{DET}}$  and  $R_{\text{A}}$ .  $R_{\text{DET}}$  is recommended as 150  $k\Omega$  to 220  $k\Omega$  to achieve valley voltage switching. When  $V_{\text{AUX}}$  (in Figure 17) is negative, the DET pin voltage is clamped to 0.3 V.

Figure 17. Valley Detect Section

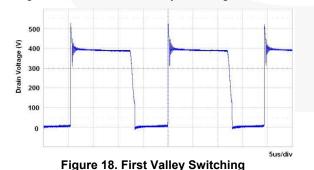

The internal timer (minimum  $t_{\text{OFF}}$ ) prevents gate retriggering within 8 µs after the gate signal going-LOW transition. The minimum  $t_{\text{OFF}}$  limit prevents system frequency being too high. Figure 18 shows a typical drain voltage waveform with first valley switching.

**Green-Mode Operation**

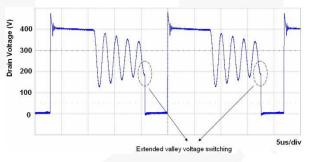

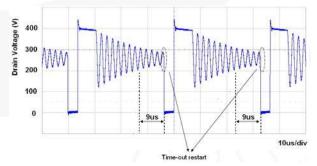

The proprietary green mode provides off-time modulation to linearly decrease the switching frequency under light-load conditions.  $V_{FB}$ , which is derived from the voltage feedback loop, is taken as the reference. In Figure 19, once  $V_{FB}$  is lower than  $V_N$ ,  $t_{\text{OFF-MIN}}$  increases linearly with lower  $V_{FB}$ . The valley voltage detection signal does not start until  $t_{\text{OFF-MIN}}$  finishes. Therefore, the valley-detect circuit is active until  $t_{\text{OFF-MIN}}$  finishes, which decreases the switching frequency and provides extended valley voltage switching. However, in very light-load condition, it might fail to detect the valley voltage after the  $t_{\text{OFF-MIN}}$  expires. Under this condition, an internal  $t_{\text{TIME-OUT}}$  signal initiates a new cycle after a 9  $\mu$ s delay. Figure 20 and Figure 21 show the two conditions.

Figure 19. V<sub>FB</sub> vs. t<sub>OFF-MIN</sub> Curve

Figure 20. QR Operation in Extended Valley Voltage Detection Mode

Figure 21. Internal t<sub>TIME-OUT</sub> Initiates New Cycle After Failure to Detect Valley Voltage

### **Current Sensing and PWM Current Limiting**

Peak-current-mode control is utilized to regulate output voltage and provide pulse-by-pulse current limiting. The switch current is detected by a sense resistor into the CS pin. The PWM duty cycle is determined by this current-sense signal and  $V_{FB}$ . When the voltage on CS reaches around  $V_{LIMIT} = (V_{FB} - 1.2)/3$ , the switch cycle is terminated immediately.  $V_{LIMIT}$  is internally clamped to a variable voltage around 0.85 V for output power limit.

#### Leading-Edge Blanking (LEB)

Each time the power MOFFET switches on, a turn-on spike occurs on the sense resistor. To avoid premature termination of the switching pulse, lead-edge blanking time is built in. During the blanking period, the current limit comparator is disabled; it cannot switch off the gate driver.

#### **Under-Voltage Lockout (UVLO)**

The turn-on, PWM-off, and turn-off thresholds are fixed internally at  $16\,V\,/\,10\,V\,/\,8\,V$ , respectively. During startup, the startup capacitor must be charged to  $16\,V$  through the startup resistor to enable the IC. The hold-up capacitor continues to supply  $V_{DD}$  until energy can be delivered from the auxiliary winding of the main transformer.  $V_{DD}$  must not drop below  $10\,V$  during this startup process. This UVLO hysteresis window ensures that hold-up capacitor is adequate to supply  $V_{DD}$  during startup.

#### **Gate Output**

The BiCMOS output stage is a fast totem-pole gate driver. Cross conduction has been avoided to minimize heat dissipation, increase efficiency, and enhance reliability. The output driver is clamped by an internal 18 V Zener diode to protect power MOSFET transistors against undesired over-voltage gate signals.

#### **Over-Power Compensation**

To compensate for the variation of a wide AC input range, the DET pin produces an offset voltage to compensate the threshold voltage of the peak current limit for a constant-power limit. The offset is generated in accordance with the input voltage when PWM signal is enabled. This results in a lower current limit at highline inputs than low-line inputs. At fixed-load condition, the CS limit is higher when the value of  $R_{\text{DET}}$  is higher.  $R_{\text{DET}}$  also affects the H/L line constant power limit.

Figure 22. H/L Line Constant Power Limit Compensated by DET Pin

#### **V<sub>DD</sub> Over-Voltage Protection**

$V_{DD}$  over-voltage protection prevents damage due to abnormal conditions. Once the  $V_{DD}$  voltage is over the  $V_{DD}$  over-voltage protection voltage ( $V_{DD\text{-}OVP}$ ) and lasts for  $t_{VDDOVP}$ , the PWM pulse is disabled until the  $V_{DD}$  voltage drops below the UVLO, then starts again.

#### **Output Over-Voltage Protection**

The output over-voltage protection works by the sampling voltage, as shown in Figure 23, after switch-off sequence. A 4 µs blanking time ignores the leakage inductance ringing. A voltage comparator and a 2.5 V reference voltage develop an output OVP protection. The ratio of the divider determines the sampling voltage of the stop gate, as an optical coupler and secondary shunt regulator are used. If the DET pin OVP is triggered, the power system enters latch-mode until AC power is removed.

Figure 23. Voltage Sampled After 4 µs Blanking Time After Switch-Off Sequence

#### **Short-Circuit and Open-Loop Protection**

The FB voltage increases every time the output of the power supply is shorted or overloaded. If the FB voltage remains higher than a built-in threshold for longer than  $t_{\text{D-OLP}}$ , PWM output is turned off. As PWM output is turned-off, the supply voltage  $V_{\text{DD}}$  begins decreasing.

When  $V_{DD}$  goes below the PWM-off threshold of 10 V,  $V_{DD}$  decreases to 8 V, then the controller is totally shut down.  $V_{DD}$  is charged up to the turn-on threshold voltage of 16 V through the startup resistor until PWM output is restarted. This protection feature continues as long as the overloading condition persists. This prevents the power supply from overheating due to overloading.

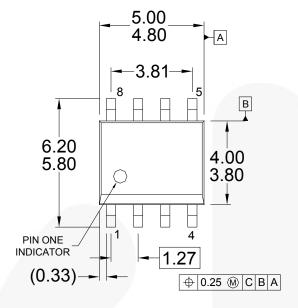

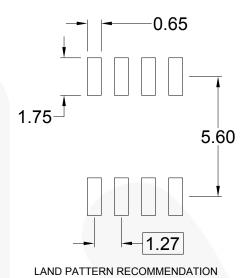

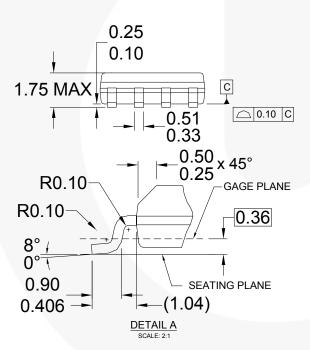

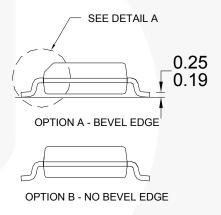

# **Physical Dimensions**

#### NOTES: UNLESS OTHERWISE SPECIFIED

- A) THIS PACKAGE CONFORMS TO JEDEC MS-012, VARIATION AA, ISSUE C,

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE MOLD

- C) DIMENSIONS DO NOT INCLUDE MOLE FLASH OR BURRS.

- D) LANDPATTERN STANDARD: SOIC127P600X175-8M.

- E) DRAWING FILENAME: M08AREV13

Figure 24. 8-Pin Small Outline Package (SOP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2Cool<sup>TI</sup> AccuPower™ AX-CAPINI BitSiC™ Build it Now™ CorePLUS™ CorePOWER™ CROSSVOLT™

CTL™ Current Transfer Logic™ DEUXPEED<sup>6</sup>

Dual Cool™ EcoSPARK® EfficientMax™ **ESBC™**

Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT **FAST®**

FastvCore™ FETBench™ FlashWriter®\* F-PFS™ FRFET® Global Power Resource SM GreenBridge™ Green FPS™

Green FPS™ e-Series™ Gmax™ **GTO™** IntelliMAX™ ISOPLANAR™

Making Small Speakers Sound Louder

and Better™ MegaBuck<sup>TI</sup> MICROCOUPLER™ MicroFET™ MicroPak™ MicroPak2™ Miller Drive™ MotionMax™ mWSaver™ OptoHiT™

OPTOLOGIC® OPTOPLANAR® PowerTrench® PowerXS™

Programmable Active Droop™

QFET® OSTM Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™ SignalWise™

SmartMax™ SMART START™

Solutions for Your Success™

SPM<sup>®</sup> STEALTH™ SuperFET® SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS® SyncFET™ Sync-Lock™ SYSTEM SGENERAL®\* The Power Franchise®

wer TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO" TinyPower™ TinyPWM™ TinyWire™ TranSIC™ TriFault Detect™ TRUECURRENT®\* µSerDes™

UHC<sup>®</sup> Ultra FRFET™ UniFET™ VCX™ VisualMax™ VoltagePlus™ XST

\* Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com,

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

| Definition of Terms                                                 |                   |                                                                                                                                                                                                     |  |  |

|---------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Datasheet Identification                                            | Product Status    | Definition                                                                                                                                                                                          |  |  |

| Advance Information Formative / In Des Preliminary First Production |                   | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

|                                                                     |                   | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed                                            | Full Production   | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                                                            | Not In Production | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.  The datasheet is for reference information only.                                                   |  |  |

Rev. 162

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hol

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81–3–5817–1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative