#### The Future of Analog IC Technology

# DESCRIPTION

The MPQ1924 is a high-frequency, 100V, halfbridge, N-channel, power MOSFET driver. Its low-side and high-side driver channels are independently controlled and matched with less than 5ns in time delay. Under-voltage lockout on both high-side and low-side supplies force their outputs low in case of insufficient supply. The integrated bootstrap diode reduces external component count.

# FEATURES

- Drives an N-Channel MOSFET Half Bridge

- 118V V<sub>BST</sub> Voltage Range

- On-Chip Bootstrap Diode

- Typical Propagation Delay of 20ns

- Gate Drive Matching of Less than 5ns

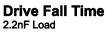

- Drives a 2.2nF Load with 15ns Rise Time and 12ns Fall Time at 12V VDD

- TTL-Compatible Input

- Quiescent Current of Less than 150μA

- UVLO for Both High Side and Low Side

- SOIC-8 Package

### **APPLICATIONS**

- Motor Drivers

- Telecom Half-Bridge Power Supplies

- Avionics DC-DC Converters

- Two-Switch Forward Converters

- Active-Clamp Forward Converters

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

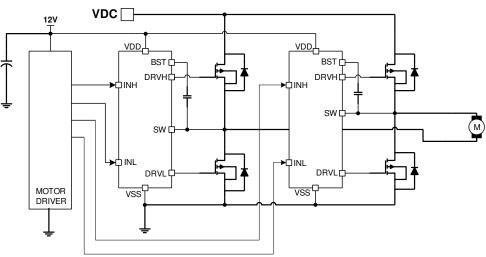

# TYPICAL APPLICATION

### **ORDERING INFORMATION**

| Part Number | Package | Top Marking |

|-------------|---------|-------------|

| MPQ1924HS*  | SOIC-8  | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MPQ1924HS–Z) For RoHS compliant packaging, add suffix –LF (e.g. MPQ1924HS–LF–Z)

# **TOP MARKING**

### MP1924

#### LLLLLLL

MPSYWW

MP1924: product code of MPQ1924HS; LLLLLLL: lot number; MPS: MPS prefix; Y: year code; WW: week code;

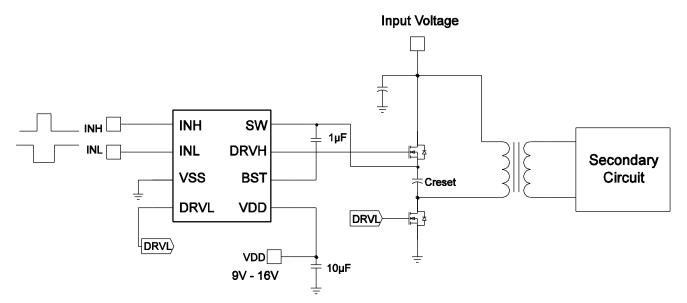

# PACKAGE REFERENCE

|                                  | TOP VIEW | 1                                 |

|----------------------------------|----------|-----------------------------------|

| VDD 1<br>BST 2<br>DRVH 3<br>SW 4 | 0        | 8 DRVL<br>7 VSS<br>6 INL<br>5 INH |

|                                  | SOIC-8   |                                   |

### ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage (V <sub>DD</sub> ) | 0.3V to 18V                             |

|-----------------------------------|-----------------------------------------|

| SW Voltage (V <sub>SW</sub> )     | 5.0V to 105V                            |

| BST Voltage (V <sub>BST</sub> )   | 0.3V to 118V                            |

| BST to SW                         |                                         |

| DRVH to SW0.3V to (E              | 3ST-SW) + 0.3V                          |

| DRVL to VSS0.3V                   | to (VDD + 0.3V)                         |

| All Other Pins0.3                 | $/ \text{ to } (V_{DD} + 0.3 \text{V})$ |

| Continuous Power Dissipation      | $(T_A = 25^{\circ}C)^{(2)}$             |

| SOIC-8                            |                                         |

| Junction Temperature              | 150°C                                   |

| Lead Temperature                  |                                         |

| Storage Temperature               |                                         |

|                                   |                                         |

# Recommended Operating Conditions <sup>(3)</sup>

| Supply Voltage V <sub>DD</sub> . | 9.0V to 16.0V                       |

|----------------------------------|-------------------------------------|

| SW Voltage (V <sub>SW</sub> )    |                                     |

| SW Slew Rate                     | <50V/ns                             |

| Operating Junction 1             | emp. (T <sub>J</sub> )40°C to 125°C |

# Thermal Resistance $^{(4)}$ $\theta_{JA}$

$\theta_{JC}$

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J(MAX)$ , the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D(MAX)=(T_J(MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{DD}$  =  $V_{BST}\text{-}V_{SW}$  = 12V,  $V_{SS}$  =  $V_{SW}$  = 0V, No load at DRVH and DRVL,  $T_A$  = +25°C, unless otherwise noted.

| Parameter                         | Symbol            | Condition                                   | Min | Тур  | Max | Units |  |

|-----------------------------------|-------------------|---------------------------------------------|-----|------|-----|-------|--|

| Supply Currents                   |                   |                                             |     |      |     |       |  |

| VDD quiescent current             | I <sub>DDQ</sub>  | INL = INH = 0                               |     | 100  | 150 | μA    |  |

| VDD operating current             | I <sub>DDO</sub>  | fsw = 500kHz                                |     | 9    |     | mA    |  |

| Floating driver quiescent current | I <sub>BSTQ</sub> | INL = INH = 0                               |     | 60   | 90  | μA    |  |

| Floating driver operating current | I <sub>BSTO</sub> | fsw = 500 kHz                               |     | 7.5  |     | mA    |  |

| Leakage current                   | I <sub>LK</sub>   | BST = SW = 100V                             |     | 0.05 | 1   | μA    |  |

| Inputs                            |                   |                                             |     |      |     |       |  |

| INL/INH High                      |                   |                                             |     | 2    | 2.4 | V     |  |

| INL/INH Low                       |                   |                                             | 1   | 1.4  |     | V     |  |

| INL/INH internal pull-down        | R <sub>IN</sub>   |                                             |     | 185  |     | kΩ    |  |

| resistance                        | ιчN               |                                             |     | 100  |     | N22   |  |

| Under Voltage Protection          |                   |                                             |     |      | n   |       |  |

| VDD rising threshold              | $V_{DDR}$         |                                             | 8.1 | 8.4  | 8.8 | V     |  |

| VDD hysteresis                    | $V_{DDH}$         |                                             |     | 0.5  |     | V     |  |

| (BST-SW) rising threshold         | $V_{BSTR}$        |                                             | 6.9 | 7.3  | 7.7 | V     |  |

| (BST-SW) hysteresis               | $V_{BSTH}$        |                                             |     | 0.55 |     | V     |  |

| Bootstrap Diode                   |                   |                                             |     |      |     |       |  |

| Bootstrap diode VF @ 100µA        | $V_{F1}$          |                                             |     | 0.5  |     | V     |  |

| Bootstrap diode VF @ 100mA        | $V_{F2}$          |                                             |     | 0.95 |     | V     |  |

| Bootstrap diode dynamic R         | $R_{D}$           | @ 100mA                                     |     | 2    |     | Ω     |  |

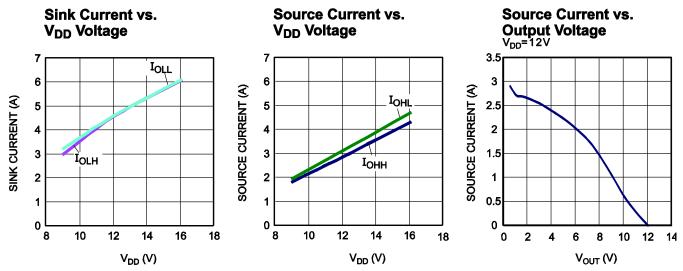

| Low Side Gate Driver              |                   |                                             |     |      |     |       |  |

| Low level output voltage          | $V_{OLL}$         | I <sub>O</sub> = 100mA                      |     | 0.08 |     | V     |  |

| High level output voltage to rail | $V_{OHL}$         | I <sub>O</sub> = -100mA                     |     | 0.23 |     | V     |  |

| Source Current <sup>(5)</sup>     | I <sub>OHL</sub>  | $V_{DRVL} = 0V, V_{DD} = 12V$               |     | 3    |     | Α     |  |

| Source Current                    |                   | $V_{DRVL} = 0V, V_{DD} = 16V$               |     | 4.7  |     | Α     |  |

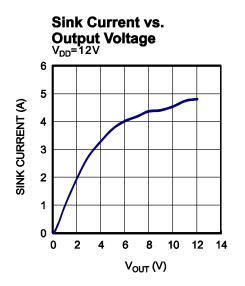

| Sink Current <sup>(5)</sup>       | 1                 | $V_{DRVL} = V_{DD} = 12V$                   |     | 4.5  |     | Α     |  |

| Sink Current                      | I <sub>OLL</sub>  | $V_{DRVL} = V_{DD} = 16V$                   |     | 6    |     | Α     |  |

| Floating Gate Driver              |                   |                                             |     |      |     |       |  |

| Low level output voltage          | $V_{OLH}$         | I <sub>O</sub> = 100mA                      |     | 0.08 |     | V     |  |

| High level output voltage to rail | $V_{OHH}$         | I <sub>O</sub> = -100mA                     |     | 0.23 |     | V     |  |

| Source Current <sup>(5)</sup>     | I <sub>ОНН</sub>  | $V_{DRVH} = 0V, V_{DD} = 12V$               |     | 2.6  |     | Α     |  |

|                                   |                   | $V_{\text{DRVH}} = 0V, V_{\text{DD}} = 16V$ |     | 4    |     | Α     |  |

| Sink Current <sup>(5)</sup>       | 1                 | $V_{\text{DRVH}} = V_{\text{DD}} = 12V$     |     | 4.5  |     | Α     |  |

|                                   | I <sub>OLH</sub>  | $V_{DRVH} = V_{DD} = 16V$                   |     | 5.9  |     | Α     |  |

### ELECTRICAL CHARACTERISTICS (continued)

$V_{DD} = V_{BST} - V_{SW} = 12V$ ,  $V_{SS} = V_{SW} = 0V$ , No load at DRVH and DRVL,  $T_A = +25^{\circ}C$ , unless otherwise noted.

| Parameter                                                          | Symbol                              | Condition     | Min | Тур | Max | Units |  |

|--------------------------------------------------------------------|-------------------------------------|---------------|-----|-----|-----|-------|--|

| Switching Spec Low Side Ga                                         | Switching Spec Low Side Gate Driver |               |     |     |     |       |  |

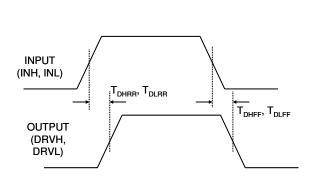

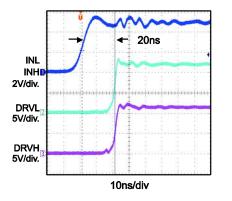

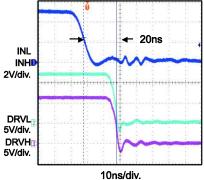

| Turn-off propagation delay<br>INL falling to DRVL falling          | $T_{DLFF}$                          |               |     | 20  |     | ns    |  |

| Turn-on propagation delay<br>INL rising to DRVL rising             | $T_{DLRR}$                          |               |     | 20  |     |       |  |

| DRVL rise time                                                     |                                     | $C_L = 2.2nF$ |     | 15  |     | ns    |  |

| DRVL fall time                                                     |                                     | $C_L = 2.2nF$ |     | 9   |     | ns    |  |

| Switching Spec Floating Gate                                       | e Driver                            |               |     |     |     |       |  |

| Turn-off propagation delay<br>INH falling to DRVH falling          | T <sub>DHFF</sub>                   |               |     | 20  |     | ns    |  |

| Turn-on propagation delay<br>INH rising to DRVH rising             | T <sub>DHRR</sub>                   |               |     | 20  |     | ns    |  |

| DRVH rise time                                                     |                                     | $C_L = 2.2nF$ |     | 15  |     | ns    |  |

| DRVH fall time                                                     |                                     | $C_L = 2.2nF$ |     | 12  |     | ns    |  |

| Switching Spec Matching                                            |                                     |               |     |     |     | _     |  |

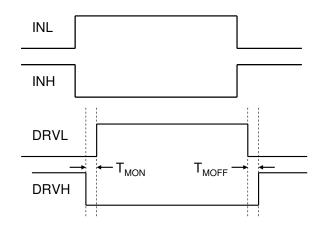

| Floating driver turn-off to low side drive turn-on $^{(5)}$        | T <sub>MON</sub>                    |               |     | 1   | 5   | ns    |  |

| Low side driver turn-off to floating driver turn-on <sup>(5)</sup> | T <sub>MOFF</sub>                   |               |     | 1   | 5   | ns    |  |

| Minimum input pulse width that changes the output <sup>(5)</sup>   | $T_{PW}$                            |               |     |     | 50  | ns    |  |

| Bootstrap diode turn-on or turn-off time $^{(5)}$                  | T <sub>BS</sub>                     |               |     | 10  |     | ns    |  |

| Thermal shutdown                                                   |                                     |               |     | 150 |     | °C    |  |

| Thermal shutdown hysteresis                                        |                                     |               |     | 25  |     | °C    |  |

Note:

5) Guaranteed by design.

# **PIN FUNCTIONS**

| SOIC-8<br>Pin # | Name                | Description                                                                                                                                                      |

|-----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | VDD                 | Supply input. This pin supplies power to all the internal circuitry. Place a decoupling capacitor to ground close to this pin to ensure stable and clean supply. |

| 2               | BST                 | Bootstrap. This is the positive power supply for the internal floating high-side MOSFET driver. Connect a bypass capacitor between this pin and SW pin.          |

| 3               | DRVH                | Floating driver output.                                                                                                                                          |

| 4               | SW                  | Switching node.                                                                                                                                                  |

|                 | NC                  | No connection.                                                                                                                                                   |

| 5               | INH                 | Control signal input for the floating driver.                                                                                                                    |

| 6               | INL                 | Control signal input for the low side driver.                                                                                                                    |

| 7               | VSS,<br>exposed pad | Chip ground. Connect exposed pad to VSS for proper thermal operation.                                                                                            |

| 8               | DRVL                | Low side driver output.                                                                                                                                          |

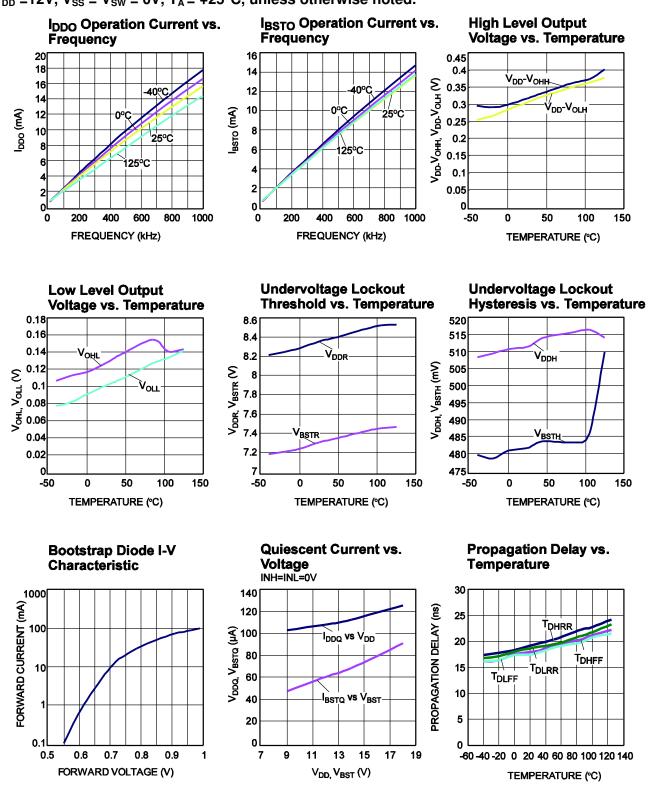

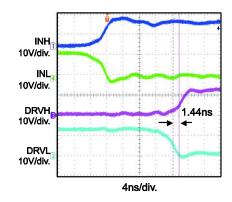

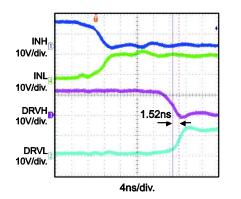

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{DD}$  =12V,  $V_{SS}$  =  $V_{SW}$  = 0V,  $T_A$  = +25°C, unless otherwise noted.

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{DD}$  =12V,  $V_{SS}$  =  $V_{SW}$  = 0V,  $T_A$  = +25°C, unless otherwise noted.

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{DD}$  =12V,  $V_{SS}$  =  $V_{SW}$  = 0V,  $T_A$  = +25°C, unless otherwise noted.

#### **Turn-on Propagation Delay**

y Turn-off Propagation Delay

Gate Drive Matching T<sub>MOFF</sub>

Gate Drive Matching T<sub>MON</sub>

DRVH DRVH SV/div. DRVL SV/div. 10ns/div.

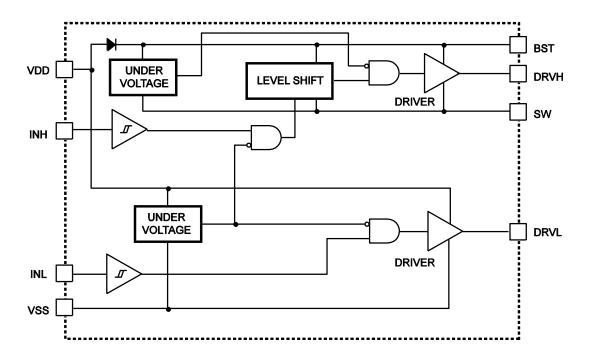

# **BLOCK DIAGRAM**

Figure 2: Function Block Diagram

# **APPLICATION**

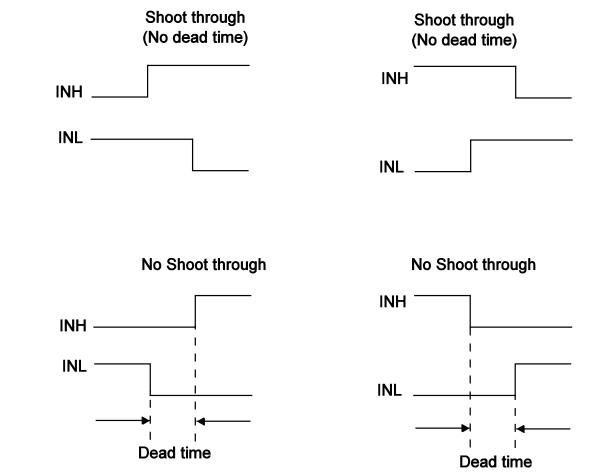

The input signals of INH and INL can be controlled independently. If both INH and INL control the high-side MOSFET and low-side MOSFET of the same bridge, then users must avoid shoot through by setting sufficient dead time between INH and INL low, and vice versa. See Figure 3 below. Dead time is defined as the time interval between INH low and INL low.

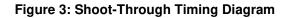

### **REFERENCE DESIGN CIRCUITS**

#### Half Bridge Converter

The MPQ1924 drives the MOSFETS with alternating signals (with dead time) in half-bridge converter topology. Therefore, from the PWM

controller drives INH and INL with alternating signals the input voltage can go up to 100V.

Figure 4: Half Bridge Converter

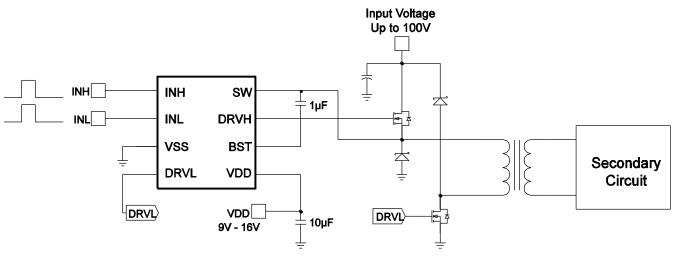

#### **Two-Switch Forward Converter**

In two-switch forward converter topology, both MOSFETs are turned on and off simultaneously. The input signal (INH and INL) comes from a PWM controller that senses the output voltage (and output current during current-mode control).

The Schottky diodes clamp the reverse swing of the power transformer and must be rated for the input voltage. The input voltage can go up to 100V.

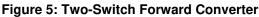

#### **Active-Clamp Forward Converter**

In active-clamp forward converter topology, the MPQ1924 drives the MOSFETs with alternating signals. The high-side MOSFET, in conjunction with  $C_{reset}$ , is used to reset the power transformer in a lossless manner.

This topology lends itself well to run at duty cycles exceeding 50%. The device may not be able to run at 100V under this topology.

Figure 6 Active-Clamp Forward Converter

# **PACKAGE INFORMATION**

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.