ISO1042

#### SLLSF09E - DECEMBER 2017 - REVISED JANUARY 2020

# ISO1042 Isolated CAN Transceiver With 70-V Bus Fault Protection and Flexible Data Rate

#### 1 Features

- Meets the ISO 11898-2:2016 physical layer standard

- Supports classic CAN up to 1 Mbps and FD (Flexible Data Rate) up to 5 Mbps

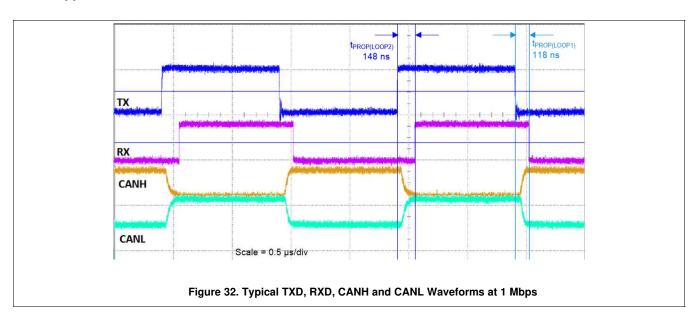

- · Low loop delay: 152 ns

- · Protection features

- DC bus fault protection voltage: ±70 V

- HBM ESD tolerance on bus pins: ±16 kV

- Driver Dominant Time Out (TXD DTO)

- Undervoltage protection on V<sub>CC1</sub> and V<sub>CC2</sub>

- Common-Mode Voltage Range: ±30 V

- Ideal passive, high impedance bus terminals when unpowered

- High CMTI: 100 kV/μs

- V<sub>CC1</sub> voltage range: 1.71 V to 5.5 V

- Supports 1.8-V, 2.5-V, 3.3-V and 5.0-V logic interface to the CAN controller

- V<sub>CC2</sub> Voltage Range: 4.5 V to 5.5 V

- Robust Electromagnetic Compatibility (EMC)

- System-level ESD, EFT, and surge immunity

- Low emissions

- Ambient Temperature Range: –40°C to +125°C

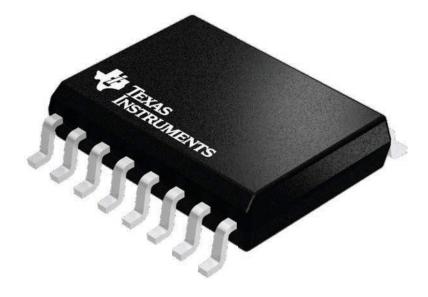

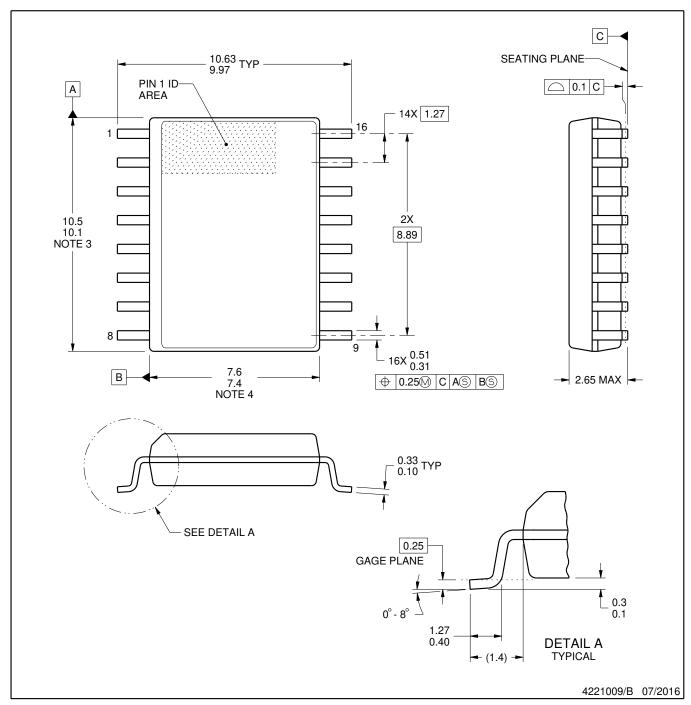

- 16-SOIC and 8-SOIC package options

- Automotive version available: ISO1042-Q1

- Safety-related certifications:

- 7071-V<sub>PK</sub> V<sub>IOTM</sub> and 1500-V<sub>PK</sub> V<sub>IORM</sub> (Reinforced and Basic Options) per DIN VDE V 0884-11:2017-01

- 5000-V<sub>RMS</sub> Isolation for 1 Minute per UL 1577

- IEC 60950-1, IEC 60601-1 and EN 61010-1 certifications

- CQC, TUV and CSA certifications

# 2 Applications

- AC and servo drives

- Solar inverters

- PLC and DCS communication modules

- · Elevators and escalators

- Industrial power supplies

- Battery charging and management

### 3 Description

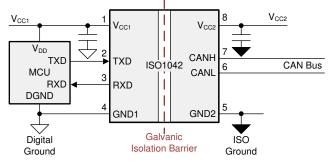

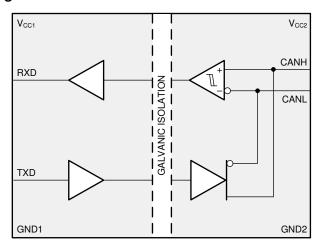

The ISO1042 device is a galvanically-isolated controller area network (CAN) transceiver that meets the specifications of the ISO11898-2 (2016) standard. The ISO1042 device offers ±70-V DC bus fault protection and ±30-V common-mode voltage range. The device supports up to 5-Mbps data rate in CAN FD mode allowing much faster transfer of payload compared to classic CAN. This device uses a silicon dioxide (SiO<sub>2</sub>) insulation barrier with a withstand voltage of 5000 V<sub>RMS</sub> and a working voltage of 1060 Electromagnetic compatibility has significantly enhanced to enable system-level ESD, EFT, surge, and emissions compliance. Used in conjunction with isolated power supplies, the device protects against high voltage, and prevents noise currents from the bus from entering the local ground. The ISO1042 device is available for both basic and reinforced isolation (see Reinforced and Basic Isolation Options). The ISO1042 device supports a wide ambient temperature range of -40°C to +125°C. The device is available in the SOIC-16 (DW) package and a smaller SOIC-8 (DWV) package.

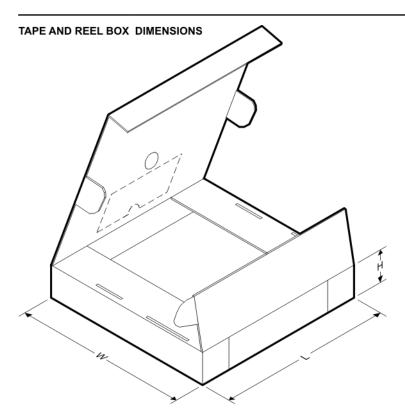

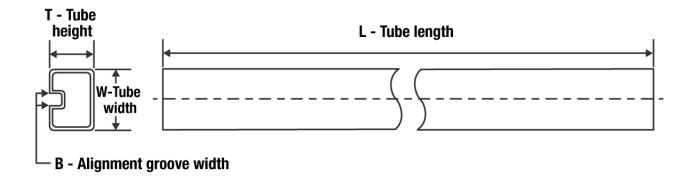

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)    |  |  |

|-------------|-----------|--------------------|--|--|

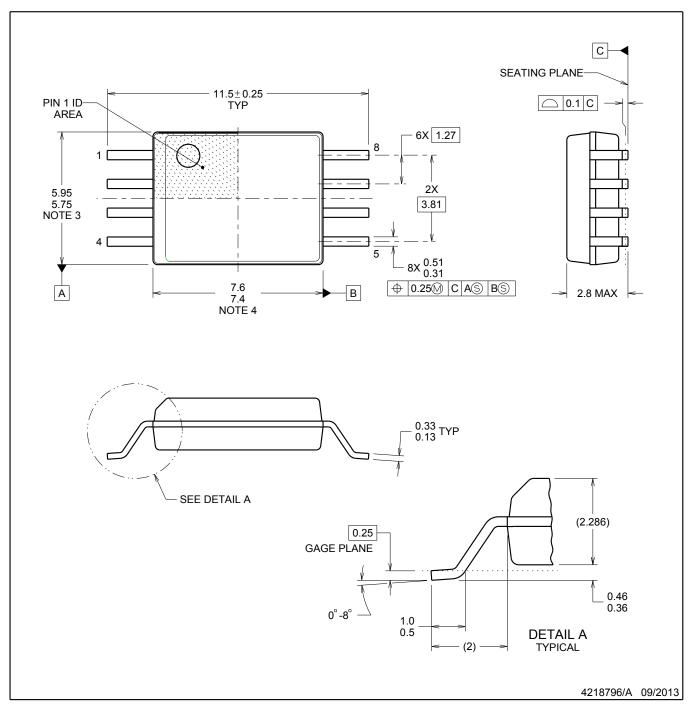

| 1001040     | SOIC (8)  | 5.85 mm × 7.50 mm  |  |  |

| ISO1042     | SOIC (16) | 10.30 mm × 7.50 mm |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

### **Reinforced and Basic Isolation Options**

| FEATURE            | ISO1042x                                        | ISO1042Bx                                       |  |  |  |

|--------------------|-------------------------------------------------|-------------------------------------------------|--|--|--|

| Protection Level   | Reinforced                                      | Basic                                           |  |  |  |

| Surge Test Voltage | 10000 V <sub>PK</sub>                           | 6000 V <sub>PK</sub>                            |  |  |  |

| Isolation Rating   | 5000 V <sub>RMS</sub>                           | 5000 V <sub>RMS</sub>                           |  |  |  |

| Working Voltage    | 1060 V <sub>RMS</sub> /<br>1500 V <sub>PK</sub> | 1060 V <sub>RMS</sub> /<br>1500 V <sub>PK</sub> |  |  |  |

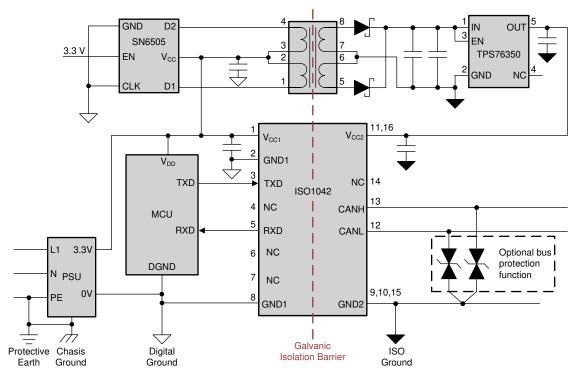

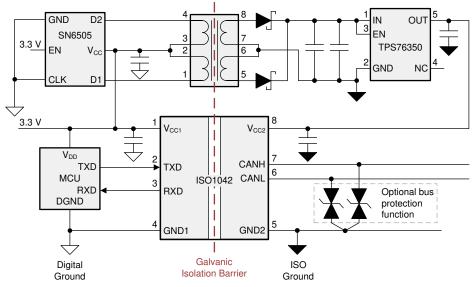

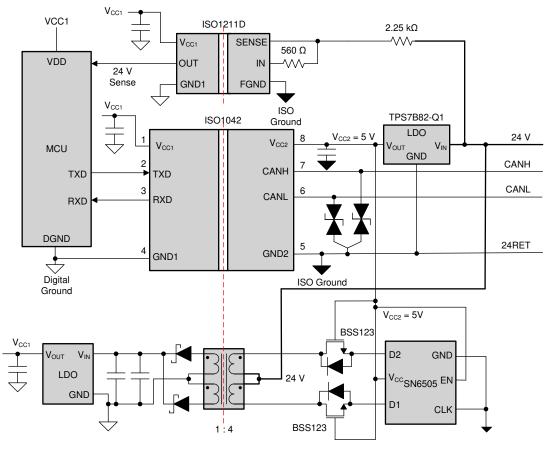

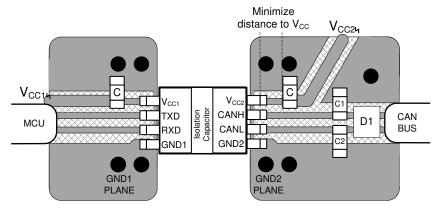

#### **Application Diagram**

Copyright © 2017, Texas Instruments Incorporated

# **Table of Contents**

| 1 | Features 1                                          | 8  | Detailed Description                               | 19 |

|---|-----------------------------------------------------|----|----------------------------------------------------|----|

| 2 | Applications 1                                      |    | 8.1 Overview                                       | 19 |

| 3 | Description 1                                       |    | 8.2 Functional Block Diagram                       | 19 |

| 4 | Revision History2                                   |    | 8.3 Feature Description                            | 19 |

| 5 | Pin Configuration and Functions                     |    | 8.4 Device Functional Modes                        | 23 |

| 6 | Specifications                                      | 9  | Application and Implementation                     | 24 |

| 0 |                                                     |    | 9.1 Application Information                        |    |

|   | • • • • • • • • • • • • • • • • • • • •             |    | 9.2 Typical Application                            |    |

|   |                                                     |    | 9.3 DeviceNet Application                          |    |

|   | 6.3 Transient Immunity                              | 10 | Power Supply Recommendations                       |    |

|   | 6.5 Thermal Information                             | 11 | Layout                                             |    |

|   | 6.6 Power Ratings                                   |    | 11.1 Layout Guidelines                             |    |

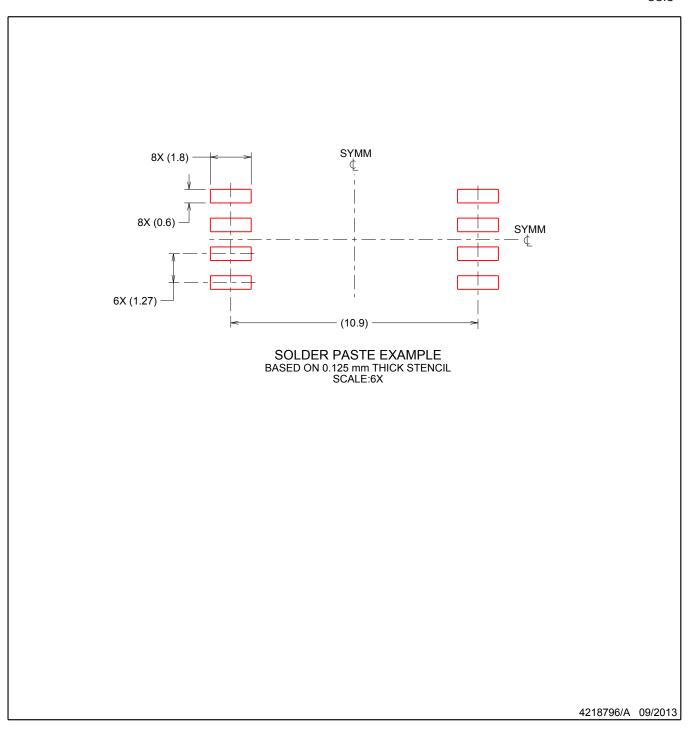

|   | 6.7 Insulation Specifications                       |    | 11.2 Layout Example                                |    |

|   | 6.8 Safety-Related Certifications                   | 12 | Device and Documentation Support                   |    |

|   | 6.9 Safety Limiting Values                          |    | 12.1 Documentation Support                         |    |

|   | 6.10 Electrical Characteristics - DC Specification9 |    | 12.2 Receiving Notification of Documentation Updat |    |

|   | 6.11 Switching Characteristics                      |    | 12.3 Community Resource                            |    |

|   | 6.12 Insulation Characteristics Curves              |    | 12.4 Trademarks                                    | 31 |

|   | 6.13 Typical Characteristics                        |    | 12.5 Electrostatic Discharge Caution               | 31 |

| 7 | Parameter Measurement Information                   |    | 12.6 Glossary                                      |    |

| • | 7.1 Test Circuits                                   | 13 | Mechanical, Packaging, and Orderable Information   |    |

**4 Revision History**NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision D (October 2019) to Revision E                                                          | Page     |

|---------------------------------------------------------------------------------------------------------------|----------|

| Changed new safety certification                                                                              | 1        |

| Changes from Revision C (October 2018) to Revision D                                                          | Page     |

| Added ISO1042-Q1 link                                                                                         | 1        |

| Changes from Revision B (July 2018) to Revision C                                                             | Page     |

| Initial Release                                                                                               | 1        |

| Changes from Revision A (May 2018) to Revision B                                                              | Page     |

| <ul> <li>Increased the size of the GND2 plane and changed the NC pin to GND2 in the 16-DW Layout E</li> </ul> | xample30 |

| Changes from Original (December 2017) to Revision A                                                           | Page     |

| Changed pin 10 from NC to GND2                                                                                |          |

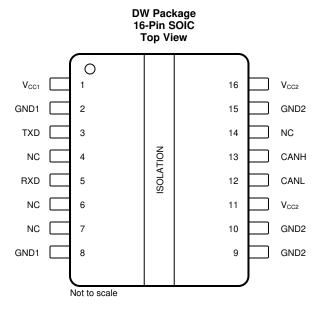

# 5 Pin Configuration and Functions

Pin Functions—16 Pins

|     | PIN              |     |                                                                                  |

|-----|------------------|-----|----------------------------------------------------------------------------------|

| NO. | NAME             | I/O | DESCRIPTION                                                                      |

| 1   | V <sub>CC1</sub> | _   | Digital-side supply voltage, Side 1                                              |

| 2   | GND1             | _   | Digital-side ground connection, Side 1                                           |

| 3   | TXD              | I   | CAN transmit data input (LOW for dominant and HIGH for recessive bus states)     |

| 4   | NC               | _   | Not connected                                                                    |

| 5   | RXD              | 0   | CAN receive data output (LOW for dominant and HIGH for recessive bus states)     |

| 6   | NC               | _   | Not connected                                                                    |

| 7   | NC               | _   | Not connected                                                                    |

| 8   | GND1             | _   | Digital-side ground connection, Side 1                                           |

| 9   | CND3             |     | Transaciver side ground connection Cide 2                                        |

| 10  | GND2             | _   | Transceiver-side ground connection, Side 2                                       |

| 11  | V <sub>CC2</sub> | _   | Transceiver-side supply voltage, Side 2. Must be externally connected to pin 16. |

| 12  | CANL             | I/O | Low-level CAN bus line                                                           |

| 13  | CANH             | I/O | High-level CAN bus line                                                          |

| 14  | NC               | _   | Not connected                                                                    |

| 15  | GND2             | _   | Transceiver-side ground connection, Side 2                                       |

| 16  | V <sub>CC2</sub> | _   | Transceiver-side supply voltage, Side 2. Must be externally connected to pin 11. |

### Pin Functions—8 Pins

|     | PIN              |     | PIN                                                                          |  | DESCRIPTION |  |

|-----|------------------|-----|------------------------------------------------------------------------------|--|-------------|--|

| NO. | NAME             | I/O | DESCRIPTION                                                                  |  |             |  |

| 1   | V <sub>CC1</sub> | _   | Digital-side supply voltage, Side 1                                          |  |             |  |

| 2   | TXD              | - 1 | CAN transmit data input (LOW for dominant and HIGH for recessive bus states) |  |             |  |

| 3   | RXD              | 0   | AN receive data output (LOW for dominant and HIGH for recessive bus states)  |  |             |  |

| 4   | GND1             | _   | Digital-side ground connection, Side 1                                       |  |             |  |

| 5   | GND2             | _   | ransceiver-side ground connection, Side 2                                    |  |             |  |

| 6   | CANL             | I/O | Low-level CAN bus line                                                       |  |             |  |

| 7   | CANH             | I/O | High-level CAN bus line                                                      |  |             |  |

| 8   | V <sub>CC2</sub> | _   | Transceiver-side supply voltage, Side 2                                      |  |             |  |

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)(2)

|                       |                                                    | MIN  | MAX                   | UNIT         |

|-----------------------|----------------------------------------------------|------|-----------------------|--------------|

| V <sub>CC1</sub>      | Supply voltage, side 1                             | -0.5 | 6                     | V            |

| V <sub>CC2</sub>      | Supply voltage, side 2                             | -0.5 | 6                     | V            |

| V <sub>IO</sub>       | Logic input and output voltage range (TXD and RXD) | -0.5 | $V_{CC1} + 0.5^{(3)}$ | ٧            |

| Io                    | Output current on RXD pin                          | -15  | 15                    | mA           |

| V <sub>BUS</sub>      | Voltage on bus pins (CANH, CANL)                   | -70  | 70                    | V            |

| V <sub>BUS_DIFF</sub> | Differential voltage on bus pins (CANH-CANL)       | -70  | 70                    | V            |

| $T_J$                 | Junction temperature                               | -40  | 150                   | $^{\circ}$   |

| T <sub>STG</sub>      | Storage temperature                                | -65  | 150                   | $^{\circ}$ C |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    | •                                                                                             |                                      |        |      |

|--------------------|-----------------------------------------------------------------------------------------------|--------------------------------------|--------|------|

|                    |                                                                                               |                                      | VALUE  | UNIT |

|                    | Electrostatic discharge                                                                       | All pins <sup>(1)</sup>              | ±6000  | V    |

| V                  | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001                                         | CANH and CANL to GND2 <sup>(1)</sup> | ±16000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge<br>Charged device model (CDM), per<br>JEDEC specification JESD22-C101 | All pins (2)                         | ±1500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Transient Immunity

|                    | PARAMETER                  | TEST CONDITIONS                                  | VALUE | UNIT |

|--------------------|----------------------------|--------------------------------------------------|-------|------|

|                    |                            | Pulse 1; CAN bus terminals (CANH, CANL) to GND2  | -100  | ٧    |

| V                  |                            | Pulse 2; CAN bus terminals (CANH, CANL) to GND2  | 75    | ٧    |

| V <sub>PULSE</sub> | CAN EMC test specification | Pulse 3a; CAN bus terminals (CANH, CANL) to GND2 | -150  | V    |

|                    |                            | Pulse 3b; CAN bus terminals (CANH, CANL) to GND2 | 100   | V    |

# 6.4 Recommended Operating Conditions

|                  |                                                          | MIN  | MAX  | UNIT |

|------------------|----------------------------------------------------------|------|------|------|

| V                | Supply Voltage, Side 1, 1.8-V operation                  | 1.71 | 1.89 | V    |

| V <sub>CC1</sub> | Supply Voltage, Side 1, 2.5-V, 3.3-V and 5.5-V operation | 2.25 | 5.5  | V    |

| V <sub>CC2</sub> | Supply Voltage, Side 2                                   | 4.5  | 5.5  | V    |

| T <sub>A</sub>   | Operating ambient temperature                            | -40  | 125  | °C   |

<sup>(2)</sup> All voltage values except differential I/O bus voltages are with respect to the local ground terminal (GND1 or GND2) and are peak voltage values.

<sup>(3)</sup> Maximum voltage must not exceed 6 V

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.5 Thermal Information

|                       |                                              | ISO       | ISO1042    |      |  |  |

|-----------------------|----------------------------------------------|-----------|------------|------|--|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | DW (SOIC) | DWV (SOIC) | UNIT |  |  |

|                       |                                              | 16 PINS   | 8 PINS     |      |  |  |

| R <sub>⊙JA</sub>      | Junction-to-ambient thermal resistance       | 69.9      | 100        | °C/W |  |  |

| R <sub>⊕JC(top)</sub> | Junction-to-case (top) thermal resistance    | 31.8      | 40.8       | °C/W |  |  |

| R <sub>⊕JB</sub>      | Junction-to-board thermal resistance         | 29.0      | 51.8       | °C/W |  |  |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 13.2      | 16.8       | °C/W |  |  |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 28.6      | 49.8       | °C/W |  |  |

| R <sub>⊕JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | -         | -          | °C/W |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.6 Power Ratings

|                 | PARAMETER                              | TEST CONDITIONS                                                                                                                                                                             | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| P <sub>D</sub>  | Maximum power dissipation (both sides) | See Figure 17, $V_{CC1} = V_{CC2} = 5.5$ V, $T_J = 150^{\circ}$ C, $R_L = 50$ $\Omega$ , A repetitive pattern on TXD with 1 ms time period, 990 $\mu$ s LOW time, and 10 $\mu$ s HIGH time. |     |     | 385 | mW   |

| P <sub>D1</sub> | Maximum power dissipation (side-1)     | See Figure 19, $V_{CC1} = V_{CC2} = 5.5$ V, $T_J = 150^{\circ}$ C, $R_L = 50$ $\Omega$ , Input a 2-V pk-pk 2.5-MHz 50% duty cycle differential square wave on CANH-CANL                     |     |     | 25  | mW   |

| P <sub>D2</sub> | Maximum power dissipation (side-2)     | See Figure 17, $V_{CC1} = V_{CC2} = 5.5$ V, $T_J = 150^{\circ}$ C, $R_L = 50$ $\Omega$ , A repetitive pattern on TXD with 1 ms time period, 990 $\mu$ s LOW time, and 10 $\mu$ s HIGH time. |     |     | 360 | mW   |

#### 6.7 Insulation Specifications

|                   | DADAMETED                                               | DAPAMETED TEST CONDITIONS                                                                                                                                                                                                                  |                    | SPECIFICATIONS     |                  |

|-------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------------------|

|                   | PARAMETER                                               | TEST CONDITIONS                                                                                                                                                                                                                            | DW-16              | DWV-8              | UNIT             |

| IEC 6066          | 64-1                                                    |                                                                                                                                                                                                                                            |                    | -                  |                  |

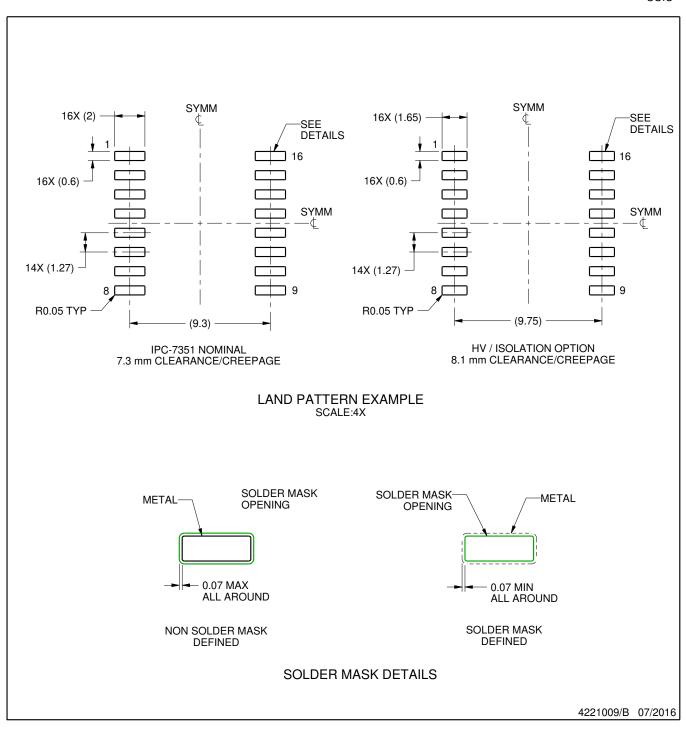

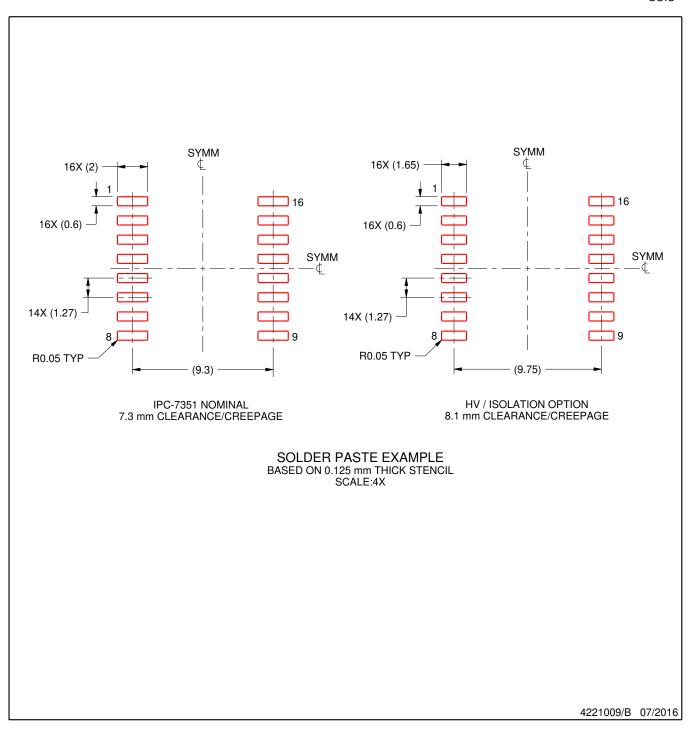

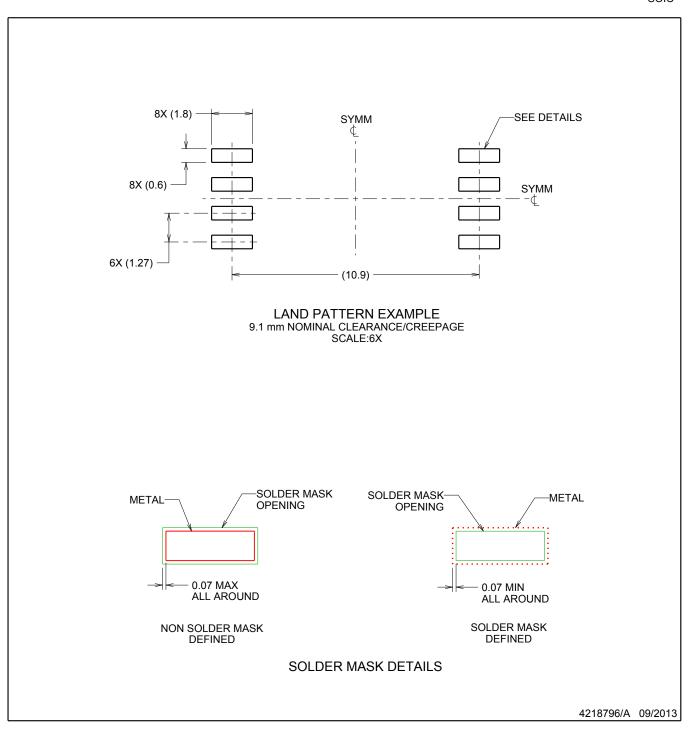

| CLR               | External clearance <sup>(1)</sup>                       | Side 1 to side 2 distance through air                                                                                                                                                                                                      | >8                 | >8.5               | mm               |

| CPG               | External Creepage <sup>(1)</sup>                        | Side 1 to side 2 distance across package surface                                                                                                                                                                                           | >8                 | >8.5               | mm               |

| DTI               | Distance through the insulation                         | Minimum internal gap (internal clearance)                                                                                                                                                                                                  | >17                | >17                | μm               |

| CTI               | Comparative tracking index                              | IEC 60112; UL 746A                                                                                                                                                                                                                         | >600               | >600               | V                |

|                   | Material Group                                          | According to IEC 60664-1                                                                                                                                                                                                                   | 1                  | I                  |                  |

|                   | Overvoltere esteren                                     | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                                                 | I-IV               | I-IV               |                  |

|                   | Overvoltage category                                    | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                                                                                | 1-111              | 1-111              |                  |

| DIN VDE           | V 0884-11:2017-01 <sup>(2)</sup>                        |                                                                                                                                                                                                                                            |                    |                    |                  |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage               | AC voltage (bipolar)                                                                                                                                                                                                                       | 1500               | 1500               | $V_{PK}$         |

| V <sub>IOWM</sub> | Maximum isolation working voltage                       | AC voltage (sine wave); time-dependent dielectric breakdown (TDDB) test;                                                                                                                                                                   | 1060               | 1060               | V <sub>RMS</sub> |

|                   |                                                         | DC voltage                                                                                                                                                                                                                                 | 1500               | 1500               | $V_{DC}$         |

| V <sub>IOTM</sub> | Maximum transient isolation voltage                     | $V_{TEST} = V_{IOTM}$ , t = 60 s (qualification); $V_{TEST}$ = 1.2 × $V_{IOTM}$ , t = 1 s (100% production)                                                                                                                                | 7071               | 7071               | V <sub>PK</sub>  |

| v                 | Maximum surge isolation voltage ISO1042 <sup>(3)</sup>  | Test method per IEC 62368-1, 1.2/50 $\mu$ s waveform, $V_{TEST}$ = 1.6 $\times$ $V_{IOSM}$ = 10000 $V_{PK}$ (qualification)                                                                                                                | 6250               | 6250               | $V_{PK}$         |

| $V_{IOSM}$        | Maximum surge isolation voltage ISO1042B <sup>(3)</sup> | Test method per IEC 62368-1, 1.2/50 $\mu$ s waveform, $V_{TEST} = 1.3 \times V_{IOSM} = 6000 V_{PK}$ (qualification)                                                                                                                       | 4615               | 4615               | $V_{PK}$         |

|                   |                                                         | Method a: After I/O safety test subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s; $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_{m} = 10$ s                                                                                                  | ≤ 5                | ≤ 5                |                  |

| q <sub>pd</sub>   | Apparent charge (4)                                     | Method a: After environmental tests subgroup 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60 \text{ s}$ ; ISO1042: $V_{pd(m)} = 1.6 \times V_{IORM}$ , $t_m = 10 \text{ s}$ ISO1042B: $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10 \text{ s}$     | ≤ 5                | ≤ 5                | рС               |

|                   |                                                         | Method b1: At routine test (100% production) and preconditioning (type test), $V_{ini} = V_{IOTM}$ , $t_{ini} = 1$ s; ISO1042: $V_{pd(m)} = 1.875 \times V_{IORM}$ , $t_m = 1$ s ISO1042B: $V_{pd(m)} = 1.5 \times V_{IORM}$ , $t_m = 1$ s | ≤ 5                | ≤ 5                |                  |

| C <sub>IO</sub>   | Barrier capacitance, input to output (5)                | $V_{IO} = 0.4 \times \sin (2 \pi ft), f = 1 MHz$                                                                                                                                                                                           | 1                  | 1                  | pF               |

|                   |                                                         | $V_{IO} = 500 \text{ V}, \ T_A = 25^{\circ}\text{C}$                                                                                                                                                                                       | > 10 <sup>12</sup> | > 10 <sup>12</sup> |                  |

| $R_{IO}$          | Insulation resistance, input to output (5)              | $V_{IO} = 500 \text{ V}, 100^{\circ}\text{C} \le T_{A} \le 150^{\circ}\text{C}$                                                                                                                                                            | > 10 <sup>11</sup> | > 10 <sup>11</sup> | Ω                |

|                   |                                                         | $V_{IO} = 500 \text{ V at } T_S = 150^{\circ}\text{C}$                                                                                                                                                                                     | > 10 <sup>9</sup>  | > 10 <sup>9</sup>  |                  |

|                   | Pollution degree                                        |                                                                                                                                                                                                                                            | 2                  | 2                  |                  |

|                   | Climatic category                                       |                                                                                                                                                                                                                                            | 40/125/<br>21      | 40/125/<br>21      |                  |

| UL 1577           |                                                         |                                                                                                                                                                                                                                            | •                  |                    |                  |

| V <sub>ISO</sub>  | Withstand isolation voltage                             | $V_{TEST} = V_{ISO}$ , $t = 60$ s (qualification); $V_{TEST} = 1.2 \times V_{ISO}$ , $t = 1$ s (100% production)                                                                                                                           | 5000               | 5000               | V <sub>RMS</sub> |

<sup>1)</sup> Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed circuit board are used to help increase these specifications.

<sup>(2)</sup> ISO1042 is suitable for *safe electrical insulation* and ISO1042B is suitable for *basic electrical insulation* only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

<sup>(3)</sup> Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

<sup>(4)</sup> Apparent charge is electrical discharge caused by a partial discharge (pd).

<sup>(5)</sup> All pins on each side of the barrier tied together creating a two-pin device.

### 6.8 Safety-Related Certifications

| VDE                                                                                                                                                                                                                                              | CSA                                                                                                                                                                                                                                          | UL                                                           | CQC                                                                                                      | TUV                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Certified according to DIN VDE V 0884-11:2017- 01                                                                                                                                                                                                | Certified according to IEC 60950-1, IEC 62368-1 and IEC 60601-1                                                                                                                                                                              | Recognized under UL<br>1577 Component<br>Recognition Program | Certified according to GB4943.1-2011                                                                     | Certified according to EN 61010-1:2010/A1:2019, EN 60950-1:2006/A2:2013 and EN 62368-1:2014                                 |

| Maximum transient isolation voltage, 7071 V <sub>PK</sub> ; Maximum repetitive peak isolation voltage, 1500 V <sub>PK</sub> ; Maximum surge isolation voltage, ISO1042: 6250 V <sub>PK</sub> (Reinforced) ISO1042B: 4615 V <sub>PK</sub> (Basic) | CSA 60950-1-07+A1+A2, IEC 60950-1 2 <sup>nd</sup> Ed.+A1+A2 and IEC 62368-1 2 <sup>nd</sup> Ed., for pollution degree 2, material group I ISO1042: 800 V <sub>RMS</sub> reinforced isolation ISO1042B: 1060 V <sub>RMS</sub> basic isolation | Single protection,<br>5000 V <sub>RMS</sub>                  | Reinforced insulation, Altitude ≤ 5000 m, Tropical Climate, 700 V <sub>RMS</sub> maximum working voltage | EN 61010-1:2010 /A1:2019 ISO1042: 600 V <sub>RMS</sub> reinforced isolation ISO1042B: 1000 V <sub>RMS</sub> basic isolation |

| Certificates:<br>Reinforced: 40040142<br>Basic: 40047657                                                                                                                                                                                         | Master contract number: 220991                                                                                                                                                                                                               | File number: E181974                                         | Certificate:<br>CQC15001121716 (DW-16)<br>CQC18001199096 (DWV-8)                                         | Client ID number: 77311                                                                                                     |

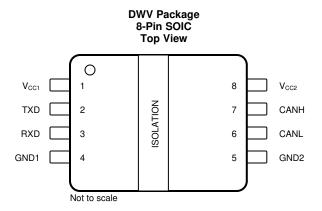

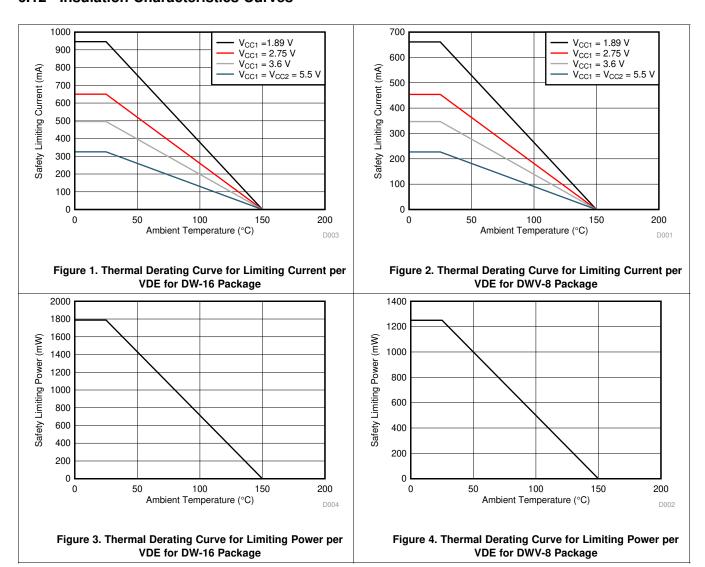

### 6.9 Safety Limiting Values

Safety limiting (1) intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry.

|                | PARAMETER                            | TEST CONDITIONS                                                                                                                               | MIN | TYP | MAX  | UNIT |

|----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| DW-1           | 6 PACKAGE                            |                                                                                                                                               |     |     |      |      |

|                |                                      | $R_{\theta JA} = 69.9^{\circ}\text{C/W}, V_I = 5.5 \text{ V}, T_J = 150^{\circ}\text{C}, T_A = 25^{\circ}\text{C}, \text{ see Figure 1}$      |     |     | 325  |      |

|                | Safety input, output, or supply      | $R_{\theta JA} = 69.9$ °C/W, $V_I = 3.6$ V, $T_J = 150$ °C, $T_A = 25$ °C, see Figure 1                                                       |     |     | 496  | ^    |

| I <sub>S</sub> | current                              | $R_{\theta JA} = 69.9^{\circ}C/W$ , $V_I = 2.75 \text{ V}$ , $T_J = 150^{\circ}C$ , $T_A = 25^{\circ}C$ , see Figure 1                        |     |     | 650  | mA   |

|                |                                      | $R_{\theta,JA} = 69.9^{\circ}C/W$ , $V_I = 1.89 \text{ V}$ , $T_J = 150^{\circ}C$ , $T_A = 25^{\circ}C$ , see Figure 1                        |     |     | 946  |      |

| Ps             | Safety input, output, or total power | R <sub>0JA</sub> = 69.9°C/W, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C, see Figure 3                                                      |     |     | 1788 | mW   |

| Ts             | Maximum safety temperature           |                                                                                                                                               |     |     | 150  | °C   |

| DWV            | -8 PACKAGE                           |                                                                                                                                               |     |     |      |      |

|                |                                      | $R_{\theta JA} = 100^{\circ}\text{C/W}, V_{I} = 5.5 \text{ V}, T_{J} = 150^{\circ}\text{C}, T_{A} = 25^{\circ}\text{C}, \text{ see Figure 2}$ |     |     | 227  |      |

|                | Safety input, output, or supply      | $R_{\theta JA} = 100^{\circ}\text{C/W}, V_{I} = 3.6 \text{ V}, T_{J} = 150^{\circ}\text{C}, T_{A} = 25^{\circ}\text{C}, \text{ see Figure 2}$ |     |     | 347  | ^    |

| IS             | current                              | $R_{\theta JA} = 100^{\circ}\text{C/W}, V_I = 2.75 \text{ V}, T_J = 150^{\circ}\text{C}, T_A = 25^{\circ}\text{C}, \text{ see Figure 2}$      |     |     | 454  | mA   |

|                |                                      | $R_{\theta JA} = 100^{\circ}\text{C/W}, V_I = 1.89 \text{ V}, T_J = 150^{\circ}\text{C}, T_A = 25^{\circ}\text{C}, \text{ see Figure 2}$      |     |     | 661  |      |

| Ps             | Safety input, output, or total power | $R_{\theta JA} = 100$ °C/W, $T_J = 150$ °C, $T_A = 25$ °C, see Figure 4                                                                       |     |     | 1250 | mW   |

| T <sub>S</sub> | Maximum safety temperature           |                                                                                                                                               |     |     | 150  | °C   |

<sup>(1)</sup> The maximum safety temperature,  $T_S$ , has the same value as the maximum junction temperature,  $T_J$ , specified for the device. The  $I_S$ and  $P_S$  parameters represent the safety current and safety power respectively. The maximum limits of  $I_S$  and  $P_S$  should not be exceeded. These limits vary with the ambient temperature, TA.

The junction-to-air thermal resistance,  $R_{\theta JA}$ , in the table is that of a device installed on a high-K test board for leaded surface-mount packages. Use these equations to calculate the value for each parameter:

Submit Documentation Feedback

Copyright © 2017-2020, Texas Instruments Incorporated

$T_J = T_A + R_{\theta JA} \times P$ , where P is the power dissipated in the device.

$T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$ , where  $T_{J(max)}$  is the maximum allowed junction temperature.  $P_S = I_S \times V_I$ , where  $V_I$  is the maximum input voltage.

# 6.10 Electrical Characteristics - DC Specification

Over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER                                                    | TEST CONDITIONS                                                                                  | MIN                  | TYP           | MAX                  | UNIT |

|----------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------|---------------|----------------------|------|

| SUPPLY               | CHARACTERISTICS                                              |                                                                                                  |                      |               |                      |      |

|                      |                                                              | $V_{CC1}$ =1.71 V to 1.89 V, TXD = 0 V, bus dominant                                             |                      | 2.3           | 3.5                  | mA   |

| loor                 | Supply current Side 1                                        | $V_{CC1} = 2.25 \text{ V to } 5.5 \text{ V, TXD} = 0 \text{ V, bus}$ dominant                    |                      | 2.4           | 3.5                  | mA   |

| I <sub>CC1</sub>     | Supply current Side 1                                        | $V_{CC1}$ = 1.71 V to 1.89 V, TXD = $V_{CC1}$ , bus recessive                                    |                      | 1.2           | 2.1                  | mA   |

|                      |                                                              | $V_{CC1}$ = 2.25 V to 5.5 V, TXD = $V_{CC1}$ , bus recessive                                     |                      | 1.3           | 2.1                  | mA   |

|                      | Cumply ourrent Cide 2                                        | TXD = 0 V, bus dominant, $R_L$ = 60 $\Omega$                                                     |                      | 43            | 73.4                 | mA   |

| I <sub>CC2</sub>     | Supply current Side 2                                        | TXD = $V_{CC1}$ , bus recessive, $R_L$ = 60 $\Omega$                                             |                      | 2.8           | 4.1                  | mA   |

| UV <sub>VCC1</sub>   | Rising under voltage detection, Side 1                       |                                                                                                  |                      |               | 1.7                  | V    |

| UV <sub>VCC1</sub>   | Falling under voltage detection, Side 1                      |                                                                                                  | 1.0                  |               |                      | V    |

| V <sub>HYS(UVC</sub> | Hysterisis voltage on V <sub>CC1</sub> undervoltage lock-out |                                                                                                  | 75                   | 125           |                      | mV   |

| UV <sub>VCC2</sub>   | Rising under voltage detection, side 2                       |                                                                                                  |                      | 4.2           | 4.45                 | V    |

| UV <sub>VCC2</sub>   | Falling under voltage detection, side 2                      |                                                                                                  | 3.8                  | 4.0           | 4.25                 | V    |

| V <sub>HYS(UVC</sub> | Hysterisis voltage on V <sub>CC2</sub> undervoltage lock-out |                                                                                                  |                      | 200           |                      | mV   |

| TXD TERI             | MINAL                                                        |                                                                                                  |                      |               |                      |      |

| V <sub>IH</sub>      | High level input voltage                                     |                                                                                                  | 0.7×V <sub>CC1</sub> |               |                      | V    |

| V <sub>IL</sub>      | Low level input voltage                                      |                                                                                                  |                      | (             | 0.3×V <sub>CC1</sub> | V    |

| I <sub>IH</sub>      | High level input leakage current                             | TXD = V <sub>CC1</sub>                                                                           |                      |               | 1                    | uA   |

| I <sub>IL</sub>      | Low level input leakage current                              | TXD = 0V                                                                                         | -20                  |               |                      | uA   |

| C <sub>I</sub>       | Input capacitance                                            | VIN = 0.4 x $\sin(2 \times \pi \times 1E+6 \times t) + 2.5 \text{ V},$<br>V <sub>CC1</sub> = 5 V |                      | 3             |                      | pF   |

| RXD TER              | MINAL                                                        |                                                                                                  | Į.                   |               |                      |      |

|                      |                                                              | See Figure 18, $I_O = -4$ mA for 4.5 V $\leq$ $V_{CC1} \leq 5.5$ V                               | -0.4                 | -0.2          |                      | V    |

| V <sub>OH</sub> -    | High level output voltage                                    | See Figure 18, $I_O = -2$ mA for 3.0 V $\leq$ $V_{CC1} \leq$ 3.6 V                               | -0.2                 | -0.07         |                      | V    |

| V <sub>CC1</sub>     | High level output voltage                                    | See Figure 18, $I_O = -1$ mA for 2.25 V $\leq$ $V_{CC1} \leq$ 2.75 V                             | -0.1                 | -0.04         |                      | V    |

|                      |                                                              | See Figure 18, $I_O = -1$ mA for 1.71 V $\leq$ $V_{CC1} \leq$ 1.89 V                             | -0.1                 | -0.045        |                      | V    |

|                      |                                                              | See Figure 18, $I_O = 4$ mA for 4.5 V $\leq$ $V_{CC1} \leq$ 5.5 V                                |                      | 0.2           | 0.4                  | V    |

| V                    | Low level output veltage                                     | See Figure 18, $I_O = 2$ mA for 3.0 V $\leq$ $V_{CC1} \leq$ 3.6 V                                |                      | 0.07          | 0.2                  | V    |

| V <sub>OL</sub>      | Low level output voltage                                     | See Figure 18, $I_O = 1$ mA for 2.25 V $\leq$ $V_{CC1} \leq$ 2.75 V                              |                      | 0.035         | 0.1                  | V    |

|                      |                                                              | See Figure 18, $I_O = 1$ mA for 1.71 V $\leq$ $V_{CC1} \leq$ 1.89 V                              |                      | 0.04          | 0.1                  | V    |

| DRIVER E             | ELECTRICAL CHARACTERISTICS                                   |                                                                                                  |                      |               |                      |      |

| Va. = -:             | Bus output voltage(Dominant), CANH                           | See Figure 15 and Figure 16, TXD = 0 V, $50 \Omega \le R_L \le 65 \Omega$ , $C_L = open$         | 2.75                 |               | 4.5                  | V    |

| V <sub>O(DOM)</sub>  | Bus output voltage(Dominant), CANL                           | See Figure 15 and Figure 16, TXD = 0 V, $50 \Omega \le R_L \le 65 \Omega$ , $C_L = open$         | 0.5                  |               | 2.25                 | V    |

| $V_{O(REC)}$         | Bus output voltage(recessive), CANH and CANL                 | See Figure 15 and Figure 16, TXD = $V_{CC1}$ , $R_L$ = open                                      | 2.0                  | 0.5 x<br>VCC2 | 3.0                  | V    |

Copyright @ 2017–2020, Texas Instruments Incorporated

# **Electrical Characteristics - DC Specification (continued)**

Over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                                                                             | TEST CONDITIONS                                                                           | MIN    | TYP  | MAX      | UNIT |

|-----------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------|------|----------|------|

|                       | Differential output voltage, CANH-CANL (dominant)                                     | See Figure 15 and Figure 16, TXD = 0 V, $45 \Omega \le R_L \le 50 \Omega$ , $C_L = open$  | 1.4    |      | 3.0      | V    |

| $V_{OD(DOM)}$         | Differential output voltage, CANH-CANL (dominant)                                     | See Figure 15 and Figure 16, TXD = 0 V, $50 \Omega \le R_L \le 65 \Omega$ , $C_L = open$  | 1.5    |      | 3.0      | V    |

|                       | Differential output voltage, CANH-CANL (dominant)                                     | See Figure 15 and Figure 16, TXD = 0 V, $R_L = 2240 \Omega$ , $C_L = open$                | 1.5    |      | 5.0      | V    |

| V                     | Differential output voltage, CANH-CANL (recessive)                                    | See Figure 15 and Figure 16, TXD = $V_{CC1}$ , $R_L = 60 \Omega$ , $C_L = open$           | -120.0 |      | 12.0     | mV   |

| $V_{OD(REC)}$         | Differential output voltage, CANH-CANL (recessive)                                    | See Figure 15 and Figure 16, TXD = $V_{CC1}$ , $R_L$ = open, $C_L$ = open                 | -50.0  |      | 50.0     | mV   |

| V <sub>SYM_DC</sub>   | DC Output symmetry (V <sub>CC2</sub> - V <sub>O(CANH)</sub> - V <sub>O(CANL)</sub> )  | See Figure 15 and Figure 16, $R_L$ = 60 $\Omega$ , $C_L$ = open, TXD = $V_{CC1}$ or 0 $V$ | -400.0 |      | 400.0    | mV   |

| I <sub>SO(SS DO</sub> | Short circuit current steady state output                                             | See Figure 23, VCANH = -5 V to 40 V, CANL = open, TXD = 0 V                               | -100.0 |      |          | mA   |

| M)                    | current, dominant                                                                     | See Figure 23, VCANL = -5 V to 40 V,<br>CANH = open, TXD = 0 V                            |        |      | 100.0    | mA   |

| I <sub>SO(SS_RE</sub> | Short circuit current steady state output current, recessive                          | See Figure 23, -27 V ≤ VBUS ≤ 32 V,<br>VBUS = CANH = CANL, TXD = V <sub>CC1</sub>         | -5.0   |      | 5.0      | mA   |

| RECEIVE               | R ELECTRICAL CHARACTERISTICS                                                          |                                                                                           |        |      | <u>.</u> |      |

|                       | Differential input threshold voltage                                                  | See Figure 18 and Table 1,  VCM  ≤ 20 V                                                   | 500.0  |      | 900.0    |      |

| V <sub>IT</sub>       | Differential input threshold voltage                                                  | See Figure 18 and Table 1, 20 V ≤  VCM  ≤ 30 V                                            | 400.0  |      | 1000.0   | mV   |

| V <sub>HYS</sub>      | Hysteresis voltage for differential input threshold                                   | See Figure 18 and Table 1                                                                 |        | 120  |          |      |

| V <sub>CM</sub>       | Input common mode range                                                               | See Figure 18 and Table 1                                                                 | -30.0  |      | 30.0     | V    |

| I <sub>OFF(LKG)</sub> | Power-off bus input leakage current                                                   | CANH = CANL = 5 V, $V_{CC2}$ to GND via 0 $\Omega$ and 47 $k\Omega$ resistor              |        |      | 4.8      | uA   |

| C <sub>I</sub>        | Input capacitance to ground (CANH or CANL)                                            | TXD = V <sub>CC1</sub>                                                                    |        | 24.0 | 30       | pF   |

| C <sub>ID</sub>       | Differential input capacitance (CANH-CANL)                                            | TXD = V <sub>CC1</sub>                                                                    |        | 12.0 | 15       | pF   |

| R <sub>ID</sub>       | Differential input resistance                                                         | TXD = V <sub>CC1</sub> ; -30 V ≤ VCM ≤ +30 V                                              | 30.0   |      | 80.0     | kΩ   |

| R <sub>IN</sub>       | Input resistance (CANH or CANL)                                                       | TXD = V <sub>CC1</sub> ; -30 V ≤ VCM ≤ +30 V                                              | 15.0   |      | 40.0     | kΩ   |

| R <sub>IN(M)</sub>    | Input resistance matching: (1 - R <sub>IN(CANH)</sub> /R <sub>IN(CANL)</sub> ) x 100% | V <sub>CANH</sub> = V <sub>CANL</sub> = 5 V                                               | -2.0   |      | 2.0      | %    |

| THERMAI               | L SHUTDOWN                                                                            |                                                                                           |        |      | <u>.</u> |      |

| T <sub>TSD</sub>      | Thermal shutdown temperature                                                          |                                                                                           |        | 170  |          | °C   |

| T <sub>TSD_HYS</sub>  | Thermal shutdown hysteresis                                                           |                                                                                           |        | 5    |          | °C   |

# 6.11 Switching Characteristics

Over recommended operating conditions (unless otherwise noted)

|                               | PARAMETER                                                                                                 | TEST CONDITIONS                                                                                                                                                         | MIN   | TYP | MAX   | UNIT  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| DEVICE                        | SWITCHING CHARACTERISTICS                                                                                 | 1201 201121110110                                                                                                                                                       | -3444 |     |       |       |

| DEVICE                        |                                                                                                           | Can Figure 20 B                                                                                                                                                         |       |     |       |       |

| t <sub>PROP(LO</sub>          | Total loop delay, driver input TXD to                                                                     | See Figure 20, $R_L = 60 \Omega$ , $C_L = 100 pF$ , $C_{L(RXD)} = 15 pF$ ; input rise/fall time (10% to 90%) on TXD =1 ns; 1.71 V $\leq$ $V_{CC1} \leq 1.89 V$          | 70    | 125 | 198.0 | ns    |

| OP1)                          | receiver RXD, recessive to dominant                                                                       | See Figure 20, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF; input rise/fall time (10% to 90%) on TXD =1 ns; 2.25 V ≤ $V_{CC1}$ ≤ 5.5 V                   | 70    | 122 | 192.0 | ns    |

| t <sub>PROP(LO</sub>          | Total loop delay, driver input TXD to                                                                     | See Figure 20, $R_L = 60 \Omega$ , $C_L = 100 pF$ , $C_{L(RXD)} = 15 pF$ ; input rise/fall time (10% to 90%) on TXD =1 ns; 1.71 V $\leq$ V <sub>CC1</sub> $\leq$ 1.89 V | 70    | 155 | 215.0 | ns    |

| OP2)                          | receiver RXD, dominant to recessive                                                                       | See Figure 20, $R_L = 60 \Omega$ , $C_L = 100 pF$ , $C_{L(RXD)} = 15 pF$ ; input rise/fall time (10% to 90%) on TXD =1 ns; 2.25 V ≤ $V_{CC1} \le 5.5 V$                 | 70    | 152 | 215.0 | ns    |

| t <sub>UV_RE_E</sub><br>NABLE | Re-enable time after Undervoltage event                                                                   | Time for device to return to normal operation from V <sub>CC1</sub> or V <sub>CC2</sub> under voltage event                                                             |       |     | 300.0 | μs    |

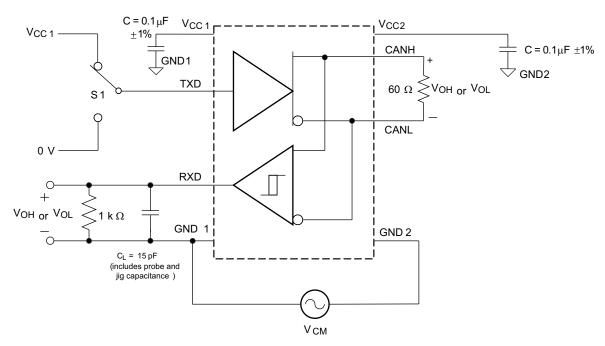

| CMTI                          | Common mode transient immunity                                                                            | V <sub>CM</sub> = 1200 V <sub>PK</sub> , See Figure 24                                                                                                                  | 85    | 100 |       | kV/μs |

| DRIVER S                      | SWITCHING CHARACTERISTICS                                                                                 |                                                                                                                                                                         |       |     |       |       |

| t <sub>pHR</sub>              | Propagation delay time, HIGH TXD to driver recessive                                                      |                                                                                                                                                                         |       | 76  | 120   |       |

| t <sub>pLD</sub>              | Propagation delay time, LOW TXD to driver dominant                                                        | See Figure 17, $R_L = 60 \Omega$ and $C_L = 100$ pF; input rise/fall time (10% to 90%) on                                                                               |       | 61  | 120   | ns    |

| t <sub>sk(p)</sub>            | Pulse skew ( tpHR - tpLD )                                                                                | TXD =1 ns                                                                                                                                                               |       | 14  |       | 113   |

| t <sub>R</sub>                | Differential output signal rise time                                                                      |                                                                                                                                                                         |       | 45  |       |       |

| t <sub>F</sub>                | Differential output signal fall time                                                                      |                                                                                                                                                                         |       | 45  |       |       |

| $V_{SYM}$                     | Output symmetry (dominant or recessive) (V <sub>O(CANH)</sub> + V <sub>O(CANL)</sub> ) / V <sub>CC2</sub> | See Figure 17 and Figure 31 , $R_{TERM}$ = $60~\Omega$ , $C_{SPLIT}$ = 4.7 nF, $C_L$ = open, $R_L$ = open, TXD = 250 kHz, 1 MHz                                         | 0.9   |     | 1.1   | V/V   |

| t <sub>TXD DTO</sub>          | Dominant time out                                                                                         | See Figure 22, $R_L = 60 \Omega$ and $C_L = open$                                                                                                                       | 1.2   |     | 3.8   | ms    |

| RECEIVE                       | R SWITCHING CHARACTERISTICS                                                                               |                                                                                                                                                                         |       |     |       |       |

| t <sub>pRH</sub>              | Propagation delay time, bus recessive input to RXD high output                                            |                                                                                                                                                                         |       | 75  | 130   | ns    |

| t <sub>pDL</sub>              | Propogation delay time, bus dominant input to RXD low output                                              | See Figure 19, C <sub>L(RXD)</sub> = 15 pF                                                                                                                              |       | 63  | 130   | ns    |

| $t_R$                         | Output signal rise time(RXD)                                                                              |                                                                                                                                                                         |       | 1.4 |       | ns    |

| t <sub>F</sub>                | Output signal fall time(RXD)                                                                              |                                                                                                                                                                         |       | 1.8 |       | ns    |

| FD TIMIN                      | G PARAMETERS                                                                                              |                                                                                                                                                                         |       |     |       |       |

| +                             | Bit time on CAN bus output pins with $t_{BIT(TXD)} = 500 \text{ ns}$                                      | butput pins with See Figure 21, $R_L = 60 \Omega$ , $C_L = 100 pF$ , $C_{L(RXD)} = 15 pF$ ; input rise/fall time (10% to 90%) on TXD =1 ns                              |       |     | 530.0 | ns    |

| t <sub>BIT(BUS)</sub>         | Bit time on CAN bus output pins with $t_{BIT(TXD)} = 200 \text{ ns}$                                      | See Figure 21, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF; input rise/fall time (10% to 90%) on TXD =1 ns                                               | 155.0 |     | 210.0 | ns    |

| t                             | Bit time on RXD output pins with t <sub>BIT(TXD)</sub> = 500 ns                                           | See Figure 21, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF; input rise/fall time (10% to 90%) on TXD =1 ns                                               | 400   |     | 550.0 | ns    |

| <sup>t</sup> BIT(RXD)         | Bit time on RXD output pins with t <sub>BIT(TXD)</sub> = 200 ns                                           | See Figure 21, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF; input rise/fall time (10% to 90%) on TXD =1 ns                                               | 120.0 |     | 220.0 | ns    |

### **Switching Characteristics (continued)**

Over recommended operating conditions (unless otherwise noted)

|       | PARAMETER                                                     | TEST CONDITIONS                                                                                                                                                            | MIN   | TYP MAX | UNIT |

|-------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|------|

| ΔtREC | Receiver timing symmetry with $t_{BIT(TXD)} = 500 \text{ ns}$ | See Figure 21, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF; input rise/fall time (10% to 90%) on TXD =1 ns; $\Delta tREC = t_{BIT(RXD)}$ - $t_{BIT(BUS)}$   | -65.0 | 40.0    | ns   |

| ΔίΝΕΟ | Receiver timing symmetry with $t_{BIT(TXD)} = 200 \text{ ns}$ | See Figure 21, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF; input rise/fall time (10% to 90%) on TXD =1 ns; $\Delta tREC$ = $t_{BIT(RXD)}$ - $t_{BIT(BUS)}$ | -45.0 | 15.0    | ns   |

### 6.12 Insulation Characteristics Curves

Submit Documentation Feedback

Copyright © 2017–2020, Texas Instruments Incorporated

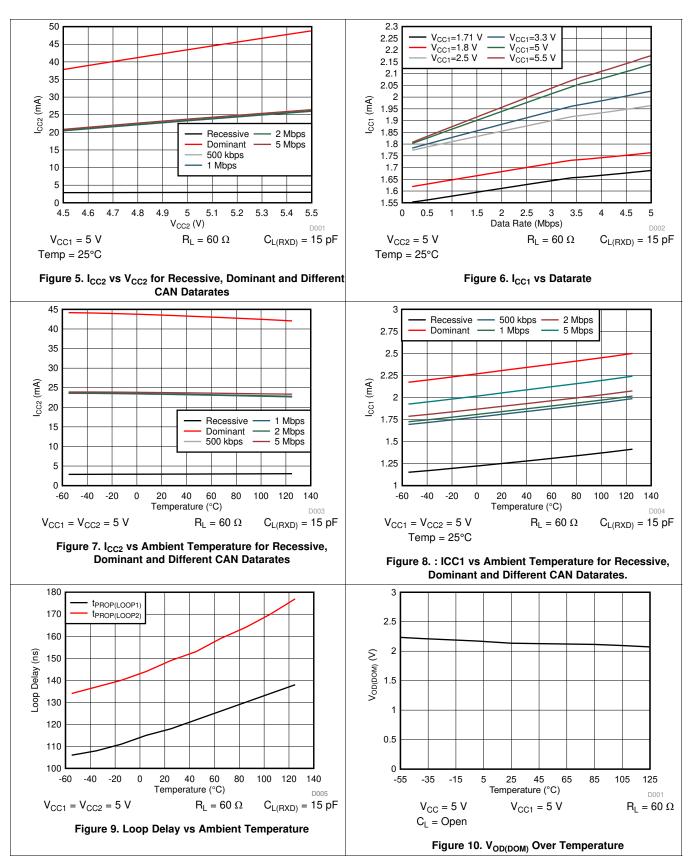

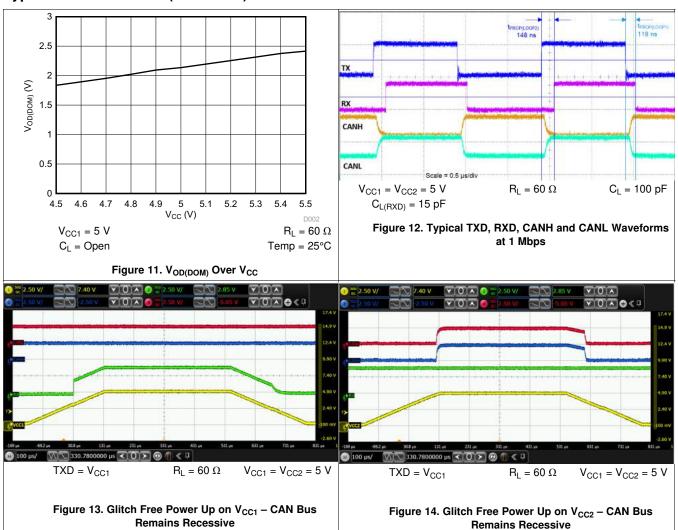

### 6.13 Typical Characteristics

### **Typical Characteristics (continued)**

### 7 Parameter Measurement Information

#### 7.1 Test Circuits

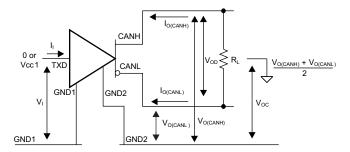

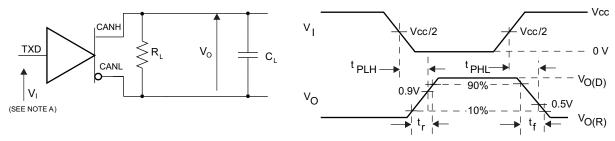

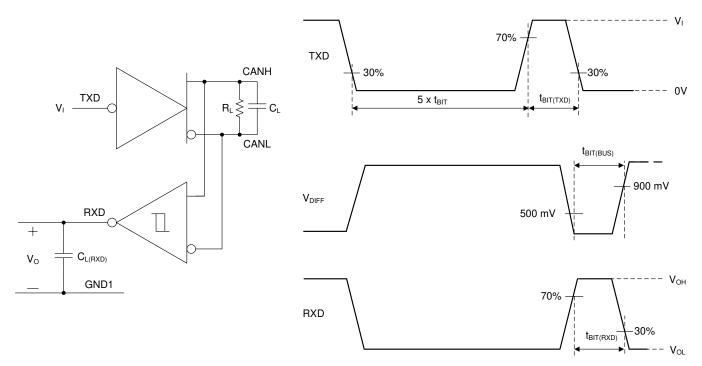

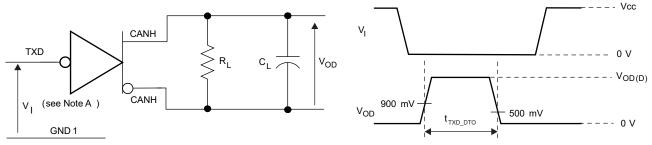

Figure 15. Driver Voltage, Current and Test Definitions

Figure 16. Bus Logic State Voltage Definitions

A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  125 kHz, 50% duty cycle,  $t_f \leq$  6 ns,  $t_f \leq$  6 ns,  $t_G \leq$  50  $\Omega$ .

Figure 17. Driver Test Circuit and Voltage Waveforms

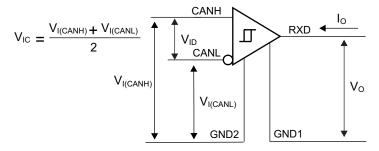

Figure 18. Receiver Voltage and Current Definitions

Copyright © 2017–2020, Texas Instruments Incorporated

### **Test Circuits (continued)**

A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  125 kHz, 50% duty cycle,  $t_r \leq$  6 ns,  $t_f \leq$  6 ns,  $t_G =$  50  $\Omega$ .

Figure 19. Receiver Test Circuit and Voltage Waveforms

Table 1. Receiver Differential Input Voltage Threshold Test

|                   | INPUT             | OUT             | <b>TPUT</b> |                 |

|-------------------|-------------------|-----------------|-------------|-----------------|

| V <sub>CANH</sub> | V <sub>CANL</sub> | V <sub>ID</sub> | RXD         |                 |

| -29.5 V           | -30.5 V           | 1000 mV         | L           |                 |

| 30.5 V            | 29.5 V            | 1000 mV         | L           | V               |

| -19.55 V          | -20.45 V          | 900 mV          | L           | V <sub>OL</sub> |

| 20.45 V           | 19.55 V           | 900 mV          | L           |                 |

| -19.75 V          | -20.25 V          | 500 mV          | Н           |                 |

| 20.25 V           | 19.75 V           | 500 mV          | Н           |                 |

| -29.8 V           | -30.2 V           | 400 mV          | Н           | V <sub>OH</sub> |

| 30.2 V            | 29.8 V            | 400 mV          | Н           |                 |

| Open              | Open              | Х               | Н           |                 |

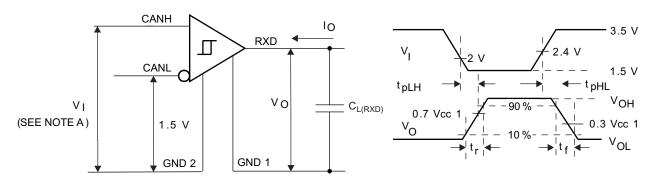

Figure 20. t<sub>LOOP</sub> Test Circuit and Voltage Waveforms

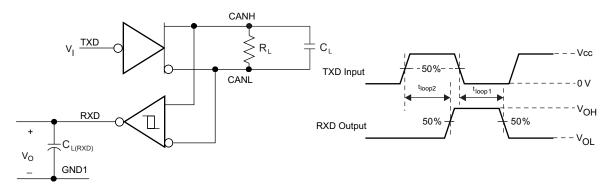

Figure 21. CAN FD Timing Parameter Measurement

A. The input pulse is supplied by a generator having the following characteristics:  $t_r \le 6$  ns,  $t_f \le 6$  ns,  $t_O = 50$   $\Omega$ .

Figure 22. Dominant Time-out Test Circuit and Voltage Waveforms

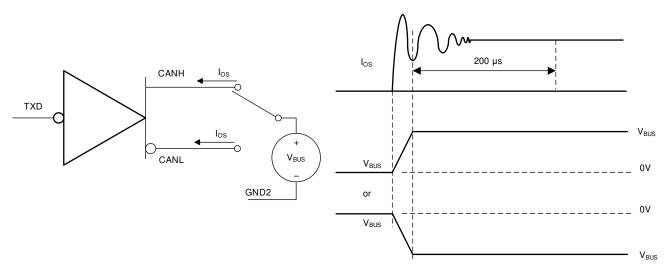

Figure 23. Driver Short-Circuit Current Test Circuit and Waveforms

Figure 24. Common-Mode Transient Immunity Test Circuit

### 8 Detailed Description

#### 8.1 Overview

The ISO1042 device is a digitally isolated CAN transceiver that offers ±70-V DC bus fault protection and ±30-V common-mode voltage range. The device supports up to 5-Mbps data rate in CAN FD mode allowing much faster transfer of payload compared to classic CAN. The ISO1042 device has an isolation withstand voltage of 5000 V<sub>RMS</sub> and is available in basic and reinforced isolation with a surge test voltage of 6 kV<sub>PK</sub> and 10 kV<sub>PK</sub> respectively. The device can operate from 1.8-V, 2.5-V, 3.3-V, and 5-V supplies on side 1 and a 5-V supply on side 2. This supply range is of particular advantage for applications operating in harsh industrial environments because the low voltage on side 1 enables the connection to low-voltage microcontrollers for power conservation, whereas the 5 V on side 2 maintains a high signal-to-noise ratio of the bus signals.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

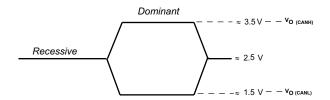

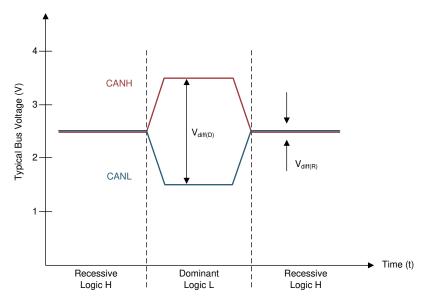

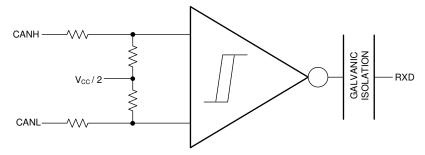

#### 8.3.1 CAN Bus States

The CAN bus has two states during operation: dominant and recessive. A dominant bus state, equivalent to logic low, is when the bus is driven differentially by a driver. A recessive bus state is when the bus is biased to a common mode of  $V_{CC}$  / 2 through the high-resistance internal input resistors of the receiver, equivalent to a logic high. The host microprocessor of the CAN node uses the TXD pin to drive the bus and receives data from the bus on the RXD pin. See Figure 25 and Figure 26.

#### **Feature Description (continued)**

Figure 25. Bus States (Physical Bit Representation)

Figure 26. Simplified Recessive Common Mode Bias and Receiver

#### 8.3.2 Digital Inputs and Outputs: TXD (Input) and RXD (Output)

The  $V_{CC1}$  supply for the isolated digital input and output side of the device can be supplied by 1.8-V, 2.5-V, 3.3-V, and 5-V supplies and therefore the digital inputs and outputs are 1.8-V, 2.5-V, 3.3-V, and 5-V compatible.

#### NOTE

The TXD pin is very weakly internally pulled up to  $V_{\text{CC1}}$ . An external pullup resistor should be used to make sure that the TXD pin is biased to recessive (high) level to avoid issues on the bus if the microprocessor does not control the pin and the TXD pin floats. The TXD pullup strength and CAN bit timing require special consideration when the device is used with an open-drain TXD output on the CAN controller of the microprocessor. An adequate external pullup resistor must be used to make sure that the TXD output of the microprocessor maintains adequate bit timing input to the input on the transceiver.

#### Feature Description (continued)

#### 8.3.3 Protection Features

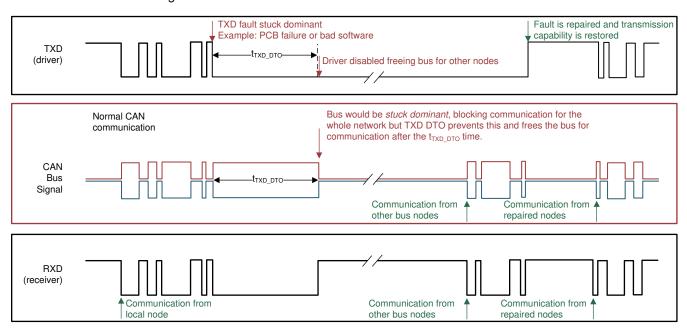

#### 8.3.3.1 TXD Dominant Timeout (DTO)

The TXD DTO circuit prevents the transceiver from blocking network communication in the event of a hardware or software failure where the TXD pin is held dominant longer than the timeout period, t<sub>TXD DTO</sub>. The DTO circuit timer starts on a falling edge on the TXD pin. The DTO circuit disables the CAN bus driver if no rising edge occurs before the timeout period expires, which frees the bus for communication between other nodes on the network. The CAN driver is activated again when a recessive signal occurs on the TXD pin, clearing the TXD DTO condition. The receiver and RXD pin still reflect activity on the CAN bus, and the bus terminals are biased to the recessive level during a TXD dominant timeout.

Figure 27. Example Timing Diagram for TXD DTO

#### **NOTE**

The minimum dominant TXD time (t<sub>TXD DTO</sub>) allowed by the TXD DTO circuit limits the minimum possible transmitted data rate of the device. The CAN protocol allows a maximum of eleven successive dominant bits (on TXD) for the worst case, where five successive dominant bits are followed immediately by an error frame. This, along with the t<sub>TXD DTO</sub> minimum, limits the minimum data rate. Calculate the minimum transmitted data rate with Equation 1.

(1) Minimum Data Rate = 11 / t<sub>TXD DTO</sub>

#### 8.3.3.2 Thermal Shutdown (TSD)

Copyright © 2017-2020, Texas Instruments Incorporated

If the junction temperature of the device exceeds the thermal shutdown threshold (T<sub>TSD</sub>), the device turns off the CAN driver circuits, blocking the TXD-to-bus transmission path. The CAN bus terminals are biased to the recessive level during a thermal shutdown, and the receiver-to-RXD path remains operational. The shutdown condition is cleared when the junction temperature drops at least the thermal shutdown hysteresis temperature  $(T_{TSD, HYST})$  below the thermal shutdown temperature  $(T_{TSD})$  of the device.

#### **Feature Description (continued)**

#### 8.3.3.3 Undervoltage Lockout and Default State

The supply pins have undervoltage detection that places the device in protected or default mode which protects the bus during an undervoltage event on the  $V_{CC1}$  or  $V_{CC2}$  supply pins. If the bus-side power supply,  $V_{CC2}$ , is less than about 4 V, the power shutdown circuits in the ISO1042 device disable the transceiver to prevent false transmissions because of an unstable supply. If the  $V_{CC1}$  supply is still active when this occurs, the receiver output (RXD) goes to a default HIGH (recessive) value. Table 2 summarizes the undervoltage lockout and fail-safe behavior.

Table 2. Undervoltage Lockout and Default State

| V <sub>CC1</sub>      | V <sub>CC2</sub>     | DEVICE STATE | BUS OUTPUT               | RXD                      |

|-----------------------|----------------------|--------------|--------------------------|--------------------------|

| > UV <sub>VCC1</sub>  | > UV <sub>VCC2</sub> | Functional   | Per Device State and TXD | Mirrors Bus              |

| <uv<sub>VCC1</uv<sub> | > UV <sub>VCC2</sub> | Protected    | Recessive                | Undetermined             |

| >UV <sub>VCC1</sub>   | < UV <sub>VCC2</sub> | Protected    | High Impedance           | Recessive (Default High) |

#### **NOTE**

After an undervoltage condition is cleared and the supplies have returned to valid levels, the device typically resumes normal operation in  $300 \mu s$ .

#### 8.3.3.4 Floating Pins

Pullup and pulldown resistors should be used on critical pins to place the device into known states if the pins float. The TXD pin should be pulled up through a resistor to the  $V_{\text{CC1}}$  pin to force a recessive input level if the microprocessor output to the pin floats.

#### 8.3.3.5 Unpowered Device

The device is designed to be *ideal passive* or *no load* to the CAN bus if it is unpowered. The bus pins (CANH, CANL) have extremely low leakage currents when the device is unpowered to avoid loading down the bus which is critical if some nodes of the network are unpowered while the rest of the of network remains in operation.

#### 8.3.3.6 CAN Bus Short Circuit Current Limiting

The device has two protection features that limit the short circuit current when a CAN bus line has a short-circuit fault condition. The first protection feature is driver current limiting (both dominant and recessive states) and the second feature is TXD dominant state time out to prevent permanent higher short circuit current of the dominant state during a system fault. During CAN communication the bus switches between dominant and recessive states, therefore the short circuit current may be viewed either as the instantaneous current during each bus state or as an average current of the two states. For system current (power supply) and power considerations in the termination resistors and common-mode choke ratings, use the average short circuit current. Determine the ratio of dominant and recessive bits by the data in the CAN frame plus the following factors of the protocol and PHY that force either recessive or dominant at certain times:

- Control fields with set bits

- Bit stuffing

- Interframe space

- TXD dominant time out (fault case limiting)

These factors ensure a minimum recessive amount of time on the bus even if the data field contains a high percentage of dominant bits. The short circuit current of the bus depends on the ratio of recessive to dominant bits and their respective short circuit currents. Use Equation 2 to calculate the average short circuit current.

$I_{OS(AVG)} = \text{\%Transmit} \times [(\text{\%REC\_Bits} \times I_{OS(SS)\_REC}) + (\text{\%DOM\_Bits} \times I_{OS(SS)\_DOM})] + [\text{\%Receive} \times I_{OS(SS)\_REC}]$

#### where

- I<sub>OS(AVG)</sub> is the average short circuit current

- %Transmit is the percentage the node is transmitting CAN messages

- %Receive is the percentage the node is receiving CAN messages

- %REC Bits is the percentage of recessive bits in the transmitted CAN messages

- %DOM Bits is the percentage of dominant bits in the transmitted CAN messages

- $I_{\text{OS(SS)}}$   $_{\text{REC}}$  is the recessive steady state short circuit current

- $I_{\text{OS(SS)}}$  DOM is the dominant steady state short circuit current

(2)

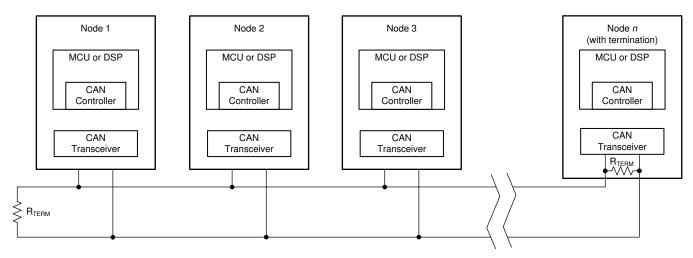

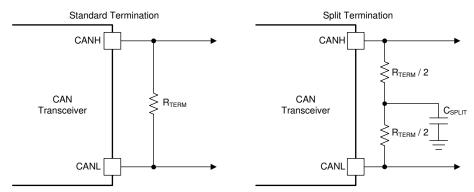

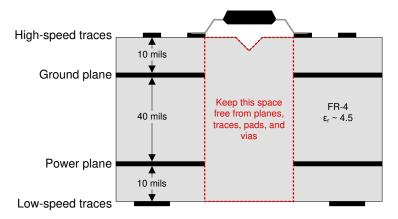

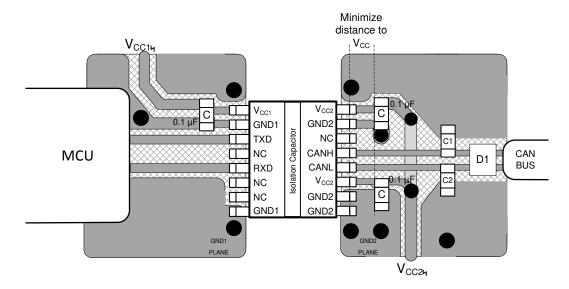

#### **NOTE**