## 650V SuperGaN™ FET in TO-247 (source tab)

### **Description**

The TP65H015G5WS 650V, 15 m $\Omega$  gallium nitride GaN FET is a normally-off device using Transphorm's Gen V platform. It combines a state-of-the-art high voltage GaN HEMT with a low voltage silicon MOSFET to offer superior reliability and performance.

The Gen V SuperGaN™ platform uses advanced epi and patented design technologies to simplify manufacturability while improving efficiency over silicon via lower gate charge, output capacitance, crossover loss, and reverse recovery charge.

#### Related Literature

- ANOOO9: Recommended External Circuitry for GaN FETs

- ANOOO3: Printed Circuit Board Layout and Probing

- ANOO10: Paralleling GaN FETs

### **Ordering Information**

| Part Number  | Package       | Package<br>Configuration |

|--------------|---------------|--------------------------|

| TP65H015G5WS | 3 lead T0-247 | Source                   |

#### **TP65H015G5WS T0-247** (top view)

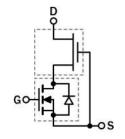

**Cascode Schematic Symbol**

**Cascode Device Structure**

#### **Features**

- JEDEC qualified GaN technology

- Dynamic R<sub>DS(on)eff</sub> production tested

- Robust design, defined by

- Intrinsic lifetime tests

- Wide gate safety margin

- Transient over-voltage capability

- Very low Q<sub>RR</sub>

- Reduced crossover loss

#### **Benefits**

- Enables AC-DC bridgeless totem-pole PFC designs

- Increased power density

- Reduced system size and weight

- Overall lower system cost

- Achieves increased efficiency in both hard- and softswitched circuits

- · Easy to drive with commonly-used gate drivers

- GSD pin layout improves high speed design

### **Applications**

- Datacom

- Broad industrial

- PV inverter

- · Servo motor

| Key Specifications                       |     |  |

|------------------------------------------|-----|--|

| V <sub>DSS</sub> (V)                     | 650 |  |

| V <sub>(TR)DSS</sub> (V)                 | 725 |  |

| $R_{DS(on)eff}(m\Omega)\;max^{m{\star}}$ | 18  |  |

| Q <sub>RR</sub> (nC) typ                 | 430 |  |

| Q <sub>G</sub> (nC) typ                  | 74  |  |

<sup>\*</sup> Dynamic on-resistance; see Figures 18 and 19

## **Absolute Maximum Ratings** (T<sub>c</sub>=25 °C unless otherwise stated.)

| Symbol               | Parameter                                         |                                          | Limit Value | Unit |

|----------------------|---------------------------------------------------|------------------------------------------|-------------|------|

| V <sub>DSS</sub>     | Drain to source voltage (T <sub>J</sub> = -       | 55°C to 150°C)                           | 650         |      |

| V <sub>(TR)DSS</sub> | Transient drain to source voltage a               |                                          | 725         | V    |

| V <sub>GSS</sub>     | Gate to source voltage                            |                                          | ±20         |      |

| P <sub>D</sub>       | Maximum power dissipation @                       | ©Tc=25°C                                 | 266         | W    |

|                      | Continuous drain current @T <sub>C</sub> =25°C b  |                                          | 93          | А    |

| I <sub>D</sub>       | Continuous drain current @T <sub>C</sub> =100°C b |                                          | 59          | А    |

| I <sub>DM</sub>      | Pulsed drain current (pulse wi                    | Pulsed drain current (pulse width: 10µs) |             | A    |

| T <sub>C</sub>       | Operating temperature                             | Case                                     | -55 to +150 | °C   |

| TJ                   | Operating temperature                             | Junction                                 | -55 to +150 | °C   |

| Ts                   | Storage temperature                               |                                          | -55 to +150 | °C   |

| Tsold                | Soldering peak temperature <sup>c</sup>           |                                          | 260         | °C   |

#### Notes:

- a. In off-state, spike duty cycle D<0.01, spike duration <1µs

- b. For increased stability at high current operation, see Circuit Implementation on page 3

- c. For 10 sec., 1.6mm from the case

### **Thermal Resistance**

| Symbol           | Parameter           | Typical | Unit |

|------------------|---------------------|---------|------|

| Rejc             | Junction-to-case    | 0.47    | °C/W |

| R <sub>OJA</sub> | Junction-to-ambient | 40      | °C/W |

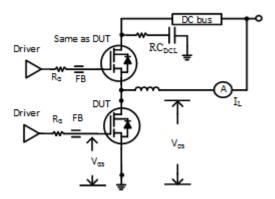

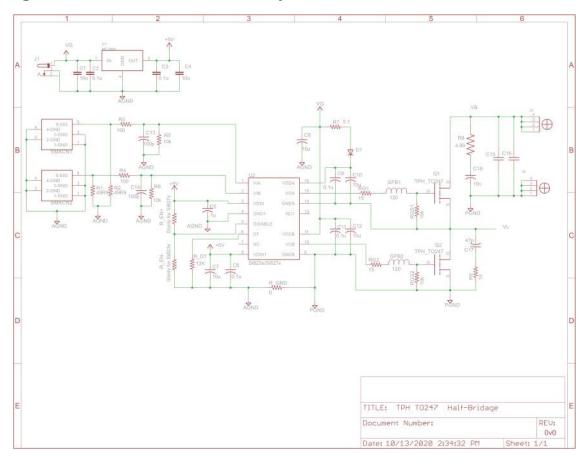

### **Circuit Implementation**

Layout Recommendations: (See also ANOOO9) Gate Loop:

- Gate Driver: SiLab Si823x/Si827x

- Keep gate loop compact

- Minimize coupling with power loop

Power loop: (For reference see page 13)

- Minimize power loop path inductance

- Minimize switching node coupling with high and low power plane

- Add DC bus snubber to reduce to voltage ringing

- Add Switching node snubber for high current operation

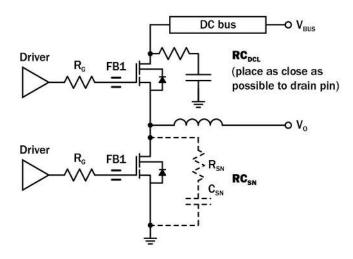

Simplified Half-bridge Schematic (See also on Figure 13)

Recommended gate drive: (OV, 12V) with R<sub>G</sub>=15 $\Omega$

| Gate Ferrite Bead (FB1) | Required DC Link RC Snubber (RC <sub>DCL</sub> ) <sup>a</sup> | Recommended Switching Node<br>RC Snubber (RC <sub>SN</sub> ) <sup>b,c</sup> |

|-------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------|

| 80-120 Ω at 100MHz      | [10nF + 3.3 Ω] x 3                                            | Not necessary                                                               |

#### Notes:

- a. RCDCL should be placed as close as possible to the drain pin

- $RC_{SN}$  is needed only if  $R_G$  is smaller than recommendations or operational current exceeds 100C rated  $I_{DMAX}$ b.

- If required, please use (100 pF + 10 ohm) or parallel two or three of the same

### **Electrical Parameters** (T<sub>J</sub>=25 °C unless otherwise stated)

| Symbol                         | Parameter                              | Min | Тур  | Max  | Unit | Test Conditions                                                                               |  |

|--------------------------------|----------------------------------------|-----|------|------|------|-----------------------------------------------------------------------------------------------|--|

| Forward Device Characteristics |                                        |     |      |      |      |                                                                                               |  |

| $V_{(BL)DSS}$                  | Drain-source voltage                   | 650 | _    | _    | V    | V <sub>GS</sub> =0V                                                                           |  |

| $V_{\text{GS(th)}}$            | Gate threshold voltage                 | 3.3 | 4    | 4.8  | V    | V <sub>DS</sub> =V <sub>GS</sub> , I <sub>D</sub> =2mA                                        |  |

| D                              | Drain-source on-resistance a           | _   | 15   | 18   | m.O. | V <sub>GS</sub> =10V, I <sub>D</sub> =60A                                                     |  |

| R <sub>DS(on)eff</sub>         | Diam-source off-resistance             | _   | 31   | _    | - mΩ | V <sub>GS</sub> =10V, I <sub>D</sub> =60A, T <sub>J</sub> =150°C                              |  |

|                                | Drain to course leakage current        | _   | 7    | 70   |      | V <sub>DS</sub> =650V, V <sub>GS</sub> =0V                                                    |  |

| I <sub>DSS</sub>               | Drain-to-source leakage current        | _   | 50   | _    | - μA | V <sub>DS</sub> =650V, V <sub>GS</sub> =0V, T <sub>J</sub> =150°C                             |  |

|                                | Gate-to-source forward leakage current | _   | _    | 400  | 0    | V <sub>GS</sub> =20V                                                                          |  |

| $I_{GSS}$                      | Gate-to-source reverse leakage current | _   | _    | -400 | - nA | V <sub>GS</sub> =-20V                                                                         |  |

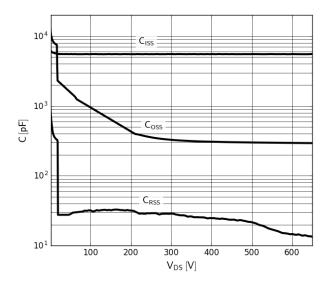

| C <sub>ISS</sub>               | Input capacitance                      | _   | 5218 | _    |      |                                                                                               |  |

| Coss                           | Output capacitance                     | _   | 307  | _    | pF   | V <sub>GS</sub> =0V, V <sub>DS</sub> =400V, <i>f</i> =1MHz                                    |  |

| $C_{RSS}$                      | Reverse transfer capacitance           | _   | 26   | _    |      |                                                                                               |  |

| $C_{\text{O(er)}}$             | Output capacitance, energy related b   | _   | 476  | _    | pF   | V <sub>GS</sub> =0V, V <sub>DS</sub> =0V to 400V                                              |  |

| $C_{O(tr)}$                    | Output capacitance, time related c     | _   | 1026 | _    | Pi   |                                                                                               |  |

| $Q_{G}$                        | Total gate charge                      | _   | 74   | 100  |      | V <sub>DS</sub> =400V, V <sub>GS</sub> =0V to 10V,<br>I <sub>D</sub> =60A                     |  |

| Q <sub>GS</sub>                | Gate-source charge                     | _   | 34   | _    | nC   |                                                                                               |  |

| $Q_{GD}$                       | Gate-drain charge                      | _   | 21   | _    |      |                                                                                               |  |

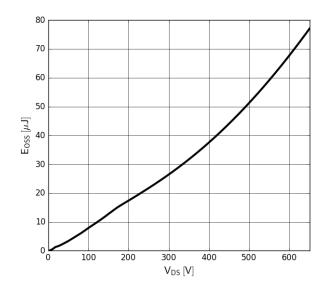

| Qoss                           | Output charge                          | _   | 430  | _    | nC   | V <sub>GS</sub> =0V, V <sub>DS</sub> =0V to 400V                                              |  |

| t <sub>D(on)</sub>             | Turn-on delay                          | _   | 87   | _    |      |                                                                                               |  |

| t <sub>R</sub>                 | Rise time                              | _   | 18   | _    | ns   | $V_{DS}$ =400V, $V_{GS}$ =0V to 12V, $R_{G}$ =15 $\Omega$ , $Z_{FB}$ =120 $\Omega$ at 100MHz, |  |

| $t_{\text{D(off)}}$            | Turn-off delay                         | _   | 123  | _    |      | I <sub>D</sub> =60A                                                                           |  |

| t <sub>F</sub>                 | Fall time                              | _   | 9.4  | _    |      |                                                                                               |  |

#### Notes:

Dynamic on-resistance; see Figures 18 and 19 for test circuit and conditions

Equivalent capacitance to give same stored energy as  $V_{\text{\scriptsize DS}}$  rises from 0V to 400V b.

Equivalent capacitance to give same charging time as  $V_{DS}$  rises from OV to 400V

## **Electrical Parameters** (T<sub>J</sub>=25 °C unless otherwise stated)

| Symbol                | Parameter                      | Min | Тур | Max  | Unit | Test Conditions                                               |  |

|-----------------------|--------------------------------|-----|-----|------|------|---------------------------------------------------------------|--|

| Reverse Dev           | Reverse Device Characteristics |     |     |      |      |                                                               |  |

| Is                    | Reverse current                | _   | _   | 60   | А    | V <sub>GS</sub> =0V, T <sub>C</sub> =100°C<br>≤15% duty cycle |  |

| V                     | Reverse voltage <sup>a</sup>   | _   | 1.6 | _    | V    | V <sub>GS</sub> =0V, I <sub>S</sub> =60A                      |  |

| $V_{SD}$              |                                | _   | 1.2 | _    |      | V <sub>GS</sub> =0V, I <sub>S</sub> =30A                      |  |

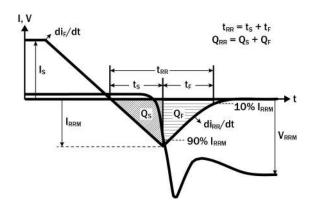

| t <sub>RR</sub>       | Reverse recovery time          | _   | 100 | _    | ns   | I <sub>S</sub> =60A, V <sub>DD</sub> =400V,<br>di/dt=1000A/μs |  |

| Q <sub>RR</sub>       | Reverse recovery charge        | _   | 430 | _    | nC   |                                                               |  |

| (di/dt) <sub>RM</sub> | Reverse diode di/dt b          | _   | _   | 3500 | A/µs | Circuit implementation and parameters on page 3               |  |

#### Notes:

a. Includes dynamic R<sub>DS(on)</sub> effect

b. Reverse conduction di/dt will not exceed this max value with recommended R<sub>G</sub>.

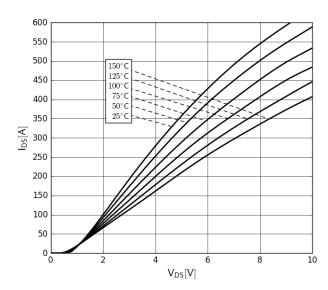

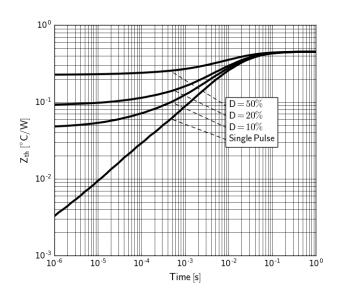

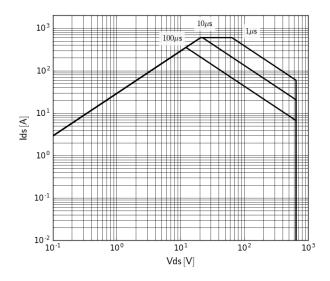

### **Typical Characteristics** (T<sub>C</sub>=25 °C unless otherwise stated)

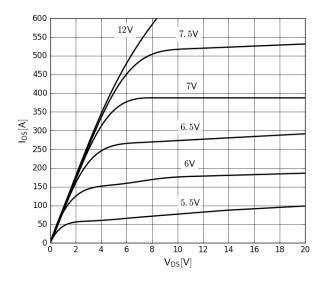

Figure 1. Typical Output Characteristics T<sub>J</sub>=25 °C

Parameter: V<sub>GS</sub>

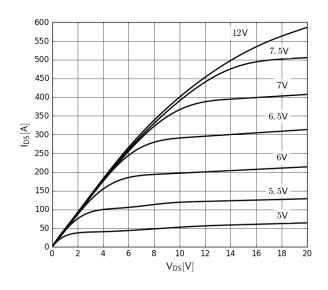

Figure 2. Typical Output Characteristics T<sub>J</sub>=150 °C

Parameter: V<sub>GS</sub>

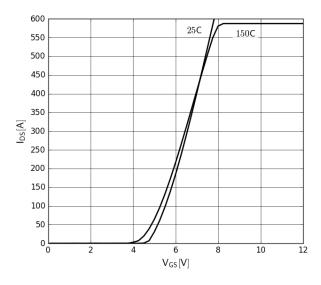

Figure 3. Typical Transfer Characteristics

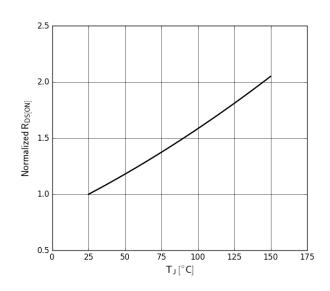

Figure 4. Normalized On-resistance  $I_D=60A,\ V_{GS}=8V$

V<sub>DS</sub>=20V, parameter: T<sub>J</sub>

## **Typical Characteristics** (T<sub>C</sub>=25 °C unless otherwise stated)

Figure 5. Typical Capacitance  $V_{GS}$ =0V, f=1MHz

Figure 6. Typical Coss Stored Energy

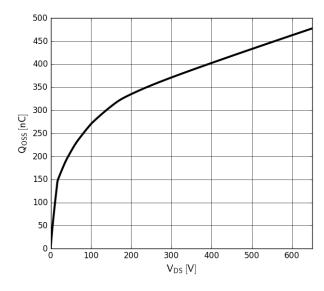

Figure 7. Typical Qoss

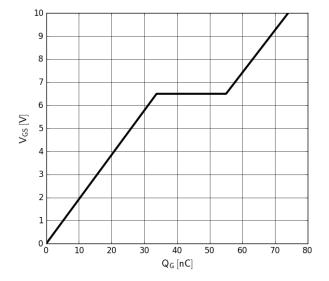

Figure 8. Typical Gate Charge I<sub>DS</sub>=60A, V<sub>DS</sub>=400V

### **Typical Characteristics** (T<sub>C</sub>=25 °C unless otherwise stated)

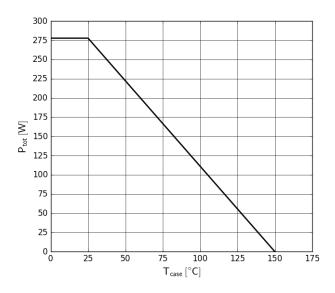

Figure 9. Power Dissipation

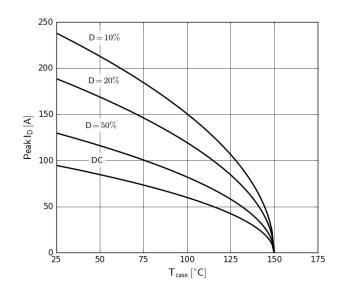

Figure 10. Current Derating Pulse width  $\leq 10\mu s$ ,  $V_{GS} \geq 10V$

Figure 11. Forward Characteristics of Rev. Diode  $I_S {=} f(V_{SD}), \ parameter; \ T_J$

Figure 12. Transient Thermal Resistance

# **Typical Characteristics** ( $T_C$ =25 $^{\circ}$ C unless otherwise stated)

Figure 13. Safe Operating Area T<sub>C</sub>=25 °C

### **Test Circuits and Waveforms**

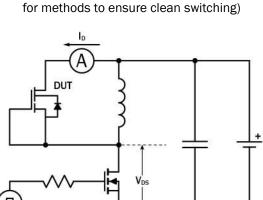

Figure 14. Switching Time Test Circuit (see circuit implementation on page 3 for methods to ensure clean switching)

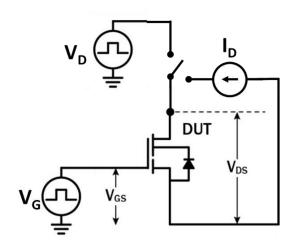

Figure 16. Diode Characteristics Test Circuit

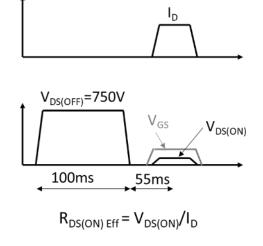

Figure 18. Dynamic R<sub>DS(on)eff</sub> Test Circuit

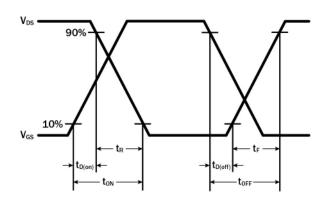

Figure 15. Switching Time Waveform

Figure 17. Diode Recovery Waveform

Figure 19. Dynamic R<sub>DS(on)eff</sub> Waveform

### **Design Considerations**

The fast switching of GaN devices reduces current-voltage crossover losses and enables high frequency operation while simultaneously achieving high efficiency. However, taking full advantage of the fast switching characteristics of GaN switches requires adherence to specific PCB layout guidelines and probing techniques.

Before evaluating Transphorm GaN devices, see application note <u>Printed Circuit Board Layout and Probing for GaN Power Switches</u>. The table below provides some practical rules that should be followed during the evaluation.

### When Evaluating Transphorm GaN Devices:

| DO                                                                                                          | DO NOT                                                             |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Minimize circuit inductance by keeping traces short, both in the drive and power loop                       | Twist the pins of T0-220 or T0-247 to accommodate GDS board layout |

| Minimize lead length of T0-220 and T0-247 package when mounting to the PCB                                  | Use long traces in drive circuit, long lead length of the devices  |

| Use shortest sense loop for probing; attach the probe and its ground connection directly to the test points | Use differential mode probe or probe ground clip with long wire    |

| See AN0003: Printed Circuit Board Layout and Probing                                                        |                                                                    |

### **GaN Design Resources**

The complete technical library of GaN design tools can be found at <a href="mailto:transphormusa.com/design">transphormusa.com/design</a>:

- Evaluation kits

- Application notes

- · Design guides

- · Simulation models

- Technical papers and presentations

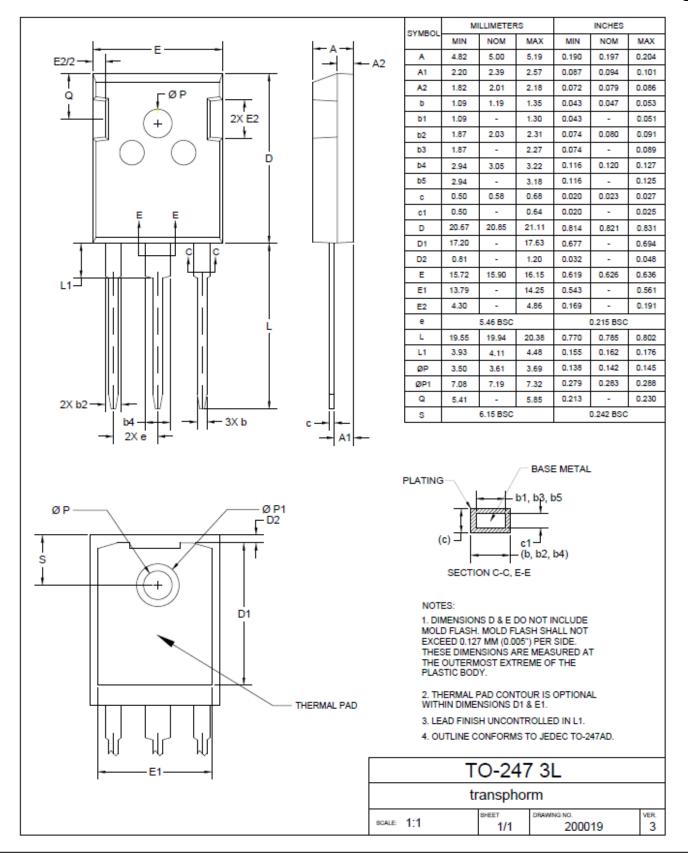

#### Mechanical

### 3 Lead TO-247 Package

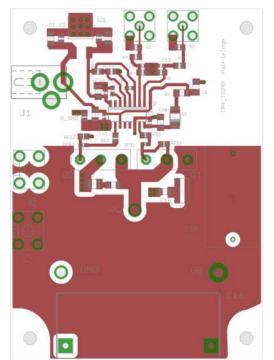

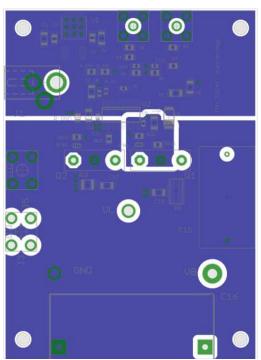

## Half-bridge Reference Schematic and PCB Layout

Half-bridge layout Sample (Top Layer)

Half-bridge layout Sample (Bottom Layer)

# **Revision History**

| Version | Date       | Change(s)                                   |  |

|---------|------------|---------------------------------------------|--|

| 0.1     | 5/25/2020  | Preliminary Datasheet                       |  |

| 0.2     | 9/24/2020  | Preliminary Datasheet                       |  |

| 0.2     | 02/23/2021 | Preliminary Datasheet. Update Figure 18, 19 |  |

| 1.0     | 07/12/2021 | Datasheet complete                          |  |