# InnoMux Family of ICs

# 2 Constant Voltage and 4 Channel Dimming LED Backlight CC Controller

# **Product Highlights**

#### CV and 4-Channel LED Backlight Controller

- Eliminates buck and LED backlight boost converters

- One or two constant voltage outputs

- Independently regulated outputs with instantaneous transient response  $\pm 5\%$  CV on 0%-100%-0% load step

- Typical output voltages

- One CV mode: 5 V to 22 V

- Two CV mode: 5 V and 12 V to 22 V

- 1-4 string LED backlight

- 3% matching accuracy for LED strings

- Analog, PWM, sequenced PWM and filtered PWM operation

- Up to 100 V string voltage / up to 960 mA total string current

- Up to 2:1 LED string voltage range

#### Advanced Protection / Safety Features

- · Individual overload protection for all outputs

- String imbalanced / short / open protection

- Output overvoltage set for auto-restart

#### **Convenient Packages**

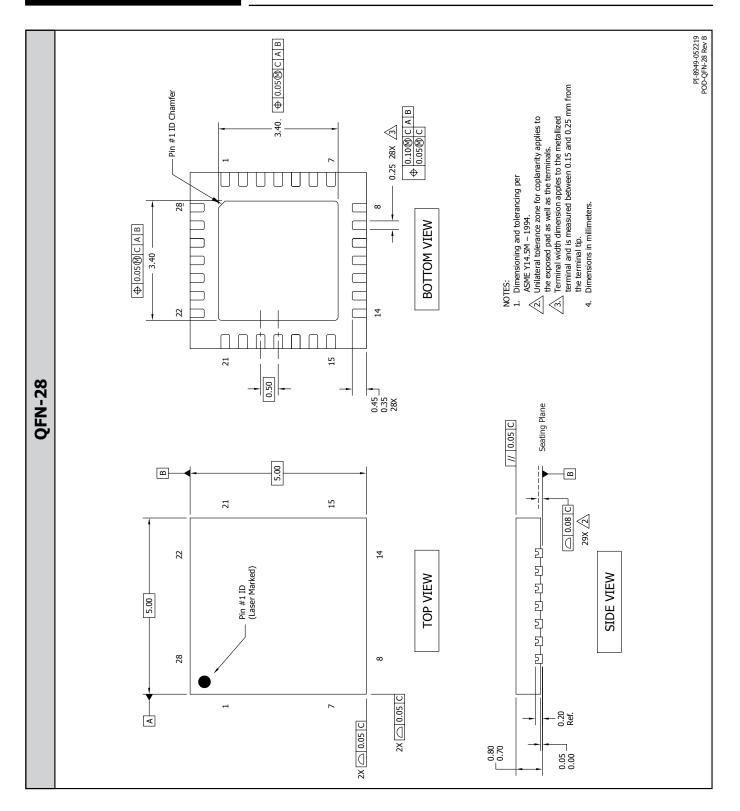

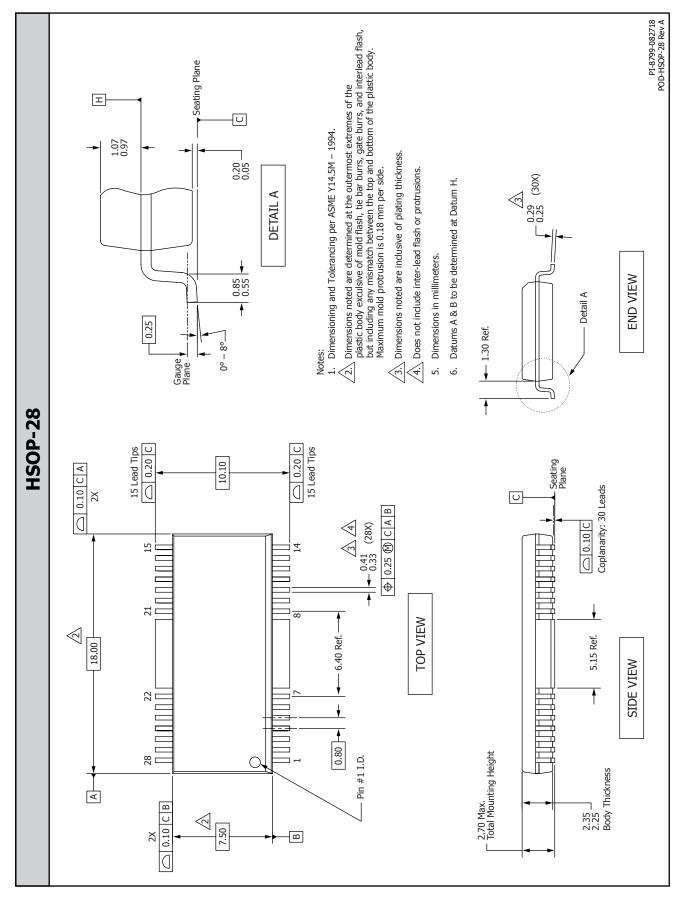

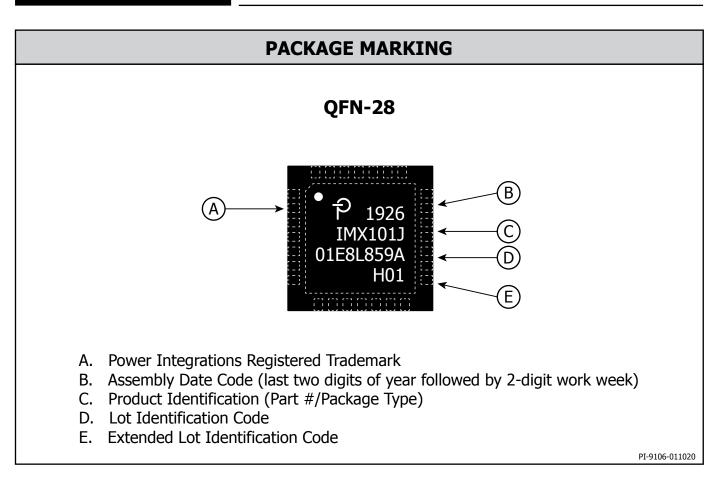

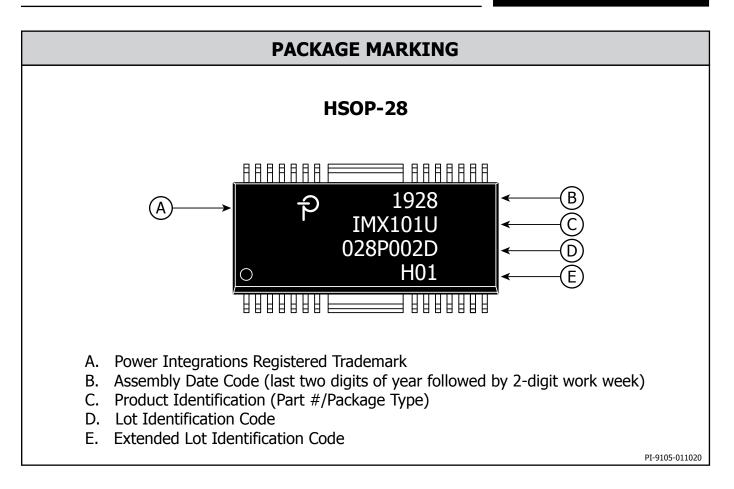

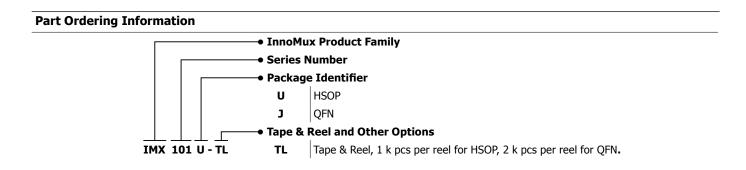

28-Lead HSOP for single-sided wave soldered PCBs or small 28-Lead QFN (5x5 mm Body) for compact multilayer designs

#### Applications

• ENERGY STAR 8, CEC, and 2021/2023 EU labeling for monitors and TVs

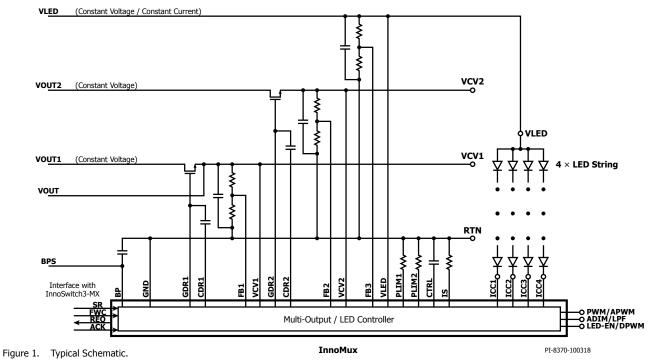

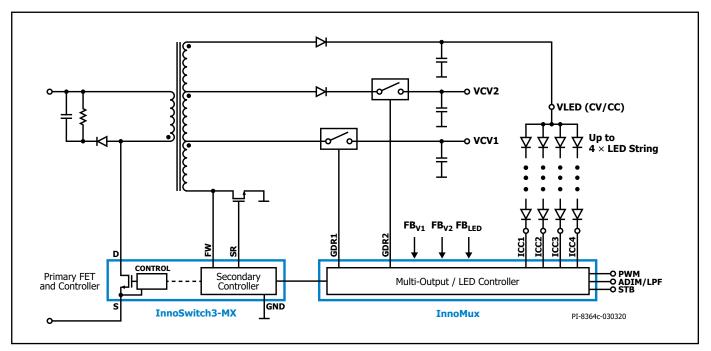

#### Description

When paired with InnoSwitch3-MX, InnoMux dramatically improves the system efficiency of monitors and TVs by eliminating the boost and buck converter stages using a single-stage flyback topology. This enables very high system efficiency up to 91%, on a small PCB footprint.

The LED backlight control offers excellent minimum threshold regulation as well as analog and several PWM dimming options. The sequenced PWM dimming option further improves visual performance and stabilizes power demand. Extensive protection features are provided.

# Real March

Figure 2. Left – InnoMux in QFN-28, Reflow Process. Right – InnoMux in HSOP-28, Wave Solder Process.

| InnoMux |                      |         |

|---------|----------------------|---------|

| Product | Output Configuration | Package |

| IMX101J | 1 CV, 1 LED string   | QFN     |

| IMX101U | 1 CV, 1 LED string   | HSOP    |

| IMX111U | 2 CV, 1 LED string   | HSOP    |

| IMX111J | 2 CV, 1 LED string   | QFN     |

| IMX102U | 1 CV, 4 LED strings  | HSOP    |

| IMX112U | 2 CV, 4 LED strings  | HSOP    |

Table 1. InnoMux Controller Part Numbers.

# InnoMux

# **Pin Functional Description**

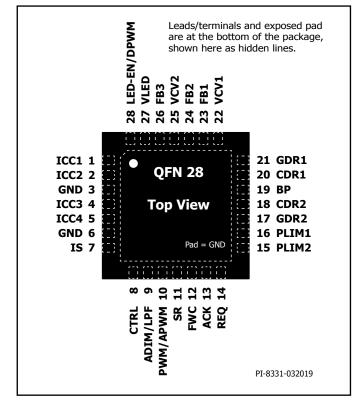

#### QFN-28 InnoMux Controller

**CHANNEL 1 (ICC1) Pin (Pin 1)** LED current regulation channel 1.

CHANNEL 2 (ICC2) Pin (Pin 2) LED current regulation channel 2.

GROUND (GND) Pin (Pin 3)

Pin 3 must be connected to the exposed pad and the secondary ground.

**CHANNEL 3 (ICC3) Pin (Pin 4)** LED current regulation channel 3.

**CHANNEL 4 (ICC4) Pin (Pin 5)** LED current regulation channel 4.

**GROUND (GND) Pin (Pin 6)** Pin 6 must be connected to the exposed pad and the secondary ground.

**SET LED CURRENT (IS) Pin (Pin 7)** Current setting for LED string current.

**CONTROL (CTRL) Pin (Pin 8)** Output to control capacitor.

ANALOG DIMMING (ADIM/LPF) Pin (Pin 9) Analog dimming/low pass filter connection.

**PWM DIMMING (PWM/APWM) Pin (Pin 10)** PWM input.

**SYNCHRONOUS RECTIFIER (SR) Pin (Pin 11)** SR signal from InnoSwitch3-MX.

**FORWARD COMPARATOR (FWC) Pin (Pin 12)** FW comparator signal from InnoSwitch3-MX.

ACKNOWLEDGE (ACK) Pin (Pin 13) ACK signal from InnoSwitch3-MX.

**REQUEST (REQ) Pin (Pin 14)** REQ output to InnoSwitch3-MX.

**POWER LIMIT 2 (PLIM2) Pin (Pin 15)** Set power limit for VLED/VCV2.

**POWER LIMIT 1 (PLIM1) Pin (Pin 16)** Set power limit for VCV1/VCV2.

**GATE DRIVE 2 (GDR2) Pin (Pin 17)** Selection MOSFET gate driver for CV2.

CAPACITOR (CDR2) Pin (Pin 18) Capacitor for GDR2.

**BYPASS (BP) Pin (Pin 19)** BP/VDD regulator output. Also supplies InnoSwitch3-MX.

CAPACITOR (CDR1) Pin (Pin 20) Capacitor for GDR1.

Figure 5. InnoMux QFN-28 Controller Pin Configuration.

**GATE DRIVE 1 (GDR1) Pin (Pin 21)** Selection MOSFET gate driver for CV1.

**OUTPUT VOLTAGE (VCV1) Pin (Pin 22)** Output voltage connection for CV1 selection MOSFET drive.

**FEEDBACK 1 (FB1) Pin (Pin 23)** Feedback input for VCV1 output voltage.

**FEEDBACK 2 (FB2) Pin (Pin 24)** Feedback input for VCV2 output voltage.

**OUTPUT VOLTAGE (VCV2) Pin (Pin 25)** Output voltage connection for BP regulator and for CV2 selection MOSFET drive.

**FEEDBACK 3 (FB3) Pin (Pin 26)** Feedback input for VLED output voltage.

**OUTPUT VOLTAGE (VLED) Pin (Pin 27)** Output voltage connection for BP regulator.

**LED-EN/DPWM Pin (Pin 28)** LED enable/digital PWM input.

# InnoMux

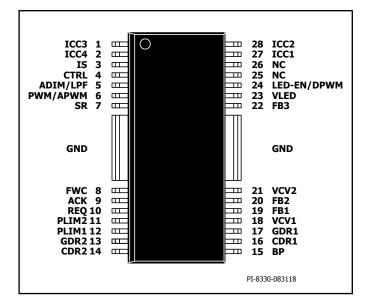

#### HSOP-28 InnoMux Controller

**CHANNEL 3 (ICC3) Pin (Pin 1)** LED current regulation channel 3.

CHANNEL 4 (ICC4) Pin (Pin 2) LED current regulation channel 4.

**SET LED CURRENT (IS) Pin (Pin 3)** Current setting for LED string current.

**CONTROL (CTRL) Pin (Pin 4)** Output to control capacitor.

**ANALOG DIMMING (ADIM/LPF) Pin (Pin 5)** Analog dimming/low pass filter connection.

**PWM DIMMING (PWM/APWM) Pin (Pin 6)** PWM input.

**SYNCHRONOUS RECTIFIER (SR) Pin (Pin 7)** SR signal from InnoSwitch3-MX.

**GROUND (GND) Pin** All grounds must connect to secondary ground.

**FORWARD COMPARATOR (FWC) Pin (Pin 8)** FW comparator signal from InnoSwitch3-MX.

ACKNOWLEDGE (ACK) Pin (Pin 9) ACK signal from InnoSwitch3-MX.

**REQUEST (REQ) Pin (Pin 10)** REQ output to InnoSwitch3-MX.

**POWER LIMIT 2 (PLIM2) Pin (Pin 11)** Set power limit for VLED/VCV2.

**POWER LIMIT 1 (PLIM1) Pin (Pin 12)** Set power limit for VCV1/VCV2.

**GATE DRIVER 2 (GDR2) Pin (Pin 13)** Selection MOSFET gate drive for CV2.

CAPACITOR (CDR2) Pin (Pin 14) Capacitor for GDR2.

BYPASS (BP) Pin (Pin 15) BP/VDD regulator output. Also supplies InnoSwitch3-MX.

CAPACITOR (CDR1) Pin (Pin 16) Capacitor for GDR1.

**GATE DRIVE 1 (GDR1) Pin (Pin 17)** Selection MOSFET gate drive for CV1.

**OUTPUT VOLTAGE (VCV1) Pin (Pin 18)** Output voltage connection for CV1 selection MOSFET drive.

**FEEDBACK 1 (FB1) Pin (Pin 19)** Feedback input for VCV1 output voltage.

Figure 6. InnoMux HSOP-28 Controller Pin Configuration.

#### FEEDBACK 2 (FB2) Pin (Pin 20)

Feedback input for VCV2 output voltage.

OUTPUT VOLTAGE (VCV2) Pin (Pin 21)

Output voltage connection for BP regulator and for CV2 selection  $\ensuremath{\mathsf{MOSFET}}$  drive.

**FEEDBACK 3 (FB3) Pin (Pin 22)** Feedback input for VLED output voltage.

**OUTPUT VOLTAGE (VLED) Pin (Pin 23)** Output voltage connection for BP regulator.

LED-EN/DPWM Pin (Pin 24) LED enable/digital PWM input.

**NOT CONNECTED (NC) Pin (Pin 25)** This pin is not connected and should be left floating.

**NOT CONNECTED (NC) Pin (Pin 26)** This pin is not connected and should be left floating.

CHANNEL 1 (ICC1) Pin (Pin 27) LED current regulation channel 1.

**CHANNEL 2 (ICC2) Pin (Pin 28)** LED current regulation channel 2.

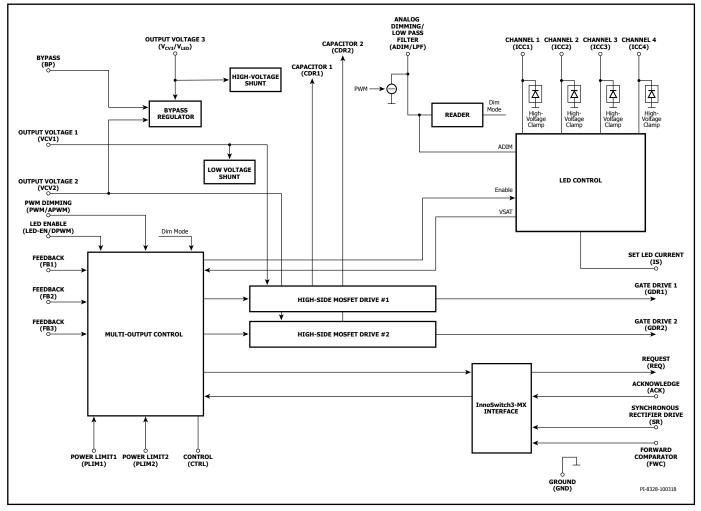

# **InnoMux Functional Description**

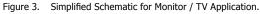

When paired with the InnoSwitch3-MX, the InnoMux combines dual constant voltage output regulation with a four string constant current LED backlight controller.

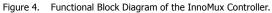

The InnoMux controller consists of a multi-output controller for regulating the three outputs independently, a BP Regulator for supplying both the InnoMux as well as the paired InnoSwitch3-MX secondary controller, High-Side MOSFET Drivers for directing the energy from the transformer to the appropriate output, Shunts to prevent individual outputs from rising in abnormal loading conditions, Current Sources to drive up to four LED backlight strings, and Readers to determine the value of application configuration resistors.

# **Block Diagram**

#### **BP Regulator**

The regulator regulates the BP pin to V<sub>BP(REG)</sub>. The BP regulator will use V<sub>CV2</sub> as its primary source. During start-up, the regulator will use V<sub>LED</sub> as long as V<sub>CV2</sub> is too low (below V<sub>CV2(MIN)</sub>).

It is possible to connect an unregulated supply to  $V_{_{\rm CV2}}$  to power the controller in single CV applications. For the controller to function properly, the application designer must make sure that  $V_{_{\rm CV2}}$  remains above  $V_{_{\rm CV2}(\rm MIN)}$  in all operating conditions after start-up.

A ceramic capacitor on the BP in is recommended. There are no stability requirements on the capacitor; the BP regulator is unconditionally stable.

# **Multi Output Control**

The multi output control regulates each of the two CV outputs and the LED output independently by requesting pulses from the primary based on the FB pin voltages for the three outputs. The transformer energy is then directed to the output that needs the energy on a cycle by cycle basis by turning on the appropriate selection MOSFET in series with either the CV1 or the CV2 output. The transformer shall be designed such that the VOR is increasing from VCV1 to VCV2 to VLED, this guarantees that the current through the VLED diode is negligible when the selection MOSFET for either VCV1 or VCV2 is turned on; only disabling both MOSFETs will direct the energy delivery to the LED output.

Due to the restriction in VOR, the maximum suggested LED output voltage range is about 2:1. A larger range will yield a less optimized design, as the VOR of the CV outputs gets very low. This is further explained in the applications section.

The controller uses a variable frequency control scheme. The CV outputs can run in continuous conduction mode (CCM) during high load. The  $V_{LED}$  output will always run discontinuous conduction mode (DCM) to prevent high reverse recovery losses in the high voltage silicon diode for the  $V_{LED}$  output.

# **High-Side MOSFET Drive**

The high side selection MOSFETs are driven with a drive voltage 5 V above  $V_{_{\rm CV1}}$  for GDR1 and 5V above  $V_{_{\rm CV2}}$  for GDR2 using a capacitive drive approach.

The capacitive drive approach benefits from easy level translation by use of capacitor  $C_{_{DR}}$ . A regular refresh cycle to top up the charge on  $C_{_{DR}}$  is needed when one of the switches has been on for a long time, as the charge on  $C_{_{DR}}$  will otherwise slowly leak away. Refresh is also needed during start-up to allow  $C_{_{DR}}$  to follow the output voltage when the output is being pulled up. The controller will perform refresh cycles when necessary by turning the selection MOSFET off and then back on.

The default refresh time is  $T_{\text{RESFRESH}}$ , which is doubled to  $2 \times T_{\text{RESFRESH}}$  during start-up. The longer the refresh time the better but the MOSFET needs to be turned back on before the end of the primary on time. Once the CV outputs are in regulation the refresh time is reduced to  $T_{\text{RESFRESH}}$ . Because the output is no longer changing the refresh is only needed to top up  $C_{\text{DR}}$  and by reducing the refresh time the risk of the primary on time finishing before the refresh is reduced.

The optimal capacitor value for  $C_{_{DR}}$  depends on the gate charge of the selection MOSFET. The selection MOSFET on-level gate voltage is determined by  $V_{_{BP}} \times (C_{_{DR}}/(C_{_G} + C_{_{DR}}))$ , so it is essential that the gate charge (at 5 V gate voltage) is much smaller than the charge in the  $C_{_{DR}}$  capa. A typical value for the  $C_{_{DR}}$  capacitor is 100nF. For higher  $C_{_{DR}}$  capacitor values, the refresh time might be insufficient and the capacitor will not be able to follow the output during start-up. It is therefore important to select low gate-charge devices for the selection MOSFETs to minimise the required  $C_{_{DR}}$  capacitor value as well as to minimise energy consumption for driving the MOSFETs.

#### Shunts

The LV shunt is designed to limit the voltage lift on the V<sub>CV1</sub> output. Voltage lift on the V<sub>CV1</sub> output will typically occur due to the lower VOR of the 5 V output. At turn-on of the 5 V selection MOSFET after delivery of a pulse to one of the other outputs, a small amount of energy is delivered to the CV1 output from the higher idle ring voltage.

The LV shunt is turned on when the FB1 voltage exceeds V<sub>LVSHUNT</sub>.

In practical applications it is unlikely for the CV1 output to lift; CV1 output lift typically only occurs when the CV1 output is completely unloaded while the other outputs are running at high output load.

The HV shunt is used to limit the voltage on the V<sub>LED</sub> rail to the maximum allowed voltage in case of peak-charging of the V<sub>LED</sub> output when the LED output is not loaded. This peak charging is predominantly caused by leakage in the transformer; the V<sub>LED</sub> output typically has lowest leakage and thus will receive a small amount of energy from switching cycles that are destined for V<sub>CV1</sub> or V<sub>CV2</sub>.

The HV shunt is turned on when the FB3 voltage exceeds V<sub>HV(SHUNT)</sub>.

In case of application problems with overvoltage on  $V_{\tiny LED'}$  it is possible to implement an additional Zener diode clamp with a small series resistor to dissipate the excess power as the range between  $V_{\tiny FB3(REG)}$  and  $V_{\tiny FB3(OVP)}$  is sufficiently large.

Note that the  $V_{\rm CV2}$  output does not need a shunt as this output is not susceptible to peak charging or unintended energy delivery.

#### **LED Current Control**

#### Operation

Current sources control the current into the ICC pins.

The maximum current for each current source is  $I_{\rm ICC(MAX)}$ . The desired (full-scale) current for each of the current sources can be set by a single external current sense resistor  ${\sf R}_{\rm LED}$  (which is connected to the IS pin).

The design of the current sources guarantees that the current in each of the strings is tightly balanced.

Current sources can be paralleled (ganged together) when only one or two strings are used. This will increase the maximum allowed string current.

The current sources accommodate PWM dimming, analog dimming and hybrid dimming. Hybrid dimming is a combination of analog and PWM dimming. Dimming is further described in Led Dimming section.

# Output Voltage Regulation for $\mathbf{V}_{\scriptscriptstyle \mathsf{LED}}$ Output

InnoMux keeps the voltage drop over the current sources as low as possible to maintain optimum system efficiency. The output voltage for driving the LED string(s) ( $V_{LED}$ ) is therefore regulated based on the minimum required voltage drop over the four current sources. The low voltage drop over the current sources is maintained for any LED current by changing the  $V_{LED}$  output voltage set point.

When the LEDs are on, the voltage on the C<sub>CTRL</sub> capacitor is used as set point for the V<sub>LED</sub> output voltage. The voltage on the capacitor is increased when the voltage drop over anyone of the current sources is less than the target value. Vice versa, the voltage on the cap is reduced when the voltage on all current sources is too high.

The regulation loop is subject to stability criteria and the capacitor has to be chosen accordingly; the optimal capacitor value depends on:

- 1. The ratio of the LED rail output capacitance (C\_{\_{VLED}}) to the available current for increasing the V\_{\_{LED}} rail voltage;

- 2. The FB3 voltage divider ratio (FB3RATIO=VLED/VFB3).

The minimum capacitance value for the  $C_{CTRL}$  capacitor is given by the following formulae; both conditions have to be met:

$$\begin{split} C_{\text{CTRL}} &\geq \frac{0.3 \times Gm_{\text{CTRL}(\text{UP})}}{0.2 \times I_{\text{LED}}} \times \text{FB3RATIO} \times C_{\text{VLED}} \\ C_{\text{CTRL}} &\geq 4 \times Gc_{\text{CTRL}(\text{DOWN})} \times \text{FB3RATIO} \end{split}$$

The first formula guarantees that the maximum dV/dt on the V<sub>LED</sub> voltage rail is larger than the dV/dt on the C<sub>CTRL</sub> capacitor. The second formula makes sure that the reduction in voltage on the C<sub>CTRL</sub> capacitor is smaller than the measured voltage error on the V<sub>LED</sub> rail

For typical designs, 220 nF is a good starting point.

#### Low Current Clamps

Low-current clamps on each of the  $I_{\rm CC}$  outputs are designed to prevent over voltage conditions on the ICC pins when the LEDs are turned off. The maximum current for these clamps is  $I_{\rm CCHV(CLAMP)}$ . These clamps will limit the voltage on the ICC pins below  $V_{\rm HV(CLAMP)}$  in LED off conditions, even when the nominal LED string voltage  $(V_{\rm F})$  is about 100 V.

## InnoSwitch3-MX Interface

The InnoMux to InnoSwitch3-MX interface is a four-wire interface.

The REQ signal indicates a request from the InnoMux controller for a new pulse. Upon reception, InnoSwitch3-MX will then communicate this request to the primary side controller over the integrated flux-link. (Note that the InnoSwitch3-MX will delay the request to the primary when in DCM to achieve QR mode switching.)

The REQ signal is also used to communicate timing for specific events during start-up as well as error conditions to the InnoSwitch3-MX. For this reason, REQ is a multi-level signal. The levels are shown in the table below.

| <b>REQ Pin Voltage Level</b>                     | Condition                                                                                                                                                                                                                                       |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ < 0.25 × V <sub>REF</sub>                    | Initial level at power-up.<br>No pulse requested by InnoMux.<br>InnoSwitch3-MX secondary on<br>stand-by / in primary control mode.<br>InnoSwitch3-MX secondary will start<br>handshake and obtain control when<br>the first pulse is requested. |

| $0.25 \times V_{REF} < REQ < 0.5 \times V_{REF}$ | InnoMux indicates measurement<br>window to InnoSwitch3-MX for idle<br>ring frequency measurement. This is a<br>one-off event during stat-up.                                                                                                    |

| $0.5 \times V_{_{REF}} < REQ < V_{_{REF}}$       | No pulse requested by InnoMux.                                                                                                                                                                                                                  |

| V <sub>REF</sub> < REQ < 2V <sub>REF</sub>       | Pulse requested by InnoMux.<br>InnoMux will retain the REQ level until<br>the pulse request has been acknowl-<br>edged (pulse on ACK pin) by Inno-<br>Switch3-MX and a rising edge is<br>observed on the SR pin.                                |

| REQ > 2V <sub>REF</sub>                          | Output overvoltage indication by<br>InnoMux.<br>InnoSwitch3-MX secondary will signal<br>the primary to latch-off.                                                                                                                               |

The ACK signal indicates that a pulse request has been made by InnoSwitch3-MX secondary to the primary controller (via the flux link). The rising edge of the SR signal (driven by InnoSwitch3-MX) is used byInnoMux to assess when the transformer starts delivering energy to the secondary.

The PCB trace connecting the REQ pins deserves specific attention during layout; it is a high-impedance multi-level analog signal and is sensitive to noise pick-up and layout impedance.

#### Readers

The (pin-) readers determine the presence and value of the resistors/ capacitors connected to the PLIM and ADIM inputs. These readers are active only directly after start-up and will not update until the next power-up.

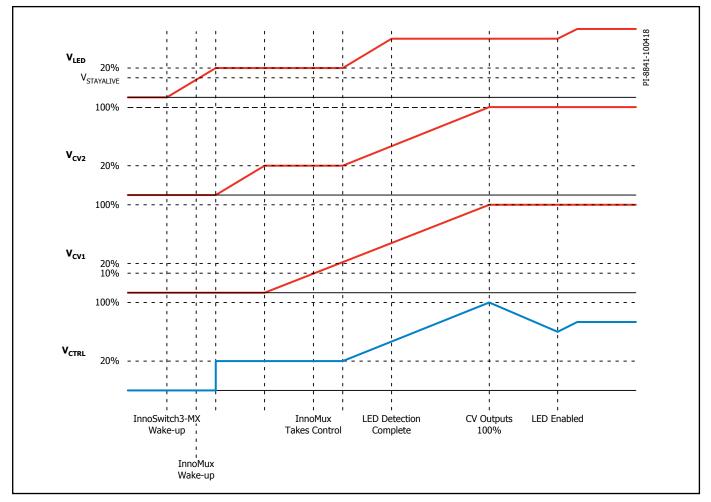

# Start-Up

During start-up, the InnoSwitch3-MX will run at a fixed frequency and 50% of maximum ILIM. The InnoMux controller will first bring up V<sub>LED</sub> to V<sub>STAVALIVE</sub> level, a sufficient level to provide power to the BP regulator or to 20% of the target value, whichever is highest. As soon as the V<sub>LED</sub> has reached the designated level, the controller will start bringing up V<sub>CV2</sub> to 20% of the target value and finally the V<sub>CV1</sub> to 10% of the target value. When all three outputs are at the correct level, the InnoMux controller will take control and bring up V<sub>CV1</sub> and V<sub>CV2</sub> simultaneously. The voltage on the control capacitor is slowly increased and is used as the reference for the V<sub>CV1</sub> and V<sub>CV2</sub> outputs during pull up. The size of the C<sub>CTRL</sub> capacitor will affect the rate of rise of the outputs during pull up.

The LEDs will only be enabled after V<sub>CV1</sub> and V<sub>CV2</sub> have reached regulation voltage. At this moment, the CV output regulators switch to a fixed internal reference and the VLED output will start using the voltage on C<sub>CTRI</sub> as its set point.

Figure 7 shows a schematic representation of the start-up process.

# **LED String Configuration Detection**

During pull up of the CV outputs, the controller will also increase the  $V_{\text{LED}}$  and try to run a small amount of current through the LEDs strings to detect which of the four ICC pins have an LED string attached and whether any of the ICC pins have been connected in parallel in a supported configuration. Unused pins should be connected to GND and will be disabled by the controller.

At start-up, the controller will verify that none of the connected LED strings is short-circuit (the ICC pin connected directly to the  $V_{LED}$  supply rail). If one of the strings were short-circuit, the response depends on the maximum LED voltage. For low-voltage LED configurations (up to about 55 V maximum LED string voltage), the affected string will be turned off and the controller will start-up as normal. For high voltage LED configurations, the controller will auto-restart as the short-circuit string could violate the maximum allowed ICC pin voltage. The low-voltage / high-voltage detection is based on the FB3 resistor ratio, which is determined at start-up.

Figure 7. Start-Up Diagram.

# **LED Dimming**

The current through the LED strings can be varied for changing (dimming) the LED brightness.

Three LED dimming modes are supported:

- 1. PWM only dimming with fixed output current

- Analog dimming, output current set by an external reference voltage (V<sub>ADIM</sub>)

- 3. Hybrid dimming: analog dimming and PWM dimming combined.

The first dimming mode only supports PWM dimming. In this mode, the LED current is set by a resistor on the IS pin. The analog dimming mode (second mode) allows reducing the LED current from 100% (as set by  $R_{\tiny LED}$  on the IS pin) to 0 (minimum current:  $I_{\tiny CC(MIN)}$ ) by

varying the voltage on the ADIM pin. The third mode is a combination of analog and PWM dimming.

The LED dimming mode is selected at start-up and is determined by the level on the ADIM pin. A pull-up connection / resistor to BP selects the PWM only dimming mode. (The value of the pull-up resistor will then select between normal and sequenced PWM. A low signal level at start-up (ADIM voltage below  $V_{\text{ADIM(SEL)}}$ ) will select the analog or the hybrid dimming mode.

After start-up, the dimming mode is fixed and cannot be changed without a power-on reset.

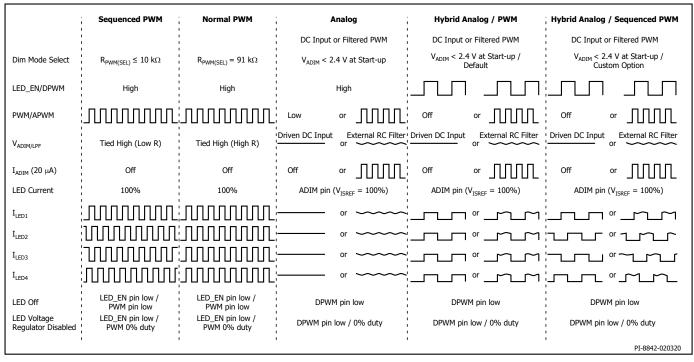

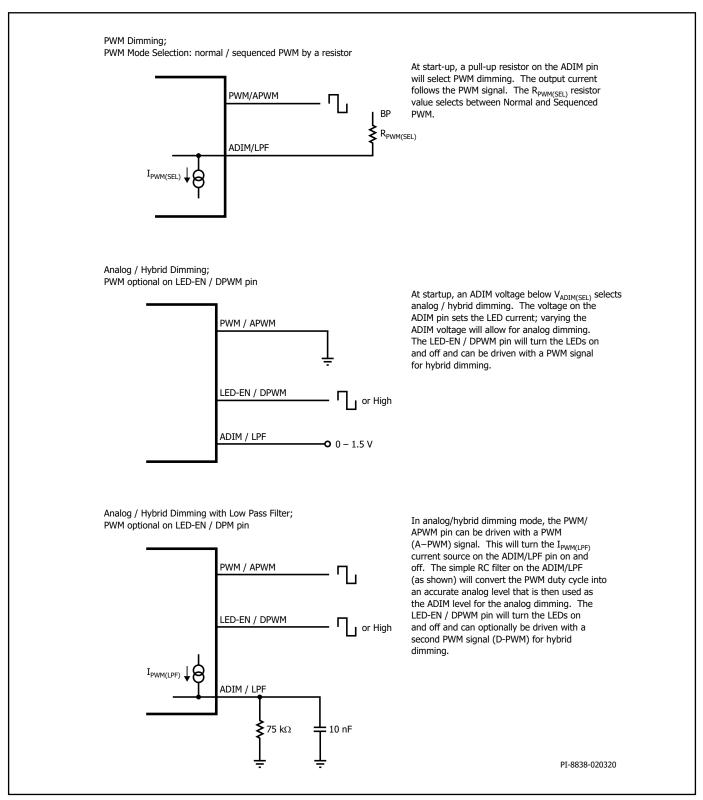

Figure 8 below shows an overview of the available dimming modes in the InnoMux controller.

Figure 8. InnoMux Dimming Modes.

## **PWM Dimming Only**

By connecting the ADIM/LPF pin to BP, the LED current (per string) is set by the RLED resistor based on an internal reference ( $V_{\text{IS(REF)}}$ ).

$$R_{LED} = V_{IS(REF)} \times \left(\frac{I_{OUT}}{561.56}\right)^{-1.015}$$

The formula shows the relationship between the desired output current and the required value for the current setting resistor.

$I_{_{OUT}}$  is the ICC pin current (for four string operation, the total current equals 4  $\times$   $I_{_{OUT}}$ ),  $V_{_{IS(REF)}}$  is an internally generated reference voltage of 1.5 V. The result gives the resistor value for RLED which sets the current for each of the ICC pins. As the formula is non-linear, the desired ICC pin current must be given in Ampere (A, not mA) and the result is in Ohms ( $\Omega$ ).

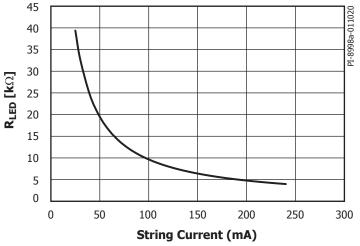

Figure 9 shows a graph of  $R_{\rm LED}$  vs. LED string current. This graph can be used for estimating the required  $R_{\rm LFD}$

PWM dimming is supported by applying a PWM signal with desired duty cycle to the PWM pin. The allowed PWM frequency range is  $PWM_{F(RANGE)}$ . Pulling the LED-EN pin low will turn off the LEDs as well as the LED regulator. This is intended for disabling the LEDs during a 'screen-off' mode. Turning off the LED regulator will reduce chip current consumption.

Notes:

- Pulling the PWM pin low to turn the LEDs off is allowed. Keeping the PWM pin low longer than the minimum PWM period will also turn off the LED regulator, independent of the LED-EN signal.

- Pulling LED-EN low will override the state of the PWM signal.

PWM dimming is supported using normal PWM dimming and sequenced (phase shifted) PWM dimming. Normal PWM and sequenced PWM are further explained in the section on PWM dimming (These two PWM dimming modes are also supported in the hybrid dimming mode, see below.)

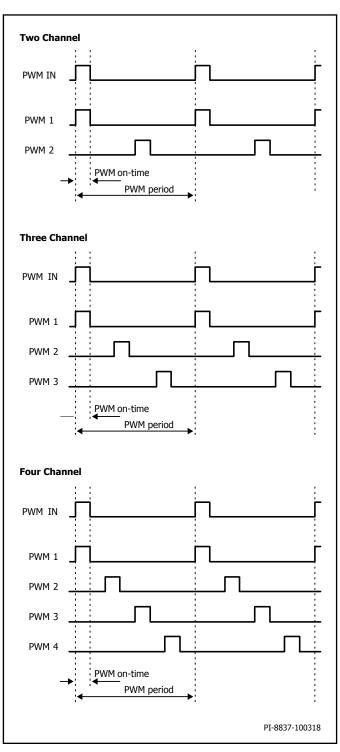

Figure 11 (page 12) shows the typical connections in this mode for the PWM and LED-EN signals. The  $R_{\mbox{\tiny PWM(SEL)}}$  pull-up resistor selects between normal and sequenced PWM mode.

#### **Analog and Hybrid Dimming Modes**

#### **Analog Dimming**

In the analog dimming mode, the voltage on the ADIM/LPF pin determines the LED current. The LED current changes linearly over the  $V_{ADIM}$  range. The 100% LED current level (per string) is set by the  $R_{LED}$  resistor.

$$\mathsf{R}_{\mathsf{LED}} = \mathsf{V}_{\mathsf{ADIM}} \times \left(\frac{\mathsf{I}_{\mathsf{OUT}}}{\mathsf{561.54}}\right)^{-1.01}$$

The formula shows the relationship between the desired output current and the required value for the current setting resistor.

$I_{_{OUT}}$  is the ICC pin current (for four string operation, the total current equals 4  $\times$   $I_{_{OUT}}$ ),  $V_{_{ADIM}}$  is the voltage on the ADIM pin (1.5 V is full scale). The result gives the resistor value for  $R_{_{LED}}$  which sets the current for each of the ICC pins. As the formula is non-linear, the desired ICC pin current must be given in Ampere (A, not mA) and the result is in Ohms ( $\Omega$ ).

Figure 9 shows a graph of  $\rm R_{LED}$  vs. LED string current at  $\rm V_{ADIM}$  = 1.5 V. This graph can be used for estimating the required  $\rm R_{LED}$ .

The ADIM pin is normally driven from an external source (e.g. display controller) to set the display brightness.

It is possible to use a PWM signal (A-PWM) to generate the analog dimming reference ( $V_{ADIM}$ ) for the LED current; the duty cycle on the APWM pin is then accurately converted into an analog dimming reference voltage on the ADIM/LPF pin by a simple external RC low pass filter fed by an on chip current source providing  $I_{PWM(LPF)}$ .

The low pass filter needs a 75 k $\Omega$  resistor to allow regulating up to 100%. The capacitor is typically chosen as 10 nF, but can be changed if a different RC time constant would be desired.

The APWM pin should be tied low when a DC voltage is supplied to the ADIM/LPF pin.

The DPWM pin should be high during analog dimming. Pulling the DPWM pin low will turn off the LEDs and the LED regulator. This is intended for disabling the LEDs during use in a 'screen-off' mode. Reducing the ADIM voltage down to 0 V to turn the LEDs off is not allowed for disabling the LEDs.

Figure 11 (page 12) shows the typical connections in this mode for the DPWM, APWM and analog dimming reference ( $V_{\text{ADIM}}$ ) signals.

| LED Configuration | <b>Required Phase Shift</b> | Description                                                                                                                          |

|-------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1 - 2 - 3 - 4     | 0°, 90°, 180°, 270°         | Four strings. All outputs 90° phase shifted.                                                                                         |

| 1 - 2 - 3         | 0°, 120°, 240°              | Three strings. Outputs 1, 2, and 3 all 120° phase shifted.<br>Output 4 not used.                                                     |

| 1 - 3             | 0°, 180°                    | Two strings only. Output 3 180° phase shifted with respect to output 1.                                                              |

| 1 2 - 34          | 0°, 180°                    | Same as above, but now with outputs 1+2 and 3+4 ganged together. Outputs 3 and 4 180° phase shifted with respect to outputs 1 and 2. |

Table 2. Sequenced PWM Dimming Options.

#### **Hybrid Dimming**

PWM dimming is supported during analog dimming by applying a PWM signal (D-PWM) with desired duty cycle to the DPWM pin. The allowed PWM frequency range is PWM<sub>F(RANGE)</sub>. The LEDs are turned off by pulling the DPWM pin low. Normal PWM is active by default. Sequenced PWM is available as a custom option. (The R<sub>PWM(SEL)</sub> resistor is not available in this mode.)

Pulling the DPWM pin low longer than the minimum PWM period will turn off the LED regulator, which will reduce chip current consumption in a 'screen-off' mode. Reducing the ADIM voltage down to 0 V to turn the LEDs off is not allowed for disabling the LEDs.

Figure 11 (page 12) shows the typical connections in this mode for the DPWM, APWM and external LED current reference ( $V_{\text{ADIM}}$ ) signals.

#### **PWM Dimming**

In PWM dimming, the LED current sources switch rapidly between the set reference current and off, following the digital state of the PWM input.

Two PWM dimming modes are available; normal and sequenced PWM. In PWM dimming, the ADIM/LPF pull-up resistor value selects between normal or sequenced PWM dimming. In hybrid dimming, the selection between normal and sequenced PWM has been preset and cannot be changed by application components.

#### **Normal PWM Dimming Mode**

During normal PWM mode dimming, all strings will turn on and off in phase.

#### Sequenced PWM Dimming Mode

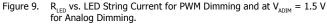

In sequenced PWM mode, the on-periods of the four LED strings are sequenced in time by applying an equal phase shift to each of the strings. The sequenced PWM mode is designed to improve visual performance as well as reduce transient loading on the power supply which will reduce audible noise. Dependent on the LED configuration, the PWM phase shift between channels should be 90°, 120° or 180°. The allowed LED configurations for sequenced PWM diming are shown in Table 2.

The controller will revert to normal PWM dimming if sequenced PWM is selected with an unsupported LED string configuration.

Typical low PWM duty cycle examples for two, three and four strings are shown in Figure 10. It shows the relative timing of the LED

currents in two, three and four-channel sequenced PWM dimming operation. The top waveform depicts the incoming PWM signal (PWM/D-PWM).

Figure 10. PWM Timing Diagram for Two, Three and Four Channel Sequenced PWM Dimming.

# **Connection Diagrams for the Various Dimming Options**

Figure 11. Connection Diagrams for Dimming Options.

# **Protection Features and Fault Handling**

# **Overload / Maximum Power Protection and Maximum Power Limit**

# Maximum Power Protection:

# **Overload / Short-Circuit Protection**

The CV1, CV2 and VLED outputs have a maximum power protection. The simplest part of the protection is to detect whether the output is more than 10% (CV outputs) or more than 1% ( $V_{LED}$  output) below set point. If this condition persists for more than 32 switching cycles, then the output is assumed to be overloaded; either the output has a short-circuit or the overall power capability of the power supply has been exceeded and it simply cannot keep the output in regulation.

#### **Maximum Power Limit**

The short-circuit fault protection forms an overall power limit but it would allow the full output power to be drawn from a single output without any further protection. Therefore, the power limit function also includes an average frequency limit that has a user selectable level.

The power limit threshold for each of the three outputs is set by the designer using external components on the two PLIM pins. Four setting levels for each output are available.

The power limit measures the average frequency of switching pulses to a specific output. If this frequency is above a preset threshold for a certain amount of time, then a fault is flagged and the controller will auto restart or latch-off.

For calculating the maximum power limit threshold, the frequency for a specific output should be calculated as a fraction of the maximum total output power.

$$f_{\text{limit}} = \frac{P_{\text{output(max)}}}{P_{\text{max}}} \times f_{\text{max}}$$

$\begin{array}{ll} P_{\text{OUTPUT(MAX)}} & \text{Maximum allowed power for this output} \\ P_{\text{MAX}} & \text{Maximum total output power} \\ f_{\text{MAX}} & \text{Operating frequency at maximum output power} \\ f_{\text{LIMIT}} & \text{Calculated maximum frequency for this output} \end{array}$

The maximum overload duration is set such that the load is able to draw at least double the nominal power for at least 10 ms, assuming the load is not drawing more power than the power supply is physically capable of delivering.

|        | CV1 PLIM1    | V <sub>LED</sub> PLIM2 |

|--------|--------------|------------------------|

| 30 kHz | 5.1 kΩ       | 5.1 kΩ                 |

| 41 kHz | 10 kΩ        | 10 kΩ                  |

| 56 kHz | 22 kΩ        | 22 kΩ                  |

| 78 kHz | <b>39</b> kΩ | 39 kΩ                  |

Table 3. CV1 and VLED Power Limit Selection.

The power for CV2 is selected with the presence or absence of capacitors on PLIM1 and PLIM2 as shown in the table below. If there is no CV2 output then no capacitors are needed.

|        | PLIM1        | PLIM2        |

|--------|--------------|--------------|

| 30 kHz | No Capacitor | No Capacitor |

| 41 kHz | Capacitor    | No Capacitor |

| 56 kHz | No Capacitor | Capacitor    |

| 78 kHz | Capacitor    | Capacitor    |

Table 4. CV2 Power Limit Selection.

The time constant for the PLIM resistor and capacitor should be chosen as  $T_{_{\rm PLIM}}.$  This defines the capacitor value for a given resistor.

Further details on setting the PLIM components can be found in the applications section.

# **Output OV**

Any output reaching the output overvoltage (V<sub>ov</sub>) threshold will cause a restart or latch-off of the controller. The output OV condition is detected on the respective FB pins for the three outputs.

#### **LED Fault Detection**

During operation, the controller will continuously monitor the voltages on the ICC pins. If a large asymmetry between the LED strings (>V<sub>ICC(OV)</sub>) is detected, the shorter string(s) will be disabled to prevent excessive power dissipation in the controller. Any strings that go open-circuit or short-circuit will also be disabled.

LED return short to ground will be detected by the power limit protection, which will force a controller restart. After restart, the affected string will be disabled.

# **Over-Temperature**

The thermal protection circuitry continuously measures the controller temperature. The threshold is set at  $T_{_{PROT}}$ . When the temperature rises above  $T_{_{PROT}}$ , the InnoMux will disable the LEDs as well as the CV outputs with hysteretic over-temperature protection; the LEDs and CV outputs will remain disabled and the  $V_{_{LED}}$  rail will be maintained at  $V_{_{STAVALIVE}}$  until the temperature drops below  $T_{_{PROT}}$ - $T_{_{HYST}}$ . The controller will restart when the temperature has dropped below this level.

If the temperature at any moment exceeds  $T_{_{\rm SD'}}$  the InnoMux will send a latch-off request to the InnoSwitch3-MX.

#### **Fault Handling**

When a fault is flagged, the controller will either auto-restart or latch-off.

In the auto-restart condition, the InnoMux will stop requesting switching cycles. This will cause the output rails to collapse. As there will be no further requests, the InnoSwitch3-MX primary will take back control after a pre-defined time-out and restart.

In the latch-off condition, the InnoMux will send a latch-off request to the InnoSwitch3-MX and the primary will latch-off. This condition will persist until the mains input power is cycled.

#### Absolute Maximum Ratings<sup>1,2</sup>

| BP Pin Voltage                                  | 0.3 V to 6 V     |

|-------------------------------------------------|------------------|

| V <sub>CV1</sub> , V <sub>CV2</sub> Pin Voltage | 0.3 V to 25 V    |

| V <sub>CV3</sub> / V <sub>LED</sub> Pin Voltage |                  |

| GDR1, GDR2 Pin Voltage                          | 0.3 V to 30 V    |

| ICC1, ICC2, ICC3, ICC4 Pin Voltage              | 0.5 V to 65 V    |

| All Other Pins                                  | 0.3 V to 6 V     |

| Storage Temperatue                              | 65 °C to 150 °C  |

| Operating Junction Temperature <sup>3</sup>     | 40 °C to +150 °C |

(θ<sub>JA</sub>)......50 °C/W<sup>2</sup>

(θ<sub>1</sub>).....15 °C/W<sup>3</sup>

#### V Notes:

1. All voltages referenced to Secondary GROUND,  $T_{A} = 25$  °C.

2. Maximum ratings specified may be applied one at a time without causing permanent damage to the product. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect product reliability.

3. Normally limited by internal circuitry.

#### **Thermal Resistance**

QFN-28 Package

#### Notes:

1. Single-Layer, 2 oz. Cu. 0.36 sq. in. heat sinking area.

- 2. Single-Layer, 2 oz. Cu. 1.0 sq. in. heat sinking area.

- 3. Single-Layer, 2 oz. Cu. 0.36 & 1.0 sq. in. heat sinking area.

- Thermocouple attached to ground lead shoulder, near to edge of plastic body.

- Dual-Layer, 2 oz. Cu. 0.36 sq. in. heat sinking area (bottom layer, connected by 9 filled vias).

- Dual-Layer, 2 oz. Cu. 1.0 sq. in. heat sinking area (bottom layer, connected by 9 filled vias).

|                           |                           |                                                                             |                                         |      | 1   | 1    | 1     |

|---------------------------|---------------------------|-----------------------------------------------------------------------------|-----------------------------------------|------|-----|------|-------|

| Parameter                 | Symbol                    | Condi<br>All Voltages Reference<br>T <sub>J</sub> = -40 °C<br>(Unless Other | ed to GROUND / 0 V                      | Min  | Тур | Max  | Units |

| Pin Description and Paran | neters                    |                                                                             |                                         |      |     |      |       |

| BP Pin                    |                           | Internal voltage sup<br>supply for Inn                                      |                                         |      |     |      |       |

| BP Voltage Regulation     | V <sub>BP(REG)</sub>      |                                                                             |                                         | 4.75 | 5.0 | 5.25 | V     |

| BP Current                | I <sub>BP</sub>           | Full load excludes cur<br>InnoSwitch3-M<br>MOSFET                           | X and selection                         |      | 18  |      | mA    |

|                           | BP <sub>uv</sub>          |                                                                             |                                         |      | 4.4 |      | V     |

| Standby Supply Current    | I <sub>SBP(STANDBY)</sub> |                                                                             |                                         |      | 6   |      | mA    |

| VCV1 Pin (See Note B)     |                           | Input voltage for CV1 s                                                     | election MOSFET drive                   |      |     |      |       |

|                           | V <sub>cv1</sub>          | V <sub>cv1</sub> output v                                                   | oltage range                            | 3    |     | 22   | v     |

| VCV2 Pin (See Note B)     |                           | Input voltage for VDD regulator and for CV2 selection MOSFET drive          |                                         |      |     |      |       |

|                           | V <sub>cv2</sub>          | V <sub>cv2</sub> output v                                                   | oltage range                            | 3    |     | 22   | v     |

|                           | N/                        | Minimum V <sub>cv2</sub> voltage                                            | Standby 25 °C                           | 5.8  |     |      | V     |

|                           | $V_{cv2(MIN)}$            | for BP regulator                                                            | Full Load (30 mA)                       | 8.0  |     |      |       |

| VLED Pin                  | V                         | V <sub>LED</sub> output v                                                   | oltage range                            | 20   |     | 100  | V     |

|                           | V <sub>STAYALIVE</sub>    | Minimum V <sub>LED</sub> voltag<br>maintained by                            | e that will always be<br>the controller |      | 15  |      | v     |

| Gate Drive Pins           | ,                         |                                                                             | · · · · · · · · · · · · · · · · · · ·   |      |     |      |       |

| Refresh Pulse Width       | T <sub>REFRESH</sub>      | T <sub>REFRESH</sub> is doubled during start-up<br>See Note D               |                                         |      | 500 |      | ns    |

| GDR1                      |                           | The GDR1 pin selection                                                      |                                         |      |     |      |       |

| Parameter                       | $T_{j} = -40 \degree C \text{ to } 125 \degree C$ (Unless Otherwise Specified) |                                                                                                                                       | Min | Тур                                                                        | Max | Units |

|---------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------|-----|-------|

| Gate Drive Pins (cont.)         |                                                                                |                                                                                                                                       |     | į                                                                          |     |       |

| GDR1 Output<br>Drive Voltage    | $V_{\rm dr1}$                                                                  | $\begin{array}{l} V_{_{CV1}} + V_{_{BPREG}} \text{ (GDR}_{_1} \text{ High)} \\ V_{_{CV1}} \text{ (GDR}_{_1} \text{ Low)} \end{array}$ |     |                                                                            |     |       |

| GDR1 Resistance                 | R <sub>dr1</sub>                                                               | T <sub>j</sub> = 125 °C<br>See Note C                                                                                                 |     | 30                                                                         | 35  | Ω     |

| GDR2                            |                                                                                | The DR2 pin drives the CV2 selection MOSFET                                                                                           |     |                                                                            |     |       |

| GDR2 Output Drive<br>Voltage    | V <sub>dr2</sub>                                                               | $V_{CV2} + V_{BPREG}$ (GDR <sub>2</sub> High)<br>$V_{CV2}$ (GDR <sub>2</sub> Low)                                                     |     | V <sub>CV2</sub> +V <sub>BPREG</sub><br>(high) /<br>V <sub>CV2</sub> (low) |     | v     |

| GDR2 Resistance                 | R <sub>dr2</sub>                                                               | T₁ = 125 °C<br>See Note C                                                                                                             |     | 30                                                                         | 35  | Ω     |

| FB/IS Pins                      | 1                                                                              | '                                                                                                                                     |     | 1 1                                                                        |     | 1     |

| FB1                             |                                                                                | FB input for $V_{\scriptscriptstyle CV1}$ output voltage                                                                              |     |                                                                            |     |       |

| FB1 Regulation Voltage          | V <sub>FB1(REG)</sub>                                                          |                                                                                                                                       |     | V <sub>REF</sub>                                                           |     |       |

| LV Shunt Threshold              | $V_{LV(SHUNT)}$                                                                |                                                                                                                                       |     | 108% of<br>V <sub>REF</sub>                                                |     | v     |

|                                 | I <sub>CCLV(SHUNT)</sub>                                                       | See Note D                                                                                                                            | 17  | 20                                                                         |     | mA    |

| FB1 Overvoltage                 | V <sub>FB1(OVP)</sub>                                                          |                                                                                                                                       |     | 112% of<br>V <sub>REF</sub>                                                |     | v     |

| FB2                             |                                                                                | FB input for V <sub>cv2</sub> output voltage                                                                                          |     |                                                                            |     |       |

| FB2 Regulation Voltage          | V <sub>FB2(REG)</sub>                                                          |                                                                                                                                       |     | V <sub>REF</sub>                                                           |     | V     |

| FB2 Overvoltage                 | V <sub>FB2(OVP)</sub>                                                          |                                                                                                                                       |     | 112% of<br>V <sub>REF</sub>                                                |     | v     |

| FB3                             |                                                                                | FB input for $V_{LED}$ output voltage                                                                                                 |     |                                                                            |     |       |

| High-Voltage<br>Shunt Threshold | V <sub>HV(SHUNT)</sub>                                                         |                                                                                                                                       |     | 108% of<br>V <sub>REF</sub>                                                |     | v     |

|                                 | I <sub>CCHV(SHUNT)</sub>                                                       | See Note D                                                                                                                            | 8.5 | 10                                                                         |     | mA    |

| FB3 Overvoltage                 | V <sub>FB3(OVP)</sub>                                                          |                                                                                                                                       |     | 120% of V <sub>REF</sub>                                                   |     | v     |

InnoMux

| Parameter                            | Symbol                                           | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                             | Min | Тур                                                                | Max    | Units |

|--------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------|--------|-------|

| InnoSwitch3-MX Interfa               | ce Pins                                          | '                                                                                                                                                 |     |                                                                    |        |       |

| REQ                                  |                                                  | Pulse request output Should be connected to the InnoSwitch3-MX REQ input                                                                          |     |                                                                    |        |       |

| ACK                                  |                                                  | Acknowledge from InnoSwitch3-MX that a<br>request has been issued to the primary-side.<br>Should be connected to the InnoSwitch3-MX<br>ACK output |     |                                                                    |        |       |

| FWC                                  |                                                  | Forward comparator output from<br>InnoSwitch3-MX. Should be connected to the<br>InnoSwitch3-MX FWC output                                         |     |                                                                    |        |       |

| SR                                   |                                                  | SR output from InnoSwitch3-MX. Should be connected to the InnoSwitch3-MX SR output                                                                |     |                                                                    |        |       |

| LED Regulation Pins                  | _                                                |                                                                                                                                                   |     |                                                                    |        |       |

| CTRL Pin                             |                                                  | Output to CTRL capacitor                                                                                                                          |     |                                                                    |        |       |

| Maximum Current                      | I <sub>ctrl(pos)</sub><br>I <sub>ctrl(neg)</sub> |                                                                                                                                                   |     | 10                                                                 |        | μA    |

|                                      | I <sub>CTRL(STARTUP)</sub>                       |                                                                                                                                                   |     | $\begin{array}{c} 0.125 \times \\ I_{\text{CTRL}} \end{array}$     |        | А     |

| Regulator Gm (UP)                    | Gm <sub>CTRL(UP)</sub>                           | $0 \text{ V} < \text{V}_{\text{ICC(ERROR)}} < 0.3 \text{ V}$                                                                                      |     | $0.825 \times I_{CTRL}$                                            |        | A/V   |

| Regulator (DOWN)                     | GC <sub>CTRL(DOWN)</sub>                         | $-0.3 V < V_{ICC(ERROR)} < 0 V$                                                                                                                   |     | $\begin{array}{c} 41.25 \mu \times \\ I_{\text{CTRL}} \end{array}$ |        | C/V   |

| ICC Pins                             |                                                  | Regulator 1-4                                                                                                                                     |     |                                                                    |        |       |

| ICC Voltage<br>Protection Limit      | V <sub>ICC(OV)</sub>                             |                                                                                                                                                   | 8   |                                                                    | 9      | v     |

| Minimum ICC Current                  | I <sub>CC(MIN)</sub>                             | Per channel                                                                                                                                       |     | 5                                                                  |        | mA    |

| Maximum ICC Current                  | I <sub>ICC(MAX)</sub>                            | Per channel                                                                                                                                       |     | 240                                                                |        | mA    |

| ICC Channel Matching<br>(See Note A) | ∆100 mA                                          | 100 mA Current per string, measured in<br>analog dimming. Equal voltage on all<br>ICC pins. $T_j = 25 \text{ °C}$                                 |     |                                                                    | ±3     | %     |

|                                      | ∆5 mA                                            | 5 mA Current per string, measured in analog dimming. Equal voltage on all ICC pins.<br>$T_{1} = 25 \text{ °C}$                                    |     |                                                                    | ±3     | %     |

| ICC Clamp Voltage                    | V <sub>ICC(CLAMP)</sub>                          |                                                                                                                                                   |     | 60                                                                 | 65     | V     |

| Maximum ICC Clamp<br>Current         | I <sub>CCHV(CLAMP)</sub>                         |                                                                                                                                                   | 4   |                                                                    |        | μA    |

| ED Control Pins                      |                                                  |                                                                                                                                                   |     | · · ·                                                              |        |       |

| LED-EN/DPWM and                      | V <sub>IL</sub>                                  | LED-EN/DPWM and PWM/APWM input from                                                                                                               |     |                                                                    | 1.5    | v     |

| PWM/APWM Pins                        | V <sub>IH</sub>                                  | system microcontroller 0 V / 5 V, 3.3 V<br>compliant                                                                                              | 2.3 |                                                                    |        | v     |

|                                      | PWM <sub>F(RANGE)</sub>                          | Frequency range                                                                                                                                   | 100 |                                                                    | 27,000 | Hz    |

| PWM/APWM/DPWM<br>Frequency           | PWM <sub>D(RANGE)</sub>                          | Duty cycle range is<br>Minimum on-time 3 μs                                                                                                       | 2   |                                                                    | 100    | %     |

| ADIM/PWM<br>Selection Voltage        | V <sub>ADIM(SEL)</sub>                           |                                                                                                                                                   | 2.4 |                                                                    | 2.5    | V     |

| Parameter                     | Symbol                  | $\begin{array}{c} \textbf{Conditions} \\ \text{All Voltages Referenced to GROUND / 0 V} \\ \text{T}_{_{j}} = -40 \ ^{\circ}\text{C to } 125 \ ^{\circ}\text{C} \\ \text{(Unless Otherwise Specified)} \end{array}$                              | Min   | Тур   | Max   | Units |

|-------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| LED Control Pins (cont.)      |                         |                                                                                                                                                                                                                                                 |       |       |       |       |

| ADIM/LPF<br>Maximum Voltage   | V <sub>ADIM</sub>       | Analog dimming mode: 2% to 100%<br>2% brightness for $V_{ADIM} = 0.03 V$<br>100% brightness for $V_{ADIM} = V_{IS(REF)}$<br>Note: Minimum output current level is $I_{CC(MIN)}$                                                                 |       |       |       |       |

| Current Source                | $\mathbf{I}_{PWM(LPF)}$ | T <sub>1</sub> = 25 °C                                                                                                                                                                                                                          | 19.6  | 20.0  | 20.4  | μA    |

| PWM Mode<br>Selection Voltage | V <sub>PWM(SEL)</sub>   | $ \begin{array}{l} V_{\text{ADIM(SEL)}} < V_{\text{ADIM}} < V_{\text{PWM(SEL)}} = \text{Normal PWM} \\ V_{\text{ADIM}} > V_{\text{PWM(SEL)}} = \text{Sequenced PWM} \end{array} $                                                               | 3.8   |       | 3.9   | v     |

| IS Pin Reference<br>Voltage   | V <sub>IS(REF)</sub>    | T <sub>3</sub> = 25 °C                                                                                                                                                                                                                          | 1.47  | 1.50  | 1.53  | v     |

| Current Source                | I <sub>PWM(SEL)</sub>   | Only enabled during start-up                                                                                                                                                                                                                    |       | -20   |       | μA    |

| IS Pin Current Gain           | I <sub>s(ratio)</sub>   | $\begin{split} I_{\text{S(RATIO)}} &= I_{\text{LED}}/I_{\text{S}} \\ I_{\text{LED}} &= 100 \ \mu\text{A} \\ T_{\text{J}} &= 25 \ ^{\circ}\text{C} \\ I_{\text{S}} &= 156 \ \mu\text{A} \\ V_{\text{ADIM}} &\approx 0.72 \ \text{V} \end{split}$ | 629   | 642   | 655   |       |

| Other Parameters              |                         |                                                                                                                                                                                                                                                 |       |       |       |       |

| PLIM Pins                     |                         | Maximum power setting for $V_{_{CV1}\!\prime}$ $V_{_{CV2}}$ and $V_{_{LED}}$                                                                                                                                                                    |       |       |       |       |

| PLIM Pin RC Time<br>Constant  | T <sub>PLIM</sub>       | External RC on $P_{_{LIM}}$ pins                                                                                                                                                                                                                | 100   |       | 250   | μS    |

| Reference Voltage             | V <sub>REF</sub>        | T <sub>.</sub> = 25 °C                                                                                                                                                                                                                          | 1.194 | 1.218 | 1.242 | V     |

| OTL Protection                | T <sub>PROT</sub>       |                                                                                                                                                                                                                                                 | 130   | 142   |       | °C    |

| OTL Hysteresis                | T <sub>HYST</sub>       |                                                                                                                                                                                                                                                 |       | 67    |       | °C    |

| OTL Shut Down                 | T <sub>SD</sub>         |                                                                                                                                                                                                                                                 |       | 150   |       | °C    |

A. The mismatch is calculated using the following formula:  $\Delta = \pm \frac{(I_{\text{MAX}} - I_{\text{MIN}})}{2 \times I_{\text{AVG}}} \times 100\%$ B. V\_CV2 must be greater than or equal to V\_CV1. C. This parameter is derived from characterization. D. This parameter is guaranteed by design.

Rev. D 11/20

| Revision | Notes                                                            | Date  |

|----------|------------------------------------------------------------------|-------|

| В        | Code L release.                                                  | 03/19 |

| С        | Code A release.                                                  | 03/20 |

| D        | Added Storage Temperature data to Absolute Maximum Rating table. | 11/20 |

#### For the latest updates, visit our website: www.power.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

#### **Patent Information**

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations patents may be found at www.power.com. Power Integrations grants its customers a license under certain patent rights as set forth at www.power.com/ip.htm.

#### **Life Support Policy**

POWER INTEGRATIONS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF POWER INTEGRATIONS. As used herein:

- 1. A Life support device or system is one which, (i) is intended for surgical implant into the body, or (ii) supports or sustains life, and (iii) whose failure to perform, when properly used in accordance with instructions for use, can be reasonably expected to result in significant injury or death to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Power Integrations, the Power Integrations logo, CAPZero, ChiPhy, CHY, DPA-Switch, EcoSmart, E-Shield, eSIP, eSOP, HiperPLC, HiperPFS, HiperTFS, InnoSwitch, Innovation in Power Conversion, InSOP, LinkSwitch, LinkZero, LYTSwitch, SENZero, TinySwitch, TOPSwitch, PI, PI Expert, PowiGaN, SCALE, SCALE-1, SCALE-2, SCALE-3 and SCALE-iDriver, are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2020, Power Integrations, Inc.

#### **Power Integrations Worldwide Sales Support Locations**

#### **World Headquarters**

5245 Hellyer Avenue San Jose, CA 95138, USA Main: +1-408-414-9200 Customer Service: Worldwide: +1-65-635-64480 Americas: +1-408-414-9621 e-mail: usasales@power.com

#### China (Shanghai)

Rm 2410, Charity Plaza, No. 88 North Caoxi Road Shanghai, PRC 200030 Phone: +86-21-6354-6323 e-mail: chinasales@power.com

#### China (Shenzhen)

17/F, Hivac Building, No. 2, Keji Nan 8th Road, Nanshan District, Shenzhen, China, 518057 Phone: +86-755-8672-8689 e-mail: chinasales@power.com

Germany (AC-DC/LED Sales) Einsteinring 24 85609 Dornach/Aschheim Germany Tel: +49-89-5527-39100

e-mail: eurosales@power.com **Germany** (Gate Driver Sales) HellwegForum 1 59469 Ense Germany

Tel: +49-2938-64-39990Phone: +81-45-471-1021e-mail: igbt-driver.sales@power.come-mail: japansales@power.com

# India

#1, 14th Main Road Vasanthanagar Bangalore-560052 India Phone: +91-80-4113-8020 e-mail: indiasales@power.com

#### Italy

Via Milanese 20, 3rd. Fl. 20099 Sesto San Giovanni (MI) Italy Phone: +39-024-550-8701 e-mail: eurosales@power.com

#### Japan

Korea

RM 602, 6FL

Yusen Shin-Yokohama 1-chome Bldg.Taiwan1-7-9, Shin-Yokohama, Kohoku-ku5F, No. 3Yokohama-shi,Nei Hu DKanagawa 222-0033 JapanTaipei 11Phone: +81-45-471-1021Phone: +80

Korea City Air Terminal B/D, 159-6

Samsung-Dong, Kangnam-Gu,

e-mail: koreasales@power.com

Seoul, 135-728, Korea

Phone: +82-2-2016-6610

Kohoku-ku5F, No. 318, Nei Hu Rd., Sec. 1<br/>Nei Hu Dist.apanTaipei 11493, Taiwan R.O.C.D21Phone: +886-2-2659-4570<br/>e-mail: taiwansales@power.com

#### UK

Singapore

51 Newton Road

Singapore, 308900

#19-01/05 Goldhill Plaza

Phone: +65-6358-2160

e-mail: singaporesales@power.com

Building 5, Suite 21 The Westbrook Centre Milton Road Cambridge CB4 1YG Phone: +44 (0) 7823-557484 e-mail: eurosales@power.com