## CLC431/432 Dual Wideband Monolithic Op Amp with Disable

## **General Description**

The CLC431 and CLC432 current-feedback amplifiers provide wide bandwidths and high slew rates for applications where board density and power are key considerations. These amplifiers provide DC-coupled small signal bandwidths exceeding 92MHz while consuming only 7mA per channel. Operating from  $\pm 15 V$  supplies, the CLC431/432's enhanced slew rate circuitry delivers large-signal bandwidths with output voltage swings up to  $28 V_{pp}$ . A wide range of bandwidth-insensitive gains are made possible by virtue of the CLC431 and CLC432's current-feedback topology.

The large common-mode input range and fast settling time (70ns to 0.05%) make these amplifiers well suited for CCD & data telecommunication applications. The disable of the CLC431 can accommodate ECL or TTL logic levels or a wide range of user definable inputs. With its fast enable/disable time (0.2 $\mu$ s/1 $\mu$ s) and high channel isolation of 70dB at 10MHz, the CLC431 can easily be configured as a 2:1 MUX. Many high performance video applications requiring signal gain and/or switching will be satisfied with the CLC431/432 due to their very low differential gain and phase errors (less than 0.1% and 0.1°; A<sub>V</sub> = +2V/V at 4.43MHz into 150 $\Omega$  load).

Quick 8ns rise and fall times on 10V pulses allow the CLC431/432 to drive either twisted pair or coaxial transmission lines over long distances.

The CLC431/432's combination of low input voltage noise, wide common-mode input voltage range and large output voltage swings make them especially well suited for wide dynamic range signal processing applications.

### **Features**

■ Wide bandwidth: 92MHz (A<sub>v</sub>=+1)

$62MHz (A_{V}=+2)$

■ Fast slew rate: 2000V/µs

Fast disable: 1µs to high-Z output

High channel isolation: 70dB at 10MHz

Single or dual supplies: ±5V to ±16.5V

## **Applications**

- Video signal multiplexing

- Twisted-pair differential driver

- CCD buffer & level shifting

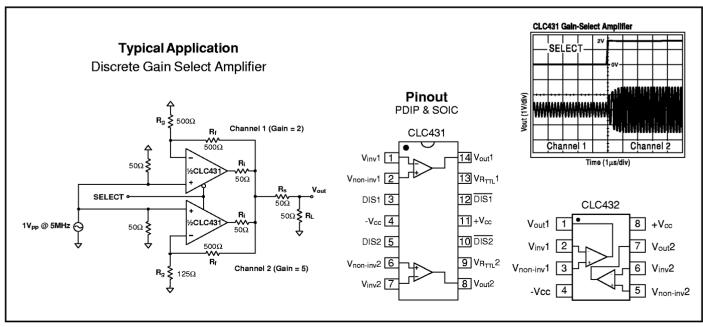

- Discrete gain-select amplifier

- Transimpedance amplifier

| CLC431/432 Electrical Characteristics ( $V_{cc} = \pm 15V$ ; $A_{v} = +2$ ; $R_{f} = R_{g} = 750\Omega$ ; $R_{L} = 100\Omega$ ; unless noted)                                                          |                                                                                                                                                                     |                                                        |                                                   |                                                           |                                                            |                                                                   | s noted)    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------|-------------|

| PARAMETERS                                                                                                                                                                                             | CONDITIONS                                                                                                                                                          | ТҮР                                                    | TYP MIN/MAX RATINGS                               |                                                           | UNITS                                                      | NOTES                                                             |             |

| Ambient Temperature                                                                                                                                                                                    | CLC431 & CLC432                                                                                                                                                     | +25                                                    | +25                                               | 0 to +70                                                  | -40 to +85                                                 | ∞                                                                 | 1           |

| FREQUENCY DOMAIN RESPO                                                                                                                                                                                 | $V_{out} < 4.0V_{pp}$                                                                                                                                               | 62                                                     | 42                                                | 37                                                        | 36                                                         | MHz                                                               |             |

| $V_{CC} = \pm 5V$                                                                                                                                                                                      | $V_{\text{out}} < 4.0V_{\text{pp}}$<br>$V_{\text{out}} < 10V_{\text{pp}}$                                                                                           | 62<br>28                                               | 21                                                | 20                                                        | 20                                                         | MHz<br>MHz                                                        | 2           |

| gain flatness peaking rolloff linear phase deviation differential gain differential phase                                                                                                              | $V_{\rm out}$ < $4.0V_{\rm pp}^{-}$<br>DC to 100MHz<br>DC to 20MHz<br>DC to 30MHz<br>$4.43$ MHz, $R_{\rm L}$ =150 $\Omega$<br>$4.43$ MHz, $R_{\rm L}$ =150 $\Omega$ | 0.05<br>0.0<br>0.3<br>0.12<br>0.12                     | 0.5<br>0.8<br>1.8<br>0.18<br>0.18                 | 0.7<br>0.8<br>2.0<br>0.2<br>0.23                          | 0.7<br>0.8<br>2.1<br>0.2<br>0.25                           | dB<br>dB<br>°                                                     |             |

| TIME DOMAIN RESPONSE rise and fall time overshoot settling time slew rate                                                                                                                              | 10V step<br>2V step<br>2V step to 0.05%<br>V <sub>out</sub> = ±10V                                                                                                  | 8<br>5<br>70<br>2000                                   | 12<br>10<br>100<br>1500                           | 13<br>12<br>110<br>1450                                   | 13<br>12<br>110<br>1400                                    | ns<br>%<br>ns<br>V/ms                                             | 2           |

| DISTORTION AND NOISE RES  2nd harmonic distortion  3rd harmonic distortion equivalent input noise                                                                                                      | SPONSE<br>2V <sub>pp</sub> , 1MHz<br>2V <sub>pp</sub> , 1MHz                                                                                                        | - 65<br>- 75                                           |                                                   |                                                           |                                                            | dBc<br>dBc                                                        | 6           |

| voltage<br>current, inverting<br>current, non-inverting                                                                                                                                                | >1MHz<br>>1MHz<br>>1MHz                                                                                                                                             | 3.3<br>13<br>2.0                                       | 4.2<br>16<br>2.5                                  | 4.4<br>17<br>2.6                                          | 4.5<br>18<br>2.8                                           | nV/√Hz<br>pA/√Hz<br>pA/√Hz                                        |             |

| input offset voltage average drift bias current, non-average drift bias current, inveraverage drift power supply rejection ratio common-mode rejection ratio supply current CLC431 disabled            | -                                                                                                                                                                   | 3<br>20<br>2<br>25<br>2<br>8<br>64<br>63<br>7.1<br>0.8 | 6<br><br>8<br><br>6<br><br>59<br>58<br>7.9<br>1.2 | 7<br>50<br>10<br>100<br>6<br>25<br>59<br>57<br>8.5<br>1.3 | 7<br>50<br>16<br>150<br>8<br>40<br>59<br>56<br>9.6<br>1.45 | mV<br>μV/°C<br>μA<br>nA/°C<br>μA<br>nA/°C<br>dB<br>dB<br>mA<br>mA | A<br>A<br>A |

| input voltage range resistance capacitance output current voltage range                                                                                                                                | ANCE common mode non-inverting non-inverting  R <sub>L</sub> ≥5kΩ R <sub>L</sub> =100Ω                                                                              | ± 12.2<br>24<br>0.5<br>± 60<br>± 14.0<br>± 6.0         | ± 12.0<br>16<br>1<br>± 38<br>± 13.6<br>± 3.7      | ±11.8<br>10<br>1<br>±35<br>±13.4<br>±3.7                  | ±11.6<br>6<br>1<br>±30<br>±13.2<br>±2.9                    | V<br>MΩ<br>pF<br>mA<br>V                                          |             |

| SWITCHING PERFORMANCE switching time  DIS logic levels    high input voltage (V <sub>IH</sub> )    low input voltage (V <sub>IL</sub> )    maximum current input  DIS-DIS     minimum differential vol | turn on turn off single-ended mode  V <sub>IH</sub> > DIS > V <sub>IL</sub> differential mode                                                                       | 0.1<br>0.7<br>> 2.0<br>< 0.8<br>150                    | 0.15<br>1.0<br>> 2.0<br>< 0.8<br>180<br>0.4       | 0.155<br>1.2<br>> 2.0<br>< 0.8<br>190<br>0.4              | 0.165<br>1.2<br>> 2.0<br>< 0.8<br>205                      | μs<br>μs<br>V<br>V<br>μA                                          | 3           |

| ISOLATION  crosstalk, input referred                                                                                                                                                                   | 10MHz                                                                                                                                                               | 70                                                     | 64                                                | 64                                                        | 64                                                         | dB                                                                |             |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

64

## Absolute Maximum Ratings

10MHz

±16.5V supply voltage short circuit current 100mA common-mode input voltage  $\pm V_{\infty}$ ±10V differential input voltage +200°C maximum junction temperature -65°C to+150°C storage temperature +300°C lead temperature (soldering 10 sec)

### Notes

60

∥ dB

- 1) Tested and guaranteed with  $R_f$  = 866 $\Omega$ . CLC432 tested and guaranteed with  $R_f = 750\Omega$ .

- 2) Spec is guaranteed for  $R_i \ge 500\Omega$ .

60

3) V<sub>RTIL</sub>= 0, See text for single-ended mode of operation. 4) V<sub>RTIL</sub>= NC, See text for differential mode of operation 5) Spec is guaranteed for AJE; AJP & AIB yield 7dB lower.

60

- 6) Spec is tested with  $2V_{pp}$ , 10MHz and  $R_L$ = 100 $\Omega$ . A) J-level: spec is 100% tested at +25°C.

2

off isolation

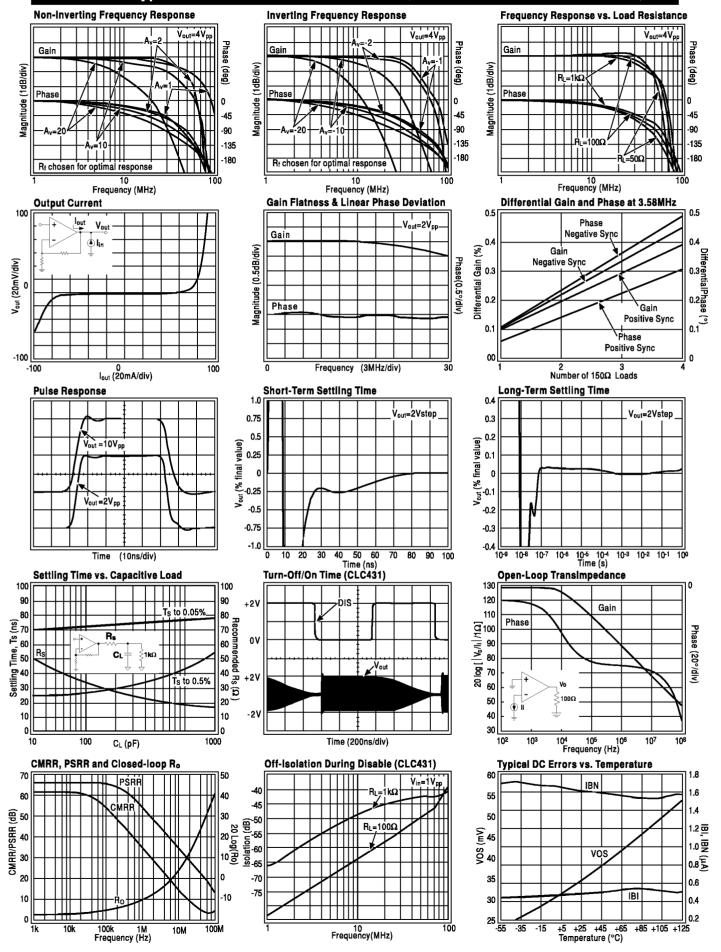

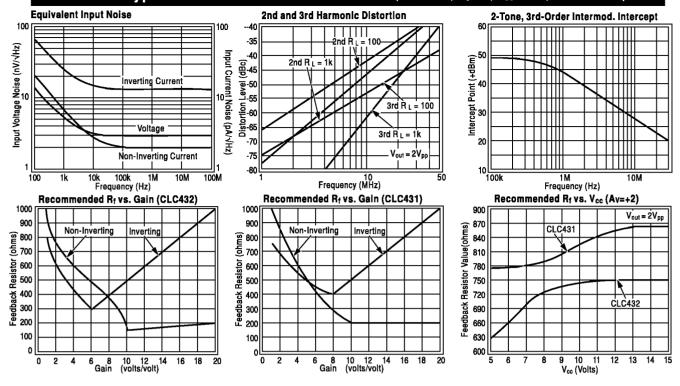

## CLC431/432 Typical Performance Characteristics (T<sub>A</sub>=+25°C, A<sub>V</sub>=+2, V<sub>CC</sub>=±15V, unless noted)

## CLC431/432 Typical Performance Characteristics (TA=+25°C, Av=+2, Vcc=±15V, unless noted)

## **Application Discussion**

#### Introduction

The CLC431 and the CLC432 are dual wideband current-feedback op amps that operate from single (+10V to +33V) or dual ( $\pm$ 5V to  $\pm$ 16.5) power supplies. The CLC431 is equipped with a disable feature and is offered in 14-pin DIP and SOIC packages. The CLC432 is packaged in a standard 8-pin dual pinout and is offered in an8-pin DIP and SOIC. Evaluation boards are available for each version of both devices. The evaluation boards can assist in the device and/or application evaluation and were used to generate the typical device performance plots on the preceding pages.

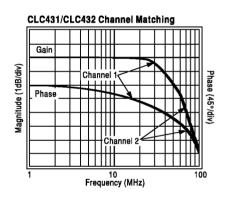

Each of the CLC431/CLC432's dual channels provide closely matched DC & AC electrical performance characteristics making them ideal choices for wideband signal processing. The CLC431, with its disable feature, can easily be configured as a 2:1 mux or several can be used to form a 10:1 mux without performance degradation. The two closely-matched channels of the CLC432 can be combined to form composite circuits for such applications as filter blocks, integrators, transimpedance amplifiers and differential line drivers and receivers.

### **Feedback Resistor Selection**

The loop gain and frequency response for a current-feedback operational amplifier is determined largely by the feedback resistor ( $R_f$ ). Package parasitics also influence ac response. Since the package parasitics of the CLC431 and the CLC432 are different, the optimum frequency and phase responses are obtained with different values of feedback resistor (for  $A_V$ =+2; CLC431:  $R_f$ =866 $\Omega$ , CLC432:  $R_f$ =750 $\Omega$ ). The Electrical Characteristics and

Typical Performance plots are valid for both devices under the specified conditions. Generally, lowering  $R_{\rm f}$  from its recommended value will peak the frequency response and extend the bandwidth while increasing its value will roll off the response. Reducing the value of  $R_{\rm f}$  too far below its recommended value will cause overshoot, ringing and eventually oscillation. For more information see Application Note OA-20 and OA-13.

In order to optimize the devices' frequency and phase response for gains other than +2V/V it is recommended to adjust the value of the feedback resistor. The two plots found in the Typical Performance section entitled "Recommended R<sub>f</sub> vs. Gain" provide the means of selecting the feedback-resistor value that optimizes frequency and phase response over the CLC431/ CLC432's gain range. Both plots show the value of R<sub>f</sub> approaching a nonzero minimum at high non-inverting gains, which is characteristic of current-feedback op amps and yields best results. The linear portion of the two R<sub>f</sub> vs. Inverting-gain curves results from the limitation placed on  $R_q$  (i.e.  $R_q \ge 50\Omega$ ) in order to maintain an adequate input impedance for the inverting configuration. It should be noted that for stable operation a noninverting gain of +1 requires an  $R_{\!\scriptscriptstyle f}$  equal to  $1k\Omega$  for both the CLC431 and the CLC432.

### **CLC431 Disable Feature**

The CLC431 disable feature can be operated either single-endedly or differentially thereby accommodating a wide range of logic families. There are three pins associated with the disable feature of each of the CLC431's two amplifiers: DIS,  $\overline{\text{DIS}}$  and  $V_{\text{RTIL}}$  (please see pinout on

front page). Also note that both amplifiers are guaranteed to be enabled if all three of these pins are unconnected.

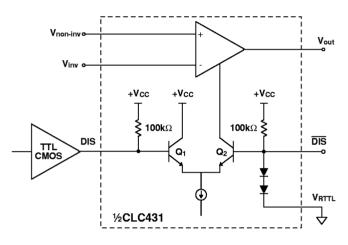

Fig. 1 illustrates the single-ended mode of the CLC431's disable feature for logic families such as TTL and CMOS. In order to operate properly,  $V_{RTTL}$  must be grounded, thereby biasing  $\overline{D}$ IS to approximately +1.4V through the two internal series diodes. For single-ended operation,  $\overline{D}$ IS should be left floating. Applying a TTL or CMOS logic "high" (i.e. >2.0Volts) to DIS will switch the tail current of the differential pair to Q1 and "shut down" Q2 which results in the *disabling* of that channel of the CLC431. Alternatively, applying a logic "low" (i.e. <0.8Volts) to DIS will switch the tail current from Q1 to Q2 effectively *enabling* that channel. If DIS is left floating under single-ended operation, then the associated amplifier is guaranteed to be *disabled*.

Fig. 1

The disable feature of the CLC431 is such that DIS and  $\overline{\text{DIS}}$  have common-mode input voltage ranges of (+V<sub>CC</sub>) to (-V<sub>CC</sub>+3V) and are so guaranteed over the commercial temperature range. Internal clamps (not shown) protect the DIS input from excessive input voltages that could otherwise cause damage to the device. This condition occurs when enough source current flows into the node so as to allow DIS to rise to V<sub>CC</sub>. This clamp is activated once DIS exceeds  $\overline{\text{DIS}}$  by 1.5Volts and guarantees that V<sub>DIS</sub> (ground referenced) does not exceed 4.7Volts.

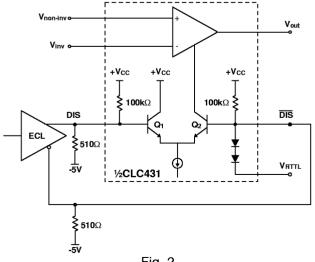

Fig. 2

Fig. 2 illustrates the differential mode of the CLC431's disable feature for ECL-type logic. In order for this mode to operate properly,  $V_{RTTL}$  must be left floating while DIS and  $\overline{DIS}$  are to be connected directly to the ECL gate as illustrated. Applying a differential logic "high" (DIS -  $\overline{DIS}$   $\geq$  0.4Volts) switches the tail current of the differential pair from Q2 to Q1 and results in the *disabling* of that CLC431 channel. Alternatively, applying a differential logic "low" (DIS -  $\overline{DIS}$   $\leq$  -0.4Volts) switches the tail current of the differential pair from Q1 to Q2 and results in the *enabling* of that same channel. The internal clamp, mentioned above, also protects against excessive differential voltages up to 30Volts while limiting input currents to <3mA.

### **DC Performance**

A current-feedback amplifier's input stage does not have equal nor correlated bias currents, therefore they cannot be cancelled and each contributes to the total DC offset voltage at the output by the following equation:

$$V_{\text{offset}} = \pm \left(I_{\text{bn}} * R_{\text{s}} \left(1 + \frac{R_{\text{f}}}{R_{\text{g}}}\right) + V_{\text{io}} \left(1 + \frac{R_{\text{f}}}{R_{\text{g}}}\right) + I_{\text{bi}} * R_{\text{f}}\right)$$

The input resistor  $R_{\rm s}$  is that resistance seen when looking from the non-inverting input back towards the source. For inverting DC-offset calculations, the source resistance seen by the input resistor  $R_{\rm g}$  must be included in the output offset calculation as a part of the non-inverting gain equation. Application note OA-7 gives several circuits for DC offset correction.

### **Layout Considerations**

It is recommended that the decoupling capacitors  $(0.1\mu F)$  ceramic and  $6.8\mu F$  electrolytic) should be placed as close as possible to the power supply pins to insure a proper high-frequency low impedance bypass. Careful attention to circuit board layout is also necessary for best performance. Of particular importance is the control of parasitic capacitances (to ground) at the output and invering input pins. See CLC431/432 Evaluation Board literature for more information.

# Applications Circuits 2:1 Video Mux (CLC431)

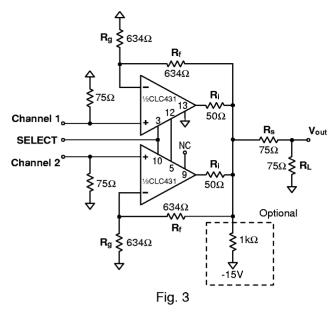

Fig. 3 illustrates the connections necessary to configure the CLC431 as a 2:1 multiplexer in a 75 $\Omega$  system. Each of the two CLC431's amplifiers is configured with a noninverting gain of +2V/V using  $634\Omega$  feedback (R<sub>f</sub>) and gain-setting  $(R_a)$  resistors. The feedback resistor value is lower than that recommended in order to compensate for the reduction of loop-gain that results from the inclusion of the  $50\Omega$  resistor (R<sub>i</sub>) in the feedback loop. This  $50\Omega$ resistor serves to isolate the output of the active channel from the impedance of the inactive channel yet does not affect the low output impedance of the active channel. Notice that for proper operation  $V_{RTTL}$  1 (pin 13) is grounded and  $V_{\text{\tiny RTTL}}2$  (pin 9) is unconnected. The pins associated with the disable feature are to be connected as follows: DIS1 and DIS2 (pins 3 & 10) are connected together as well as DIS2 and  $\overline{DIS1}$  (pins 5 & 12). Channel 1 is selected with the application of a logic "low" to SELECT while a logic "high" selects Channel 2.

The optional  $1k\Omega$  pull-down resistor connected from the output of the 2:1 mux to the negative power supply (-V<sub>CC</sub>) results in improved differential gain and phase performance (0.02% and 0.01°) at PAL video levels.

### **Switched Gain Amplifier (CLC431)**

As seen from the front page, the CLC431 can also be configured as a switched-gain amplifier that is similar to the 2:1 mux. Configuring each of the two CLC431's amplifiers with different non-inverting gains and tying the two inputs together (eliminating one of the input-terminating resistors) allows the CLC431 to switch an input signal between two different gains.

### **Inactive Channel Impedances (CLC431)**

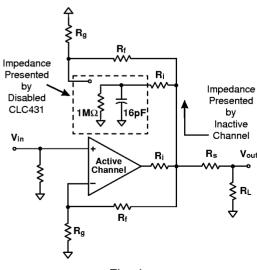

The impedance that is seen when looking into the output of a disabled CLC431 is typically represented as  $1M\Omega||16pF.$  The inverting input impedance becomes very high, essentially open. Therefore, the impedance presented by a disabled channel is  $(R_f + R_g)|| (R_i + (1M\Omega||16pF))$  as illustrated in Fig. 4. It should also be noted that any trace capacitance that is associated with the common output connection will add in parallel to that presented by the CLC431's inactive channel.

Fig. 4

### Twisted-Pair Driver.

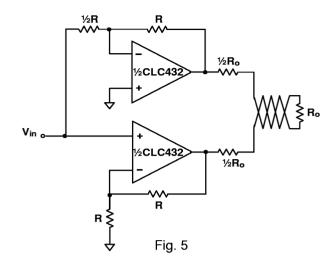

Twisted-pair cables are used in many applications such as telephony, video and data communications. The CLC432's two matched channels make it well suited for such applications and is illustrated in Fig. 5.

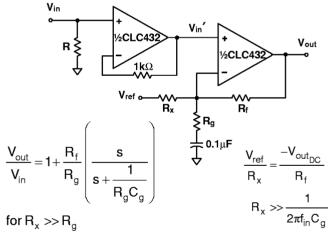

### **CCD Amplifier.**

The CLC432 can easily be configured as 10MSPS CCD amplifier with DC level shifting as illustrated in Fig 6. Notice that one of the CLC432's channels buffers the CCD output while the other channel is configured with both an inverting DC gain and an AC gain in order to achieve the overall transfer function shown in Fig. 6.

Fig. 6

## Ordering Information

| Model                         | Temperature Range | Description                |  |  |  |  |

|-------------------------------|-------------------|----------------------------|--|--|--|--|

| CLC431AJP                     | -40°C to +85°C    | 14-pin PDIP                |  |  |  |  |

| CLC431AJE                     | -40°C to +85°C    | 14-pin SOIC                |  |  |  |  |

| CLC431ALC                     | -40°C to +85°C    | dice                       |  |  |  |  |

| CLC431A8B                     | -55°C to +125°C   | 14-pin CerDIP, MIL-STD-883 |  |  |  |  |

| CLC431AMC                     | -55°C to +125°C   | dice, MIL-STD-883          |  |  |  |  |

| CLC432AJP                     | -40°C to +85°C    | 8-pin PDIP                 |  |  |  |  |

| CLC432AJE                     | -40°C to +85°C    | 8-pin SOIC                 |  |  |  |  |

| CLC432ALC                     | -40°C to +85°C    | dice                       |  |  |  |  |

| CLC432A8B                     | -55°C to +125°C   | 8-pin CerDIP, MIL-STD-883  |  |  |  |  |

| CLC432AMC                     | -55°C to +125°C   | dice, MIL-STD-883          |  |  |  |  |

| DESC SMD numbers: 5962-94725. |                   |                            |  |  |  |  |

http://www.national.com

6

# Reliability Information

Transistor count 37

| Package Thermal Resistance |                      |                         |  |  |  |

|----------------------------|----------------------|-------------------------|--|--|--|

| CLC431 Package             | $\theta_{\text{JC}}$ | $\theta_{JA}$           |  |  |  |

| AJP<br>AJE<br>CERDIP       | 55°C<br>35°C<br>25°C | 100°C<br>105°C<br>80°C  |  |  |  |

| CLC432 Package             |                      |                         |  |  |  |

| AJP<br>AJE<br>CERDIP       | 55°C<br>40°C<br>25°C | 110°C<br>115°C<br>115°C |  |  |  |

### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

### **Life Support Policy**

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### National Semiconductor Corporation

1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

### National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

### National Semiconductor Hong Kong Ltd.

13th Floor, Straight Block Ocean Centre, 5 Canton Road Tsimshatsui, Kowloon Hong Kong

Tel: (852) 2737-1600 Fax: (852) 2736-9960

### National Semiconductor Japan Ltd.

Tel: 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.