National Semiconductor is now part of

Texas Instruments.

Search <u>http://www.ti.com/</u> for the latest technical

information and details on our current products and services.

M3500 Synchronous Step-up DC/DC Converter for White LED Applications

# LM3500 Synchronous Step-up DC/DC Converter for White LED Applications

### **General Description**

The LM3500 is a fixed-frequency step-up DC/DC converter that is ideal for driving white LEDs for display backlighting and other lighting functions. With fully intergrated synchronous switching (no external schottky diode required) and a low feedback voltage (500mV), power efficiency of the LM3500 circuit has been optimized for lighting applications in wireless phones and other portable products (single cell Li-Ion or 3-cell NiMH battery supplies). The LM3500 operates with a fixed 1MHz switching frequency. When used with ceramic input and output capacitors, the LM3500 provides a small, low-noise, low-cost solution.

Two LM3500 options are available with different output voltage capabilities. The LM3500-21 has a maximum output voltage of 21V and is typically suited for driving 4 or 5 white LEDs in series. The LM3500-16 has a maximum output voltage of 16V and is typically suited for driving 3 or 4 white LEDs in series (maximum number of series LEDs dependent on LED forward voltage). If the primary white LED network should be disconnected, the LM3500 uses internal protection circuitry on the output to prevent a destructive over-voltage event.

A single external resistor is used to set the maximum LED current in LED-drive applications. The LED current can easily be adjusted using a pulse width modulated (PWM) signal on the shutdown pin. In shutdown, the LM3500 completely disconnects the input from output, creating total isolation and preventing any leakage currents from trickling into the LEDs.

### Features

- Synchronous rectification, high efficiency and no external schottky diode required

- Uses small surface mount components

- Can drive 2-5 white LEDs in series (may function with more low-V<sub>F</sub> LEDs)

- 2.7V to 7V input range

- Internal output over-voltage protection (OVP) circuitry, with no external zener diode required LM3500-16: 15.5V OVP: LM3500-21: 20.5V OVP.

- True shutdown isolation

- Input undervoltage lockout

- Requires only small ceramic capacitors at the input and output

- Thermal Shutdown

- 0.1µA shutdown current

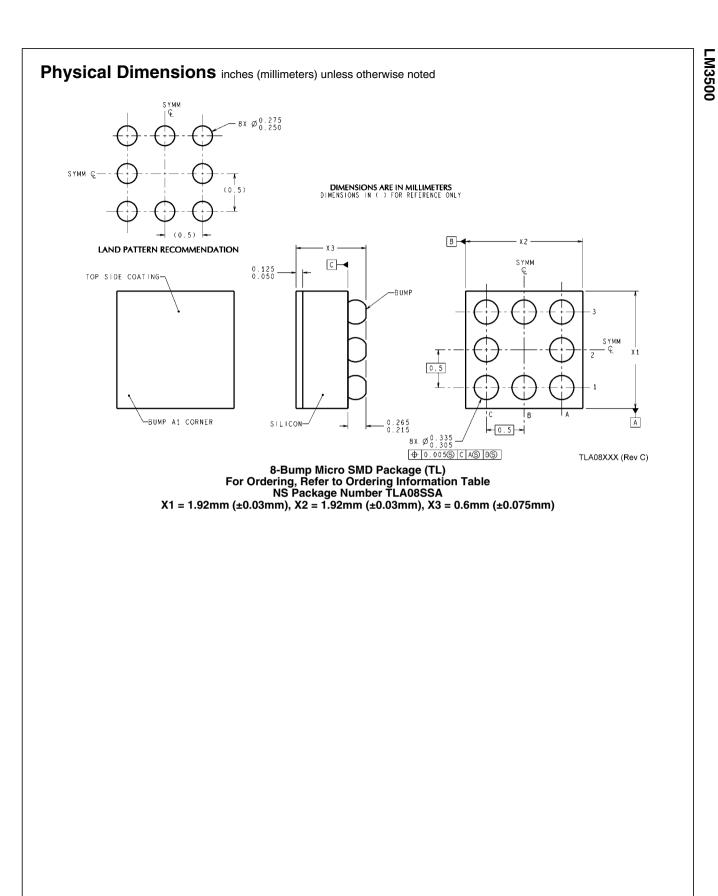

- Small 8-bump thin micro SMD package

## Applications

- LCD Bias Supplies

- White LED Backlighting

- Handheld Devices

- Digital Cameras

- Portable Applications

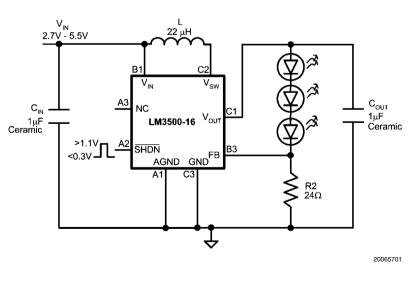

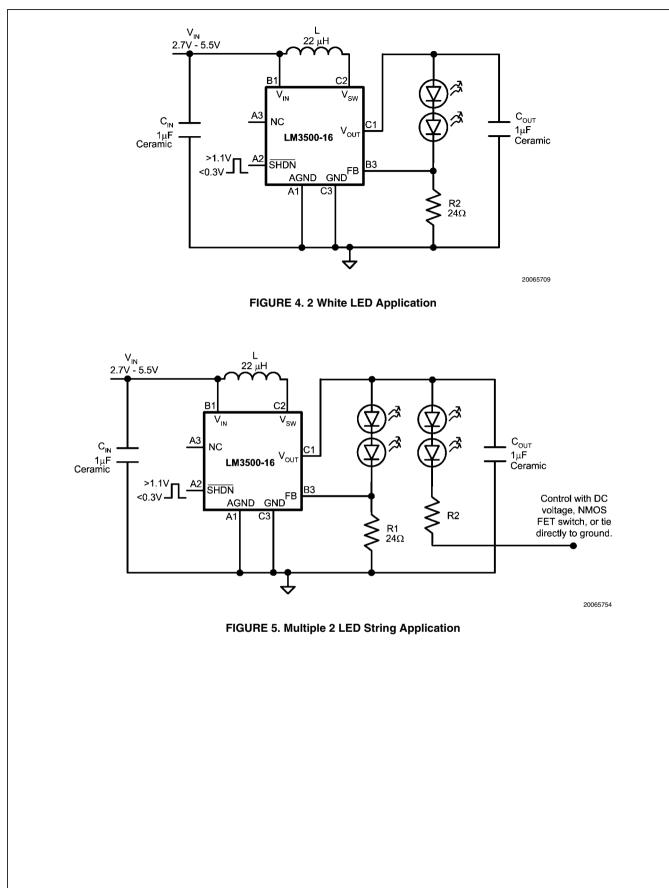

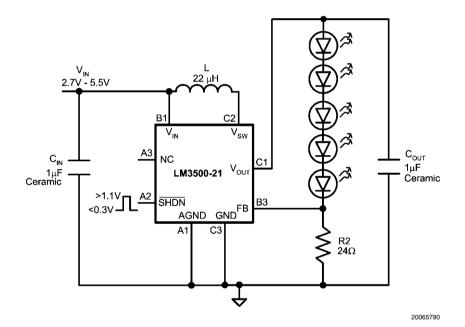

# **Typical Application Circuit**

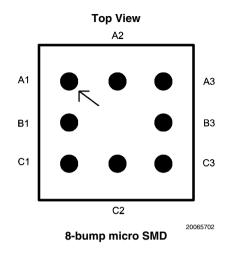

## **Connection Diagram**

## **Ordering Information**

| Maximum<br>Output Voltage | Order Number | Package Type | NSC Package<br>Drawing | Top Mark | Supplied As               |  |

|---------------------------|--------------|--------------|------------------------|----------|---------------------------|--|

| 16V                       | LM3500TL-16  | micro SMD    | TL08SSA                | S18      | 250 Units, Tape and Reel  |  |

| 16V                       | LM3500TLX-16 | micro SMD    | TL08SSA                | S18      | 3000 Units, Tape and Reel |  |

| 21V                       | LM3500TL-21  | micro SMD    | TL08SSA                | S23      | 250 Units, Tape and Reel  |  |

| 21V                       | LM3500TLX-21 | micro SMD    | TL08SSA                | S23      | 3000 Units, Tape and Reel |  |

## **Pin Description/Functions**

| Pin | Name             | Function                                                           |

|-----|------------------|--------------------------------------------------------------------|

| A1  | AGND             | Analog ground.                                                     |

| B1  | V <sub>IN</sub>  | Analog and Power supply input.                                     |

| C1  | V <sub>OUT</sub> | PMOS source connection for synchronous rectification.              |

| C2  | V <sub>SW</sub>  | Switch pin. Drain connections of both NMOS and PMOS power devices. |

| C3  | GND              | Power Ground.                                                      |

| B3  | FB               | Output voltage feedback connection.                                |

| A3  | NC               | No internal connection made to this pin.                           |

| A2  | SHDN             | Shutdown control pin.                                              |

**AGND(pin A1):** Analog ground pin. The analog ground pin should tie directly to the GND pin.

$V_{IN}(pin \ B1)$ : Analog and Power supply pin. Bypass this pin with a capacitor, as close to the device as possible, connected between the  $V_{IN}$  and GND pins.

$V_{\text{OUT}}(\text{pin C1})$ : Source connection of internal PMOS power device. Connect the output capacitor between the  $V_{\text{OUT}}$  and GND pins as close as possible to the device.

$V_{SW}(\text{pin C2})\text{:}$  Drain connection of internal NMOS and PMOS switch devices. Keep the inductor connection close to this pin to minimize EMI radiation.

GND(pin C3): Power ground pin. Tie directly to ground plane.

**FB(pin B3):** Output voltage feedback connection. Set the primary White LED network current with a resistor from the FB pin to GND. Keep the current setting resistor close to the device and connected between the FB and GND pins.

**NC(pin A3):** No internal connection is made to this pin. The maximum allowable voltage that can be applied to this pin is 7.5V.

**SHDN(pin A2):** Shutdown control pin. Disable the device with a voltage less than 0.3V and enable the device with a voltage greater than 1.1V. The white LED current can be controlled using a PWM signal at this pin. There is an internal pull down on the SHDN pin, the device is in a normally off state.

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| V <sub>IN</sub>                                      | -0.3V to 7.5V                   |

|------------------------------------------------------|---------------------------------|

| V <sub>OUT</sub> (LM3500-16)(Note 2)                 | –0.3V to 16V                    |

| V <sub>OUT</sub> (LM3500-21)(Note 2)                 | -0.3V to 21V                    |

| V <sub>SW</sub> (Note 2)                             | –0.3V to V <sub>OUT</sub> +0.3V |

| FB, SHDN, and NC Voltages                            | -0.3V to 7.5V                   |

| Maximum Junction Temperature                         | 150°C                           |

| Lead Temperature<br>(Note 3)<br>ESD Ratings (Note 4) | 300°C                           |

| Human Body Model<br>Machine Model                    | 2kV<br>200V                     |

# **Operating Conditions**

Ambient Temperature (Note 5) Junction Temperature Supply Voltage

-40°C to +85°C -40°C to +125°C 2.7V to 7V

## **Thermal Properties**

Junction to Ambient Thermal Resistance  $(\theta_{JA})$ (Note 6)

75°C/W

## **Electrical Characteristics**

Specifications in standard type face are for  $T_A = 25^{\circ}$ C and those in **boldface type** apply over the Operating Temperature Range of  $T_A = -10^{\circ}$ C to +85^{\circ}C. Unless otherwise specified  $V_{IN} = 2.7$ V and specification apply to both LM3500-16 and LM3500-21.

| Symbol             | Parameter                                  | Conditions                                                  | Min<br>(Note 7) | Typ<br>(Note 8) | Max<br>(Note 7) | Units |  |

|--------------------|--------------------------------------------|-------------------------------------------------------------|-----------------|-----------------|-----------------|-------|--|

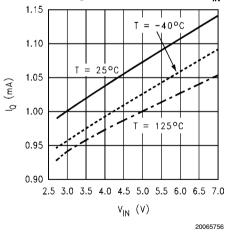

| l <sub>Q</sub>     | Quiescent Current, Device Not<br>Switching | FB > 0.54V                                                  |                 | 0.95            | 1.2             | mA    |  |

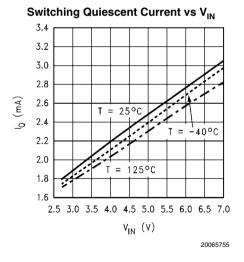

|                    | Quiescent Current, Device<br>Switching     | FB = 0V                                                     |                 | 1.8             | 2.5             |       |  |

|                    | Shutdown                                   | SHDN = 0V                                                   |                 | 0.1             | 2               | μA    |  |

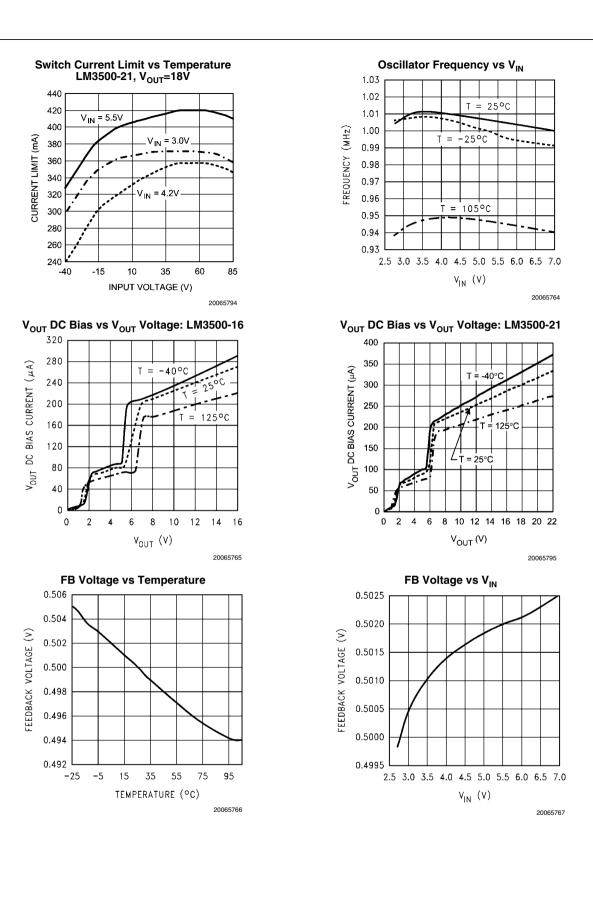

| V <sub>FB</sub>    | Feedback Voltage                           | $V_{IN} = 2.7V$ to 7V                                       | 0.47            | 0.5             | 0.53            | V     |  |

| ΔV <sub>FB</sub>   | Feedback Voltage Line<br>Regulation        | $V_{IN} = 2.7V$ to 7V                                       |                 | 0.1             | 0.4             | %/V   |  |

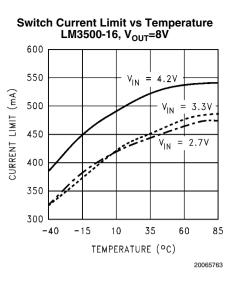

| CL                 | Switch Current Limit<br>(LM3500-16)        | V <sub>IN</sub> = 2.7V,<br>Duty Cycle = 80%                 | 275             | 400             | 480             |       |  |

|                    |                                            | V <sub>IN</sub> = 3.0V,<br>Duty Cycle = 70%                 | 255             | 400             | 530             |       |  |

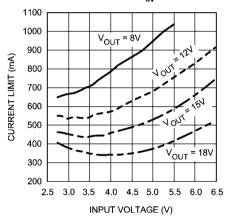

|                    | Switch Current Limit<br>(LM3500-21)        | V <sub>IN</sub> = 2.7V,<br>Duty Cycle = 70%                 | 420             | 640             | 770             | mA    |  |

|                    |                                            | V <sub>IN</sub> = 3.0V,<br>Duty Cycle = 63%                 | 450             | 670             | 800             |       |  |

| B                  | FB Pin Bias Current                        | FB = 0.5V (Note 9)                                          |                 | 45              | 200             | nA    |  |

| V <sub>IN</sub>    | Input Voltage Range                        |                                                             | 2.7             |                 | 7.0             | V     |  |

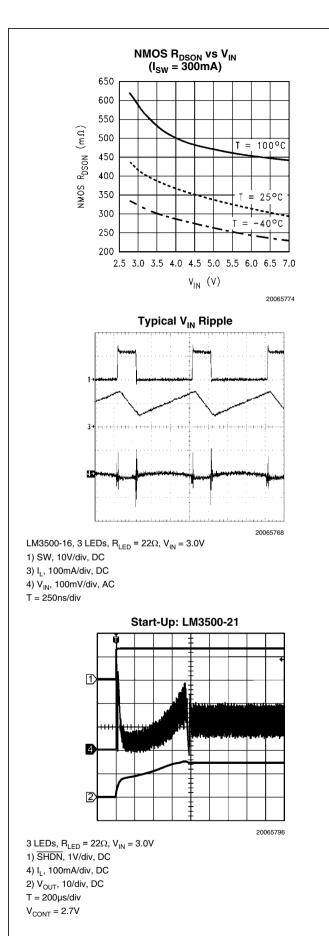

| R <sub>DSON</sub>  | NMOS Switch R <sub>DSON</sub>              | S Switch $R_{DSON}$ $V_{IN} = 2.7V, I_{SW} = 300 \text{mA}$ |                 |                 | 0.43            | 0     |  |

|                    | PMOS Switch R <sub>DSON</sub>              | V <sub>OUT</sub> = 6V, I <sub>SW</sub> = 300mA              |                 | 1.1             | 2.3             | Ω     |  |

| D <sub>Limit</sub> | Duty Cycle Limit (LM3500-16)               | FB = 0V                                                     | 80              | 87              |                 | 0/    |  |

|                    | Duty Cycle Limit (LM3500-21)               | FB = 0V                                                     | 85              | 94              |                 | %     |  |

| F <sub>sw</sub>    | Switching Frequency                        |                                                             | 0.85            | 1.0             | 1.15            | MHz   |  |

| SD                 | SHDN Pin Current (Note 10)                 | <u>SHDN</u> = 5.5V                                          |                 | 18              | 30              |       |  |

|                    |                                            | <u>SHDN</u> = 2.7V                                          | 9 10            |                 | 16              | μA    |  |

|                    |                                            | SHDN = GND                                                  |                 | 0.1             |                 |       |  |

| I <sub>L</sub>     | Switch Leakage Current (LM3500-16)         | V <sub>SW</sub> = 15V                                       |                 | 0.01            | 0.5             | μA    |  |

|                    | Switch Leakage Current<br>(LM3500-21)      | V <sub>SW</sub> = 20V                                       |                 | 0.01            | 2.0             |       |  |

| UVP                | Input Undervoltage Lockout                 | ON Threshold                                                | 2.4             | 2.5             | 2.6             | V     |  |

|                    |                                            | OFF Threshold                                               | 2.3             | 2.4             | 2.5             | V     |  |

| Symbol            | Parameter                                    | arameter Conditions                               |     | Typ<br>(Note 8) | Max<br>(Note 7) | Units |  |

|-------------------|----------------------------------------------|---------------------------------------------------|-----|-----------------|-----------------|-------|--|

| OVP               | Output Overvoltage Protection                | ON Threshold                                      | 15  | 15.5            | 16              |       |  |

|                   | (LM3500-16)                                  | OFF Threshold                                     | 14  | 14.6            | 15              |       |  |

|                   | Output Overvoltage Protection                | ON Threshold                                      | 20  | 20.5            | 21              | V     |  |

|                   | (LM3500-21)                                  | OFF Threshold                                     | 19  | 19.5            | 20              |       |  |

| I <sub>Vout</sub> | V <sub>OUT</sub> Bias Current<br>(LM3500-16) | $V_{OUT} = 15V, \overline{SHDN} = V_{IN}$         |     | 260             | 400             |       |  |

|                   | V <sub>OUT</sub> Bias Current<br>(LM3500-21) | $V_{OUT} = 20V, \overline{SHDN} = V_{IN}$         |     | 300             | 460             | μA    |  |

| I <sub>VL</sub>   | PMOS Switch Leakage<br>Current (LM3500-16)   | V <sub>OUT</sub> = 15V, V <sub>SW</sub> = 0V      |     | 0.01            | 3               |       |  |

|                   | PMOS Switch Leakage<br>Current (LM3500-21)   | V <sub>OUT</sub> = 20V, V <sub>SW</sub> = 0V 0.01 |     | 0.01            | 3               | μA    |  |

| SHDN              | SHDN Low                                     |                                                   |     | 0.65            | 0.3             | v     |  |

| Threshold         | SHDN High                                    |                                                   | 1.1 | 0.65            |                 | v     |  |

Specifications in standard type face are for  $T_J = 25^{\circ}$ C and those in **boldface type** apply over the full **Operating Temperature Range (T<sub>J</sub> = -40°C to +125°C)**. Unless otherwise specified V<sub>IN</sub> =2.7V and specification apply to both LM3500-16 and LM3500-21.

| Symbol             | Parameter                                  | Conditions                                      | Min<br>(Note 7) | Typ<br>(Note 8) | Max<br>(Note 7) | Units |  |

|--------------------|--------------------------------------------|-------------------------------------------------|-----------------|-----------------|-----------------|-------|--|

| Ι <sub>Q</sub>     | Quiescent Current, Device Not<br>Switching | FB > 0.54V                                      |                 | 0.95            | 1.2             | ٣A    |  |

|                    | Quiescent Current, Device<br>Switching     | FB = 0V                                         |                 | 1.8             | 2.5             | mA    |  |

|                    | Shutdown                                   | SHDN = 0V                                       |                 | 0.1             | 2               | μA    |  |

| V <sub>FB</sub>    | Feedback Voltage                           | V <sub>IN</sub> = 2.7V to 7V                    | 0.47            | 0.5             | 0.53            | V     |  |

| $\Delta V_{FB}$    | Feedback Voltage Line<br>Regulation        | V <sub>IN</sub> = 2.7V to 7V                    |                 | 0.1             | 0.4             | %/V   |  |

| I <sub>CL</sub>    | Switch Current Limit<br>(LM3500-16)        | $V_{IN} = 3.0V$ , Duty Cycle = 70%              |                 | 400             |                 | 0     |  |

|                    | Switch Current Limit<br>(LM3500-21)        | $V_{IN} = 3.0V$ , Duty Cycle = 63%              |                 | 670             |                 | mA    |  |

| I <sub>B</sub>     | FB Pin Bias Current                        | FB = 0.5V (Note 9)                              |                 | 45              | 200             | nA    |  |

| V <sub>IN</sub>    | Input Voltage Range                        |                                                 | 2.7             |                 | 7.0             | V     |  |

| R <sub>DSON</sub>  | NMOS Switch R <sub>DSON</sub>              | V <sub>IN</sub> = 2.7V, I <sub>SW</sub> = 300mA |                 |                 | 0.43            |       |  |

|                    | PMOS Switch R <sub>DSON</sub>              | V <sub>OUT</sub> = 6V, I <sub>SW</sub> = 300mA  |                 | 1.1             | 2.3             | Ω     |  |

| D <sub>Limit</sub> | Duty Cycle Limit (LM3500-16)               | FB = 0V                                         |                 | 87              |                 | %     |  |

|                    | Duty Cycle Limit (LM3500-21)               | FB = 0V                                         |                 | 94              |                 |       |  |

| F <sub>SW</sub>    | Switching Frequency                        |                                                 | 0.8             | 1.0             | 1.2             | MHz   |  |

| I <sub>SD</sub>    | SHDN Pin Current (Note 10)                 | <u>SHDN</u> = 5.5V                              |                 | 18              | 30              |       |  |

|                    |                                            | SHDN = 2.7V                                     |                 | 9               | 16              | μA    |  |

|                    |                                            | SHDN = GND                                      |                 | 0.1             |                 |       |  |

| I <sub>L</sub>     | Switch Leakage Current (LM3500-16)         | V <sub>SW</sub> = 15V                           |                 | 0.01            | 0.5             | μA    |  |

|                    | Switch Leakage Current (LM3500-21)         | V <sub>SW</sub> = 20V                           |                 | 0.01            | 2.0             |       |  |

| UVP                | Input Undervoltage Lockout                 | ON Threshold                                    | 2.4             | 2.5             | 2.6             | V     |  |

|                    |                                            | OFF Threshold                                   | 2.3             | 2.4             | 2.5             | V     |  |

| OVP                | Output Overvoltage Protection              | ON Threshold                                    | 15              | 15.5            | 16              |       |  |

|                    | (LM3500-16)                                | OFF Threshold                                   | 14              | 14.6            | 15              | l v   |  |

|                    | Output Overvoltage Protection              | ON Threshold                                    | 20              | 20.5            | 21              |       |  |

|                    | (LM3500-21)                                | OFF Threshold                                   | 19              | 19.5            | 20              |       |  |

| Symbol            | Parameter                                    | Conditions                                | Min<br>(Note 7) | Typ<br>(Note 8) | Max<br>(Note 7) | Units |  |

|-------------------|----------------------------------------------|-------------------------------------------|-----------------|-----------------|-----------------|-------|--|

| I <sub>Vout</sub> | V <sub>OUT</sub> Bias Current<br>(LM3500-16) | $V_{OUT} = 15V, \overline{SHDN} = V_{IN}$ |                 | 260             | 400             |       |  |

|                   | V <sub>OUT</sub> Bias Current<br>(LM3500-21) | $V_{OUT} = 20V, \overline{SHDN} = V_{IN}$ |                 | 300             | μ/<br>460       |       |  |

| I <sub>VL</sub>   | PMOS Switch Leakage<br>Current (LM3500-16)   | $V_{OUT} = 15V, V_{SW} = 0V$              |                 | 0.01            | 3               |       |  |

|                   | PMOS Switch Leakage<br>Current (LM3500-21)   | $V_{OUT} = 20V, V_{SW} = 0V$              |                 | 0.01            | 3               | μA    |  |

| SHDN              | SHDN Low                                     |                                           |                 | 0.65            | 0.3             | V     |  |

| Threshold         | SHDN High                                    |                                           | 1.1             | 0.65            |                 | 7 V   |  |

Note 1: Absolute maximum ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is intended to be functional, but device parameter specifications may not be guaranteed. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: This condition applies if  $V_{IN} < V_{OUT}$ . If  $V_{IN} > V_{OUT}$ , a voltage greater than  $V_{IN} + 0.3V$  should not be applied to the  $V_{OUT}$  or  $V_{SW}$  pins.

Note 3: For more detailed soldering information and specifications, please refer to National Semiconductor Application Note 1112: Micro SMD Wafer Level Chip Scale Package (AN-1112), available at www.national.com.

Note 4: The human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin.

**Note 5:** In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A-MAX})$  is dependent on the maximum operating junction temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ , the maximum power dissipation of the device in the application  $(P_{D-MAX})$ , and the junction-to ambient thermal resistance of the part/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

Note 6: Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) is highly application and board-layout dependent. The 75°C/W figure provided was measured on a 4-layer test board conforming to JEDEC standards. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues when designing the board layout.

Note 7: All limits guaranteed at room temperature (standard typeface) and at temperature extremes (bold typeface). All room temperature limits are production tested, guaranteed through statistical analysis or guaranteed by design. All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 8: Typical numbers are at 25°C and represent the most likely norm.

Note 9: Feedback current flows out of the pin.

Note 10: Current flows into the pin.

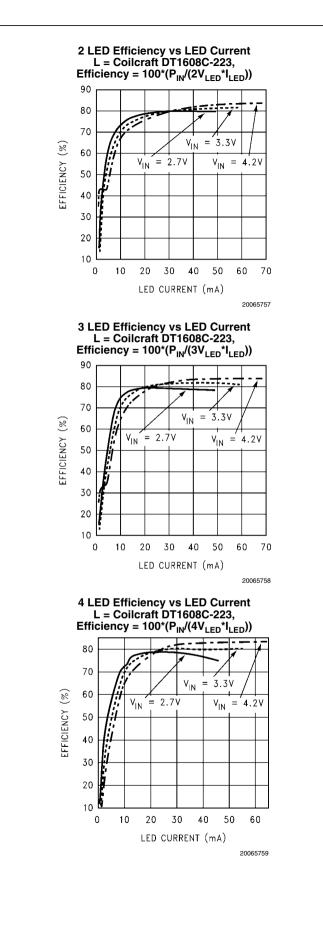

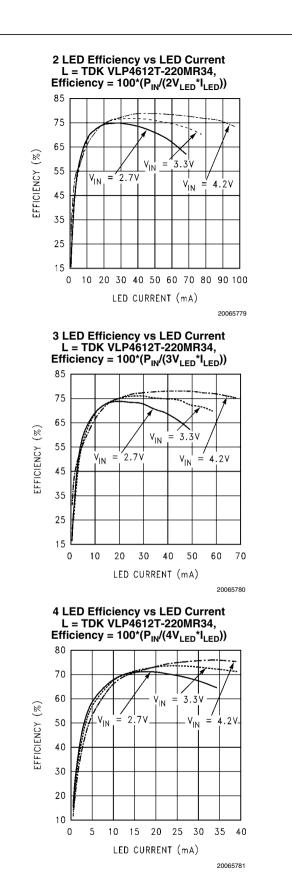

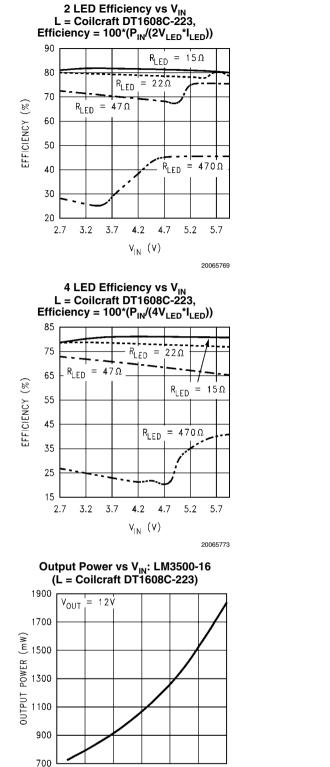

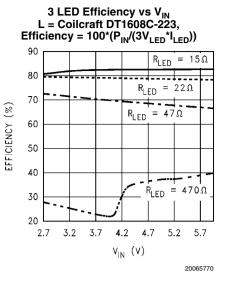

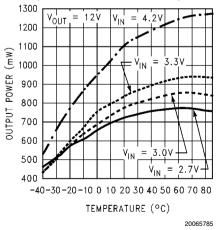

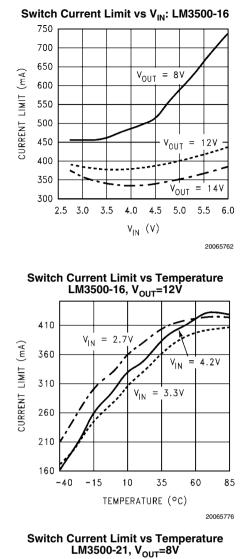

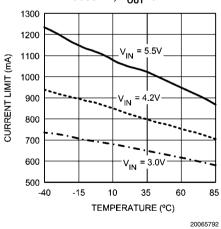

## **Typical Performance Characteristics**

### Non-Switching Quiescent Current vs V<sub>IN</sub>

3.0

2.5

3.5

4.0

INPUT VOLTAGE (V)

4.5

5.0

5.5

20065784

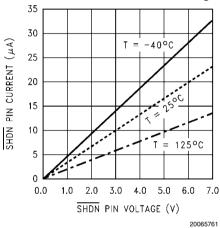

SHDN Pin Current vs SHDN Pin Voltage

Switch Current Limit vs VIN: LM3500-21

20065791

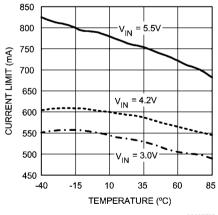

Switch Current Limit vs Temperature LM3500-21, V<sub>OUT</sub>=12V

20065793

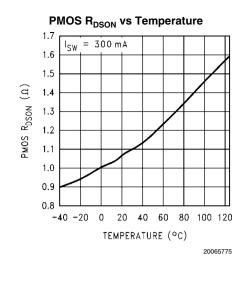

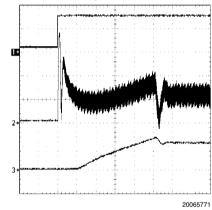

$\begin{array}{l} 3 \; LEDs, \; R_{LED} = 22 \Omega, \; V_{|N} = 3.0V \\ 1) \; \overline{SHDN}, \; 1V/div, \; DC \\ 2) \; I_L, \; 100mA/div, \; DC \\ 3) \; I_{LED}, \; 20mA/div, \; DC \\ T = 100 \mu s/div \end{array}$

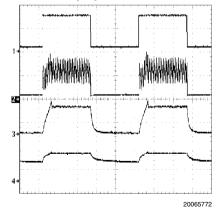

#### **SHDN** Pin Duty Cycle Control Waveforms

LM3500-16, 3 LEDs, R<sub>LED</sub> = 22 $\Omega$ , V<sub>IN</sub> = 3.0V, SHDN frequency = 200Hz 1) SHDN, 1V/div, DC 2) I<sub>L</sub>, 100mA/div, DC 3) I<sub>LED</sub>, 20mA/div, DC 4) V<sub>OUT</sub>, 10V/div, DC

T = 1 ms/div

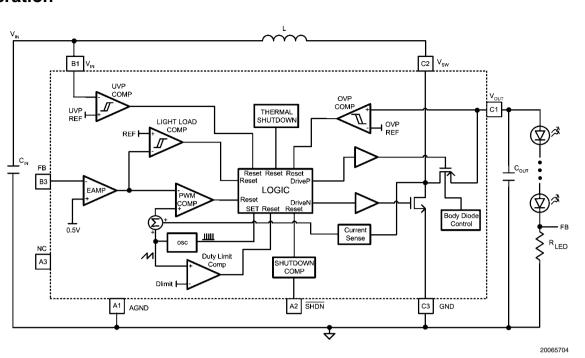

# Operation

The LM3500 utilizes a synchronous Current Mode PWM control scheme to regulate the feedback voltage over almost all load conditions. The DC/DC controller acts as a controlled current source ideal for white LED applications. The LM3500 is internally compensated preventing the use of any external compensation components providing a compact overall solution. The operation can best be understood referring to the block diagram in Figure 1. At the start of each cycle, the oscillator sets the driver logic and turns on the NMOS power device conducting current through the inductor and turns off the PMOS power device isolating the output from the V<sub>SW</sub> pin. The LED current is supplied by the output capacitor when the NMOS power device is active. During this cycle, the output voltage of the EAMP controls the current through the inductor. This voltage will increase for larger loads and decrease for smaller loads limiting the peak current in the inductor minimizing EMI radiation. The EAMP voltage is compared with a voltage ramp and the sensed switch voltage. Once this voltage reaches the EAMP output voltage, the PWM COMP will then reset the logic turning off the NMOS power device and turning on the PMOS power device. The inductor current then flows through the PMOS power device to the white LED load and output capacitor. The inductor current recharges the output capacitor and supplies the current for the white LED branches. The oscillator then sets the driver logic again repeating the process. The Duty Limit Comp is always operational preventing the NMOS power switch from being on more than one cycle and conducting large amounts of current.

The LM3500 has dedicated protection circuitry active during normal operation to protect the IC and the external components. The Thermal Shutdown circuitry turns off both the NMOS and PMOS power devices when the die temperature reaches excessive levels. The LM3500 has a UVP Comp that disables both the NMOS and PMOS power devices when battery voltages are too low preventing an on state of the power devices which could conduct large amounts of current. The OVP Comp prevents the output voltage from increasing beyond 15.5V(LM3500-16) and 20.5V(LM3500-21) when the primary white LED network is removed or if there is an LED failure, allowing the use of small (16V for LM3500-16 and 25V for LM3500-21) ceramic capacitors at the output. This comparator has hysteresis that will regulate the output voltage between 15.5V and 14.6V typically for the LM3500-16, and between 20.5V and 19.5V for the LM3500-21. The LM3500 features a shutdown mode that reduces the supply current to 0.1uA and isolates the input and output of the converter.

## **Application Information**

### ADJUSTING LED CURRENT

The White LED current is set using the following equation:

$$I_{LED} = V_{FB}/R_{LED}$$

The LED current can be controlled using a PWM signal on the SHDN pin with frequencies in the range of 100Hz (greater than visible frequency spectrum) to 1kHz. For controlling LED currents down to the  $\mu$ A levels, it is best to use a PWM signal frequency between 200-500Hz. The LM3500 LED current can be controlled with PWM signal frequencies above 1kHz but the controllable current decreases with higher frequency. The maximum LED current would be achieved using the equation above with 100% duty cycle, ie. the SHDN pin always high.

### LED-DRIVE CAPABILITY

The maximum number of LEDs that can be driven by the LM3500 is limited by the output voltage capability of the LM3500. When using the LM3500 in the typical application configuration, with LEDs stacked in series between the V<sub>OUT</sub> and FB pins, the maximum number of LEDs that can be placed in series (N<sub>MAX</sub>) is dependent on the maximum LED forward voltage (V<sub>F-MAX</sub>), the voltage of the LM3500 feedback pin (V<sub>FB-MAX</sub> = 0.53V), and the minimum output over-voltage protection level of the chosen LM3500 option (LM3500-16: OVP<sub>MIN</sub> = 15V; LM3500-21: OVP<sub>MIN</sub> = 20V). For the circuit to function properly, the following inequality must be met:

$(N_{MAX} \times V_{F-MAX}) + 0.53V \le OVP_{MIN}$

When inserting a value for maximim LED  $V_F$ , LED forward voltage variation over the operating temperature range should be considered. The table below provides maximum LED voltage numbers for the LM3500-16 and LM3500-21 in the typical application circuit configuration (with 3, 4, 5, 6, or 7 LEDs placed in series between the  $V_{OLT}$  and FB pins).

| # of LEDs   | Maximum LED V <sub>F</sub> |           |  |  |  |

|-------------|----------------------------|-----------|--|--|--|

| (in series) | LM3500-16                  | LM3500-21 |  |  |  |

| 3           | 4.82V                      | 6.49V     |  |  |  |

| 4           | 3.61V                      | 4.86V     |  |  |  |

| 5           | 2.89V                      | 3.89V     |  |  |  |

| 6           | X                          | 3.24V     |  |  |  |

| 7           | Х                          | 2.78V     |  |  |  |

For the LM3500 to operate properly, the output voltage must be kept above the input voltage during operation. For most applications, this requires a minimum of 2 LEDs (total of 6V or more) between the FB and  $V_{OUT}$  pins.

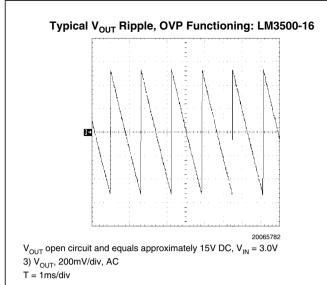

### OUTPUT OVERVOLTAGE PROTECTION

The LM3500 contains dedicated circuitry for monitoring the output voltage. In the event that the primary LED network is disconnected from the LM3500-16, the output voltage will increase and be limited to 15.5V (typ.). There is a 900mV hysteresis associated with this circuitry which will cause the output to fluctuate between 15.5V and 14.6V (typ.) if the primary network is disconnected. In the event that the network is reconnected regulation will begin at the appropriate output voltage. The 15.5V limit allows the use of 16V 1µF ceramic output capacitors creating an overall small solution for white LED applications.

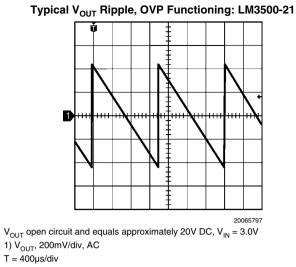

In the event that the primary LED network is disconnected from the LM3500-21, the output voltage will increase and be

limited to 20.5V (typ.). There is a 1V hysteresis associated with this circuitry which will cause the output to fluctuate between 20.5V and 19.5V (typ.) if the primary network is disconnected. In the event that the network is reconnected regulation will begin at the appropriate output voltage. The 20.5V limit allows the use of 25V 1 $\mu$ F ceramic output capacitors.

### **RELIABILITY AND THERMAL SHUTDOWN**

The maximum continuous pin current for the 8 pin thin micro SMD package is 535mA. When driving the device near its power output limits the  $V_{SW}$  pin can see a higher DC current than 535mA (see INDUCTOR SELECTION section for average switch current). To preserve the long term reliability of the device the average switch current should not exceed 535mA.

The LM3500 has an internal thermal shutdown function to protect the die from excessive temperatures. The thermal shutdown trip point is typically 150°C. There is a hysteresis of typically 35°C so the die temperature must decrease to approximately 115°C before the LM3500 will return to normal operation.

### INDUCTOR SELECTION

The inductor used with the LM3500 must have a saturation current greater than the cycle by cycle peak inductor current (see Typical Peak Inductor Currents table below). Choosing inductors with low DCR decreases power losses and increases es efficiency.

The minimum inductor value required for the LM3500-16 can be calculated using the following equation:

$$L > \frac{V_{IN} R_{DSON}}{0.29} \left(\frac{D}{D'} - 1\right)$$

The minimum inductor value required for the LM3500-21 can be calculated using the following equation:

$$L > \frac{V_{IN} R_{DSON}}{0.58} \left(\frac{D}{D'} - 1\right)$$

For both equations above, L is in  $\mu$ H, V<sub>IN</sub> is the input supply of the chip in Volts, R<sub>DSON</sub> is the ON resistance of the NMOS power switch found in the Typical Performance Characteristics section in ohms and D is the duty cycle of the switching regulator. The above equation is only valid for D greater than or equal to 0.5. For applications where the minimum duty cycle is less than 0.5, a 22µH inductor is the typical recommendation for use with most applications. Bench-level verification of circuit performance is required in these special cases, however. The duty cycle, D, is given by the following equation:

$$D' = \frac{V_{IN}}{V_{OUT}} = 1-D$$

where  $V_{OUT}$  is the voltage at pin C1.

#### Typical Peak Inductor Currents (mA)

|                        | # LEDs         |          |          | LED C    | urrent   |          |          |

|------------------------|----------------|----------|----------|----------|----------|----------|----------|

| V <sub>IN</sub><br>(V) | (in<br>series) | 15<br>mA | 20<br>mA | 30<br>mA | 40<br>mA | 50<br>mA | 60<br>mA |

| 2.7                    | 2              | 82       | 100      | 134      | 160      | 204      | 234      |

|                        | 3              | 118      | 138      | 190      | 244      | 294      | 352      |

|                        | 4              | 142      | 174      | 244      | 322      | Х        | х        |

|                        | 5              | 191      | 232      | 319      | 413      | Х        | Х        |

| 3.3                    | 2              | 76       | 90       | 116      | 136      | 172      | 198      |

|                        | 3              | 110      | 126      | 168      | 210      | 250      | 290      |

|                        | 4              | 132      | 158      | 212      | 270      | 320      | Х        |

|                        | 5              | 183      | 216      | 288      | 365      | 446      | Х        |

| 4.2                    | 2              | 64       | 76       | 96       | 116      | 142      | 162      |

|                        | 3              | 102      | 116      | 148      | 180      | 210      | 246      |

|                        | 4              | 122      | 146      | 186      | 232      | 272      | 318      |

|                        | 5              | 179      | 206      | 263      | 324      | 388      | 456      |

$C_{IN} = C_{OUT} = 1 \ \mu F$

L = 22  $\mu$ H, 160 m $\Omega$  DCR max. Coilcraft DT1608C-223

2 and 3 LED applications: LM3500-16 or LM3500-21; LED  $V_{\rm F}$  = 3.77V at

20mA;  $T_A = 25^{\circ}C$ 4 LED applications: LM3500-16 or LM3500-21; LED V<sub>F</sub> = 3.41V at 20mA;  $T_A = 25^{\circ}C$

$T_A = 25 \text{ C}$ 5 LED applications: LM3500-21 only; LED V<sub>F</sub> = 3.28V at 20mA;  $T_A = 25^{\circ}\text{C}$

The typical cycle-by-cycle peak inductor current can be calculated from the following equation:

$$I_{PK} \approx \frac{I_{OUT}}{\eta D'} + \frac{V_{IN}D}{2LF_{SM}}$$

where  $I_{OUT}$  is the total load current,  $F_{SW}$  is the switching frequency, L is the inductance and  $\eta$  is the converter efficiency of the total driven load. A good typical number to use for  $\eta$  is 0.8. The value of  $\eta$  can vary with load and duty cycle. The average inductor current, which is also the average  $V_{SW}$  pin current, is given by the following equation:

$$I_{L(AVE)} \approx \frac{I_{OUT}}{\eta D'}$$

The maximum output current capability of the LM3500 can be estimated with the following equation:

$$I_{OUT} \approx \eta D' \left( I_{CL} - \frac{V_{IN}D}{2LF_{SW}} \right)$$

where  $I_{CL}$  is the current limit. Some recommended inductors include but are not limited to:

Coilcraft DT1608C series Coilcraft DO1608C series TDK VLP4612 series TDK VLP5610 series TDK VLF4012A series

### CAPACITOR SELECTION

Choose low ESR ceramic capacitors for the output to minimize output voltage ripple. Multilayer X7R or X5R type ceramic capacitors are the best choice. For most applications, a  $1\mu$ F ceramic output capacitor is sufficient.

Local bypassing for the input is needed on the LM3500. Multilayer X7R or X5R ceramic capacitors with low ESR are a good choice for this as well. A 1 $\mu$ F ceramic capacitor is sufficient for most applications. However, for some applications at least a 4.7 $\mu$ F ceramic capacitor may be required for proper startup of the LM3500. Using capacitors with low ESR decreases input voltage ripple. For additional bypassing, a 100nF ceramic capacitor can be used to shunt high frequency ripple on the input. Some recommended capacitors include but are not limited to:

TDK C2012X7R1C105K

Taiyo-Yuden EMK212BJ105 G

### LAYOUT CONSIDERATIONS

The input bypass capacitor  $C_{IN}$ , as shown in Figure 1, must be placed close to the device and connect between the  $V_{IN}$ and GND pins. This will reduce copper trace resistance which effects the input voltage ripple of the IC. For additional input voltage filtering, a 100nF bypass capacitor can be placed in parallel with C<sub>IN</sub> to shunt any high frequency noise to ground. The output capacitor, C<sub>OUT</sub>, should also be placed close to the LM3500 and connected directly between the  $V_{OUT}$  and GND pins. Any copper trace connections for the COUT capacitor can increase the series resistance, which directly effects output voltage ripple and efficiency. The current setting resistor, R<sub>LED</sub>, should be kept close to the FB pin to minimize copper trace connections that can inject noise into the system. The ground connection for the current setting resistor should connect directly to the GND pin. The AGND pin should connect directly to the GND pin. Not connecting the AGND pin directly, as close to the chip as possible, may affect the performance of the LM3500 and limit its current driving capability. Trace connections made to the inductor should be minimized to reduce power dissipation. EMI radiation and increase overall efficiency. It is good practice to keep the V<sub>SW</sub> routing away from sensitive pins such as the FB pin. Failure to do so may inject noise into the FB pin and affect the requlation of the device. See Figure 2 and Figure 3 for an example of a good layout as used for the LM3500 evaluation board.

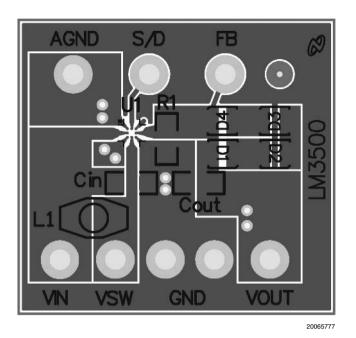

FIGURE 2. Evaluation Board Layout (2X Magnification) Top Layer

20065778

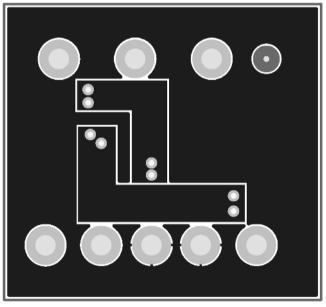

FIGURE 3. Evaluation Board Layout (2X Magnification) Bottom Layer (as viewed from the top)

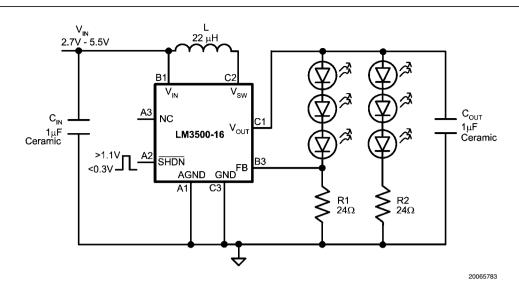

FIGURE 7. LM3500-21 5 LED Application

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email: new.feedback@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530-85-86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560