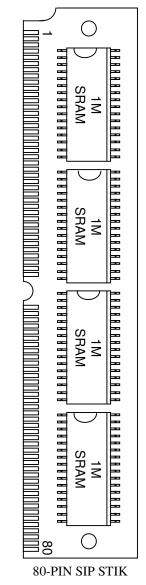

# DS2229 Word-Wide 8 Meg SRAM Stik

#### www.dalsemi.com

## FEATURES

- Organized as a high density 512k x 16 bit Stik<sup>TM</sup>

- Fast access time of 85 ns

- Unlimited write cycles

- Employs popular JEDEC standard 80-position SIMM connector

- Full ±10% operating range

- Read cycle time equals write cycle time

- Ultra-low standby current < 10 μA</li>

- Suitable for battery-backed applications

## **PIN ASSIGNMENT**

#### DESCRIPTION

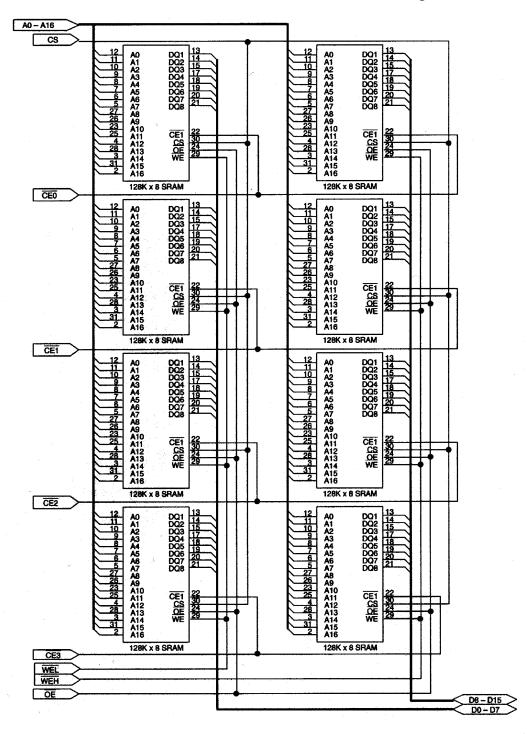

The DS2229 is an 8,388,608-bit low-power fully static Random Access Memory organized as a 524,888 word by 16 bits using CMOS technology. The device employs the popular JEDEC standard 80-pin SIMM connection scheme with no additional circuitry required. The device operates from a single power supply with a voltage input of 4.5 to 5.5 volts. The Chip Enable inputs ( $\overline{CE0}$ ,  $\overline{CE1}$ ,  $\overline{CE2}$ ,  $\overline{CE3}$ ) are used for device selection and can be used in order to achieve the minimum standby current mode which facilitates battery backup. The device provides a fast access time of 85 ns. The DS2229 maintains TTL levels over input voltage range 4.5V to 5.5V. The DS2229 is JEDEC pin compatible (see Figure 1) with flash EEPROM memory SIMM boards of similar density.

# PIN DESCRIPTION Figure 1

|       |                         |       | •                |       |                                                   |                         |

|-------|-------------------------|-------|------------------|-------|---------------------------------------------------|-------------------------|

| PIN # | PIN NAME                | PIN # | PIN NAME         | PIN # | PIN NAME                                          |                         |

| 1     | GND                     | 32    | NC               | 63    | DQ <sub>7</sub>                                   |                         |

| 2     | V <sub>CC</sub>         | 33    | NC               | 64    | $DQ_6$                                            |                         |

| 3     | NC                      | 34    | NC               | 65    | DQ <sub>5</sub>                                   |                         |

| 4     | OE                      | 35    | NC               | 66    | $DQ_4$                                            |                         |

| 5     | WEH                     | 36    | A <sub>16</sub>  | 67    | DQ <sub>3</sub>                                   |                         |

| 6     | WEL                     | 37    | A <sub>15</sub>  | 68    | $DQ_2$                                            |                         |

| 7     | NC                      | 38    | $A_{14}$         | 69    | $DQ_1$                                            |                         |

| 8     | CS                      | 39    | A <sub>13</sub>  | 70    | $\mathrm{D}\mathrm{Q}_0$                          |                         |

| 9     | NC                      | 40    | A <sub>12</sub>  | 71    | NC                                                |                         |

| 10    | NC                      | 41    | $A_{11}$         | 72    | V <sub>CC</sub>                                   |                         |

| 11    | NC                      | 42    | $A_{10}$         | 73    | NC                                                |                         |

| 12    | NC                      | 43    | $A_9$            | 74    | GND                                               |                         |

| 13    | NC                      | 44    | $A_8$            | 75    | NC                                                |                         |

| 14    | NC                      | 45    | $A_7$            | 76    | GND                                               |                         |

| 15    | NC                      | 46    | $A_6$            | 77    | GND                                               |                         |

| 16    | NC                      | 47    | $A_5$            | 78    | NC                                                |                         |

| 17    | NC                      | 48    | $A_4$            | 79    | NC                                                |                         |

| 18    | NC                      | 49    | $A_3$            | 80    | GND                                               |                         |

| 19    | NC                      | 50    | $A_2$            |       |                                                   |                         |

| 20    | NC                      | 51    | $A_1$            |       |                                                   |                         |

| 21    | $\overline{CE3}$        | 52    | $A_0$            |       | PIN NAME                                          | DESCRIPTION             |

| 22    | CE2                     | 53    | GND              |       | A <sub>0</sub> - A <sub>16</sub>                  | Address Input           |

| 23    | $\overline{\text{CE1}}$ | 54    | GND              |       | WEL                                               | Write Enable Input Low  |

| 24    | $\overline{\text{CE0}}$ | 55    | DQ15             |       | WEH                                               | Write Enable Input High |

| 25    | GND                     | 56    | $DQ_{14}$        |       | ŌĒ                                                | Output Enable Input     |

| 26    | NC                      | 57    | DQ <sub>13</sub> |       | NC                                                | No Connect              |

| 27    | NC                      | 58    | DQ <sub>12</sub> |       | $\overline{\text{CE0}}$ - $\overline{\text{CE3}}$ | Chip Enable Input       |

| 28    | NC                      | 59    | DQ11             |       | CS                                                | Chip Select             |

| 29    | NC                      | 60    | DQ10             |       | DQ <sub>0</sub> - DQ <sub>15</sub>                | Data Input/Output       |

| 30    | NC                      | 61    | DQ <sub>9</sub>  |       | V <sub>CC</sub>                                   | +5 Volts                |

| 31    | NC                      | 62    | $DQ_8$           |       | GND                                               | Ground                  |

# DS2229 STATIC RAM MODULE FUNCTION DIAGRAM Figure 2

## **ABSOLUTE MAXIMUM RATINGS\***

| Power Supply Voltage        | -0.3V to +7.0V                  |

|-----------------------------|---------------------------------|

| Input, Input/Output Voltage | -0.3 to $V_{CC}$ +0.3V          |

| Operating Temperature       | $0^{\circ}$ C to $70^{\circ}$ C |

| Storage Temperature         | -55°C to +125°C                 |

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### **OPERATION MODE**

| MODE     | $\overline{\text{CE0}}$ - $\overline{\text{CE3}}$ | CS | ŌĒ | WE | A0 - A16 | DQ - DQ15 | POWER                                 |

|----------|---------------------------------------------------|----|----|----|----------|-----------|---------------------------------------|

| READ     | L                                                 | Н  | L  | Н  | STABLE   | DATA OUT  | I <sub>CC0</sub>                      |

| WRITE    | L                                                 | Н  | Х  | L  | STABLE   | DATA IN   | I <sub>CC0</sub>                      |

| DESELECT | L                                                 | Н  | Н  | Н  | Х        | HIGH-Z    | I <sub>CC0</sub>                      |

| STANDBY  | Н                                                 | Х  | Х  | Х  | Х        | HIGH-Z    | I <sub>CCS1</sub> , I <sub>CCS2</sub> |

| STANDBY  | Х                                                 | L  | Х  | Х  | Х        | HIGH-Z    | $I_{CCS1}, I_{CCS2}$                  |

# CAPACITANCE

| CAPACITANCE (t <sub>A</sub> =25 |                  |     |     |     |       | <sub>A</sub> =25°C) |

|---------------------------------|------------------|-----|-----|-----|-------|---------------------|

| PARAMETER                       | SYMBOL           | MIN | ТҮР | MAX | UNITS | NOTES               |

| Input Capacitance               | C <sub>IN</sub>  |     |     | 64  | pF    |                     |

| Input/Output Capacitance        | C <sub>I/O</sub> |     |     | 80  | pF    |                     |

# **RECOMMENDED DC OPERATING CONDITIONS**

$(t_A = 0^\circ C \text{ to } 70^\circ C)$

| PARAMETER            | SYMBOL          | MIN  | ТҮР | MAX                  | UNITS | NOTES |

|----------------------|-----------------|------|-----|----------------------|-------|-------|

| Power Supply Voltage | V <sub>CC</sub> | 4.5  | 5.0 | 5.5                  | V     |       |

| Input High Voltage   | V <sub>IH</sub> | 2.0  |     | V <sub>CC</sub> +0.3 | V     |       |

| Input Low Voltage    | V <sub>IL</sub> | -0.3 |     | 0.8                  | V     |       |

#### **DC CHARACTERISTICS**

$(t_A = 0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5V \pm 10\%)$

| PARAMETER             | SYMBOL            | CONDITIONS                                                                                                                             | MIN  | MAX | UNITS | NOTES |

|-----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-------|

| Input Leakage Current | I <sub>IL</sub>   | $0V \leq V_{IN} \leq V_{CC}$                                                                                                           |      | 8   | μA    |       |

| I/O Leakage Current   | I <sub>LO</sub>   | $\overline{\text{CE0}} - \overline{\text{CE3}} = \text{V}_{\text{IH}},$ $0\text{V} \le \text{V}_{\text{I/O}} \le \text{V}_{\text{CC}}$ |      | 8   | μA    |       |

| Output High Current   | I <sub>OH</sub>   | $V_{OH} = 2.4 V$                                                                                                                       | -1.0 |     | mA    |       |

| Output Low Current    | I <sub>OL</sub>   | $V_{OL} = 0.4V$                                                                                                                        | 2.1  |     | mA    |       |

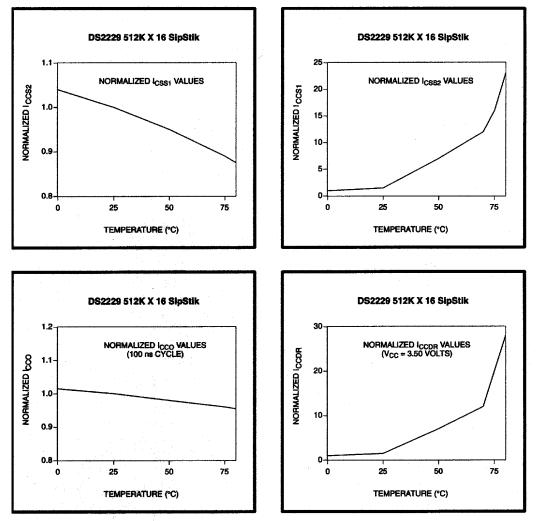

| Standby Current       | I <sub>CCS1</sub> | $\overline{\text{CE0}}$ - $\overline{\text{CE3}}$ = 2.0V t <sub>A</sub> = 25°C                                                         |      | 8   | mA    |       |

| Standby Current       | I <sub>CCS2</sub> | $\overline{CE0} - \overline{CE3} \ge V_{CC} - 0.3V$ $t_{A}=25^{\circ}C$                                                                |      | 10  | μA    |       |

| Operating Current     | I <sub>CCO</sub>  | $\overline{CE0} - \overline{CE3} = 0.8V;$<br>Cycle=100 ns t <sub>A</sub> =25°C                                                         |      | 100 | mA    | 9     |

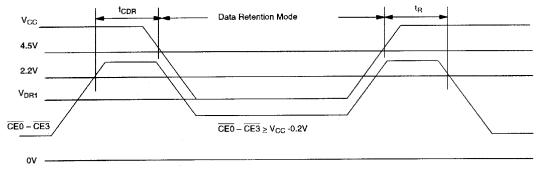

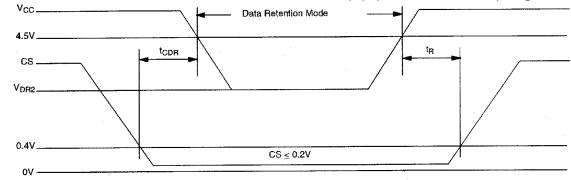

| LOW VCC DATA RET                        | ENTION O          | CHARA | CTER | ISTICS |       | $(t_A = 0^{\circ}C \text{ to } 70^{\circ}C)$                                                                                                                                                              |

|-----------------------------------------|-------------------|-------|------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                               | SYMBOL            | MIN   | ТҮР  | MAX    | UNITS | TEST CONTIDION                                                                                                                                                                                            |

| V <sub>CC</sub> for Data Retention      | V <sub>DR</sub>   | 2.0   | -    | -      | V     | $\overline{\text{CE0}} - \overline{\text{CE3}} \ge \text{V}_{\text{CC}} - 0.2\text{V},$<br>$\text{CS} \ge \text{V}_{\text{CC}} - 0.2\text{V} \text{ or } 0\text{V}$                                       |

|                                         |                   |       |      |        |       | $\leq CS \leq 0.2V V_{IN} \geq 0V$                                                                                                                                                                        |

| Data Retention Current                  | I <sub>CCDR</sub> | -     | 1    | 8      | μΑ    | $\begin{split} & V_{CC} = 3.0V,  V_{IN} \ge 0V \\ & \overline{CE0} - \overline{CE3} \ge V_{CC} - 0.2V, \\ & CS \ge V_{CC} - 0.2V \text{ or } 0V \le \\ & CS \le 0.2V  t_A = 25^\circ\text{C} \end{split}$ |

| Chip Deselect to Data<br>Retention Time | t <sub>CDR</sub>  | 0     | -    | -      | ns    | See Retention<br>Waveform                                                                                                                                                                                 |

| Operation Recovery Time                 | t <sub>R</sub>    | 5     | -    | -      | ms    |                                                                                                                                                                                                           |

## LOW V<sub>CC</sub> DATA RETENTION TIMING WAVEFORM (1) ( $\overline{CE0}$ - $\overline{CE3}$ Controlled) Figure 3

SEE NOTE 5

# LOW V<sub>cc</sub> DATA RETENTION TIMING WAVEFORM (2) (CS Controlled) Figure 4

**SEE NOTE 5**

# **PRODUCT CHARACTERISTICS**

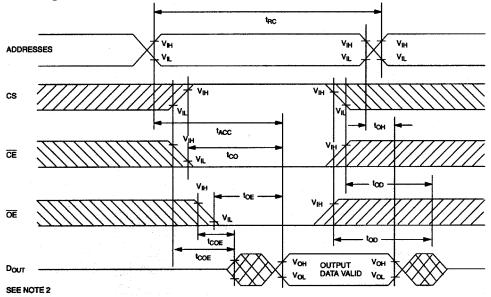

# AC ELECTRICAL CHARACTERISTICS READ CYCLE

| READ CYCLE                                                                                     | EAD CYCLE        |     |     |     | $(0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5V + 10\%)$ |       |  |  |  |

|------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------------------------------------------------------------|-------|--|--|--|

| PARAMETER                                                                                      | SYMBOL           | MIN | ТҮР | MAX | UNITS                                                      | NOTES |  |  |  |

| Read Cycle Time                                                                                | t <sub>RC</sub>  | 85  |     |     | ns                                                         |       |  |  |  |

| Access Time                                                                                    | t <sub>ACC</sub> |     |     | 85  | ns                                                         |       |  |  |  |

| OE to Output Valid                                                                             | t <sub>OE</sub>  |     |     | 45  | ns                                                         |       |  |  |  |

| $\overline{\text{CE0}}$ - $\overline{\text{CE3}}$ to Output Valid                              | t <sub>CO</sub>  |     |     | 85  | ns                                                         |       |  |  |  |

| $\overline{\text{OE}}$ or $\overline{\text{CE0}}$ - $\overline{\text{CE3}}$ to Output In Low-Z | t <sub>COE</sub> | 10  |     |     | ns                                                         | 8     |  |  |  |

| Output High-Z from Deselection                                                                 | t <sub>OD</sub>  | 0   |     | 30  | ns                                                         | 8     |  |  |  |

| Output Hold from Address Change                                                                | t <sub>OH</sub>  | 10  |     |     | ns                                                         |       |  |  |  |

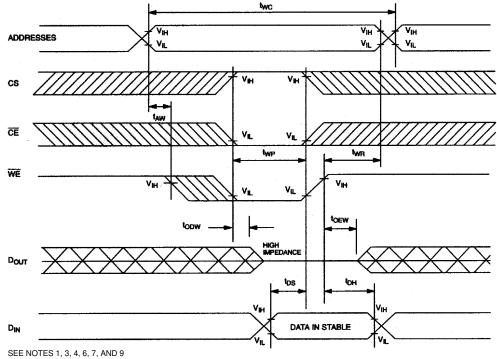

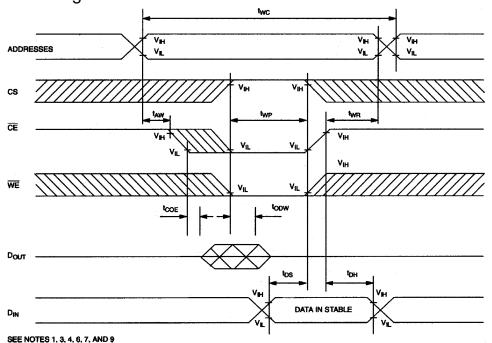

# AC ELECTRICAL CHARACTERISTICS

| WRITE CYCLE                         |                  | $(0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5V + 10\%)$ |     |     |       |       |

|-------------------------------------|------------------|------------------------------------------------------------|-----|-----|-------|-------|

| PARAMETER                           | SYMBOL           | MIN                                                        | ТҮР | MAX | UNITS | NOTES |

| Write Cycle Time                    | t <sub>WC</sub>  | 85                                                         |     |     | ns    |       |

| Write Pulse Width                   | t <sub>WP</sub>  | 65                                                         |     |     | ns    | 1     |

| Address Setup Time                  | t <sub>AW</sub>  | 0                                                          |     |     | ns    |       |

| Write Recovery Time                 | t <sub>WR</sub>  | 10                                                         |     |     | ns    | 4     |

| Output High-Z from $\overline{WE}$  | t <sub>ODW</sub> | 0                                                          |     | 30  | ns    | 8     |

| Output Active from $\overline{WE}$  | t <sub>OEW</sub> | 5                                                          |     |     | ns    | 8     |

| Data Setup Time                     | t <sub>DS</sub>  | 35                                                         |     |     | ns    | 3     |

| Data Hold Time from $\overline{WE}$ | t <sub>DH</sub>  | 0                                                          |     |     | ns    | 3     |

# **READ CYCLE** Figure 5

#### WRITE CYCLE 2 Figure 7

### NOTES:

- 1. A write occurs during the overlap of a low  $\overline{CE0} \overline{CE3}$ , a high CS, and a low  $\overline{WE}$ . A write begins at the latest transition among  $\overline{CE0} \overline{CE3}$  going low, CS going high, and  $\overline{WE}$  going low. A write ends at the earliest transition among  $\overline{CE0} \overline{CE3}$  going high, CS going low and  $\overline{WE}$  going high. twp is measured from the beginning of write to the end of write.

- 2.  $\overline{\text{WE}}$  is high for a read cycle.

- 3.  $t_{DS}$  ends and  $t_{DH}$  begins at the earliest transaction among  $\overline{CE0} \overline{CE3}$  going high.

- 4.  $t_{WR}$  is measured from the earliest of  $\overline{CE0} \overline{CE3}$  or  $\overline{WE}$  going high or CS going low to the end of write cycle.

- 5. CS controls address buffer,  $\overline{WE}$  buffer,  $\overline{CE0} \overline{CE3}$  buffer,  $\overline{OE}$  buffer and  $D_{IN}$  buffer. If CS controls data retention mode,  $V_{IN}$  levels (address,  $\overline{WE}$ ,  $\overline{OE}$ ,  $\overline{CE0} \overline{CE3}$ , I/O) can be in the high impedance state. If  $\overline{CE0} \overline{CE3}$  controls data retention mode, CS must be  $CS \ge V_{CC} 0.2V$  or 0V < CS < 0.2V. The other input levels (address,  $\overline{WE}$ ,  $\overline{OE}$ , I/O) can be in the high impedance state.

- 6. If  $\overline{CE0} \overline{CE3}$  goes low simultaneously with  $\overline{WE}$  going low or after  $\overline{WE}$  going low, the outputs remain in a high impedance state.

- 7. If  $\overline{CE0} \overline{CE3}$  is low and CS is high during this period, I/O pins are in the output state. Therefore, the input signals of the opposite phase to the outputs must not be applied to them.

- 8. This parameter is sampled and not 100% tested.

- 9. Only one  $\overline{CE}$  active during any read or write cycle.

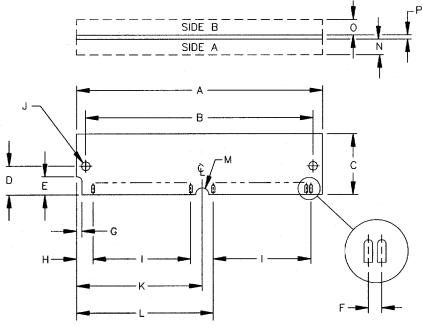

# DS2229 80-PIN SIP STIK

| PKG | 80-PIN    |       |  |  |  |

|-----|-----------|-------|--|--|--|

| DIM | MIN       | MAX   |  |  |  |

| Α   | 4.645     | 4.655 |  |  |  |

| В   | 4.379     | 4.389 |  |  |  |

| С   | 0.729     | 0.739 |  |  |  |

| D   | 0.395     | 0.405 |  |  |  |

| E   | 0.245     | 0.255 |  |  |  |

| F   | 0.050 BSC |       |  |  |  |

| G   | 0.075     | 0.085 |  |  |  |

| н   | 0.245     | 0.255 |  |  |  |

| I   | 1.950     | BSC   |  |  |  |

| J   | 0.120     | 0.130 |  |  |  |

| к   | 2.320     | 2.330 |  |  |  |

| L   | 2.445     | 2.455 |  |  |  |

| м   | 0.057     | 0.067 |  |  |  |

| N   |           | 0.130 |  |  |  |

| 0   |           | 0.130 |  |  |  |

| Р   |           | 0.054 |  |  |  |