# Nuvoton N-Channel FET Synchronous Buck Regulator Controller W83320G

# W83320G Data Sheet Revision History

|    | PAGES | DATES   | VERSION | VERSION<br>ON WEB | MAIN CONTENTS                                                                                 |  |

|----|-------|---------|---------|-------------------|-----------------------------------------------------------------------------------------------|--|

| 1  | N.A.  | N.A.    | 0.50    | N.A.              | All version before 0.5 are for internal use only.                                             |  |

| 2  | N.A.  | N.A.    | 0.51    | N.A.              | Add Pb-free part no :W83320G                                                                  |  |

| 3  | 9,10. | Oct./05 | 0.52    | N.A.              | To modify the application circuit.                                                            |  |

| 4. | N.A   | Oct./06 | 1.0     | 1.0               | 1.Remove non Pb-free part no:W83320S     2. All versions before 1.0 are preliminary versions. |  |

| 5. | 10    | Apr./08 | 1.1     | 1.1               | Add Absolute Maximum Rating                                                                   |  |

|    |       |         |         |                   |                                                                                               |  |

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.

## LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

## Table of Content-

| 1.  | GENERAL DESCRIPTION                 | 3    |

|-----|-------------------------------------|------|

| 2.  | FEATURES                            | 3    |

| 3.  | APPLICATIONS                        | 3    |

| 4.  | PIN-OUT                             | 4    |

| 5.  | PIN DESCRIPTION                     | 5    |

| 6.  | INTERNAL BLOCK DIAGRAM              | 6    |

| 7.  | APPLICATION CIRCUIT                 |      |

| 8.  | ABSOLUTE MAXIMUM RATINGS            |      |

| 9.  | ELECTRICAL CHARACTERISTICS          |      |

| 10. | TYPICAL PERFORMANCE CHARACTERISTICS |      |

| 11. | PACKAGE DIMENSION OUTLINE           |      |

|     | TAPING SPECIFICATION                |      |

| 12. | ORDERING INSTRUCTION                | . 18 |

| 13. | TOP MARKING SPECIFICATION           | . 18 |

### 1. GENERAL DESCRIPTION

The W83320G is a high-speed, N-Channel synchronous buck regulator controller optimized for wide reference input range. The W83320G employs adjustable frequency ranging from 100 KHz to 400 KHz voltage-mode PWM control architecture. The regulator is biased from a 5V rail and the power for the high-side MOSFET can be supplied by a separate 12V rail or supplied from the internal charge pump.

A Current limit protection is implemented by monitoring the voltage drop across the switch ON resistance of the low-side MOSFET. This method can eliminate the requirement of extra current sensing resistor and avoids false trigger of OC protection when V<sub>IN</sub> varies efficiently. The adaptive non-overlapping MOSFET gate drivers help avoid potential shoot-through problems while maintaining high efficiency. All these together with Power-good flag, enable and soft start features make power sequencing easy.

## 2. FEATURES

- 1.8V to 5V power stage input voltage

- Providing +/-1.5% reference voltage

- Power Good flag

- Current limit without sense resistor

- Soft start

- Switching frequency from 100 kHz to 400 kHz

- Tiny plastic SOP-14 package

## 3. APPLICATIONS

- DDR SDRAM and AGP core power for Desktop PC

- Set-Top Boxes/ Home Gateways

- Core Logic Regulators

- High-Efficiency Buck Regulation

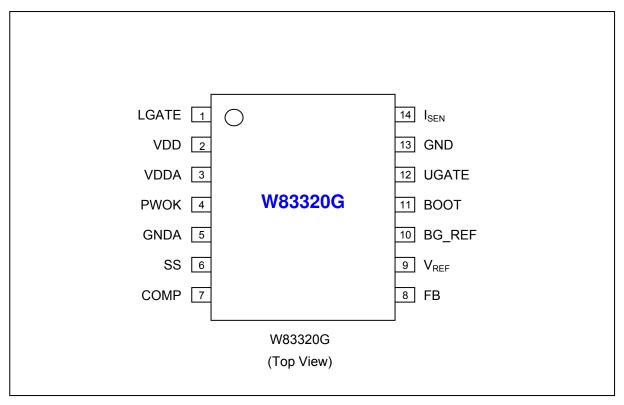

## 4. PIN-OUT

Figure 1. W83320G Pin-out

## 5. PIN DESCRIPTION

| 5. PIN DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                      |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN                | NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FUNCTION                                                                                                                                                                                             |  |  |  |  |

| 1                  | LGATE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Low-Side N-Channel MOSFET Gate Drive Pin. This pin is monitored by the adaptive shoot-through protection circuitry to determine when the low-side MOSFET turned off.                                 |  |  |  |  |

| 2                  | VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | +5V supply rail for the lower gate driver and control logic circuit.                                                                                                                                 |  |  |  |  |

| 3                  | VDDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDDA: +5V supply rail for the chip.                                                                                                                                                                  |  |  |  |  |

| 4                  | PWROK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Power OK. Open drain output. This pin will be opened in following condition 1. No over-current detected; 2. V <sub>REF_IN</sub> >0.6V; 3. FB > 75% of V <sub>REF_IN</sub> ; 4. S >3V.                |  |  |  |  |

| 5                  | GNDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ground for analog circuit. Connect it to system ground.                                                                                                                                              |  |  |  |  |

| 6                  | SS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Soft Start Pin. A capacitor should be attached in this pin to ground for soft start output clamping. This capacitor, along with an internal 12uA current source, set the output clamp ramp up speed. |  |  |  |  |

| 7                  | COMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | COMP Internal Error Amplifier Output Pin. This pin is available for compensation the control loop.                                                                                                   |  |  |  |  |

| 8                  | FB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Inverting Input of the Error Amplifier. This pin is available for compensation the control loop.                                                                                                     |  |  |  |  |

| 9                  | Non-inverting Input of the Error Amplifier. Voltage on this pin provides reference input to the PWM control loop. When the $V_{REF\_IN}$ voltage is less than 0.27V, the PWM is shut-down and the UGATE and LGAET are driven low. Due to its wide input range (0 ~ 3.6V), the $V_{REF\_IN}$ voltage can be raised slowly to perform the input clamp function. Besides, a special function is implemented in this IC to inform the reference provider of over current alarm. Each time as the OC occurs, $V_{REF\_IN}$ will be short to GND (through 170 ohms) for about 5~10uS. The reference provider can be aware of the OC condition by detecting this pulse. |                                                                                                                                                                                                      |  |  |  |  |

| 10                 | BG_REF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Internal Band gap Reference Voltage Output.                                                                                                                                                          |  |  |  |  |

| 11                 | воот                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Supply rail for the high-side MOSFET driver. A bootstrap circuit may be used to create a BOOT voltage or a separate 12V supply can be used.                                                          |  |  |  |  |

| 12                 | UGATE  High-Side N-Channel MOSFET Gate Drive Pin. This pin is also monitore the adaptive shoot through protection circuitry to determine when the high MOSFET has turned off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                      |  |  |  |  |

| 13                 | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ground for signal level circuit. Connect it to system ground.                                                                                                                                        |  |  |  |  |

| 14                 | Current limit threshold setting. Connect a resistor ( $R_{OCSET}$ ) between and the drain of the low-side MOSFET. An internal 72uA current so flow through $R_{ISEN}$ and cause a fixed voltage drop on it while the MOSFET is turned on. In the mean while, the W83320G compares the drop with the voltage across the low-side MOSFET and determines the current limit has been reached. The equation for over-current limit $I_{LIM} = (72uA * R_{ISEN})/R_{DSON}$                                                                                                                                                                                             |                                                                                                                                                                                                      |  |  |  |  |

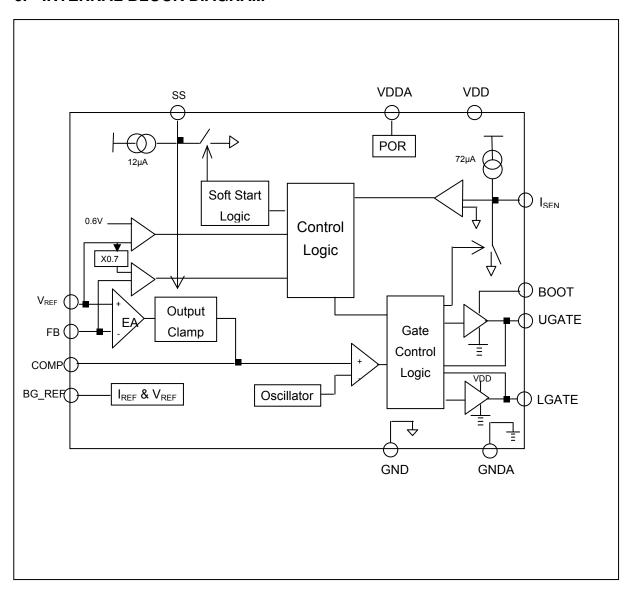

## 6. INTERNAL BLOCK DIAGRAM

Figure 2. W83320G Block Diagram

#### Soft-Start

When  $V_{DDA}$  and  $V_{DD}$  ramp over 4.3V and the voltage at pin  $V_{REF}$  ramps over 0.27V; the soft start capacitor begins to charge through an internal 12uA ( $I_{REF}/2$ ) current source. The error amplifier (and the PWM duty) is both output clamped by the voltage on soft-start pin  $V_{SS}$  and input clamped by the voltage on  $V_{REF}$ . There are two ways to soft start the power that's following the rising of the slower one between  $V_{SS}$  or  $V_{REF}$ ; during soft-start, PWOK is forced to low and the internal Over-Current Protection is triggered to work. 0.4V to 1.9V of  $V_{SS}$  is roughly mapping to 0 to 100% pulse-width. Smaller than 0.27V on  $V_{REF}$  will disable the PWM controller and discharge  $C_{SS}$ .

#### **MOSFET Gate Drivers**

The power for the high-side driver is flowing through the BOOT pin. This voltage can be supplied by a separate, higher voltage source, or supplied from a local charge pump structure or combination of the two.

Since the voltage of the low-side MOSFET gate and the high-side MOSFET gate are being monitored to determine the state of the MOSFET, it should be taken carefully to add external components between the gate drivers and their respective MOSFET gates. Doing so may interfere with the shoot-through protection.

#### **Current Limit**

Current limit is implemented by sensing the voltage across the low-side MOSFET while it is ON. This method enhances the converter's efficiency and reduces total cost by eliminating a current sensing resistor.

While low-side MOSFET is turned on, a constant current of 72uA ( $I_{REF}$  X 3) is forced through  $R_{OCSET}$  which is an external resistor connected between phase and  $I_{SEN}$ , causing a fixed voltage drop. This fixed voltage is compared against  $V_{DS}$  and if the latter is higher, the chip enters current limit mode. In the current limit mode both the high-side and low-side MOSFETS are turned off and the soft start capacitor  $C_{SS}$  will be discharged immediately. The  $V_{REF}$  is shorted to GND for 5~10uS to indicate the over current condition. After a 5mS delay, a soft-start cycle is initiated. If the cause of the over-current is still present after the delay interval, the current limit would be triggered again. The shut down - delay - soft start cycle will be repeated indefinitely until the over-current event been removed.

#### Input Tracking

When the  $V_{REF}$  voltage is less than 0.3V, the PWM is shut-down and the UGATE and LGATE are driven low. Due to its wide input range (0 ~ 3.6V), this chip is suitable for reference input tracking application. But note that the chip will be shut-down when  $V_{REF}$  <0.27V, a proper setting of  $C_{SS}$  is needed to clamp the output at initiation of start up and avoid output voltage step-up (and so a large inrush current).

## IREE and PWM Clock

The Internal reference current ( $I_{REF}$ ) is determined by the resistor between pin BG\_REF pin and GND ( $R_{SET}$ ) according to the following equation:

$$I_{REF} = 1.19V/R_{SET}$$

The nominal 200 kHz PWM clock can be adjusted ranging form 100 kHz to 400 kHz by changing  $I_{REF}$  according to the following equation:

Freq = 200 KHz  $*I_{REF}$  / 24uA;

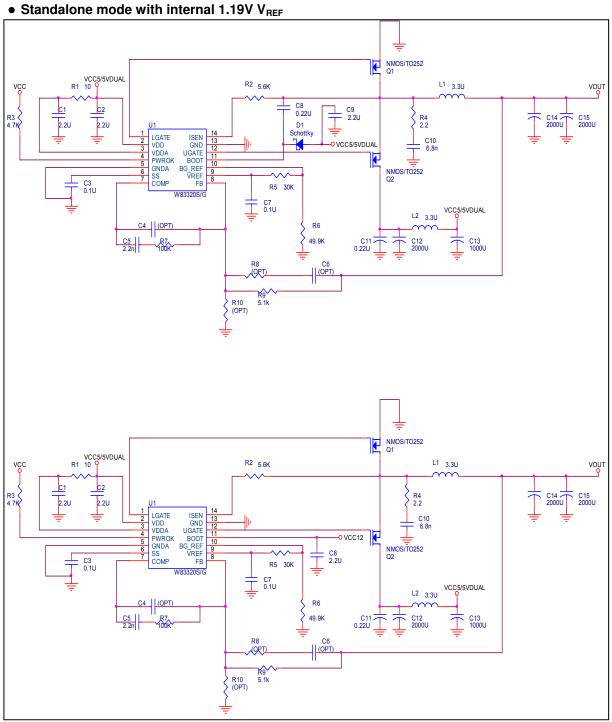

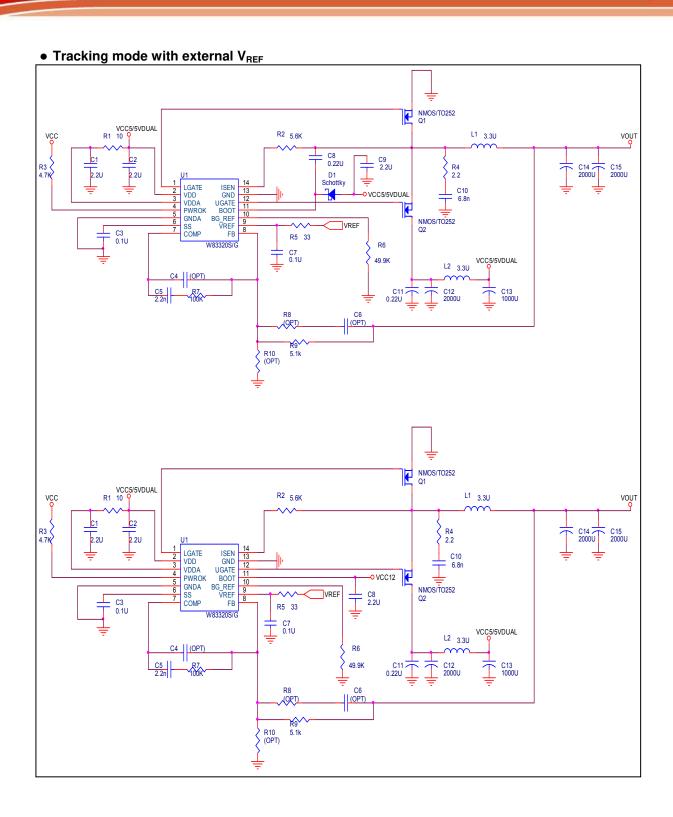

## 7. APPLICATION CIRCUIT

# 8. ABSOLUTE MAXIMUM RATINGS

| Supply Voltage VDD/VDDA                                  | 6V             |

|----------------------------------------------------------|----------------|

| BOOT & UGATE to GND                                      | 15V            |

| ullet Package Thermal Resistance SOP-14, $	heta$ JA      | 128° C/W       |

| Ambient Temperature Range                                | 0° C~+70° C    |

| Junction Temperature Range                               | -40° C~+125° C |

| Storage Temperature Range                                | -65° C~+150° C |

| Flectrostatic discharge protection (FSD) Human Body Mode | ±2KV           |

# 9. ELECTRICAL CHARACTERISTICS

| PARAMETER                            | SYMBOL                 | TEST CONDITIONS                               | MIN  | TYP  | MAX | UNITS            |

|--------------------------------------|------------------------|-----------------------------------------------|------|------|-----|------------------|

| V <sub>CC</sub> SUPPLY CURRENT       |                        |                                               |      |      |     |                  |

| Nominal Supply                       | I <sub>CC</sub>        | EN=V <sub>CC</sub> ; UGATE and LGATE Open     | -    | 3    | -   | mA               |

| POWER-ON RESET                       |                        |                                               |      |      |     |                  |

| Rising $V_{\text{DD}}$<br>Threshold  |                        |                                               | -    | 4.3  | -   | V                |

| Falling V <sub>DD</sub><br>Threshold |                        |                                               | -    | 3.7  | -   | V                |

| V <sub>REF</sub> Enable              |                        |                                               | -    | 0.27 | -   | V                |

| OSCILLATOR                           |                        |                                               |      |      |     |                  |

| Free Running<br>Frequency            |                        | R <sub>SET</sub> =49.6K                       | 160  | 200  | 240 | kHz              |

| Ramp Amplitude                       | $\Delta V_{OSC}$       | R <sub>SET</sub> =49.6K                       | -    | 1.5  | -   | $V_{P-P}$        |

| REFERENCE                            |                        |                                               |      |      |     |                  |

| Reference Voltage Tolerance          | $V_{REF}$              |                                               | -1.5 | -    | 1.5 | %                |

| Reference Voltage                    |                        |                                               | -    | 1.19 | -   | V                |

| ERROR AMPLIFIER                      |                        |                                               |      |      |     |                  |

| DC Gain                              |                        |                                               | -    | 80   | -   | dB               |

| Gain-Bandwidth                       |                        |                                               | -    | 5    | -   | MHz              |

| Slew Rate                            |                        |                                               | -    | 4    | -   | V/ <sub>µS</sub> |

| GATE DRIVERS                         |                        |                                               |      |      |     |                  |

| High-side Gate<br>Source             | I <sub>HGATE-SRC</sub> | V <sub>BOOT</sub> =12V,V <sub>UGATE</sub> =6V | 250  | -    | -   | mA               |

| High-side Gate Sink                  | I <sub>HGATE-SNK</sub> | V <sub>BOOT</sub> =12V,V <sub>UGATE</sub> =6V | 600  | -    | -   | mA               |

| Low-side Gate<br>Source              | I <sub>LGATE-SRC</sub> | V <sub>CC</sub> =5V, V <sub>LGATE</sub> =2.5V | 250  | -    | -   | mA               |

| Low-side Gate Sink                   | I <sub>LGATE-SNK</sub> | V <sub>CC</sub> =5V, V <sub>LGATE</sub> =2.5V | 300  | -    | -   | mA               |

| PROTECTION                           |                        |                                               |      |      |     |                  |

| I <sub>SEN</sub> Current Source      | I <sub>SEN</sub>       |                                               | 64   | 72   | 80  | μΑ               |

| Soft-Start Current                   | I <sub>SS</sub>        |                                               | 10   | 12   | 14  | μΑ               |

## 10. TYPICAL PERFORMANCE CHARACTERISTICS

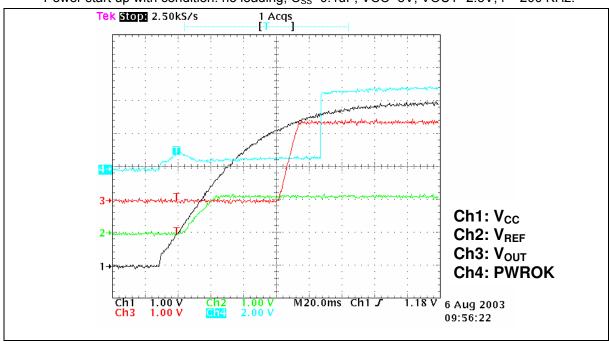

Power start up with condition: no loading; C<sub>SS</sub>=0.1uF; VCC=5V; VOUT=2.5V; f = 200 KHz.

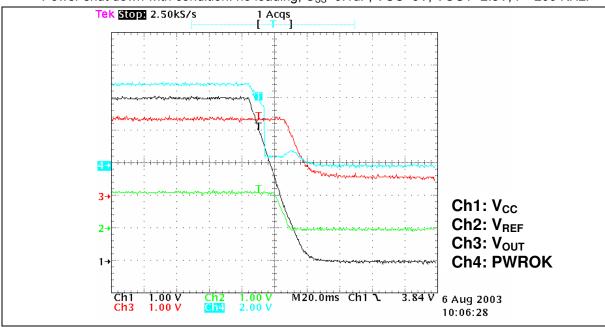

- Power shut down with condition: no loading; C<sub>SS</sub>=0.1uF; VCC=5V; VOUT=2.5V; f = 200 KHz.

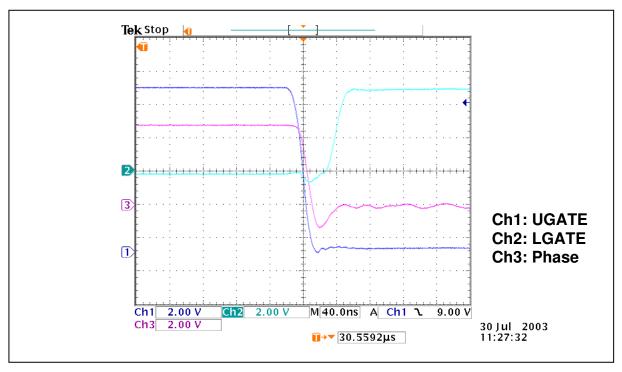

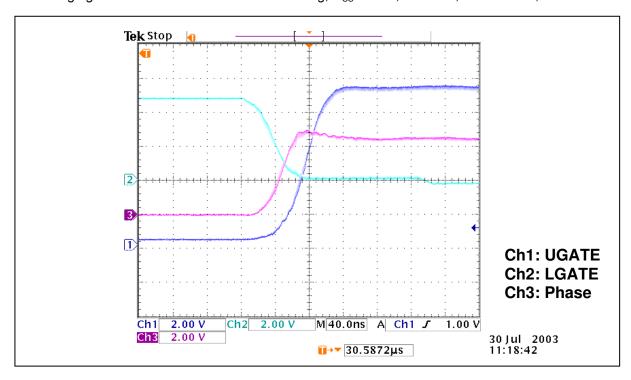

High gate switch off with condition: no loading; C<sub>SS</sub>=0.1uF; VCC=5V; VOUT=2.5V; f = 200 KHz.

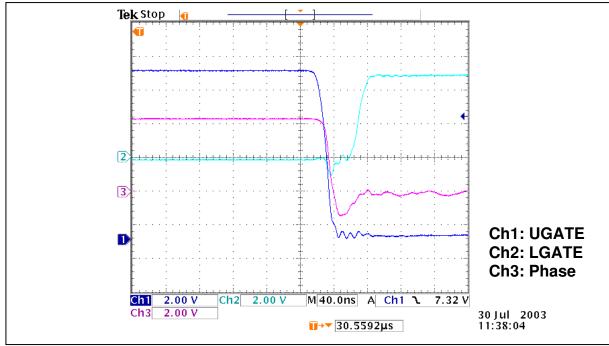

High gate switch off with condition: 2Amp loading;  $C_{SS}=0.1uF$ ; VCC=5V; VOUT=2.5V; f = 200 KHz.

# nuvoton

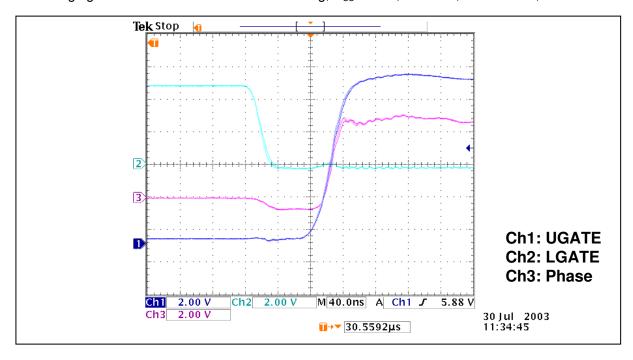

- High gate switch on with condition: no loading; C<sub>SS</sub>=0.1uF; VCC=5V; VOUT=2.5V; f = 200 KHz.

High gate switch on with condition: no loading; C<sub>SS</sub>=0.1uF; VCC=5V; VOUT=2.5V; f = 200 KHz.

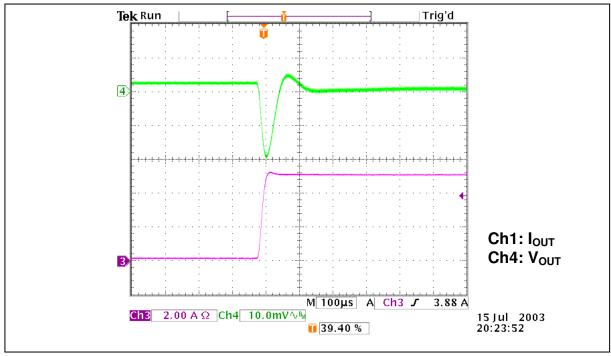

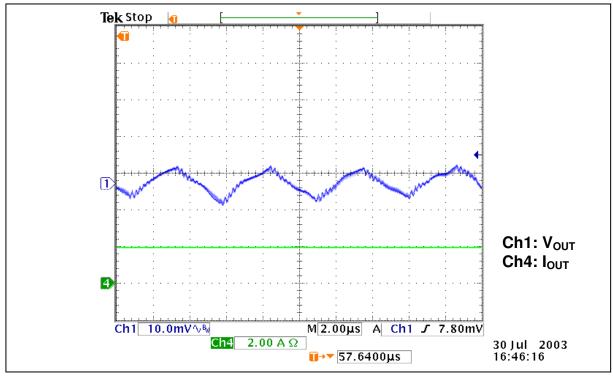

Load transient response with condition: 0.5Amp to 5.5Amp; C<sub>ss</sub>=0.1uF; VIN=5V; VOUT=2.5V; f = 200 KHz.

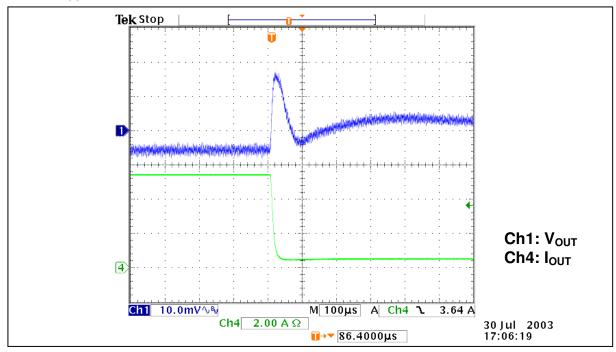

Load transient response with condition: 5.5Amp to 0.5Amp; C<sub>SS</sub>=0.1uF; VIN=5V; VOUT=2.5V; f = 200 KHz.

Output load transient response with condition: IOUT=2Amp; C<sub>SS</sub>=0.1uF; VIN=5V; VOUT=2.5V; f = 200 KHz.

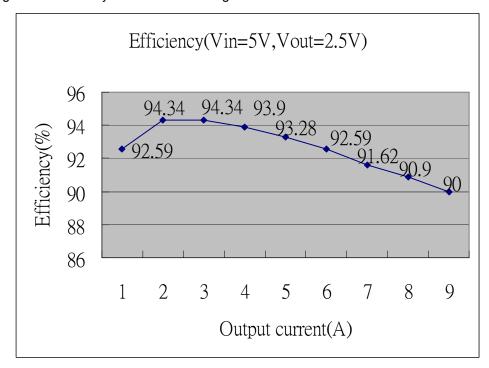

- Regulation efficiency with various loading

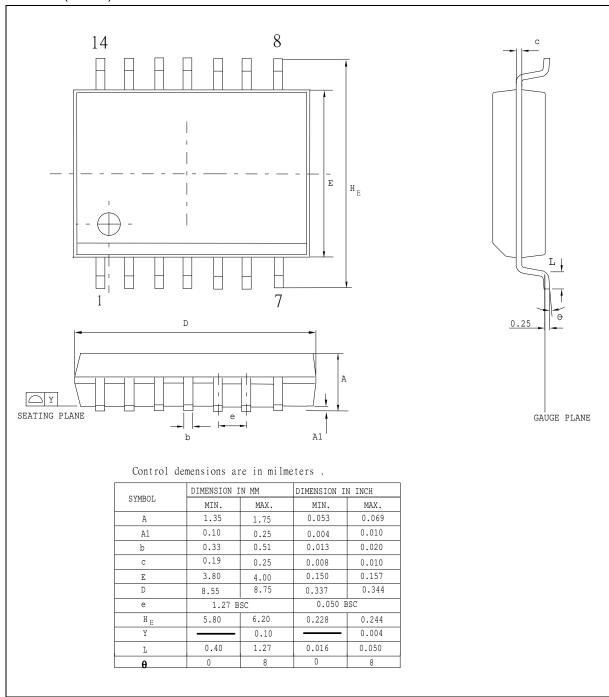

## 11. PACKAGE DIMENSION OUTLINE

## 14L SOP (150mil)

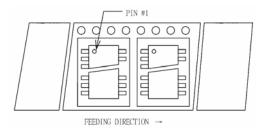

#### TAPING SPECIFICATION

14 Pin SOP Package

## 12. ORDERING INSTRUCTION

| PART<br>NUMBER | PACKAGE TYPE                | SUPPLIED AS                                        | PRODUCTION FLOW          |

|----------------|-----------------------------|----------------------------------------------------|--------------------------|

| W83320G        | 14PIN SOP (Pb-free package) | E Shape: 56 units/Tube<br>T Shape: 2,500 units/T&R | Commercial, 0°C to +70°C |

### 13. TOP MARKING SPECIFICATION

Left Line: Nuvoton Logo

1<sup>st</sup> Line: Part No – **W83320G** is for Pb-free package.

2<sup>nd</sup> Line: IC Tracking Code

$3^{rd}$  Line: Manufacturing Date Code ( $\underline{X}$   $\underline{XX}$ ) + Assembly Code ( $\underline{X}$ ) + IC Version ( $\underline{X}$ )

523: packages assembled in Year 05', week 23

**G**: assembly house ID; G means GR, O means OSE, etc.

**A**: the IC version (A means A, B means B and C means C...etc.)

## **Important Notice**

Nuvoton products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further more, Nuvoton products are not intended for applications wherein failure of Nuvoton products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.

Nuvoton customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper use or sales.

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.