## Dual T1/E1 Line Interface

## **Features**

- Dual T1/E1 Line Interface

- Low Power Consumption (Typically 220mW per Line Interface)

- Matched Impedance Transmit Drivers

- Common Transmit and Receive Transformers for all Modes

- Selectable Jitter Attenuation for Transmit or Receive Paths

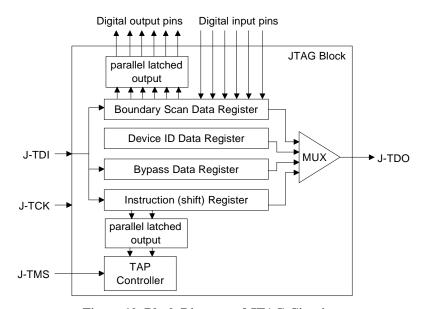

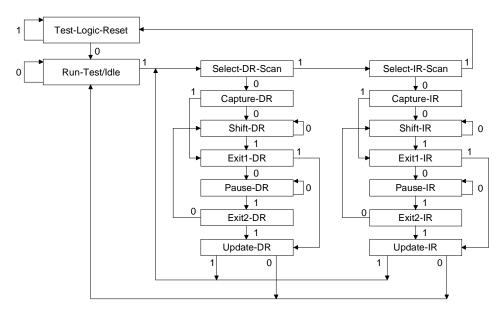

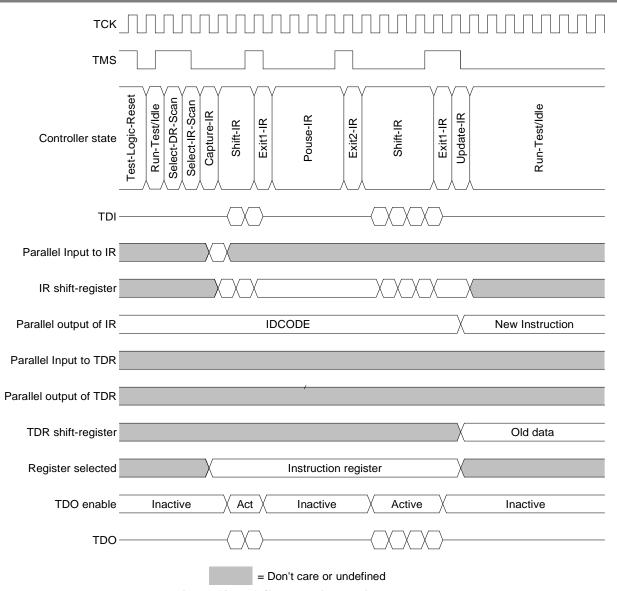

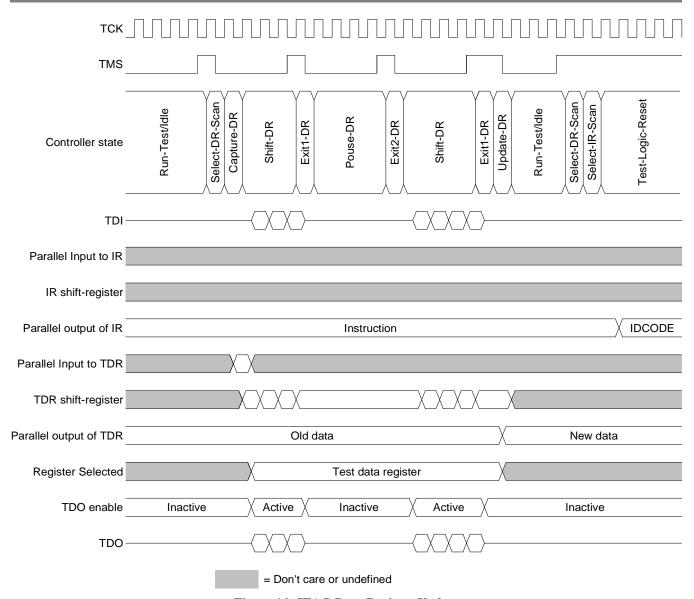

- Supports JTAG Boundary Scan

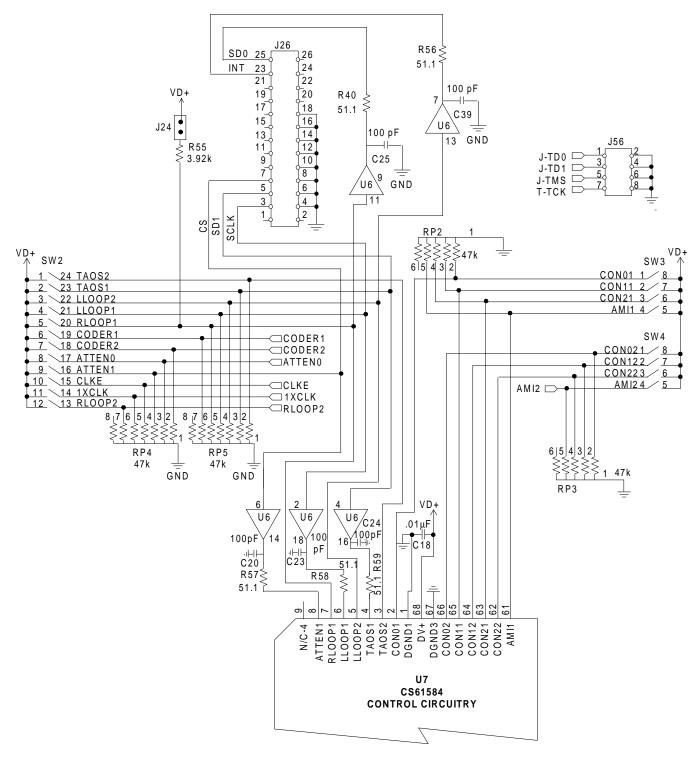

- Hardware Mode Derivative of the CS61584

## **General Description**

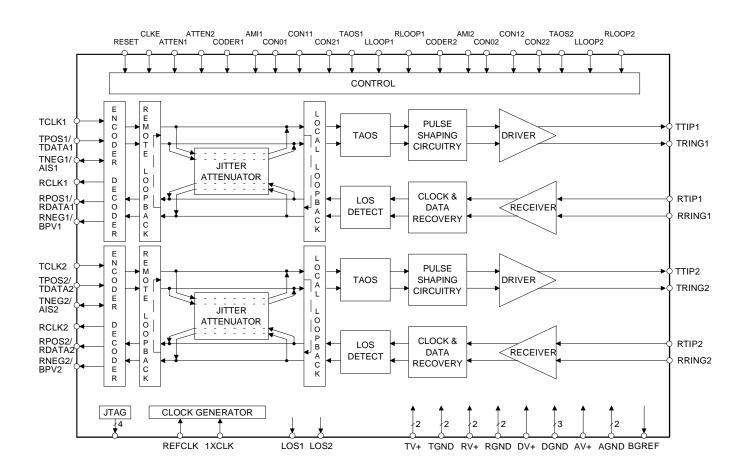

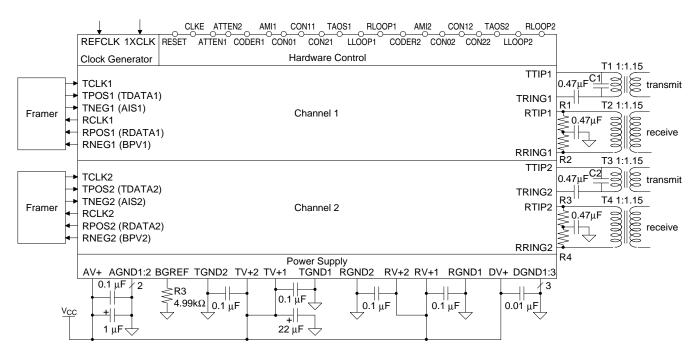

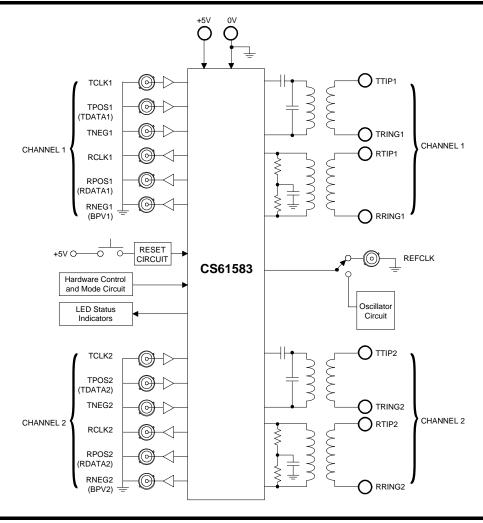

The CS61583 is a dual line interface for T1/E1 applications, designed for high-volume cards where low power and high density are required. Each channel features individual control and status pins which eliminates the need for external microprocessor support. The matched impedance drivers reduce power consumption and provide substantial return loss to insure superior T1/E1 pulse quality.

The CS61583 provides JTAG boundary scan to enhance system testability and reliability. The CS61583 is a 5 volt device and is a hardware mode derivative of the CS61584.

#### **ORDERING INFORMATION**

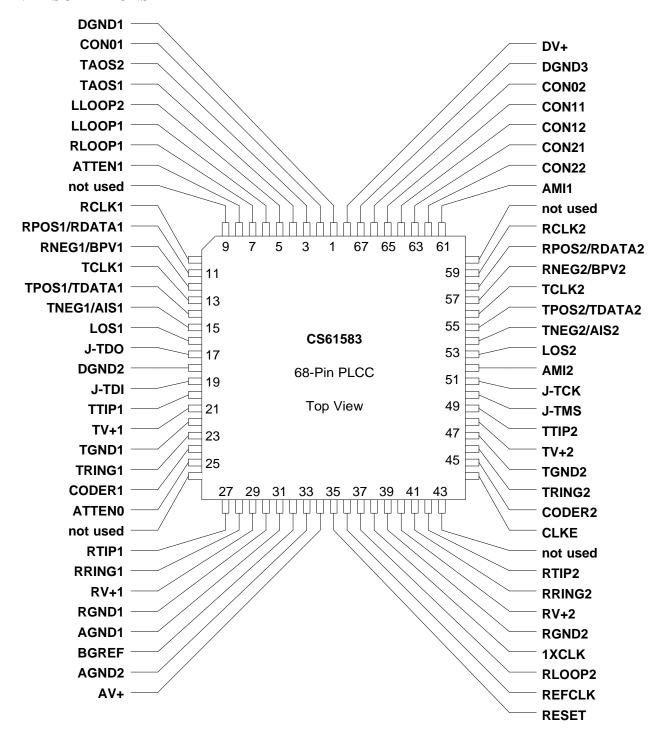

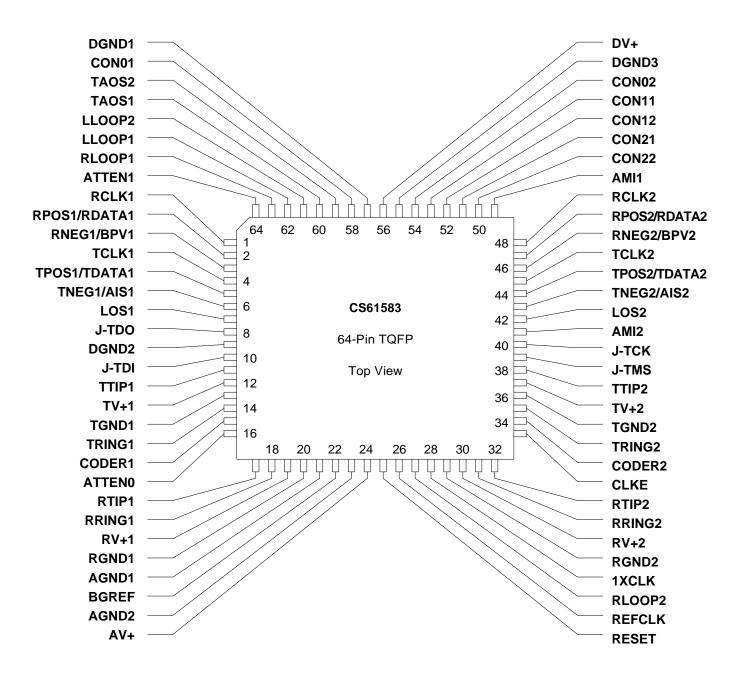

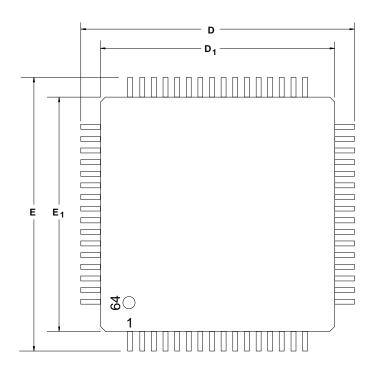

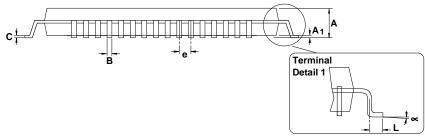

CS61583-IL5: 68-pin PLCC, -40 to +85 °C CS61583-IQ5: 64-pin TQFP, -40 to +85 °C

## **Table of Contents**

| Block Diagram                    |

|----------------------------------|

| Specifications                   |

| Absolute Maximum Ratings3        |

| Recommended Operating Conditions |

| Digital Characteristics          |

| Analog Specifications            |

| Receiver                         |

| Jitter Attenuator                |

| Transmitter                      |

| Switching Characteristics        |

| T1 Clock/Data6                   |

| E1 Clock/Data6                   |

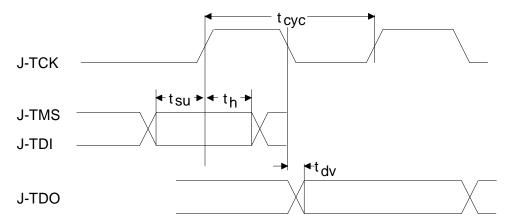

| JTAG8                            |

| General Description              |

| Overview9                        |

| Transmitter                      |

| Receiver                         |

| Jitter Attenuator                |

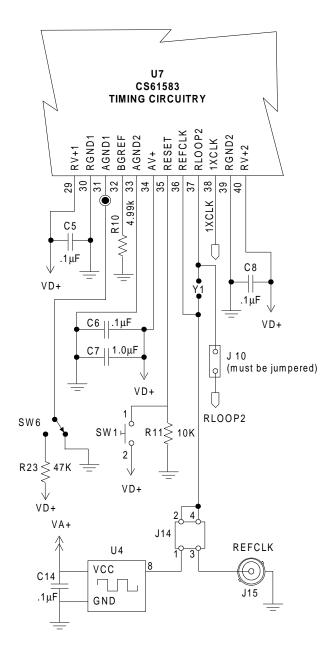

| Reference Clock                  |

| Power-Up Reset                   |

| Line Control and Monitoring      |

| Line Code Encoder/Decoder        |

| Alarm Indication Signal          |

| Bipolar Violation Detection      |

| Loss of Signal14                 |

| Transmit All Ones                |

| Local Loopback                   |

| Remote Loopback14                |

| Reset Pin                        |

| JTAG Boundary Scan               |

| Pin Description                  |

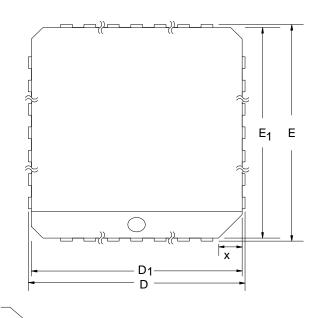

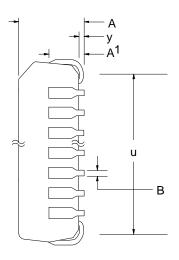

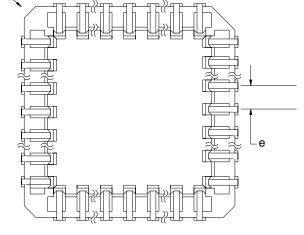

| Physical Dimensions              |

| Applications                     |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                             | Symbol           | Min        | Max         | Units |

|-------------------------------------------------------|------------------|------------|-------------|-------|

| DC Supply (TV+1, TV+2, RV+1, RV+2, AV+, DV+) (Note 1) |                  | -          | 6.0         | V     |

| Input Voltage (Any Pin)                               | Vin              | RGND - 0.3 | (RV+) + 0.3 | V     |

| Input Current (Any Pin) (Note 2)                      | lin              | -10        | 10          | mA    |

| Ambient Operating Temperature                         | TA               | -40        | 85          | °C    |

| Storage Temperature                                   | T <sub>stg</sub> | -65        | 150         | Ô     |

WARNING: Operations at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

Notes: 1. Referenced to RGND1, RGND2, TGND1, TGND2, AGND, DGND at 0V.

2. Transient currents of up to 100 mA will not cause SCR latch-up.

## RECOMMENDED OPERATING CONDITIONS

| Par                                 | Parameter           |                                                       |    |                     |                   | Max                 | Units          |

|-------------------------------------|---------------------|-------------------------------------------------------|----|---------------------|-------------------|---------------------|----------------|

| DC Supply (TV+1, TV+2, RV           | /+1, RV+2, AV       | '+, DV+) (Note 3)                                     |    | 4.75                | 5.0               | 5.25                | V              |

| Ambient Operating Tempera           | ture                |                                                       | TA | -40                 | 25                | 85                  | °C             |

| Power Consumption<br>(Each Channel) | T1<br>T1<br>E1, 75Ω | (Notes 4 and 5)<br>(Notes 4 and 6)<br>(Notes 4 and 5) |    | -                   | 310<br>220<br>275 | -                   | mW<br>mW<br>mW |

|                                     | E1, $120\Omega$     | (Notes 4 and 5)                                       |    | -                   | 275               | -                   | mW             |

| REFCLK Frequency                    | T1                  | 1XCLK = 1                                             |    | 1.544 -<br>100 ppm  | 1.544             | 1.544 +<br>100 ppm  | MHz            |

|                                     | T1                  | 1XCLK = 0                                             |    | 12.352 -<br>100 ppm | 12.352            | 12.352 +<br>100 ppm | MHz            |

|                                     | E1                  | 1XCLK = 1                                             |    | 2.048 -<br>100 ppm  | 2.048             | 2.048 +<br>100 ppm  | MHz            |

|                                     | E1                  | 1XCLK = 0                                             |    | 16.384 -<br>100 ppm | 16.384            | 16.384 +<br>100 ppm | MHz            |

Notes: 3. TV+1, TV+2, AV+, DV+, RV+1, RV+2 should be connected together. TGND1, TGND2, RGND1, RGND2, DGND1, DGND2, DGND3 should be connected together.

- 4. Power consumption while driving line load over operating temperature range. Includes IC and load. Digital input levels are within 10% of the supply rails and digital outputs are driving a 50 pF capacitive load.

- 5. Assumes 100% ones density and maximum line length at 5.25V.

- 6. Assumes 50% ones density and 300ft. line length at 5.0V.

## **DIGITAL CHARACTERISTICS** (T<sub>A</sub> = -40 to 85 °C; power supply pins within ±5% of nominal)

| Parameter                                           |               |          |     | Min       | Тур | Max | Units |

|-----------------------------------------------------|---------------|----------|-----|-----------|-----|-----|-------|

| High-Level Input Voltage                            |               | (Note 7) | VIH | (DV+)-0.5 | -   | -   | V     |

| Low-Level Input Voltage                             |               | (Note 7) | VIL | -         | -   | 0.5 | V     |

| High-Level Output Voltage (Digital pins)            | IOUT = -40 μA | (Note 8) | Vон | (DV+)-0.3 | -   | -   | V     |

| Low-Level Output Voltage (Digital pins)             | IOUT = 1.6 mA | (Note 8) | VoL | -         | -   | 0.3 | V     |

| Input Leakage Current (Digital pins except J-TMS, a | nd J-TDI)     |          |     | -         | -   | ±10 | μΑ    |

Notes: 7. Digital inputs are designed for CMOS logic levels.

8. Digital outputs are TTL compatible and drive CMOS levels into a CMOS load.

## **ANALOG SPECIFICATIONS** (T<sub>A</sub> = -40 to 85 °C; power supply pins within ±5% of nominal)

|                                                         | Min                                                            | Тур                                             | Max                  | Units               |                      |                |

|---------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|----------------------|---------------------|----------------------|----------------|

| Receiver                                                |                                                                | 1                                               |                      | 1                   |                      |                |

| RTIP/RRING Differential Inp                             | out Impedance                                                  |                                                 | -                    | 20k                 | -                    | Ω              |

| Sensitivity Below DSX-1 (0                              | dB = 2.4 V)                                                    |                                                 | -13.6                | -                   | -                    | dB             |

| Loss of Signal Threshold                                |                                                                |                                                 | -                    | 0.3                 | -                    | V              |

| Data Decision Threshold                                 | T1, DSX-1<br>E1                                                | (Note 9)<br>(Note 10)<br>(Note 11)<br>(Note 12) | 60<br>55<br>45<br>40 | 65<br>-<br>50<br>-  | 70<br>75<br>55<br>60 | % of<br>Peak   |

| Allowable Consecutive Zero                              | s before LOS                                                   |                                                 | 160                  | 175                 | 190                  | bits           |

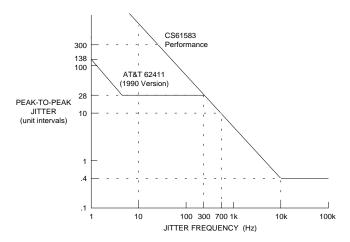

| Receiver Input Jitter<br>Tolerance (DSX-1, E1)          | 10 Hz and below<br>2 kHz<br>10 kHz - 100 kHz                   | (Note 13)                                       | 300<br>6.0<br>0.4    | -<br>-<br>-         |                      | UI<br>UI<br>UI |

| Receiver Return Loss                                    | 51 kHz - 102 kHz<br>102 kHz - 2.048 MH;<br>2.048 MHz - 3.072 N | ,                                               | 12<br>18<br>14       | -<br>-<br>-         | -<br>-<br>-          | dB<br>dB<br>dB |

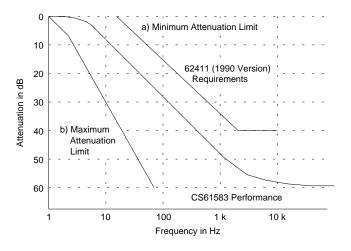

| Jitter Attenuator                                       |                                                                |                                                 |                      |                     |                      |                |

| Jitter Attenuation Curve Corner Frequency               | T1<br>E1                                                       | (Notes 14 and 15)                               | -                    | 4<br>5.5            | -                    | Hz<br>Hz       |

| Attenuation at 10 kHz Jitter                            | -                                                              | 60                                              | -                    | dB                  |                      |                |

| Attenuator Input Jitter Toler (Before Onset of FIFO Ove | 28                                                             | 43                                              | -                    | UI <sub>pk-pk</sub> |                      |                |

Notes: 9. For input amplitude of 1.2  $V_{pk}$  to 4.14  $V_{pk}$

- 10. For input amplitude of 0.5  $V_{pk}$  to 1.2  $V_{pk}$ , and 4.14  $V_{pk}$  to 5.0  $V_{pk}$

- 11. For input amplitude of 1.07  $V_{pk}$  to 4.14  $V_{pk}$ ,

- 12. For input amplitude of 4.14 V<sub>pk</sub> to 5.0 V<sub>pk</sub>,

- 13. Jitter tolerance increases at lower frequencies. Refer to the Receiver section.

- 14. Not production tested. Parameters guaranteed by design and characterization.

- 15. Attenuation measured with sinusoidal input jitter equal to 3/4 of measured jitter tolerance. Circuit attenuates jitter at 20 dB/decade above the corner frequency. Output jitter can increase significantly when more than 28 UI's are input to the attenuator. Refer to the Jitter Attenuator section.

## **ANALOG SPECIFICATIONS** (T<sub>A</sub> = -40 to 85 °C; power supply pins within ±5% of nominal)

| Power in 2 kHz band about 1.544 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Units             | Max   | Тур   | Min    |                                                     | Parameter                    |                        |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------|--------|-----------------------------------------------------|------------------------------|------------------------|--|--|--|

| E1, 75Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |       |       |        |                                                     | er                           | Transmitter            |  |  |  |

| E1, 120Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |       |       |        | (Note 16)                                           | t Pulse Amplitudes           | AMI Output Pulse Am    |  |  |  |

| T1, DSX-1 (Note 19) 2.4 3.0 3.6  Recommended Transmitter Output Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V                 | 2.6   | 2.37  | 2.14   | (Note 17)                                           | E1, 75Ω                      |                        |  |  |  |

| Recommended Transmitter Output Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V                 |       |       |        | (Note 18)                                           | E1, 120Ω                     |                        |  |  |  |

| T1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V                 | 3.6   | 3.0   | 2.4    | (Note 19)                                           | T1, DSX-1                    |                        |  |  |  |

| E1, 75Ω E1, 120Ω  Ditter Added During Remote Loopback  8 kHz - 40 kHz 10 Hz - 8 kHz 10 Hz - 40 kHz Broad Band (Note 20)  Power in 2 kHz band about 772 kHz  Referenced to power in 2 kHz band at 772 kHz)  Positive to Negative Pulse Imbalance E1, amplitude at center of pulse interval E1, amplitude at center of pulse interval E1, width at 50% of nominal amplitude  Transmitter Return Loss  (Notes 14, 21, and 22)  S1 kHz - 102 kHz 102 kHz 2.048 MHz 2.048 MHz 3.072 MHz  (Note 23)  - 57.4 - 0.005 - 0.008 - 0.010 - 0.015 - 0.015 - 17.9  - 29 -38 - 0.2 - 38 - 0.2 - 38 - 0.2 - 38 - 0.2 - 38 - 0.2 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 50.5 - 5  |                   |       |       |        | (Note 16)                                           | nded Transmitter Output Load | Recommended Trans      |  |  |  |

| E1, 120Ω                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ω                 | -     | 76.6  | -      |                                                     | T1                           |                        |  |  |  |

| Jitter Added During Remote Loopback  8 kHz - 40 kHz 10 Hz - 40 kHz Broad Band (Note 20) - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.015 - 0.01 | Ω                 | -     | 57.4  | -      |                                                     | E1, 75Ω                      |                        |  |  |  |

| Remote Loopback                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ω                 | -     | 90.6  | -      |                                                     | E1, 120Ω                     |                        |  |  |  |

| 10 Hz - 40 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U                 | -     | 0.005 |        |                                                     | d During 10 Hz - 8 kHz       | Jitter Added During    |  |  |  |

| Broad Band   (Note 20)   -   0.015   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UI                | -     | 0.008 | -      |                                                     | opback 8 kHz - 40 kHz        | Remote Loopback        |  |  |  |

| Power in 2 kHz band about 772 kHz  (Notes 14 and 21) (DSX-1 only)  Power in 2 kHz band about 1.544 MHz (referenced to power in 2 kHz band at 772 kHz)  Positive to Negative Pulse Imbalance (Notes 14 and 21) T1, DSX-1 E1, amplitude at center of pulse interval E1, width at 50% of nominal amplitude  (Notes 14, 21, and 22)  Transmitter Return Loss (Notes 14, 21, and 22)  S1 kHz - 102 kHz 102 kHz - 2.048 MHz 2.048 MHz - 3.072 MHz  (Note 23)  - 15  12.6  15 17.9  - 29 - 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | UI                | -     | 0.010 | -      |                                                     | 10 Hz - 40 kHz               |                        |  |  |  |

| CDSX-1 only    12.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UI                | -     | 0.015 | -      | (Note 20)                                           | Broad Band                   |                        |  |  |  |

| (referenced to power in 2 kHz band at 772 kHz)       (DSX-1 only)       -29       -38       -         Positive to Negative Pulse Imbalance       (Notes 14 and 21)       -       0.2       0.5         E1, amplitude at center of pulse interval E1, width at 50% of nominal amplitude       -5       -       +5         Transmitter Return Loss       (Notes 14, 21, and 22)       -       -       +5         51 kHz - 102 kHz       18       25       -         102 kHz - 2.048 MHz       14       18       -         2.048 MHz - 3.072 MHz       10       12       -         E1 Short Circuit Current       (Note 23)       -       -       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | dBm               | 17.9  | 15    | 12.6   |                                                     | kHz band about 772 kHz       | Power in 2 kHz band    |  |  |  |

| T1, DSX-1 E1, amplitude at center of pulse interval E1, width at 50% of nominal amplitude  -5 -1 -5 -1 -5 -1 -5 -1 -5 -5 -1 -5 -5 -5 -5 -5 -5 -5 -5 -5 -5 -5 -5 -5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB                | -     | -38   | -29    |                                                     |                              |                        |  |  |  |

| T1, DSX-1 E1, amplitude at center of pulse interval E1, width at 50% of nominal amplitude  -5 -1 -5 -1 -5 -1 -5 -1 -5 -5 -1 -5 -5 -5 -5 -5 -5 -5 -5 -5 -5 -5 -5 -5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |       |       |        | (Notes 14 and 21)                                   | Negative Pulse Imbalance     | Positive to Negative F |  |  |  |

| E1, width at 50% of nominal amplitude -5 - +5  Transmitter Return Loss (Notes 14, 21, and 22) 51 kHz - 102 kHz 18 25 - 102 kHz - 2.048 MHz 14 18 - 2.048 MHz - 3.072 MHz 10 12 -  E1 Short Circuit Current (Note 23) - 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | dB                | 0.5   | 0.2   | -      | ,                                                   |                              | · ·                    |  |  |  |

| Transmitter Return Loss (Notes 14, 21, and 22) 51 kHz - 102 kHz 18 25 - 102 kHz - 2.048 MHz 14 18 - 2.048 MHz - 3.072 MHz 10 12 -  E1 Short Circuit Current (Note 23) - 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | %                 | +5    | -     |        | enter of pulse interval                             | E1, amplitude at c           |                        |  |  |  |

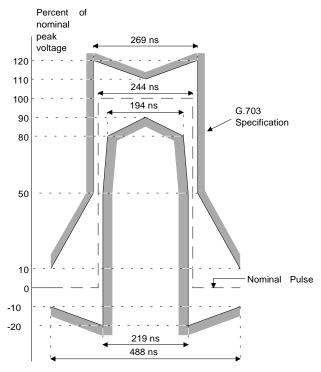

| 51 kHz - 102 kHz 18 25 - 102 kHz - 2.048 MHz 14 18 - 2.048 MHz - 3.072 MHz 10 12 - 50 E1 Short Circuit Current (Note 23) - 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | %                 | +5    | -     | -5     | of nominal amplitude                                | E1, width at 50% of          |                        |  |  |  |

| 102 kHz - 2.048 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |       |       |        | Notes 14, 21, and 22)                               | Return Loss (                | Transmitter Return Lo  |  |  |  |

| 2.048 MHz - 3.072 MHz 10 12 - E1 Short Circuit Current (Note 23) 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | dB                | -     | 25    | 18     | ,                                                   | 51 kHz - 102 kHz             |                        |  |  |  |

| E1 Short Circuit Current (Note 23) 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | dB                | -     |       |        |                                                     |                              |                        |  |  |  |

| ` '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | dB                | -     | 12    | 10     | MHz                                                 | 2.048 MHz - 3.072            |                        |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mA <sub>rms</sub> | 50    | -     | -      | (Note 23)                                           | Fircuit Current              | E1 Short Circuit Curre |  |  |  |

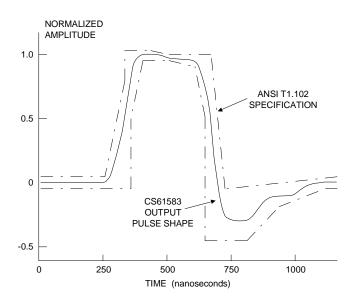

| E1 and DSX-1 Output Pulse Rise/Fall Times (Note 24) - 25 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns                | -     | 25    | -      | E1 and DSX-1 Output Pulse Rise/Fall Times (Note 24) |                              |                        |  |  |  |

| E1 Pulse Width (at 50% of peak amplitude) - 244 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ns                | -     | 244   | -      | •                                                   |                              |                        |  |  |  |

| E1 Pulse Amplitude E1, 75Ω -0.237 - 0.237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V                 | 0.237 | -     | -0.237 |                                                     | mplitude E1, 75Ω             | E1 Pulse Amplitude     |  |  |  |

| for a space E1, $120\Omega$ -0.3 - 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V                 |       | -     |        |                                                     | •                            | •                      |  |  |  |

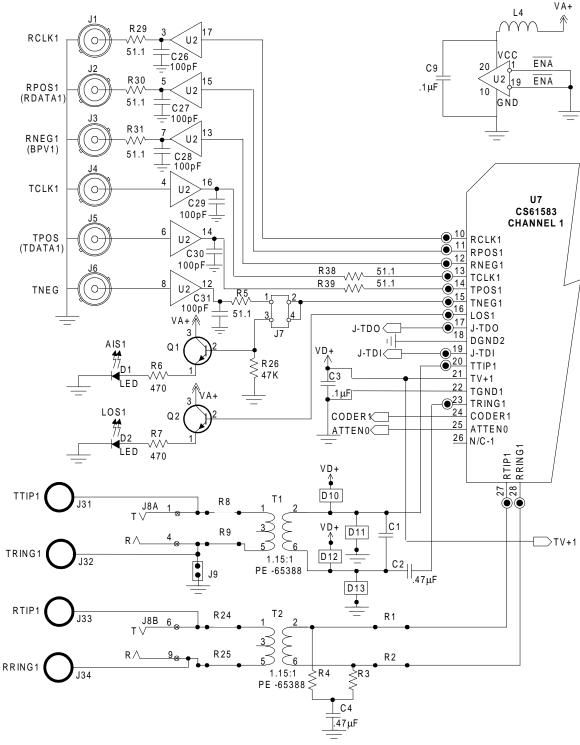

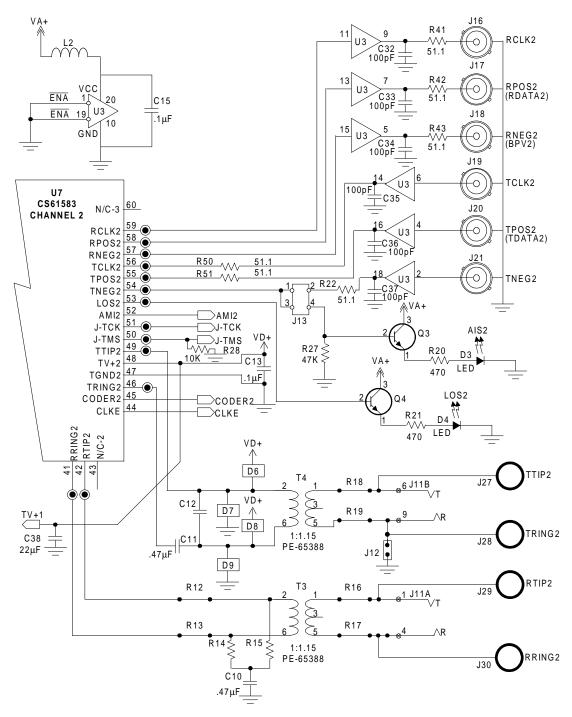

Notes: 16. Using a transformer that meets the specifications in the Applications section.

- 17. Measured across 75  $\Omega$  at the output of the transmit transformer for CON2/1/0 = 0/0/0.

- 18. Measured across 120  $\Omega$  at the output of the transmit transformer for CON2/1/0 = 0/0/1.

- 19. Measured at the DSX-1 cross-connect for line length settings CON2/1/0 = 0/1/0, 0/1/1, 1/0/0, 1/0/1, and 1/1/0 after the appropriate length of #22 ABAM cable specified in Table 1.

- 20. Input signal to RTIP/RRING is jitter free. Values will reduce slightly if jitter free clock is input to TCLK.

- 21. Typical performance using the line interface circuitry recommended in the Applications section.

- 22. Return loss = 20 log  $_{10}$  ABS(( $z_1+z_0$ )/( $z_1-z_0$ )) where  $z_1$ =impedance of the transmitter or receiver, and  $z_0$ =cable impedance.

- 23. Transformer secondary shorted with 0.5  $\Omega$  resistor during the transmission of 100% ones.

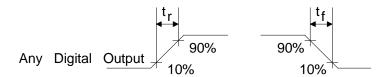

- 24. At transformer secondary and measured from 10% to 90% of amplitude.