## System Reset IC with Watchdog Timer

### FEATURES

- •Full compatible with NJM2102

- Detection voltage

- Watchdog timer function

- Reset output of both positive and negative logic

V<sub>SI</sub>=4.2V±1.0%

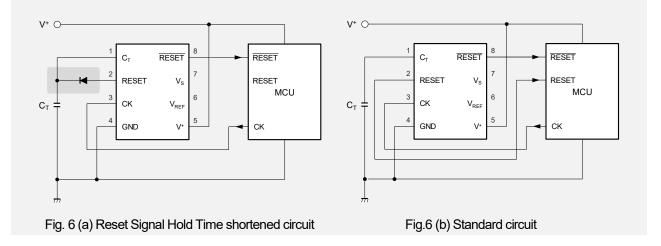

DMP8

- •Operating temperature Ta=-40 to 125°C

- •Low quiescent current 320µA typ.

- •Low reset operation voltage 0.8V typ.

- Package

■GENERAL DESCRIPTION

The NJU2102A is a system reset IC with watchdog timer to detect the abnormal conditions, such as shutdown of all supply voltages at once, or sudden voltage down and then generate the reset signal.

It is possible to direct replacement from NJM2102.

Furthermore, it improves usability by extending operating temperature, standardizing AC characteristics, and making each parameter highly accurate.

### ■APPLICATION

- Industrial equipment

- Housing and facility equipment

- OA equipment

- Amusement equipment

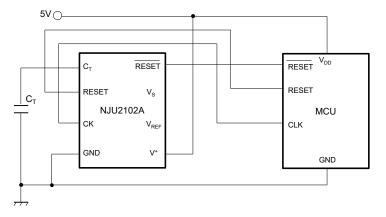

### **TYPICAL APPLICATION**

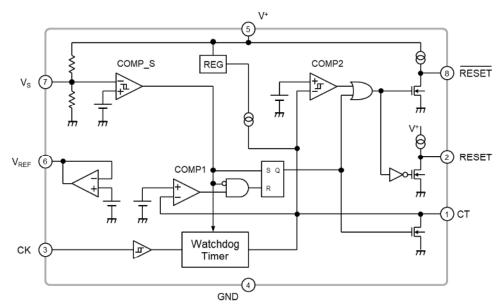

### BLOCK DIAGRAM

New Japan Radio Co., Ltd. www.njr.com

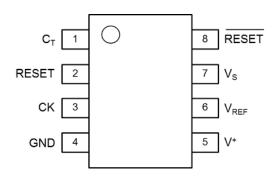

### **■PIN CONFIGURATION**

| DMP8    |                  |                                    |

|---------|------------------|------------------------------------|

| PIN No. | PIN NAME         | FUNCTION                           |

|         |                  | Connects Capacitor pin for setting |

| 1       | C <sub>T</sub>   | WDT monitor time, WDT reset time,  |

|         |                  | and Reset signal hold time.        |

| 2       | RESET            | RESET output pin. (Active High)    |

| 3       | CK               | Clock input pin.                   |

| 4       | GND              | GND pin.                           |

| 5       | V*               | Power Supply pin.                  |

| 6       | V <sub>REF</sub> | Output reference voltage pin.      |

| 7       | Vs               | Comparator S input pin.            |

| 8       | RESET            | RESET output pin. (Active Low)     |

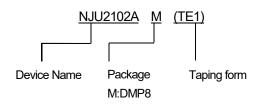

### ■PRODUCT NAME INFORMATION

### **■ORDERING INFORMATION**

| PRODUCT NAME   | PACKAGE<br>OUTLINE | RoHS | Halogen-<br>Free | TERMINAL<br>FINISH | MARKING | WEIGHT<br>(mg) | MOQ<br>(pcs) |

|----------------|--------------------|------|------------------|--------------------|---------|----------------|--------------|

| NJU2102AM(TE1) | DMP8               | 0    | 0                | Sn-2Bi             | 2102A   | 95             | 2000         |

Note) "-" is non-evaluation. Please contact your sales representative for more information.

*New Japan Radio Co., Ltd.* www.njr.com

### ■ABSOLUTE MAXIMUM RATINGS

| PARAMETER                   | SYMBOL             | RATINGS                                 | UNIT  |

|-----------------------------|--------------------|-----------------------------------------|-------|

| Supply Voltage              | V <sup>+</sup>     | -0.3 to 20                              | V     |

| Input Voltage               | Vs                 | -0.3 to V <sup>+</sup> +0.3 (<20)       | V     |

| Clock Input Voltage         | V <sub>CK</sub>    | -0.3 to 20                              | V     |

| $C_T$ Pin Voltage           | V <sub>CT</sub>    | -0.3 to V <sup>+</sup> +0.3 (<20)       | V     |

| RESET Output Voltage        | VRESET             | -0.3 to V <sup>+</sup> +0.3 (<20)       | V     |

| RESET Output Voltage        | V <sub>RESET</sub> | -0.3 to V <sup>+</sup> +0.3 (<20)       | V     |

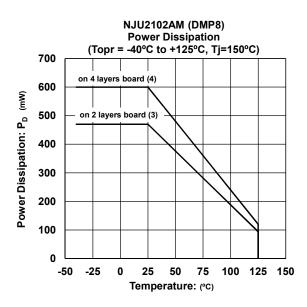

| Power Dissipation (Ta=25°C) | п                  | (2-layer / 4-layer)                     | mW    |

| DMP8                        | P <sub>D</sub>     | 470 <sup>(1)</sup> / 600 <sup>(2)</sup> | TTIVV |

| Junction Temperature        | Tj                 | -40 to +150                             | °C    |

| Operating Temperature       | T <sub>opr</sub>   | -40 to +125                             | °C    |

| Storage Temperature         | T <sub>stg</sub>   | -50 to +150                             | °C    |

(1): Mounted on glass epoxy board.(76.2 x 114.3 x 1.6 :based on EIA/JEDEC standard, 2 Layers)

(2): Mounted on glass epoxy board.(76.2 x 114.3 x 1.6 :based on EIA/JEDEC standard, 4 Layers) internal Cu area: 74.2 x 74.2mm

### ■RECOMMENDED OPERATING CONDITIONS

| NIT |

|-----|

| V   |

| V   |

| V   |

| nA  |

| nA  |

| JA  |

| ns  |

| ns  |

| ns  |

| μF  |

| ייי |

*New Japan Radio Co., Ltd.* www.njr.com

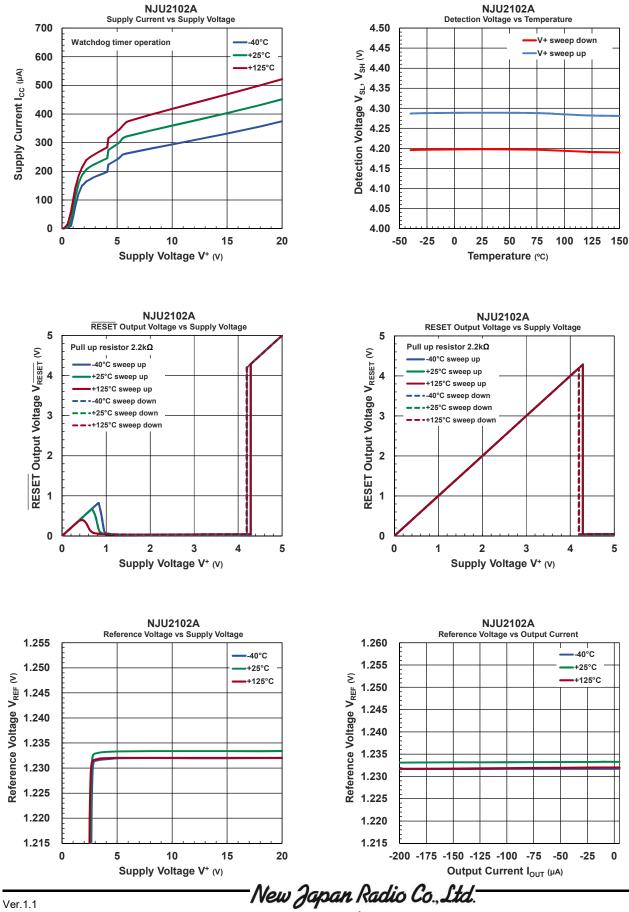

## ■ELECTRICAL CHARACTERISTICS

| (DC Characteristics)                 |                   | Unless                                             | other noted, \ | /⁺=5.0V, C <sup>.</sup> | <sub>Γ</sub> =0.1μF, Τ <sub>ε</sub> | ₃=25°C |

|--------------------------------------|-------------------|----------------------------------------------------|----------------|-------------------------|-------------------------------------|--------|

| PARAMETER                            | SYMBOL            | TEST CONDITION                                     | MIN.           | TYP.                    | MAX.                                | UNIT   |

| Supply Current                       | I <sub>CC</sub>   | Watchdog timer operation                           | -              | 320                     | 430                                 | μA     |

| Detection Voltage 1                  | V <sub>SL</sub>   | V⁺ sweep down                                      | 4.158          | 4.200                   | 4.242                               | V      |

| Detection Voltage 2                  | V <sub>SH</sub>   | V⁺ sweep up                                        | 4.210          | 4.300                   | 4.390                               | V      |

| Hysteresis Width                     | V <sub>HYS</sub>  | V <sub>HYS</sub> =V <sub>SH-</sub> V <sub>SL</sub> | 50             | 100                     | 150                                 | mV     |

| Reference Voltage                    | V <sub>REF</sub>  |                                                    | 1.217          | 1.235                   | 1.253                               | V      |

| Reference Voltage<br>Line Regulation | $\Delta V_{REF1}$ | V <sup>+</sup> =3.5V to 18V                        | -10            | 3                       | 10                                  | mV     |

| Reference Voltage<br>Load Regulation | $\Delta V_{REF2}$ | I <sub>OUT</sub> =-200μA to +5μA                   | -5             | -                       | 5                                   | mV     |

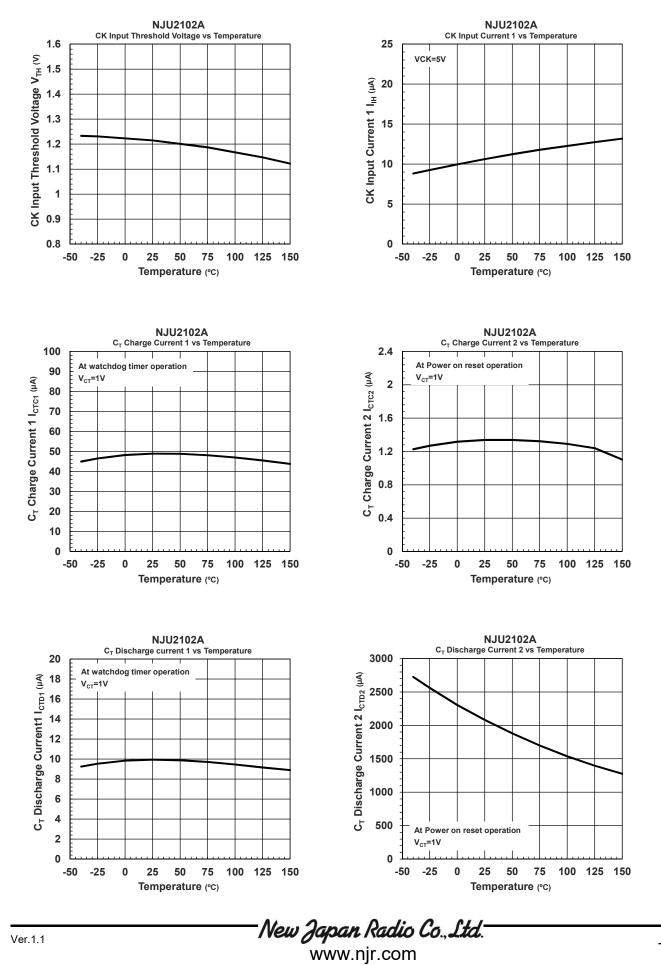

| CK Input Threshold Voltage           | V <sub>TH</sub>   |                                                    | 0.7            | 1.2                     | 1.9                                 | V      |

| CK Input Current 1                   | IIH               | V <sub>CK</sub> =5V                                | -              | 10                      | 20                                  | μA     |

| CK Input Current 2                   | ١ <sub>L</sub>    | V <sub>CK</sub> =0V                                | -0.1           | 0                       | 0.1                                 | μA     |

| $C_T$ Charge Current 1               | I <sub>CTC1</sub> | Watchdog timer operation, $V_{CT}$ =1V             | 20             | 50                      | 110                                 | μA     |

| $C_T$ Charge Current 2               | I <sub>CTC2</sub> | Power on reset operating, $V_{CT}$ =1V             | 0.6            | 1.4                     | 3.0                                 | μA     |

| $C_T$ Discharge Current 1            | I <sub>CTD1</sub> | Watchdog timer operation, $V_{CT}$ =1V             | 6              | 10                      | 13                                  | μA     |

| $C_T$ Discharge Current 2            | I <sub>CTD2</sub> | Power on reset operating, $V_{CT}$ =1V             | 100            | 2000                    | -                                   | μA     |

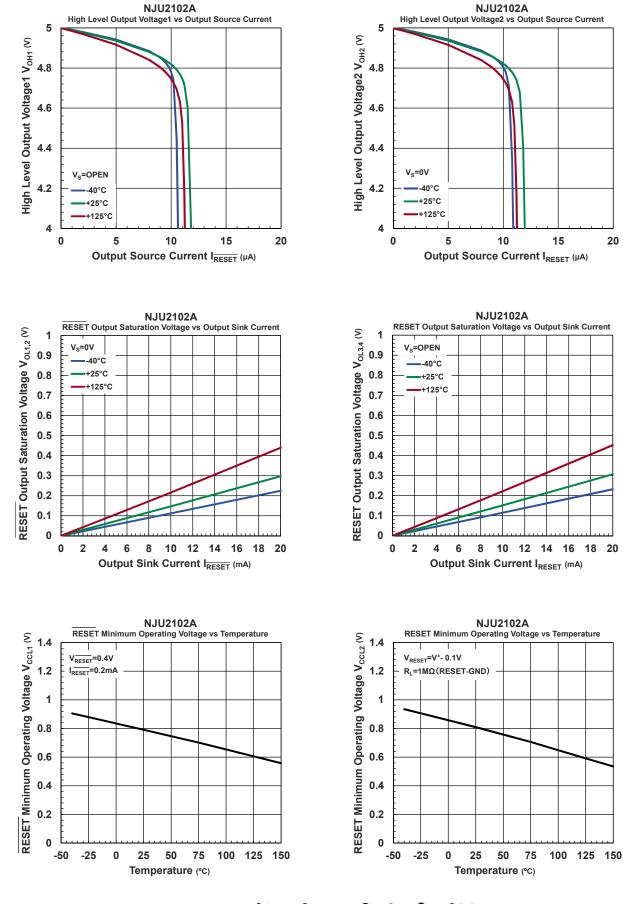

| High Level Output Voltage 1          | V <sub>OH1</sub>  | V <sub>S</sub> =OPEN, I <sub>RESET</sub> =-5µA     | 4.5            | 4.9                     | -                                   | V      |

| High Level Output Voltage 2          | V <sub>OH2</sub>  | V <sub>S</sub> =0V, I <sub>RESET</sub> =-5µA       | 4.5            | 4.9                     | -                                   | V      |

| Output Saturation Voltage 1          | V <sub>OL1</sub>  | V <sub>S</sub> =0V, I <sub>RESET</sub> =3mA        | -              | 0.05                    | 0.4                                 | V      |

| Output Saturation Voltage 2          | V <sub>OL2</sub>  | V <sub>S</sub> =0V, I <sub>RESET</sub> =10mA       | -              | 0.15                    | 0.5                                 | V      |

| Output Saturation Voltage 3          | V <sub>OL3</sub>  | V <sub>S</sub> =OPEN, I <sub>RESET</sub> =3mA      | -              | 0.05                    | 0.4                                 | V      |

| Output Saturation Voltage 4          | V <sub>OL4</sub>  | V <sub>S</sub> =OPEN, I <sub>RESET</sub> =10mA     | -              | 0.15                    | 0.5                                 | V      |

| Output Sink Current 1                | I <sub>OL1</sub>  | $V_{S}=0V, V_{RESET}=1V$                           | 20             | 60                      | -                                   | mA     |

| Output Sink Current 2                | I <sub>OL2</sub>  | V <sub>S</sub> =OPEN, V <sub>RESET</sub> =1V       | 20             | 60                      | -                                   | mA     |

| RESET Minimum<br>Operating Voltage   | V <sub>CCL1</sub> | VRESET=0.4V, IRESET=0.2mA                          | -              | 0.8                     | 1.2                                 | V      |

| RESET Minimum<br>Operating Voltage   | V <sub>CCL2</sub> | $V_{RESET}=V^+-0.1V, R_L=1M_{\Omega}(RESET-GND)$   | -              | 0.8                     | 1.2                                 | V      |

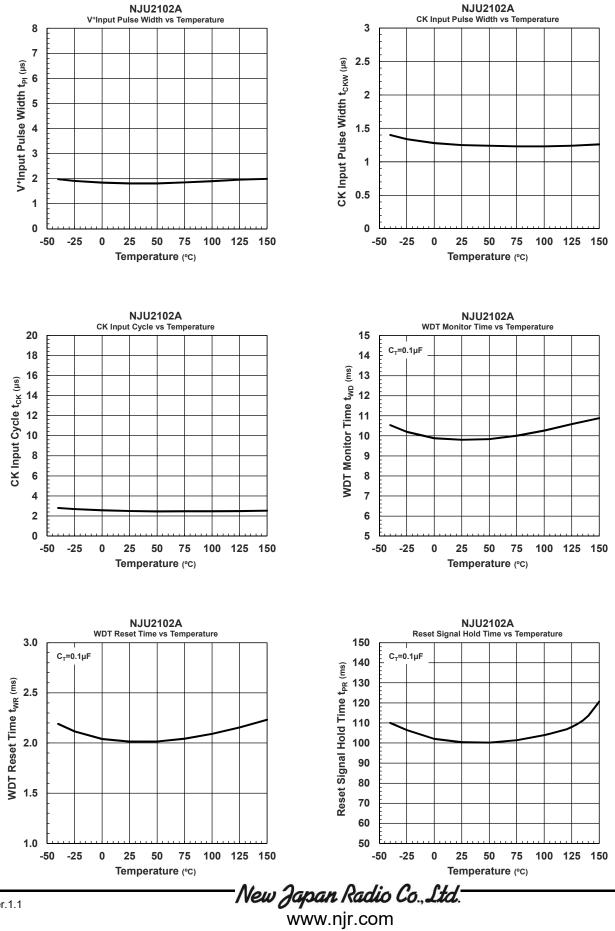

Unless other noted,  $V^+=5.0V$ ,  $C_T=0.1\mu$ F,  $T_a=25^{\circ}C$ (AC Characteristics) PARAMETER SYMBOL **TEST CONDITION** MIN. TYP. MAX. UNIT V<sup>+</sup> Input Pulse width 8 t<sub>Pl</sub> \_ \_ μs CK Input Pulse width 3 t<sub>CKW</sub> -μs 20 CK Input Cycle μs t<sub>CK</sub> -\_ Watchdog Timer Monitor Time 5 10 15 C<sub>T</sub>=0.1µF t<sub>WD</sub> ms Watchdog Timer Reset Time 3 t<sub>WR</sub> C<sub>T</sub>=0.1µF 1 2 ms **Reset Signal Hold Time** t<sub>PR</sub> C⊤=0.1µF 50 100 150 ms RESET pin,  $R_L=2.2k\Omega$ ,  $C_L=100pF$ 2 10 **Output Propagation** t<sub>PD1</sub> μs Delay Time from V<sup>+</sup> RESET pin, R<sub>L</sub>= $2.2k\Omega$ , C<sub>L</sub>=100pF 10 3 t<sub>PD2</sub> μs RESET pin, 10% to 90%, R<sub>L</sub>=2.2kΩ, C<sub>L</sub>=100pF 1.0 1.5 t<sub>R1</sub> \_ μs Output Rise Time RESET pin, 10% to 90%,  $R_L$ =2.2k $\Omega$ ,  $C_L$ =100pF 1.0 1.5 t<sub>R2</sub> μs RESET pin, 90% to 10%, RL=2.2kΩ, CL=100pF -0.1 0.5  $\mathbf{t}_{\text{F1}}$ μs **Output Fall Time** RESET pin, 90% to 10%, RL=2.2kΩ, CL=100pF 0.5 -0.1 t<sub>F2</sub> μs

New Japan Radio Co.,Ltd.

### www.njr.com

### ■THERMAL CHARACTERISTICS

| PARAMETER                                             | SYMBOL | VAL  | UE                                       | UNIT |

|-------------------------------------------------------|--------|------|------------------------------------------|------|

| Junction-to-ambient<br>thermal resistance             | θja    | DMP8 | 262 <sup>(3)</sup><br>206 <sup>(4)</sup> | °C/W |

| Junction-to-Top of package characterization parameter | ψjt    | DMP8 | 72 <sup>(3)</sup><br>65 <sup>(4)</sup>   | °C/W |

(3): Mounted on glass epoxy board.(76.2 x 114.3 x 1.6 :based on EIA/JEDEC standard, 2 Layers)

(4): Mounted on glass epoxy board.(76.2 x 114.3 x 1.6 :based on EIA/JEDEC standard, 4 Layers) internal Cu area: 74.2 x 74.2mm

### ■POWER DISSIPATION vs. AMBIENT TEMPERATURE

New Japan Radio Co., Ltd. www.njr.com

### **TYPICAL CHARACTERISTICS**

www.njr.com

New Japan Radio Co., Ltd. www.njr.com

### **■FUNCTION EXPLAMATION**

## **Technical Information**

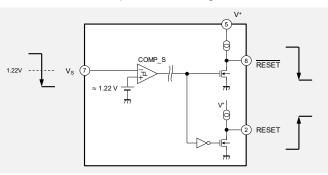

The COMP\_S is the comparator with hysteresis in detection voltage. When Vspin voltage becomes about 1.22V or less, the RESET output becomes " Low " and RESET output becomes "High".

The NJU2102A can detect the instantaneous interruption and the instantaneous drop of the power line with a time of about 2 µs width. If this level of instantaneous interruption or drop is not a problem, it can have a delayed trigger function by connecting capacitor between the  $V_{S}$  pin and GND (refer to Fig.2).

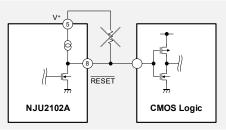

Since the RESET pin and RESET pin are internally pulled up to V<sup> $\dagger$ </sup>, an external pull-up resistor isn't required in case of high impedance load like a CMOS logic IC.

The watchdog timer monitors the clock input to CK pin. And CK pin detects falling edge of clock. While the supply voltage is below the detection voltage, the watchdog timer operation is disabled.

The V<sub>REF</sub> pin outputs reference voltage of 1.235V typ. And it is possible to monitor the multiple supply voltage or over voltage by adding an external comparator.

Unused Pin should be treated as shown in the table below.

| Pin. No. | Pin Name         | Treatment method of unused Pin |

|----------|------------------|--------------------------------|

| 2        | RESET            | OPEN                           |

| 3        | CK               | Connect to GND                 |

| 6        | V <sub>REF</sub> | OPEN                           |

| 7        | Vs               | OPEN                           |

| 8        | RESET            | OPEN                           |

New Japan Radio Co., Ltd. www.njr.com

New Japan Radio Co., Ltd. www.njr.com

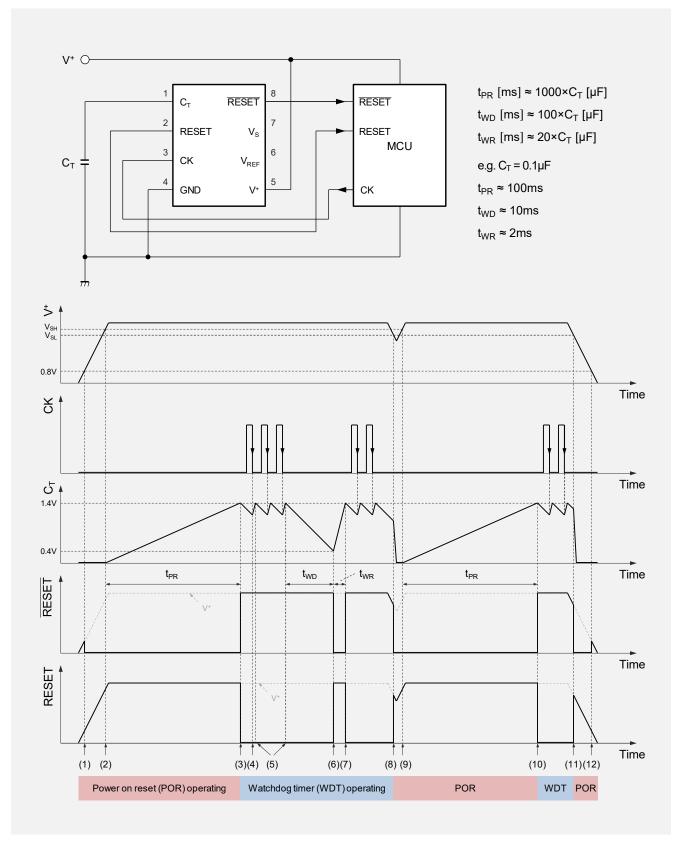

### (Power-ON Reset Operation)

- When V<sup>+</sup> increases to Minimum operating Voltage V<sub>CCL</sub> (0.8V typ.), each output becomes reset state (RESET="Low", (1) RESET="High").

- (2) When  $V^{\dagger}$  increases to  $V_{SH}$  (4.3V typ.), it starts to charge to capacitor  $C_T$ . At this time, each output holds the reset state (RESET="Low", RESET="High").

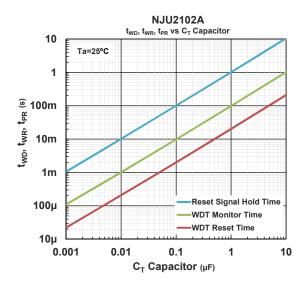

- When the  $C_T$  voltage reaches the threshold voltage (about 1.4V), each output releases the reset state (3) (RESET="High", RESET="Low"). The Reset Signal Hold Time  $t_{PR}$  is the time from when V<sup>+</sup> reaches to V<sub>SH</sub> to the output reset is released. And it is calculated as follows.

Reset Signal Hold Time  $t_{PR}$  [ms]  $\approx 1000 \times C_T$  [µF]

After the reset release, it starts to discharge the capacitor  $C_T$  and the watchdog timer operation is started. Also, it is not affected by CK input during power-on reset operation.

### (Watchdog Timer Operation)

- (4) If a clock from MCU is input to the CK pin during discharging of capacitor  $C_T$ ,  $C_T$  is switched from discharging to charging. And CK pin detects falling edge.

- (5) When the  $C_T$  voltage reaches the threshold voltage (about 1.4V),  $C_T$  is switched from charging to discharging. Repeat the steps (4) and (5) as long as a normal clock is input.

- When the clock stops and  $C_T$  voltage decrease to the threshold voltage (about 0.4V), each output goes into reset (6) state (RESET="Low", RESET="High"). At the same time,  $C_T$  is switched from discharging to charging. The Watchdog Timer Monitor Time  $t_{WD}$  is the  $C_T$  discharge time when  $C_T$  is switched from charging to discharging until reset is output. And it is calculated as follows.

Watchdog Timer Monitor Time  $t_{WD}$  [ms]  $\approx 100 \times C_T$  [µF]

(7) When the  $C_T$  voltage reaches the threshold voltage (about 1.4V), the reset output is released and CT is switched from charging to discharging (RESET="High", RESET="Low"). The Watchdog Timer Reset Time t<sub>WR</sub> is the C<sub>T</sub> charge time when  $C_T$  switches from charging to discharging after reset signal output and it is calculated as follows.

Watchdog Timer Reset Time  $t_{WR}$  [ms]  $\approx 20 \times C_T$  [µF]

After that, repeat the steps (4) and (5) as long as the normal clock is input, but when the clock stops, repeat (6) and (7).

### (Power-ON Reset Operation)

- (8) When V<sup>+</sup> decrease below the V<sub>SL</sub> (4.2V typ.), each output goes into reset state (RESET="Low", RESET="High"). At the same time, C<sub>T</sub> is discharged rapidly.

- When V<sup>+</sup> increase to V<sub>SH</sub>, C<sub>T</sub> is started to charge. In case of instantaneous V<sup>+</sup> drop, if the time from the decreasing of (9)  $V^*$  below V<sub>SL</sub> to the increasing above V<sub>SH</sub> is longer than  $V^*$  Input Pulse Width t<sub>Pl</sub>, C<sub>T</sub> charging will start after discharging CT.

- (10) The reset output is released after  $t_{PR}$  from the time when V<sup>+</sup> becomes higher than V<sub>SH</sub> (RESET = "High", RESET="Low"), and the watchdog timer operation is started. After that, when V<sup>+</sup> becomes V<sub>SL</sub> or less, repeat the steps (8) to (10).

- (11) In the case of power off, when V<sup>+</sup> decrease to V<sub>SL</sub>, the output becomes reset state ( $\overline{RESET}$ ="Low", RESET="High").

- (12) Then, when V<sup>+</sup> decrease to 0V, hold the output reset state (RESET="Low", RESET="High") until V<sup>+</sup> reaches Minimum operating Voltage V<sub>CCL</sub> (0.8V typ.).

New Japan Radio Co., Ltd. www.njr.com

### ■APPLICATION EXAMPLE

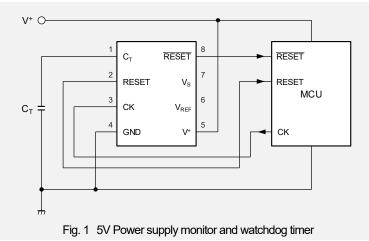

### 1. 5V Power supply monitor and watchdog timer

Monitor the 5V power supply with V<sub>S</sub>(COMP\_S). Detection voltage is Detection Voltage 1 (4.2V typ.) and Detection Voltage 2 (4.3V typ.) according to ELECTRICAL CHARACTERISTICS. Also, monitor the clock from a MCU by watchdog timer.

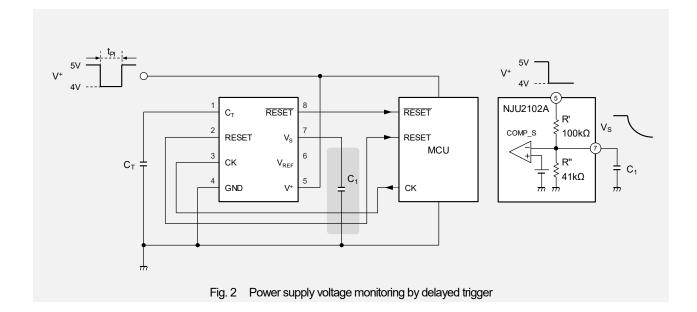

#### Power supply voltage monitoring by delayed trigger 2.

Add an arbitrary delay to the COMP S operation by connecting capacitor  $C_1$  between  $V_S$  pin and GND When C<sub>1</sub> is connected, V<sup>+</sup> Input Pulse width t<sub>Pl</sub> becomes longer. e.g. t<sub>Pl</sub> = 40 $\mu$ s (C1=1000pF)

V<sup>+</sup> Input Pulse width t<sub>Pl</sub> in case of C<sub>1</sub> connected is calculated as following formula.

V<sup>+</sup> Input Pulse width

$$t_{PI} [\mu s] \approx (R' \parallel R'') \times \ln\left(\frac{5-4}{V_{SAL}-4}\right) \times 10^{-6} \times C_1 [pF] \approx 4.7 \times 10^{-2} \times C_1 [pF]$$

New Japan Radio Co., Ltd. www.njr.com

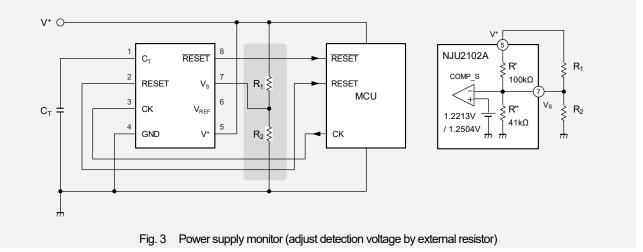

#### Power supply monitor (adjust detection voltage by external resistor) 3.

The detection voltage of  $V^{\dagger}$  can be adjusted with an external resistor.

By selecting the external voltage-dividing resistors R1 and R2 to a sufficiently smaller value than internal voltagedividing resistors R ', R "(100 kΩ, 41 kΩ), the detection voltage can be set by the resistance ratio of R1 and R2 (refer to Tab.1).

The detection voltage should be set higher than the recommended minimum supply voltage (3.5V). Also, the method of adjusting the detection voltage using only either R<sub>1</sub> or R<sub>2</sub> is not recommended because of bad accuracy.

Detection voltage calculate formula ( $R_1 \ll 100 k\Omega$ ,  $R_2 \ll 41 k\Omega$ )

| Detection Voltage(falling) = $\frac{(R_1 \parallel R') + (R_2 \parallel R'')}{R_2 \parallel R''} \times \frac{R''}{R' + R''} \times V_{SL} \approx \frac{R_1 + R_2}{R_2} \times 1.2213$ [V] |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Detection Voltage(rising) = $\frac{(R_1 \parallel R') + (R_2 \parallel R'')}{R_2 \parallel R''} \times \frac{R''}{R' + R''} \times V_{SH} \approx \frac{R_1 + R_2}{R_2} \times 1.2504$ [V]  |  |

### Tab. 1 Setting example

| External resistor R <sub>1</sub><br>[kΩ] | External resistor $R_2$ [k $\Omega$ ] | Detection Voltage(falling)<br>[V] | Detection Voltage(rising)<br>[V] |

|------------------------------------------|---------------------------------------|-----------------------------------|----------------------------------|

| 10                                       | 3.9                                   | 4.34                              | 4.44                             |

| 9.1                                      | 3.9                                   | 4.08                              | 4.18                             |

New Japan Radio Co., Ltd. www.njr.com

#### **Manual Reset function** 4.

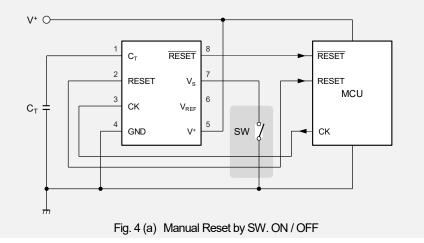

### Manual Reset by SW. ON / OFF (a)

By setting V<sub>S</sub> pin to GND with SW\_ON, it is possible to output reset signal (RESET="Low", RESET="High") arbitrarily regardless of the state of  $V^+$ .

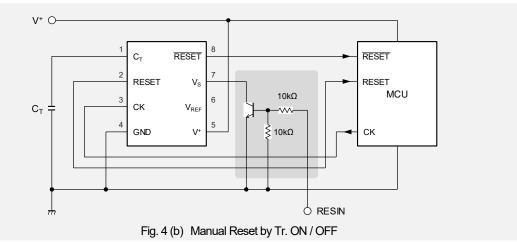

### (b) Manual Reset by Tr. ON / OFF

By turning on Tr. with the RESIN signal, it is possible to output reset signal (RESET="Low", RESET="High") arbitrarily regardless of the state of  $V^+$ .

New Japan Radio Co., Ltd. www.njr.com

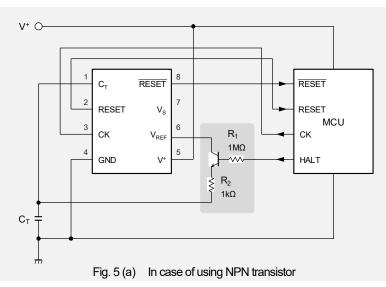

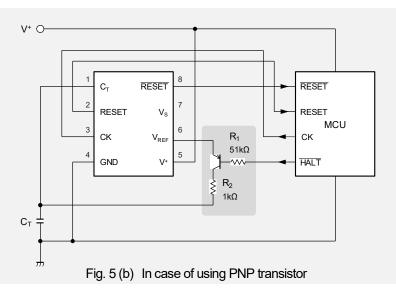

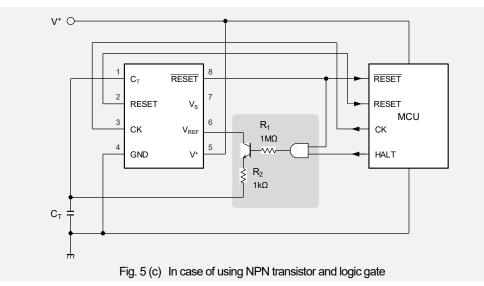

### 5. Disable watchdog timer operation

Disable watchdog timer operation when HALT="High", HALT="Low". When the MCU is in standby mode, even if the clock from the MCU is interrupted, it is possible to monitor the power supply without resetting by the watchdog timer.

### (Notes)

In Fig.5 (a) and (b), it should be set HALT="Low",  $\overline{HALT}$ ="High" during C<sub>T</sub> charging at power-on reset operation. In this circuit, the watchdog timer operation is disabled by fixing C<sub>T</sub> pin voltage with V<sub>REF</sub>.

If it set HALT="High",  $\overline{HALT}$ ="Low" during C<sub>T</sub> charging at power-on reset operation, C<sub>T</sub> is not charged till the reset release voltage.

On the other hand, in Fig.5 (c) and (d), it can be used without considering the logic of HALT and  $\overline{HALT}$  at power on reset operation by applying a logic gate.

### (a) In case of using NPN transistor

Disable the watchdog timer operation with HALT="High". Should be set HALT="Low" during power-on reset operation.

### (b) In case of using PNP transistor

Disable the watchdog timer operation with HALT="Low". Should be set HALT="High" during power-on reset operation.

(c) In case of using NPN transistor and logic gate Disable the watchdog timer operation with HALT="High".

(d) In case of using PNP transistor and logic gate

Disable the watchdog timer operation with HALT="Low".

New Japan Radio Co., Ltd. www.njr.com

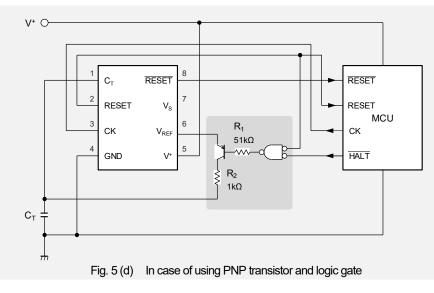

#### Shortening of Reset Signal Hold Time t<sub>PR</sub> 6.

By inserting a diode between C<sub>T</sub> and RESET pin and increasing C<sub>T</sub> charge current, Reset Signal Hold Time t<sub>PR</sub> can be shortened. The available output is only RESET. Estimated value of Reset Signal Hold Time term is calculated as following formula.

Comparison of shortened circuit and standard circuit at  $C_T = 0.1 \ \mu\text{F}$  is shown in Tab. 2.

## **Reset Signal Hold Time (shortened circuit)** $t_{PR}$ [ms] $\approx 100 \times C_T$ [µF] $t_{WD}$ [ms] $\approx 100 \times C_T$ [µF] $t_{WR}$ [ms] $\approx 16 \times C_T$ [µF]

Reset Signal Hold Time (standard circuit)  $t_{PR}$  [ms]  $\approx 1000 \times C_T$  [µF]  $t_{WD}$  [ms]  $\approx 100 \times C_T$  [µF]  $t_{WR}$  [ms]  $\approx 20 \times C_T$  [µF]

| Tab. 2 | Comparison of shortened circuit and standard circuit ( $C_T=0.1\mu F$ ) |  |

|--------|-------------------------------------------------------------------------|--|

|        |                                                                         |  |

| ltem              | Reset Signal Hold Time shortened circuit | Standard circuit |

|-------------------|------------------------------------------|------------------|

| t <sub>PR</sub> ≈ | 10 ms                                    | 100 ms           |

| t <sub>WD</sub> ≈ | 10 ms                                    | 10 ms            |

| t <sub>WR</sub> ≈ | 1.6 ms                                   | 2.0 ms           |

New Japan Radio Co., Ltd. www.njr.com

### 7. Upper limit of Clock input frequency

## **Technical Information**

Set the clock input frequency upper limit  $f_H$  from MCU by external filters made of  $C_2$  and  $R_2$ . When the clock frequency from the MCU exceeds  $f_H$ , reset signal is output. On the other hand, the lower limit is set by  $C_T$ .

When the MCU outputs a clock like the Fig. 7, if the clock cycle  $t_2$  is shorter, the clock interval  $t_1$  also becomes shorter. If the clock input to NJU2102A (C<sub>2</sub> voltage) does not reach the CK Input Threshold Voltage V<sub>TH</sub> (1.2V typ.), a reset signal output.

The  $t_1$  value can be calculated as following formula. However,  $t_3$  must be 3.0µs or more according to the minimum value of the CK Input Pulse width  $t_{CKW}$  and  $t_2$  must be 20µs or more according to the minimum value of the CK Input Cycle  $t_{CK}$ .

A setting example of C2, R2 is shown in Tab.3.

Fig. 7 Upper limit of Clock input frequency

|                | 0 1            |                |

|----------------|----------------|----------------|

| C <sub>2</sub> | R <sub>2</sub> | t <sub>1</sub> |

| 0.01 µF        | 10 kΩ          | 30 µs          |

| 0.1 µF         | 10 kΩ          | 300 µs         |

Tab. 3 Setting example of  $C_2$ ,  $R_2$

New Japan Radio Co., Ltd.

## NJU2102A

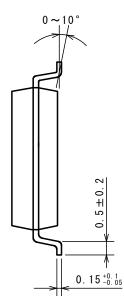

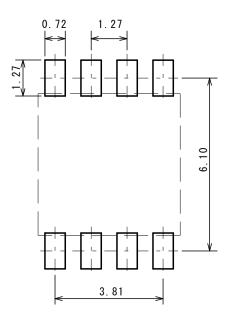

DMP8

Unit: mm

### ■PACKAGE DIMENSIONS

### ■EXAMPLE OF SOLDER PADS DIMENSIONS

-*New Japan Radio Co., Ltd.*-www.njr.com

# NJU2102A

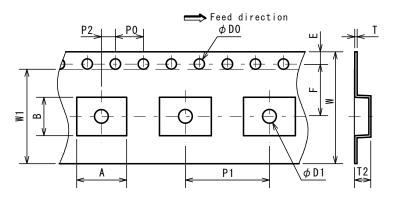

DMP8

Unit: mm

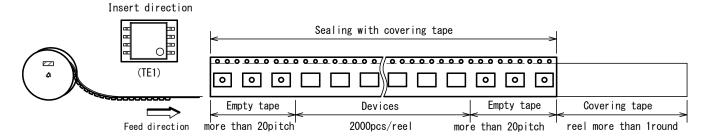

### ■PACKING SPEC

### TAPING DIMENSIONS

| SYMBOL | DIMENSION | REMARKS          |

|--------|-----------|------------------|

| A      | 7.1       | BOTTOM DIMENSION |

| В      | 5.4       | BOTTOM DIMENSION |

| DO     | 1.55±0.05 |                  |

| D1     | 2.05±0.1  |                  |

| E      | 1.75±0.1  |                  |

| F      | 7.5±0.1   |                  |

| P0     | 4.0±0.1   |                  |

| P1     | 12.0±0.1  |                  |

| P2     | 2.0±0.1   |                  |

| T      | 0.3±0.05  |                  |

| T2     | 2. 3      |                  |

| W      | 16.0±0.3  |                  |

| W1     | 13 5      | THICKNESS 0.1max |

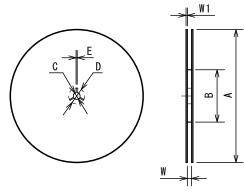

**REEL DIMENSIONS**

| SYMBOL | DIMENSION    |

|--------|--------------|

| Α      | $\phi$ 330±2 |

| В      | φ 80±1       |

| C      | φ 13±0.2     |

| D      | φ 21±0.8     |

| E      | 2±0.5        |

| W      | 17.5±0.5     |

| W1     | 2±0.2        |

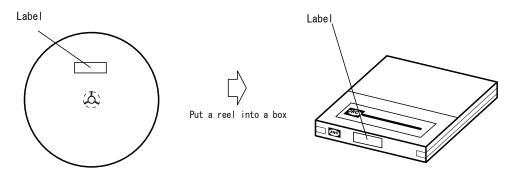

### **TAPING STATE**

PACKING STATE

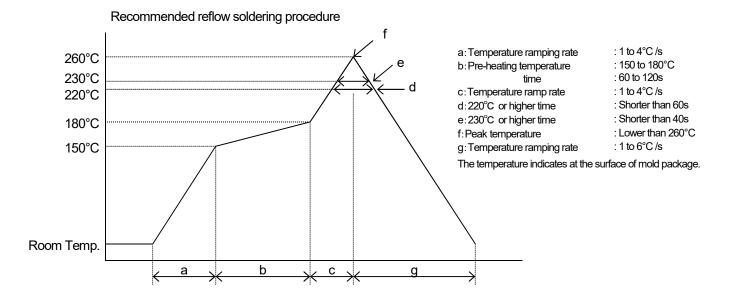

### ■RECOMMENDED MOUNTING METHOD

### INFRARED REFLOW SOLDERING METHOD

-*New Japan Radio Co., Ltd.*-www.njr.com

### **REVISION HISTORY**

| Date        | Revision | Changes                                                                                              |

|-------------|----------|------------------------------------------------------------------------------------------------------|

| 18.Sep.2018 | 1.0      | New Release                                                                                          |

| 08.Nov.2018 | 1.1      | Add the Technical Information.<br>(FUNCTION EXPLAMATION, OPERATION EXPLAMATION, APPLICATION EXAMPLE) |

|             |          |                                                                                                      |

-*New Japan Radio Co., Ltd.*--www.njr.com

### [CAUTION]

- New JRC strives to produce reliable and high quality semiconductors. New JRC's semiconductors are intended for specific 1. applications and require proper maintenance and handling. To enhance the performance and service of New JRC's semiconductors, the devices, machinery or equipment into which they are integrated should undergo preventative maintenance and inspection at regularly scheduled intervals. Failure to properly maintain equipment and machinery incorporating these products can result in catastrophic system failures

- 2. The specifications on this datasheet are only given for information without any guarantee as regards either mistakes or omissions. The application circuits in this datasheet are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights. All other trademarks mentioned herein are property of their respective companies.

- 3. To ensure the highest levels of reliability, New JRC products must always be properly handled. The introduction of external contaminants (e.g. dust, oil or cosmetics) can result in failures of semiconductor products.

- New JRC offers a variety of semiconductor products intended for particular applications. It is important that you select the 4. proper component for your intended application. You may contact New JRC's Sale's Office if you are uncertain about the products listed in this catalog.

- 5. Special care is required in designing devices, machinery or equipment which demand high levels of reliability. This is particularly important when designing critical components or systems whose failure can foreseeably result in situations that could adversely affect health or safety. In designing such critical devices, equipment or machinery, careful consideration should be given to amongst other things, their safety design, fail-safe design, back-up and redundancy systems, and diffusion design.

- 6. The products listed in the catalog may not be appropriate for use in certain equipment where reliability is critical or where the products may be subjected to extreme conditions. You should consult our sales office before using the products in any of the following types of equipment.

Aerospace Equipment Equipment Used in the Deep sea Power Generator Control Equipment (Nuclear, Steam, Hydraulic) Life Maintenance Medical Equipment Fire Alarm/Intruder Detector Vehicle Control Equipment (airplane, railroad, ship, etc.) Various Safety devices

- 7. New JRC's products have been designed and tested to function within controlled environmental conditions. Do not use products under conditions that deviate from methods or applications specified in this catalog. Failure to employ New JRC products in the proper applications can lead to deterioration, destruction or failure of the products. New JRC shall not be responsible for any bodily injury, fires or accident, property damage or any consequential damages resulting from misuse or misapplication of its products. Products are sold without warranty of any kind, either express or implied, including but not limited to any implied warranty of merchantability or fitness for a particular purpose.

- Warning for handling Gallium and Arsenic(GaAs) Products (Applying to GaAs MMIC, Photo Reflector). This Products uses 8. Gallium(Ga) and Arsenic(As) which are specified as poisonous chemicals by law. For the prevention of a hazard, do not burn, destroy, or process chemically to make them as gas or power. When the product is disposed, please follow the related regulation and do not mix this with general industrial waste or household waste.

- The product specifications and descriptions listed in this catalog are subject to change at any time, without notice. 9

-*New Japan Radio Co., Ltd.*-www.njr.com