# STMLS05

### Enhanced five-channel PMOS load switches

Datasheet - production data

#### **Features**

- Five-channel PMOS switches

- Input/output voltage range: 1.05 V 5.5 V

- V<sub>DD</sub> voltage range: 1.8 V 3.6 V

- Maximum output rated current: 100 mA

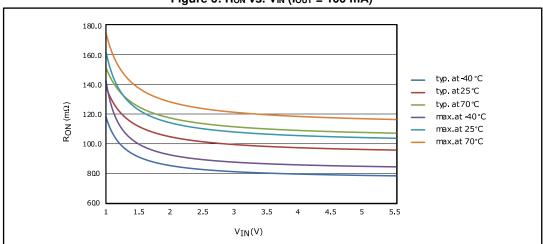

- Low R<sub>ON</sub>: 120 mΩ typ. at 1.8 V

- Built-in soft-start feature for each channel programmable by I<sup>2</sup>C (1, 2, 4, and 8 ms)

- Enable/disable function of each load switch programmed by I<sup>2</sup>C

- Enable pin for I<sup>2</sup>C block

- Ultra low quiescent current: 2.4 μA max.

- Output discharge circuitry

- ESD tolerance: 2 kV HBM

- Temperature range: -40 up to 70 °C

- Package: UFQFPN, 3 x3 mm, 16L

- Lead-free and Halogen-free device

- V<sub>DD</sub> UVLO circuit for enhanced application robustness

### **Applications**

- Smart phones

- Tablets

- Mobile device accessories

- Wearable devices

### **Description**

The STMLS05 device is an array of five load switches, all featuring a soft-start turn-on to protect from high inrush current. The soft-start timing can be programmed by the I<sup>2</sup>C. Each channel may be turned ON/OFF by the I<sup>2</sup>C block. The I<sup>2</sup>C block may be disabled through the EN I2C pin.

In addition, channel 0 can be programmed ON or OFF by the EN\_SW0 pin. The device is available in a UFQFPN package (3x3 mm) and its temperature range is -40 to 70 °C.

Table 1: Device summary

| Order code   | l <sup>2</sup> C base<br>address | Package<br>marking |

|--------------|----------------------------------|--------------------|

| STMLS05ACQTR | 0x5C                             | AS5C               |

Contents STMLS05

## **Contents**

| 1 | <b>Functio</b>        | nal block diagram                                    | 3  |

|---|-----------------------|------------------------------------------------------|----|

| 2 |                       | tings                                                |    |

|   | 2.1                   | Pin connections                                      |    |

|   | 2.2                   | Pin description                                      | 4  |

| 3 | Maximu                | ım ratings                                           | 5  |

|   | 3.1                   | Absolute maximum ratings                             | 5  |

|   | 3.2                   | Recommended operating conditions                     | 5  |

| 4 | Electric              | al specifications                                    | 6  |

| 5 | I <sup>2</sup> C regi | ster map                                             | 9  |

| 6 | _                     | operating characteristics                            |    |

| 7 | Applica               | ition information                                    | 11 |

|   | 7.1                   | Power-up sequence and UVLO functionality             | 11 |

|   | 7.2                   | Output discharge circuitry                           | 11 |

|   | 7.3                   | EN_I2C (I <sup>2</sup> C block enable) functionality | 11 |

|   | 7.4                   | I <sup>2</sup> C register auto-incrementation        | 11 |

| 8 | Packag                | e information                                        | 12 |

|   | 8.1                   | UFQFPN, 3x3mm, 16 L package information              | 13 |

| 9 | Revisio               | n history                                            | 15 |

#### Functional block diagram 1

Figure 1: Functional block diagram  $V_{DD}$ 15 13 VIN0 OUT0 12 OUT1 VIN1 Switch Switch 11 OUT2 VIN2 outputs inputs VIN3 10 OUT3 3 4 9 OUT4 VIN4 SCL EN\_SW0 I<sup>2</sup>C block controller soft-start I2C Control 14 EN\_I2C SDA GND

Pin settings STMLS05

# 2 Pin settings

## 2.1 Pin connections

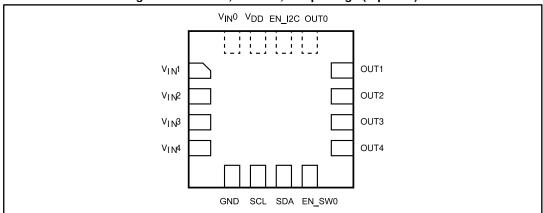

Figure 2: UFQFPN, 3x3 mm, 16L package (top view)

# 2.2 Pin description

Table 2: UFQFPN 3x3 mm, 16L pin description

| Pin number | Name              | Function                              |

|------------|-------------------|---------------------------------------|

| 1          | V <sub>IN</sub> 1 |                                       |

| 2          | V <sub>IN</sub> 2 | Power input                           |

| 3          | V <sub>IN</sub> 3 | Power input                           |

| 4          | V <sub>IN</sub> 4 |                                       |

| 5          | GND               | Ground                                |

| 6          | SCL               | I <sup>2</sup> C serial clock         |

| 7          | SDA               | I <sup>2</sup> C serial data          |

| 8          | EN_SW0            | Enable input - switch 0               |

| 9          | OUT4              |                                       |

| 10         | OUT3              |                                       |

| 11         | OUT2              | Power output                          |

| 12         | OUT1              |                                       |

| 13         | OUT0              |                                       |

| 14         | EN_I2C            | Enable input - I <sup>2</sup> C block |

| 15         | V <sub>DD</sub>   | Supply voltage                        |

| 16         | V <sub>IN</sub> 0 | Power input                           |

STMLS05 Maximum ratings

# 3 Maximum ratings

Stressing the device beyond the rating listed in *Table 3: "Absolute maximum ratings"* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in *Table 4: "Recommended operating conditions"* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 3.1 Absolute maximum ratings

Table 3: Absolute maximum ratings

| Symbol              | Parameter                            | Value                         | Unit |

|---------------------|--------------------------------------|-------------------------------|------|

| V <sub>DD</sub>     | Supply voltage range                 | -0.3 to 6.0                   | V    |

| VIN, VOUT           | I/O voltage                          | -0.3 to 6.0                   | V    |

| Іоит                | Maximum continuous output current    | 500                           | mA   |

| TJ                  | Junction operating temperature       | 150                           |      |

| TA                  | Operating temperature range          | -40 to 70                     | °C   |

| T <sub>STG</sub>    | Storage temperature                  | -55 to 150                    |      |

| ESD                 | ESD protection level (all pins, HBM) | 2                             | kV   |

| V <sub>SDA</sub>    | I/O voltage                          | -0.3 to 6.0                   |      |

| V <sub>SCL</sub>    | I/O voltage                          | -0.3 to 6.0                   | V    |

| V <sub>EN_I2C</sub> | I/O voltage                          | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| V <sub>EN_SW0</sub> | I/O voltage                          | -0.3 to V <sub>DD</sub> + 0.3 |      |

## 3.2 Recommended operating conditions

Table 4: Recommended operating conditions

| 0                | Power at an                                         |                     |      |                     |      |

|------------------|-----------------------------------------------------|---------------------|------|---------------------|------|

| Symbol           | Parameter                                           | Min.                | Тур. | Max.                | Unit |

| $V_{DD}$         | Supply voltage                                      | 1.8                 |      | 3.6                 |      |

| VIN              | Input voltage range                                 | 1.05                |      | 5.5                 | V    |

| Vout             | Output voltage range                                | 0                   |      | VIN                 |      |

| l <sub>OUT</sub> | Continuous output current                           | _                   |      | 100                 | mA   |

| VIL              | Input logic low voltage (EN_I2C, EN_SW0, SDA, SCL)  | _                   |      | 0.3 V <sub>DD</sub> | V    |

| V <sub>IH</sub>  | Input logic high voltage (EN_I2C, EN_SW0, SDA, SCL) | 0.7 V <sub>DD</sub> |      | $V_{DD}$            | V    |

# 4 Electrical specifications

In the table below, typical values are valid for  $T_A = T_J = 25\ ^{\circ}C$ .

**Table 5: Electrical characteristics**

|                               | _                                                                                                 |                                                                                                           | Value |      |      |      |  |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|------|------|--|--|--|

| Symbol                        | Parameter                                                                                         | Test condition                                                                                            | Min.  | Тур. | Max. | Unit |  |  |  |

| 1                             | Quiescent current, switches ON, I <sup>2</sup> C OFF                                              | I <sub>OUT</sub> = 0 mA                                                                                   | _     | 1    | 24   |      |  |  |  |

| I <sub>DD</sub>               | Quiescent current, switches ON, I <sup>2</sup> C ON                                               | I <sub>OUT</sub> = 0 mA, no clock on SCL                                                                  | _     | _    | 2.4  |      |  |  |  |

| I <sub>DD</sub> (OFF)         | OFF-state supply current                                                                          | V <sub>OUT</sub> open                                                                                     | _     | 0.04 | 1    |      |  |  |  |

|                               |                                                                                                   | $V_{IN} = 1.05 \text{ V}, V_{OUT} = 0 \text{ V}, V_{DD} = 1.8 \text{ V to } 3.6 \text{ V}$                | _     | 0.01 | 10   | μΑ   |  |  |  |

| In a sure                     | OFF-state switch leakage current                                                                  | V <sub>IN</sub> = 1.8 V, V <sub>OUT</sub> = 0 V,<br>V <sub>DD</sub> = 1.8 V to 3.6 V                      | _     | 0.04 | 12   |      |  |  |  |

| IINx(LEAKAGE)                 | per switch                                                                                        | V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 0 V,<br>V <sub>DD</sub> = 1.8 V to 3.6 V                      | _     | 0.07 | 20   |      |  |  |  |

|                               |                                                                                                   | V <sub>IN</sub> = 5.5 V, V <sub>OUT</sub> = 0 V,<br>V <sub>DD</sub> = 1.8 V to 3.6 V                      | _     | 0.2  | 25   |      |  |  |  |

| (1)                           | OFF-state switch leakage current                                                                  | $V_{IN} = 3.6 \text{ V}, V_{OUT} \text{ floating},$<br>$V_{DD} = 1.8 \text{ V} \text{ to } 3.6 \text{ V}$ | _     | 2    | 75   | nA   |  |  |  |

| I <sub>INx(LEAKAGE)</sub> (1) | per switch                                                                                        | $V_{IN} = 5.5 \text{ V}, V_{OUT} \text{ floating},$<br>$V_{DD} = 1.8 \text{ V} \text{ to } 3.6 \text{ V}$ | _     | 4    | 200  |      |  |  |  |

| Vuvlo                         | V <sub>DD</sub> UVLO threshold (2)                                                                |                                                                                                           | 0.9   | 1.35 | 1.6  | V    |  |  |  |

|                               |                                                                                                   | V <sub>IN</sub> = 1.05 V, I <sub>OUT</sub> = 100 mA                                                       | _     | 150  | 180  |      |  |  |  |

| Ron                           | ON resistance                                                                                     | V <sub>IN</sub> = 1.8 V, I <sub>OUT</sub> = 100 mA                                                        | _     | 120  | 140  | mΩ   |  |  |  |

| NON                           |                                                                                                   | $V_{IN} = 3.3 \text{ V}, I_{OUT} = 100 \text{ mA}$                                                        | _     | 110  | 130  |      |  |  |  |

|                               |                                                                                                   | V <sub>IN</sub> = 5.5 V, I <sub>OUT</sub> = 100 mA                                                        | _     | 108  | 125  |      |  |  |  |

| t <sub>DIS</sub>              | Output discharge pulse width                                                                      |                                                                                                           | 1.7   | 4.1  | 8.3  | ms   |  |  |  |

| td_on <sup>(3)</sup>          | Delay between discharge switch<br>turn-off and main switch turn-on to<br>prevent cross-conduction | $V_{IN} = V_{DD} = 1.8 \text{ V}, C_L = 47 \mu\text{F},$                                                  | 100   | _    | _    |      |  |  |  |

| td_off (3)                    | Delay between main switch turn-off<br>and discharge switch turn-on to<br>prevent cross-conduction | R <sub>L</sub> disconnected, ST2_x = 0,<br>DEx = 1, DTx = 1                                               | 220   | _    | _    | ns   |  |  |  |

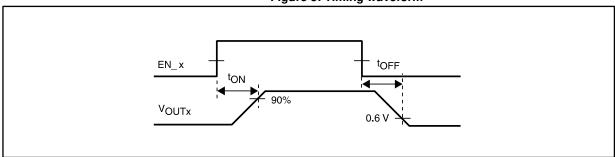

| Switching cha                 | aracteristics V <sub>IN</sub> = 3.6 V, V <sub>DD</sub> = 1.8 V,                                   | R <sub>L</sub> = 100 Ω, C <sub>L</sub> = 47 μF                                                            | •     |      | •    |      |  |  |  |

|                               | Turn-on time: from switch enabled to V <sub>OUT</sub> above 90 % of V <sub>IN</sub>               | No soft-start                                                                                             | _     | 80   | _    | μs   |  |  |  |

| tou                           | Turn-on time: from switch enabled to V <sub>OUT</sub> above 90 % of V <sub>IN</sub>               | Soft-start = 1 ms                                                                                         | 0.5   | 1    | 1.15 |      |  |  |  |

| ton                           | Turn-on time: from switch enabled to V <sub>OUT</sub> above 90 % of V <sub>IN</sub>               | Soft-start = 2 ms                                                                                         | 1.2   | 2    | 2.25 | ms   |  |  |  |

|                               | Turn-on time: from switch enabled to V <sub>OUT</sub> above 90 % of V <sub>IN</sub>               | Soft-start = 4 ms                                                                                         | 2.3   | 4    | 4.3  |      |  |  |  |

|                               |                                                                                                   |                                                                                                           |       |      |      |      |  |  |  |

| Cumbal   | Davamatav                                                                           | Test condition                                                     |      | l lmit |      |      |  |

|----------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|--------|------|------|--|

| Symbol   | Parameter                                                                           | rest condition                                                     | Min. | Тур.   | Max. | Unit |  |

| ton      | Turn-on time: from switch enabled to V <sub>OUT</sub> above 90 % of V <sub>IN</sub> | Soft-start = 8 ms                                                  | 4.35 | 8      | 10   |      |  |

|          |                                                                                     | Discharge enabled (DEx = 1)                                        | _    | 1.1    | 1.4  | mo   |  |

| toff (1) | Turn-off time: from switch disabled                                                 | Discharge disabled (DEx = 0)                                       | _    | 8.4    |      | ms   |  |

|          | to V <sub>OUT</sub> below 0.6 V                                                     | Discharge enabled (DEx = 1), $C_L = 47 \mu F$ , $R_L$ disconnected | _    | 1.3    | 1.7  |      |  |

#### Notes:

Figure 3: Timing waveform

$<sup>\</sup>ensuremath{^{(1)}}\mbox{Based}$  on characterization data. Not tested in production.

$<sup>^{(2)}\</sup>text{Minimum }V_{DD}$  fall time for proper UVLO circuit functionality is 20  $\mu s.$

$<sup>{}^{(3)}\</sup>mbox{Guaranteed}$  by design. Not tested in production.

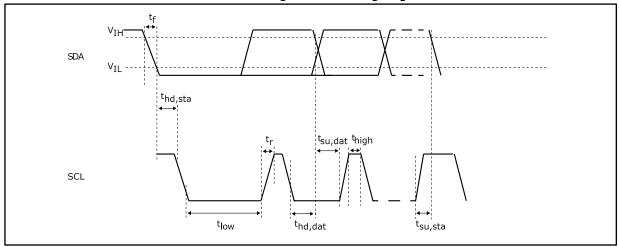

Table 6:  $I^2C$  timing -  $V_{DD}$  = 1.8 V,  $T_A$  = -40 to 70 °C (unless otherwise specified)

| Symbol              | Parameter                                        | Conditions | Min.                    | Тур. | Max. | Unit |

|---------------------|--------------------------------------------------|------------|-------------------------|------|------|------|

| F <sub>scl</sub>    | SCL clock frequency                              |            | 0                       |      | 400  | kHz  |

| thd,sta             | Hold time (repeated) START condition             |            | 0.6                     |      | 1    |      |

| t <sub>low</sub>    | LOW period of the SCL clock                      |            | 1.3                     |      | 1    |      |

| t <sub>high</sub>   | HIGH period of the SCL clock                     |            | 0.6                     |      | 1    | μs   |

| t <sub>su,dat</sub> | Setup time for repeated START condition          |            | 0.6                     |      | 1    |      |

| thd,dat             | Data hold time                                   |            | 0                       |      | 0.9  |      |

| t <sub>su,dat</sub> | Data setup time                                  | _          | 100                     | _    | 1    |      |

| tr                  | Rise time of both SDA and SCL signals            |            | 20 + 0.1 C <sub>b</sub> |      | 300  | ns   |

| tf                  | Fall time of both SDA and SCL signals            |            | 20 + 0.1 C <sub>b</sub> |      | 300  |      |

| t <sub>su,sto</sub> | Setup time for STOP condition                    |            | 0.6                     |      | _    |      |

| tbuf                | Bus free time between a STOP and START condition |            | 1.3                     |      | _    | μs   |

| Сь                  | Capacitive load for each bus line                |            | _                       |      | 400  | pF   |

Figure 4: I<sup>2</sup>C timing diagram

STMLS05 I2C register map

# 5 I<sup>2</sup>C register map

### I<sup>2</sup>C base address

The  $I^2C$  base address for writing to the device is 0x5C (01011100). For reading from device it is 0x5D (01011101).

Table 7: I<sup>2</sup>C register map

| Address | Register purpose | b7 | b6 | b5 | b4   | b3   | b2    | b1    | b0    |

|---------|------------------|----|----|----|------|------|-------|-------|-------|

| 0x00    | Channel 0 setup  | _  | 1  | 1  | DT0  | DE0  | ST2_0 | ST1_0 | ST0_0 |

| 0x01    | Channel 1 setup  | _  | _  | _  | DT1  | DE1  | ST2_1 | ST1_1 | ST0_1 |

| 0x02    | Channel 2 setup  | _  | _  | _  | DT2  | DE2  | ST2_2 | ST1_2 | ST0_2 |

| 0x03    | Channel 3 setup  | _  | 1  | 1  | DT3  | DE3  | ST2_3 | ST1_3 | ST0_3 |

| 0x04    | Channel 4 setup  | _  | _  | _  | DT4  | DE4  | ST2_4 | ST1_4 | ST0_4 |

| 0x05    | Channel enable   | _  | _  | _  | EN_4 | EN_3 | EN_2  | EN_1  | EN_0  |

### Table 8: I<sup>2</sup>C register bit functions

| Bit                                 | Value | Function                                              | Power-up value |  |

|-------------------------------------|-------|-------------------------------------------------------|----------------|--|

| EN x (1)                            | 0     | Channel x disabled (off)                              | 0              |  |

| EN_X W                              | 1     | Channel x enabled (on)                                |                |  |

| DEx (discharge enable on channel x) | 0     | No discharge after channel x disable                  | 1              |  |

| DEX (discharge enable on charmer x) | 1     | Discharge enabled                                     |                |  |

|                                     | 0     | Discharge during tois                                 |                |  |

| DTx (discharge type on channel x)   | 1     | Permanent discharge when channel x is disabled        | 0              |  |

|                                     | 0     | No soft-start time for channel x                      |                |  |

| ST2_x                               | 1     | Soft-start for channel x defined by ST1_x, ST0_x bits | 0              |  |

|                                     | 0, 0  | Soft-start 1 ms                                       |                |  |

| ST1 v ST0 v                         | 0, 1  | Soft-start 2 ms                                       |                |  |

| ST1_x, ST0_x                        | 1, 0  | Soft-start 4 ms                                       | 0              |  |

|                                     | 1, 1  | Soft-start 8 ms                                       |                |  |

#### Notes:

$<sup>^{(1)}</sup>$ The state-of-channel 0 is the OR function between the EN\_0 bit and EN\_SW0 pin

# 6 Typical operating characteristics

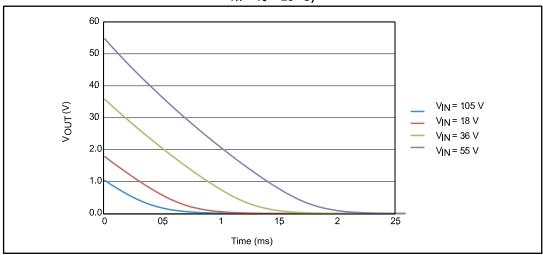

Figure 5: Output discharge circuitry performance (V  $_{DD}$  = 1.8 V, C  $_{L}$  = 47  $\mu F,~R_{L}$  = 100  $\Omega,~T_{A}$  =  $T_{J}$  = 25  $^{\circ}C)$

Figure 6: Ron vs. VIN (lout = 100 mA)

## 7 Application information

### 7.1 Power-up sequence and UVLO functionality

The STMLS05 device is powered from the  $V_{DD}$  pin. Thus, for full device functionality a valid  $V_{DD}$  must be present.

The  $V_{DD}$  UVLO circuit enhances application robustness. If the  $V_{DD}$  is below the UVLO threshold, all main switches and discharge circuits are off and all registers are reset to their power-up values even if the  $V_{IN}$  is applied.

For proper UVLO functionality, the  $V_{DD}$  rise and fall time must be longer than 20 microseconds. In most applications this is ensured automatically otherwise a simple R-C element in the  $V_{DD}$  line (see *Figure 7: "R-C element in VDD line"*) ensures proper functionality. This R-C element also provides an excellent  $V_{DD}$  decoupling.

### 7.2 Output discharge circuitry

Internal output discharge circuits are activated at the moment of the main MOSFET turn-off. They are kept active for a period of 1.7 ms min. t<sub>DIS</sub>, or they are kept active permanently for the whole period when the main switch is turned off, based on the DTx bit.

Output discharge can also be disabled by setting the DEx bit to 0.

It is guaranteed that the main MOSFET and the discharge circuit are never turned on at the same time. The  $t_{D\_ON}$  delay shown in applies and the discharge circuit is disabled if the main MOSFET is enabled during the  $t_{DIS}$  pulse.

## 7.3 EN\_I2C (I<sup>2</sup>C block enable) functionality

The EN\_I2C pin disables I<sup>2</sup>C communication. During the I<sup>2</sup>C block disable period (EN\_I2C = 0) the last state-of-power switches are kept and I<sup>2</sup>C commands are ignored. I<sup>2</sup>C communication is not influenced.

## 7.4 I<sup>2</sup>C register auto-incrementation

The STMLS05 device supports automatic incrementation of the I<sup>2</sup>C register addresses. However, the automatic shift from the highest register address to the lowest address is not supported.

V<sub>DD</sub> supply 1.8 V to 3.6 V R

20 Ω

C VDD

STMLS05

GND

Figure 7: R-C element in VDD line

Package information STMLS05

# 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

STMLS05 Package information

#### 8.1 UFQFPN, 3x3mm, 16 L package information

A В (D/2xE/2) Ε aaa C 2x △ aaa C 2x TOP VIEW eee C SIDE VIEW

BOTTOM VIEW

Figure 8: UFQFPN, 3x3 mm, 16 L package outline

- 1. 2. Dimensioning and tolerancing conform to ASME Y14.5-2009.

- The location of the terminal no.1 identifier is within the hatched area.

- Coplanarity applies to the terminals and all other bottom surface metalization.

Package information STMLS05

Table 9: UFQFPN, 3x3 mm, 16 L mechanical data

|                   | Dimensions |             |      |           |           |       |  |  |  |

|-------------------|------------|-------------|------|-----------|-----------|-------|--|--|--|

| Ref.              |            | Millimeters |      | Inches    |           |       |  |  |  |

|                   | Min.       | Nom.        | Max. | Min.      | Nom.      | Max.  |  |  |  |

| Α                 | 0.45       | 0.50        | 0.55 | 0.018     | 0.020     | 0.022 |  |  |  |

| A1                | 0.00       | 0.02        | 0.05 | 0.000     | 0.001     | 0.002 |  |  |  |

| b <sup>(1)</sup>  | 0.18       | 0.25        | 0.30 | 0.007     | 0.010     | 0.012 |  |  |  |

| D                 |            | 3.00 BSC    |      |           | 0.118 BSC |       |  |  |  |

| Е                 |            | 3.00 BSC    |      | 0.118 BSC |           |       |  |  |  |

| е                 |            | 0.5         |      | 0.020     |           |       |  |  |  |

| L                 | 0.30       | 0.40        | 0.50 | 0.012     | 0.016     | 0.020 |  |  |  |

| aaa               |            |             | 0.05 |           |           | 0.002 |  |  |  |

| bbb               |            |             | 0.10 |           |           | 0.004 |  |  |  |

| ccc               |            |             | 0.05 |           |           | 0.002 |  |  |  |

| ddd               |            |             | 0.05 |           |           | 0.002 |  |  |  |

| eee               |            |             | 0.05 |           |           | 0.002 |  |  |  |

| N <sup>(2)</sup>  | 16         |             |      |           | 0.630     |       |  |  |  |

| ND <sup>(3)</sup> | 4          |             |      | 0.157     |           |       |  |  |  |

| NE <sup>(3)</sup> |            | 4           |      |           | 0.157     |       |  |  |  |

#### Notes

$<sup>^{(1)}</sup>$ Dimension b applies to the metallized terminal and is measured between 0.15 mm and 0.30 mm from the terminal tip. If the terminal has the optional radius on the other end of the terminal, dimension b should not be measured in that radius area.

<sup>(2)</sup>N is the total number of terminals.

$<sup>\</sup>ensuremath{^{(3)}}\mbox{ND}$  and NE refer to the number of terminals on the D and E side respectively.

STMLS05 Revision history

# 9 Revision history

Table 10: Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 13-Dec-2016 | 1        | Initial release  |

| 10-Feb-2017 | 2        | Typo corrections |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved