# RT1025 ECG/PPG AFE Daughter Board

### **Purpose**

The RT1025 is an integrated SOC solution for Heart-Rate monitoring and Biopotential measurements. The RT1025 integrate low noise voltage and current sensing channels and is capable of sensing ECG(Electrocardiography) and PPG(Photoplethysmography) simultaneously. Richtek Technology develops a daughter board (DTB) to evaluate RT1025 performance. This document describes the operation manual of RT1025 daughter board. It includes the schematic, hardware and bench measure procedure.

## **Table of Contents**

| Purpose                                      | 1 |

|----------------------------------------------|---|

| ntroduction                                  | 2 |

| Key Performance Summary Table                | 3 |

| Bench Test Setup Conditions                  | 4 |

| Schematic, Bill of Materials & Board Layout  | 6 |

| More Information                             | 8 |

| mportant Notice for Richtek Evaluation Board | 8 |

#### Introduction

#### General Product Information

The RT1025 is an integrated AFE solution for Heart-Rate monitoring and measurements. The RT1025 integrates low noise voltage and current sensing channels and is capable of sensing ECG (Electrocardiography) and PPG (Photoplethysmography) simultaneously. The RT1025 have > 100dB dynamic range and can sense pulses accurately by detecting the heart's electric signals. The sampling rates of the high-precision voltage and current sensing channels in the RT1025 are configurable between 64 to 4 kHz. The RT1025 solution need only few discrete components and is easy to use for low-power medical ECG/PPG, sports, and fitness applications. With high levels of integration and high-precision voltage and current sensing channels, the RT1025 solution is suitable for scalable medical instrumentation systems. The RT1025 is available in a 3.1mm x 3.4mm, 41-Ball, 0.4mm pitch, WL-CSP package.

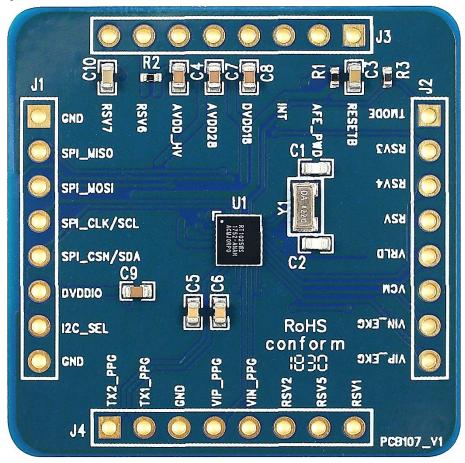

The daughter board (DTB) was developed to bring out alls of RT1025 pins to DIP pins. The daughter board includes the RT1025 together with the required 32kHz Xtal and the passive components to quickly evaluate the operation and performance of the RT1025. The detail schematic, hardware and bench measure procedure will be described in the following section. The daughter board number is PCB107\_V1 and the dimensions are 3.3cm x 3.3cm.

#### **Product Feature**

- Daughter Board Feature

- ► Evaluation Board Number : PCB107\_V1

- ▶ Dimension: 3.3cm x 3.3cm

- ▶ 32 DIP Pins

- ECG Channel Feature

- ► Supports Two-Electrode (2E) Mode and Right Leg Drive (RLD) Mode

- ► Low Noise PGA and High Resolution ADC

- ▶ Input Impedance : 125M to 500MΩ at Two-Electrode Mode and > 1GΩ at Right Leg Drive Mode

- ► Low Input-Referred Noise : 0.67µVrms (64Hz ODR, Gain = 12)

- ▶ Dynamic Range: 110dB at Gain = 6

- ► CMRR > 85dB at 60Hz

- ▶ Data Rate: 64SPS to 4k SPS

- PPG Channel Feature

- ► Flexible Timing Control and Support Dynamic Power Down

- ► TX Supports H-bridge and Push/Pull Mode

- ► TX LED Current Range: 10 / 25 / 35 / 50 / 65 / 75 / 90 / 105mA, Each with 8-bit Current Resolution

- ▶ Input Maximum Current Range : 0.5 to 50µA

- ▶ Input Maximum Capacitance : 1nF

- ► Input-Referred Noise : 50pA<sub>rms</sub> at 5µA Input Current

- ► CMRR > 80dB at 60Hz

► PGA Gain : 1 to 6V/V

- ► Ambient DAC1/DAC2 Range : 1 to 6µA

- Others

- ► 2-in-1 Bio-Sensing AFE (Voltage/Current)

- ▶ Built-In Heartbeat Interval Estimation

- ▶ Integrates an Oscillator to offer High-Precision Clock with External Crystal

- ► Support I<sup>2</sup>C and SPI I/F for MCU

- ▶ On-Chip SRAM for Data Buffering

- **▶ Ultra-Low Power Consumption**

- ► Operating Temperature Range : -20°C to 65°C

- ► Small 3.1mm x 3.4mm, 41-Ball, 0.4mm Pitch, and WL-CSP Package

- ► RoHS Compliant and Halogen Free

## Key Performance Summary Table

| Key Features                   | Evaluation Board Number : PCB107_V1 |

|--------------------------------|-------------------------------------|

| Analog Supply Voltage          | 2.8V                                |

| Digital Supply Voltage         | 1.8V                                |

| I/O Supply Voltage             | 1.8V to 3.3V                        |

| Current Consumption (Idle)     | < 7μΑ                               |

| Current Consumption (ECG)      | 570μΑ                               |

| Current Consumption (PPG)      | 530μΑ                               |

| Default Marking & Package Type | RT1025WS, WL-CSP-41B 3.10x3.48 (BS) |

## **Bench Test Setup Conditions**

### Headers Description and Placement

Carefully inspect all the components used in the EVB according to the following Bill of Materials table, and then make sure all the components are undamaged and correctly installed. If there is any missing or damaged component, which may occur during transportation, please contact our distributors or e-mail us at evb service@richtek.com.

#### **Test Points**

The EVB is provided with the connecter interfaces and pin names listed in the table below.

| Test Point | Pin Name      | Comment (expected waveforms or voltage levels on test points)                                                            |  |

|------------|---------------|--------------------------------------------------------------------------------------------------------------------------|--|

| JP1-1      | GND           | Ground.                                                                                                                  |  |

| JP1-2      | SPI_MISO      | SPI serial out master in.                                                                                                |  |

| JP1-3      | SPI_MOSI      | SPI serial in master out.                                                                                                |  |

| JP1-4      | SPI_CLK / SCL | 1. SPI mode : SPI clock pin. (SPI_CLK) 2. I <sup>2</sup> C mode : I <sup>2</sup> C clock pin. (I2C_SCL)                  |  |

| JP1-5      | SPI_CSN / SDA | <ol> <li>SPI mode : SPI data pin. (SPI_CSN)</li> <li>I<sup>2</sup>C mode : I<sup>2</sup>C data pin. (I2C_SDA)</li> </ol> |  |

| JP1-6      | DVDDIO        | Digital IO supply.                                                                                                       |  |

| JP1-7      | I2C_SEL       | 1. SPI mode : please keep I2C_SEL low.<br>2. I <sup>2</sup> C mode : please keep I2C_SEL high.                           |  |

| Test Point          | Pin Name         | Comment (expected waveforms or voltage levels on test points) |  |

|---------------------|------------------|---------------------------------------------------------------|--|

| JP1-8               | GND              | Ground.                                                       |  |

| JP2-1               | TMODE            | Leave floating. (Connect to Ground on EVB)                    |  |

| JP2-2, JP2-3, JP2-4 | RSV3, RSV4, RSV  | Reserve for testing. (Leave floating)                         |  |

| JP2-5               | VRLD             | RLD output. (Leave floating at 2E mode)                       |  |

| JP2-6               | VCM              | PPG input common mode voltage. (Leave floating)               |  |

| JP2-7               | VIN_EKG          | INN_ECG Pin for ECG IA negative input.                        |  |

| JP2-8               | VIP_EKG          | INP_ECG Pin for ECG IA positive input.                        |  |

| JP3-1               | RESETB           | Reset pin.                                                    |  |

| JP3-2               | AFE_PWD          | Power down pin.                                               |  |

| JP3-3               | INT              | Interrupt pin.                                                |  |

| JP3-4               | DVDD18           | Digital supply.                                               |  |

| JP3-5               | AVDD28           | Analog supply.                                                |  |

| JP3-6               | AVDD_HV          | PPG LED driver power.                                         |  |

| JP3-7, JP3-8        | RSV6, RSV7       | Reserve for testing. (leave floating)                         |  |

| JP4-1               | TX2_PPG          | TX2 pin for LED driver output.                                |  |

| JP4-2               | TX1_PPG          | TX1 pin for LED driver output.                                |  |

| JP4-3               | GND              | Ground.                                                       |  |

| JP4-4               | VIP_PPG          | INP_PPG Pin for PPG receiver input pin.                       |  |

| JP4-5               | VIN_PPG          | INN_PPG Pin for PPG receiver input pin.                       |  |

| JP4-6, JP4-7, JP4-8 | RSV2, RSV5, RSV1 | Reserve for testing. (Leave floating)                         |  |

#### Measurement Procedure

The RT1025 daughter board is fully assembled and tested. The daughter board brings out all I/O pins of the RT1025 for easily evaluate the IC performance and development.

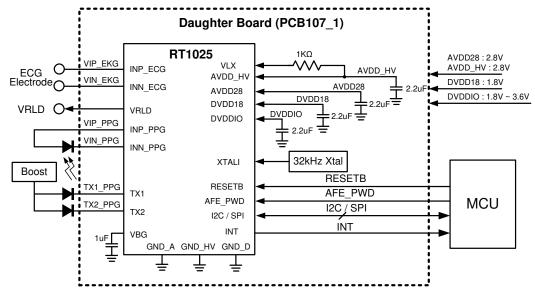

### Typical Applicatin Circuite

Using daughter board for ECG/PPG Sensing

## Schematic, Bill of Materials & Board Layout

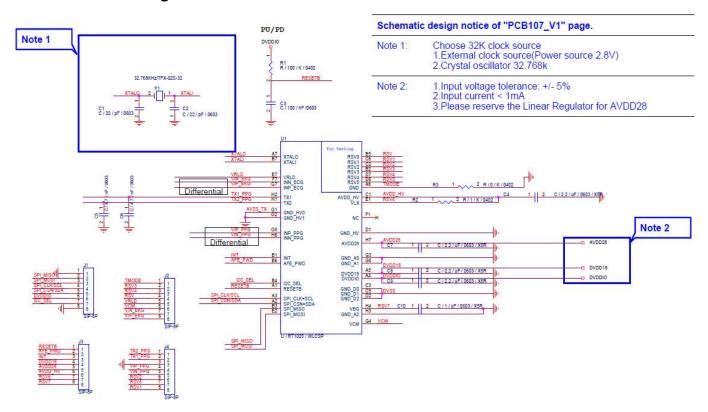

### **EVB Schematic Diagram**

### Bill of Materials

| Reference      | Qty | Part Number         | Description          | Package                      | Manufacturer |

|----------------|-----|---------------------|----------------------|------------------------------|--------------|

| C1, C2         | 2   | 0603N220J500CT      | 22pF/50V/NPO         | C-0603                       | WALSIN       |

| C3             | 1   | C1608X7R1H104K080AA | 100nF/50V/X7R        | C-0603                       | TDK          |

| C4, C7, C8, C9 | 4   | 0603X225K160CT      | 2.2μF/16V/X5R        | C-0603                       | WALSIN       |

| C5, C6         | 2   | 0603B472K500CT      | 4.7nF/50V/X7R        | C-0603                       | WALSIN       |

| C10            | 1   | C1608X5R1E105K080AC | 1μF/25V/X5R          | C-0603                       | TDK          |

| R1             | 1   | WR04X1003FTL        | 100k/1%              | R-0402                       | WALSIN       |

| R2             | 1   | WR04X1001FTL        | 1k/1%                | R-0402                       | WALSIN       |

| R3             | 1   | WR04X000 PTL        | 0k                   | R-0402                       | WALSIN       |

| U1             | 1   | RT1025WS            | ECG/PPG AFE IC       | WL-CSP-41B<br>3.10x3.48 (BS) | Richtek      |

| Y1             | 1   | DST-310S            | 32.768kHz/TFX-02S-32 | CRY-DST310S                  | HARMONY      |

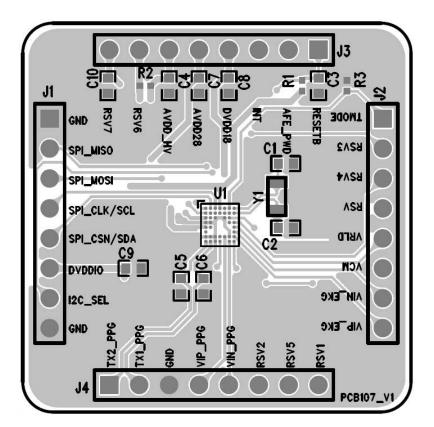

### PCB Layout

Top View

**Bottom View**

### More Information

For more information, please find the related datasheet or application notes from Richtek website <a href="http://www.richtek.com">http://www.richtek.com</a>.

## Important Notice for Richtek Evaluation Board

THIS DOCUMENT IS FOR REFERENCE ONLY, NOTHING CONTAINED IN THIS DOCUMENT SHALL BE CONSTRUED AS RICHTEK'S WARRANTY, EXPRESS OR IMPLIED, UNDER CONTRACT, TORT OR STATUTORY, WITH RESPECT TO THE PRESENTATION HEREIN. IN NO EVENT SHALL RICHTEK BE LIABLE TO BUYER OR USER FOR ANY AND ALL DAMAGES INCLUDING WITHOUT LIMITATION TO DIRECT, INDIRECT, SPECIAL, PUNITIVE OR CONSEQUENTIAL DAMAGES.