# TCM8030 Data Manual

**Baseband Processor for Analog Cellular Telephones**

SLWS033A October 1997

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

## Contents

## Title

Section

| 1 | Intro<br>1.1<br>1.2<br>1.3<br>1.4 | TCM803<br>1.1.1<br>1.1.2<br>Function<br>Terminal | 0 Features<br>Data Processing Features<br>Audio Processing Features<br>al Block Diagram<br>Assignments | 1–2<br>1–2<br>1–2<br>1–3<br>1–4 |

|---|-----------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------|

| 2 | Elec                              | trical Spe                                       | ecifications                                                                                           | 2–1                             |

|   | 2.1                               |                                                  | Maximum Ratings Over Operating Free-Air Temperature Range                                              |                                 |

|   | 2.2                               |                                                  | nended Operating Conditions                                                                            |                                 |

|   | 2.3                               |                                                  | I Characteristics Over Recommended Range of Supply Voltages and                                        |                                 |

|   | 2.0                               |                                                  | ng Conditions                                                                                          | 2–2                             |

|   |                                   | 2.3.1                                            | Electrical Characteristics Over Recommended Operating Conditions .                                     |                                 |

|   |                                   | 2.3.2                                            | DIGITAL I/Os                                                                                           |                                 |

|   | 2.4                               | -                                                | t Path Specifications                                                                                  |                                 |

|   |                                   | 2.4.1                                            | MICAMP1 and MICAMP2                                                                                    |                                 |

|   |                                   | 2.4.2                                            | Voice and DTMF (V/D) Trim, MIC1 to TXO                                                                 |                                 |

|   |                                   | 2.4.3                                            | COMPRESSOR, MIC1 to TXO                                                                                |                                 |

|   |                                   | 2.4.4                                            | LIMITER, MIC1 to TXO                                                                                   |                                 |

|   |                                   | 2.4.5                                            | TXTRIM, MIC1 to TXO                                                                                    | 2–5                             |

|   |                                   | 2.4.6                                            | Transmit Path, MIC1 to TXO                                                                             | 2–5                             |

|   |                                   | 2.4.7                                            | Transmit Data at TXO                                                                                   | 2–6                             |

|   |                                   | 2.4.8                                            | TX-DAT TRIM at TXO                                                                                     |                                 |

|   |                                   | 2.4.9                                            | Transmit SAT at TXO                                                                                    |                                 |

|   |                                   | 2.4.10                                           | SAT TRIM at TXO                                                                                        |                                 |

|   | 2.5                               |                                                  | Path Specifications                                                                                    |                                 |

|   |                                   | 2.5.1                                            | RXAMP                                                                                                  |                                 |

|   |                                   | 2.5.2                                            | RXTRIM, RXGAIN to REC1                                                                                 |                                 |

|   |                                   | 2.5.3                                            | EXPANDOR, RXGAIN to REC1                                                                               |                                 |

|   |                                   | 2.5.4                                            | Receive Path, RXGAIN to REC1                                                                           |                                 |

|   |                                   | 2.5.5                                            | VOL CTRL, RXGAIN to REC1                                                                               |                                 |

|   |                                   | 2.5.6                                            | LS DRIVER, at RECP and RECN, Input at RECIN                                                            |                                 |

|   |                                   | 2.5.7                                            | Receive Data Detect                                                                                    |                                 |

|   |                                   | 2.5.8                                            | Receive SAT Detect                                                                                     |                                 |

|   | 2.6                               |                                                  | neous Block Specifications                                                                             |                                 |

|   |                                   | 2.6.1                                            | Digital-to-Analog Converters DAC1, DAC2, and DAC3                                                      |                                 |

|   |                                   | 2.6.2                                            | TCXO Amplifier                                                                                         |                                 |

|   |                                   | 2.6.3                                            | IF Amplifier                                                                                           |                                 |

|   |                                   | 2.6.4                                            | DTMF Generator                                                                                         |                                 |

|   |                                   | 2.6.5                                            | AMP7                                                                                                   | 2–11                            |

|   | 2.7  | Timing Requirements Over Recommended Ranges of Operating Conditions . 2–12       |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|---|------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 3 | Para | ameter Measurement Information 3–1                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 4 | Турі | cal Chara                                                                        | acteristics                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4–1                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 5 |      | ciples of<br>Overview<br>Receive<br>Transmit<br>Data Pro<br>Miscellar<br>Clocks. | Operation         Audio Path         Audio Path         t Audio Path         t Audio Path         bocessor         neous Circuits         Modes         Total Power-Down Mode         Shutdown Mode         Idle Mode         Tone Mode                                                                                                                                                                                                               | 5–1<br>5–4<br>5–5<br>5–6<br>5–6<br>5–7<br>5–8<br>5–11<br>5–14<br>5–15<br>5–16                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|   |      | 5.7.5<br>5.7.6<br>5.7.7                                                          | Full Operation Mode, DTMF TX Off<br>Full Operation Mode, DTMF TX On<br>Independent Circuits                                                                                                                                                                                                                                                                                                                                                           | . 5–16<br>. 5–16                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|   | 5.8  |                                                                                  | Definitions         Transmit Path Audio Processing Functions         Receive Path Audio Processing Functions         Transmit Path Data Processing Functions         Receive Path Data Processing Functions         Transmit Path Data Processing Functions         Receive Path Data Processing Functions         Receive Path Data Processing Functions         Receive Path SAT Processing Functions         Receive Path SAT Processing Functions | . 5–17<br>. 5–17<br>. 5–18<br>. 5–19<br>. 5–19<br>. 5–20                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|   |      | Microcor                                                                         | neous Functions                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ul> <li>. 5–22</li> <li>. 5–24</li> <li>. 5–26</li> <li>. 5–28</li> <li>. 5–29</li> <li>. 5–32</li> <li>. 5–32</li> <li>. 5–33</li> <li>. 5–33</li> <li>. 5–34</li> <li>. 5–35</li> <li>. 5–35</li> <li>. 5–35</li> </ul> |  |  |  |  |

| E 44 40 | Address 44 TV Data Mard 4 (TVD4)                                |      |

|---------|-----------------------------------------------------------------|------|

| 5.11.19 | Address 14 - TX Data Word 4 (TXD4)                              |      |

| 5.11.20 | Addresses 15, 17, 19 - PIO Control Words (PIOC1, PIOC2, PIOC3). |      |

| 5.11.21 | Addresses 16, 18, 1A - PIO Output Words (PO1, PO2, PO3)         |      |

| 5.11.22 | Address 1B - PIO3 Pullup Enable Transistors (PI3PULL)           |      |

| 5.11.23 | Address 1C - PIO3 Interrupt Control (PI3INT)                    |      |

| 5.11.24 | Address 20 - RXRF Idle Mode Timer (RXRFTIM)                     |      |

| 5.11.25 | Address 21 - Counter/Timer Coef (TIMER)                         |      |

| 5.11.26 | Address 22 - Mismatch Wideband (FRAMEMIS)                       |      |

| 5.11.27 | Address 23 - FOCC Dotting Coefficient (FCCDOT) - Wideband       |      |

| 5.11.28 | Address 24 - FVC Dotting Coefficient (FVCDOT) - Wideband        |      |

| 5.11.29 | Address 25 - Allowed Narrowband Errors (NBCOEF) - Narrowband .  |      |

| 5.11.30 | Address 26 - SAT Lock Determination (SATCOEF) - Wideband        |      |

| 5.11.31 | Address 2E - Data Processor Test Control 1 (DTEST1)             | 5–38 |

| 5.11.32 | Address 30 - Auxiliary Power Enable (AUXPE) Register            | 5–38 |

| 5.11.33 | Address 31 - Clock Source Frequency Select (CLKSRC)             |      |

| 5.11.34 | Address 32 - Receive-Audio Path Configuration (RXCFG)           | 5–39 |

| 5.11.35 | Address 33 - Transmit-Audio Path Configuration (TXCFG)          | 5–40 |

| 5.11.36 | Address 34 - Microphone and TX DTMF Trim (VDTRIM)               | 5–40 |

| 5.11.37 | Address 35 - Limiter Trim (LIMITER)                             | 5–41 |

| 5.11.38 | Address 36 - Transmit SAT Trim (SAT TRIM)                       |      |

| 5.11.39 | Address 37 - Transmit Data Trim (TXDATRIM)                      | 5–42 |

| 5.11.40 | Address 38 - Transmit Trim (TXTRIM)                             | 5–43 |

| 5.11.41 | Address 39 - Receive Trim (RXTRIM)                              |      |

| 5.11.42 | Address 3A - Loudspeaker Volume Control (VOL CTRL)              |      |

| 5.11.43 | Address 3B - DTMF Control (DTMFCTRL)                            |      |

| 5.11.44 | Address 3C - Analog Test Modes (ATEST)                          |      |

| 5.11.45 | Address 40 - DAC Range Select (DACRANGE)                        |      |

| 5.11.46 | Address 41 - DAC1 Data (DAC1DAT)                                |      |

| 5.11.47 | Address 42 - DAC2 Data (DAC2DAT)                                |      |

| 5.11.48 | Address 43 - DAC3 Data (DAC3DAT)                                |      |

| 5.11.49 | Address 44 - AFC control (AFCCTRL)                              |      |

|         | peration                                                        |      |

| 5.12.1  | Address 00 - Status Word 1 Register (S1)                        |      |

| 5.12.2  | Address 01 - Status Word 2 Register (S2)                        |      |

| 5.12.3  | Address 05 - Event Register 1 (E1)                              |      |

| 5.12.4  | Address 06 - Event Register 2 (E2)                              |      |

| 5.12.5  | Address 10 - RX Data Word 0 (RXD0)                              |      |

| 5.12.6  | Address 11 - RX Data Word 1 (RXD1)                              |      |

| 5.12.7  | Address 12 - RX Data Word 2 (RXD2)                              |      |

| 5.12.8  | Address 13 - RX Data Word 3 (RXD3)                              |      |

| 5.12.9  | Addresses 16, 18, 1A - PIO Status Words (PI1, PI2, PI3)         |      |

| 5.12.10 | Address 22 - RX Repeat Count - Wideband                         |      |

| 5.12.10 | Address 25 - Narrowband Error Rate (NBERRS)                     |      |

| 5.12.11 | Address 43 - AFC Terminal Count MS Byte (AFCIF1)                |      |

| 5.12.12 | Address 44 - AFC Terminal Count Middle Byte (AFCIF1)            |      |

| 5.12.13 | Address 45 - AFC Terminal Count Iniddle Byte (AFCIF2)           |      |

| 5.12.14 |                                                                 | 5-55 |

| 5.13 | 5.13 Event Register 1 (E1) Status Definitions 5 |                                                      |      |  |  |

|------|-------------------------------------------------|------------------------------------------------------|------|--|--|

|      | 5.13.1                                          | RX data available (E1 bit 1)                         | 5–53 |  |  |

|      | 5.13.2                                          | TX buffer available (E1 bit 1)                       | 5–53 |  |  |

|      | 5.13.3                                          | Arbitration failure (E1 bit 2)                       | 5–53 |  |  |

|      | 5.13.4                                          | TX sequence complete (E1 bit 3)                      | 5–53 |  |  |

|      | 5.13.5                                          | Change of FOCC busy/idle (E1 bit 4)                  | 5–53 |  |  |

|      | 5.13.6                                          | Counter/timer reaches zero state (E1 bit 5)          | 5–53 |  |  |

|      | 5.13.7                                          | Wideband SAT/Narrowband DSAT changed (E1 bit 6)      | 5–53 |  |  |

| 5.14 | Event Re                                        | egister 2 (E2) Status Definitions                    | 5–54 |  |  |

|      | 5.14.1                                          | FOCC data changed value (E2 bit 0)                   | 5–54 |  |  |

|      | 5.14.2                                          | FVC dotting detected – wideband (E2 bit 1)           | 5–54 |  |  |

|      | 5.14.3                                          | FVC Frame Sync achieved (E2 bit 2)                   | 5–54 |  |  |

|      | 5.14.4                                          | Change in Frame Sync (E2 bit 3)                      | 5–54 |  |  |

|      | 5.14.5                                          | Change of RXRF idle mode power savings (E2 bit 4)    | 5–54 |  |  |

|      | 5.14.6                                          | NRZ error count register (NBERRS) updated (E2 bit 5) | 5–55 |  |  |

|      | 5.14.7                                          | PIO3 input port sensed signal (E2 bit 6)             | 5–55 |  |  |

|      | 5.14.8                                          | AFC has reached terminal count (E2 bit 7)            | 5–55 |  |  |

## List of Illustrations

| Figu | ire Title                                                  | Page |

|------|------------------------------------------------------------|------|

|      | Functional Block Diagram      Terminal Assignments         |      |

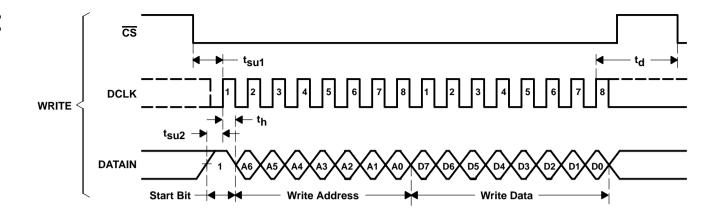

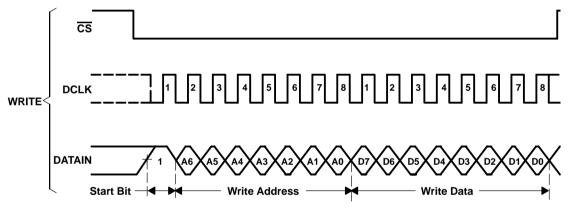

|      | Microcontroller Interface Write Timing Diagram             |      |

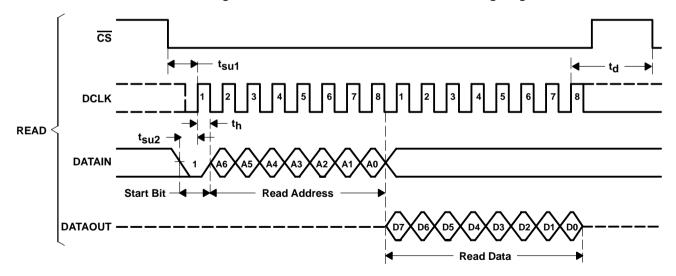

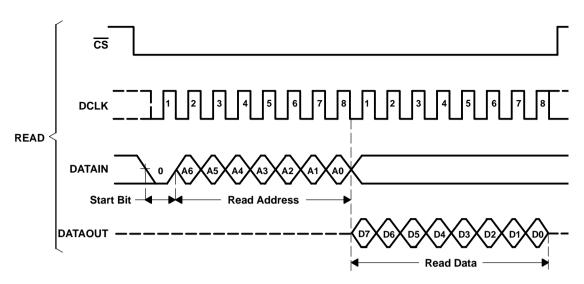

|      | Microcontroller Interface Read Timing Diagram              |      |

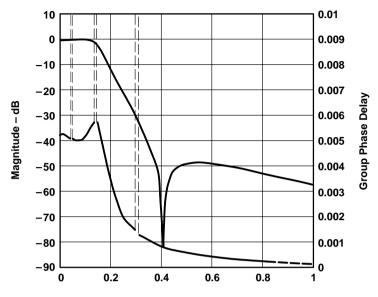

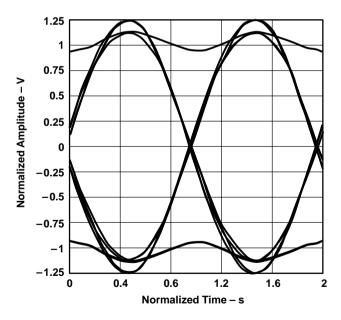

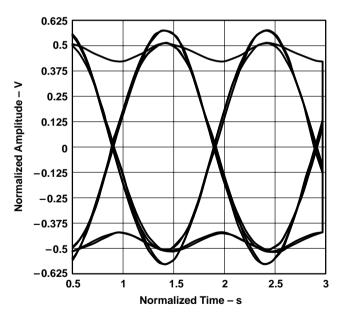

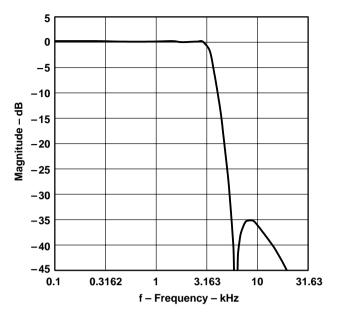

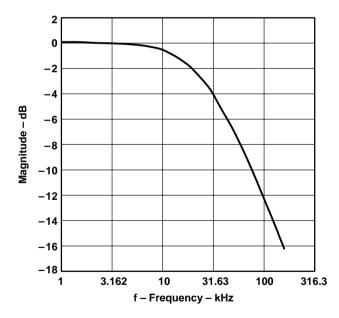

|      | NBRXLPF Frequency Response                                 |      |

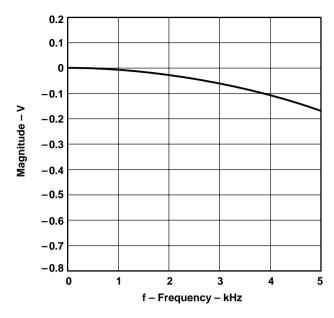

|      | NBRXLPF Eye Pattern                                        |      |

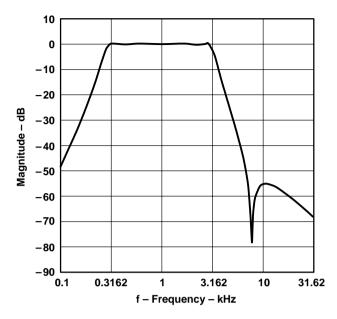

| 4–3  | TXBPF Frequency Response                                   | 4–2  |

| 4–4  | TXBPF Frequency Response                                   | 4–2  |

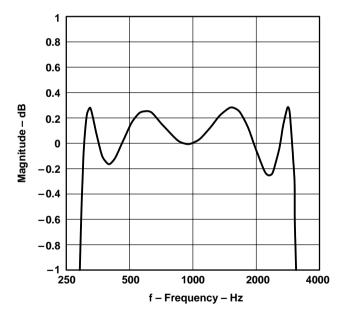

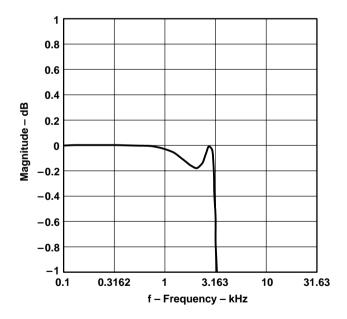

| 4–5  | TXDATLPF and TXSUMLPF Combined Response                    | 4–3  |

|      | Eye Pattern for TXDALPF and TXSUMLPF Combined (Narrowband) |      |

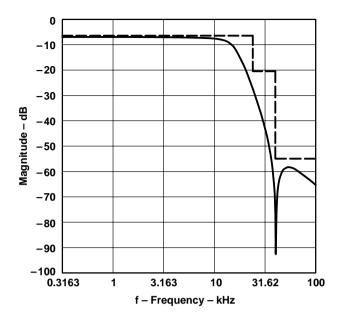

|      | TXLPF Frequency Response                                   |      |

|      | TXLPF Frequency Response                                   |      |

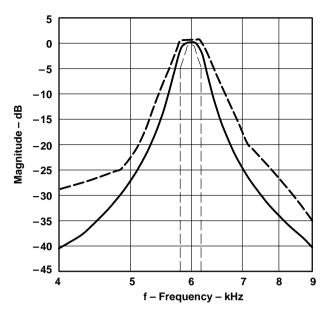

|      | TXSATBPF Response Profile                                  |      |

|      | 0 TXSUMLPF Frequency Response                              |      |

|      | 1 TXSUMLPF Frequency Response                              |      |

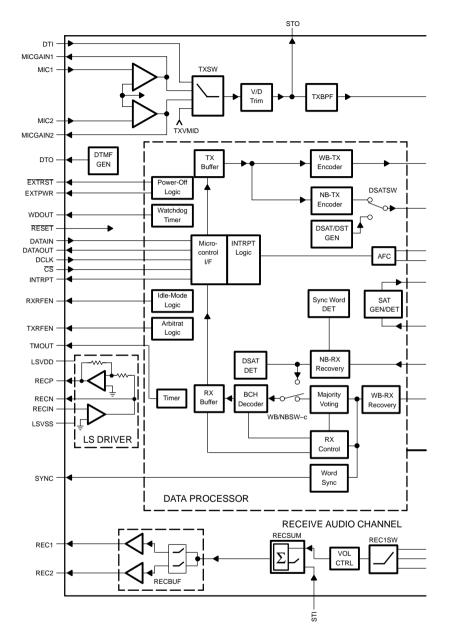

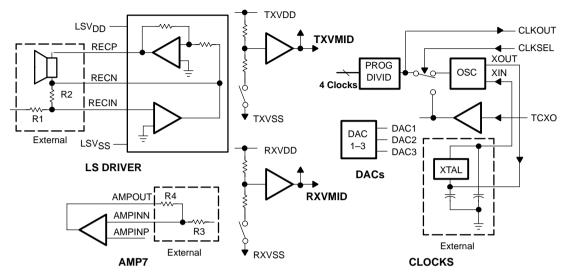

|      | TCM8030 Detailed Functional Block Diagram                  |      |

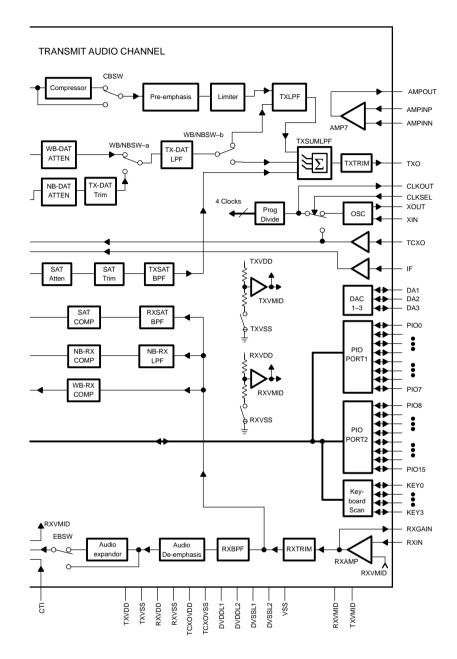

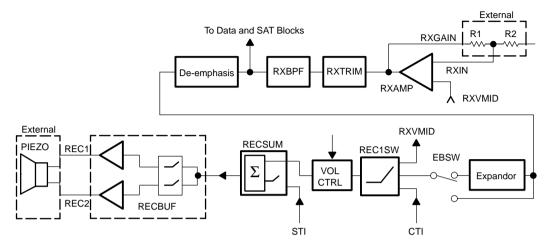

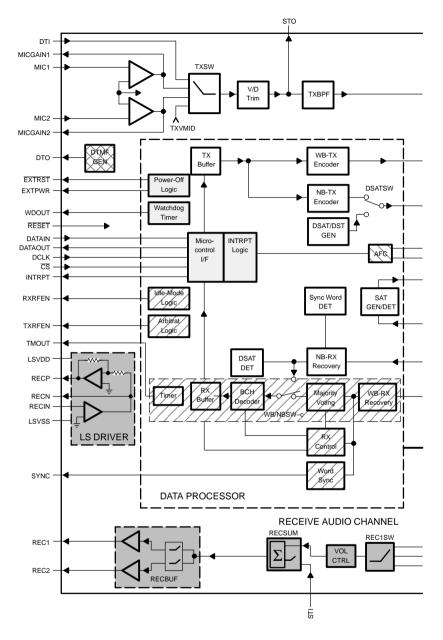

|      | Receive Audio Path                                         |      |

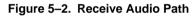

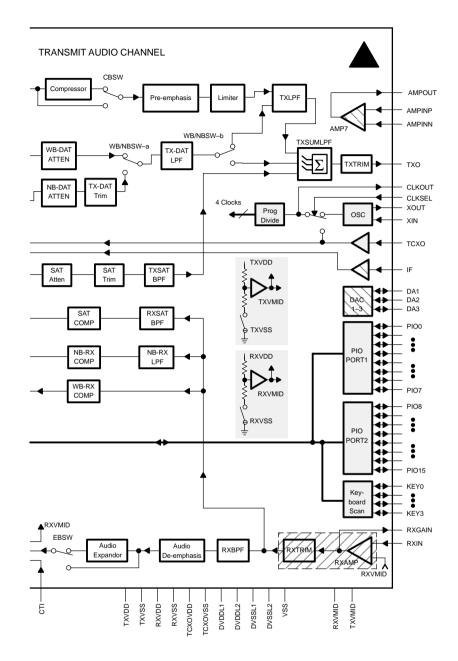

|      | Transmit Audio Path                                        |      |

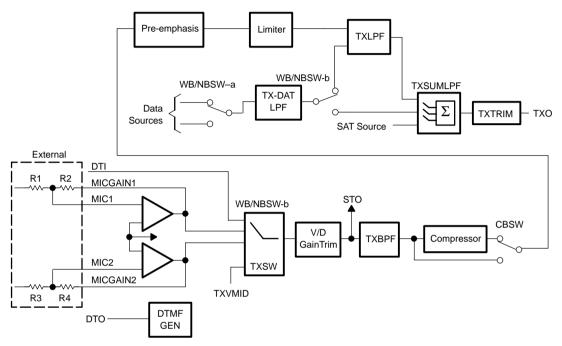

|      | Data Processor Block Diagram                               |      |

|      | Miscellaneous Circuit Block Diagrams                       |      |

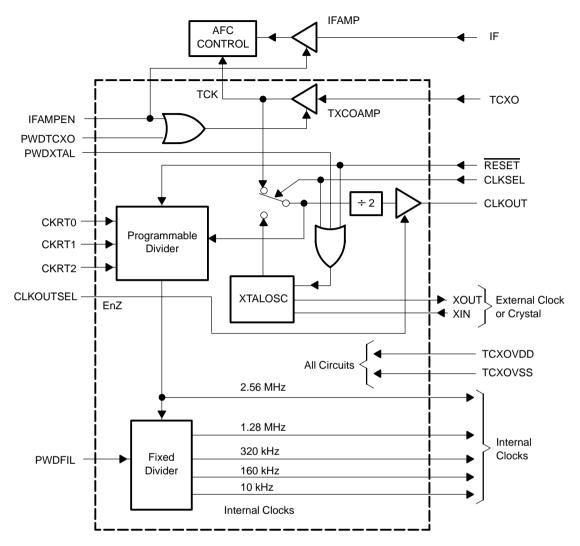

|      | Clocking Scheme Functional Block Diagram                   |      |

|      | Power Modes Block Diagram                                  |      |

|      | Summary of TCM8030 Power-Up Events                         |      |

|      | Microcontroller Interface Write Timing Diagram             |      |

| 5-10 | 0 Microcontroller Interface Read Timing Diagram            | 5–25 |

## **List of Tables**

| Table | Title                                                  | Page  |

|-------|--------------------------------------------------------|-------|

| 5-1 0 | Clock Sources                                          | . 5–8 |

|       | Aster Clock Input Frequency and CLKOUT Select          |       |

|       | Power Modes Block Diagram Legend                       |       |

|       | Vrite Address Map                                      |       |

| 5-5 0 | Control Word 1 (C1) Definition                         | 5–28  |

|       | ransmit Signal Selection                               |       |

| 5-7 ( | Dperational Control Word 1, Bit 4 Definition C1.4      | 5–29  |

| 5-8 0 | Control Word 2 (C2) Definition                         | 5–30  |

| 5-9 C | Digital Color Codes — Narrowband                       | 5–30  |

| 5–10  | SAT Color Codes — Wideband                             | 5–30  |

| 5–11  | DSAT Color Codes — Narrowband                          | 5–31  |

| 5–12  | Signal Polarity Selection Control Word (C3) Definition | 5–32  |

|       | Master Power Enable Modes (C4) Definition              |       |

| 5–14  | TCM8030 Power Modes                                    | 5–33  |

| 5–15  | Optional Controls Word 5 (C5) Definition               | 5–33  |

|       | Interrupt Control Word 1 (IE1) Definition              |       |

| 5–17  | Interrupt Control Word 2 (IE2) Definition              | 5–34  |

| 5–18  | Transmit Data Word 4 (TXD4) Definition                 | 5–35  |

| 5–19  | PIO Control Words (PIO C1,2,3) Definition              | 5–35  |

| 5–20  | PIO3 Interrupt Control (PI3INT, bits 3–0) Definition   | 5–35  |

| 5–21  | PIO3 Interrupt Control (PI3INT bits 7–4) Definition    | 5–36  |

| 5–22  | Narrowband Error Coefficient Setting                   | 5–37  |

|       | SAT Lock Control Definition                            |       |

| 5–24  | TCM8030 Data Processor Test Modes                      | 5–38  |

| 5–25  | Data Recovery Observation (DTEST1.2 = 1)               | 5–38  |

| 5–26  | Auxiliary Power Enables (AUXPE) Definition             | 5–39  |

|       | External Clock and Crystal Frequency Select            |       |

| 5–28  | Receive-Audio Path Configuration (RXCFG) Control       | 5–39  |

| 5–29  | Transmit-Audio Path Configuration (TXCFG) Control      | 5–40  |

| 5–30  | Microphone and TXDTMF Trim (VDTRIM) Adjust             | 5–40  |

| 5–31  | Limiter Trim Adjust                                    | 5–41  |

| 5–32  | Transmit SAT TRIM Adjust                               | 5–41  |

| 5–33  | Transmit Data Trim (TXDATRIM) Adjust                   | 5–42  |

| 5–34  | Transmit Trim (TXTRIM) Adjust                          | 5–43  |

|       | Receive Trim (RXTRIM) Adjust                           |       |

| 5–36  | Loud Speaker Volume Control (VOL CTRL) Adjust          | 5–44  |

|       |                                                        |       |

| 5–38  | DTMF Mode Control                                      | 5–46  |

| 5–39  | DAC Range Select (DACRANGE) Definition                 | 5–47  |

|       | AFC Control                                            |       |

| 5–41  | Read Address Map                                       | 5–49  |

| 5–42 | Status Word 1 (S1) Definition                            | 5–50 |

|------|----------------------------------------------------------|------|

| 5–43 | Status Word 2 (S2) Definition                            | 5–50 |

| 5–44 | Event Register 1 (E1) Definition                         | 5–50 |

| 5–45 | Event Register 2 (E2) Definition                         | 5–51 |

| 5–46 | RX Data Word 3 (RXD3) Definition                         | 5–52 |

| 5–47 | RX Data Word 3 (RXD3) Error Correction Status Definition | 5–52 |

| 5–48 | AFC Terminal Count Lower Byte (AFCIF3) Definition        | 5–53 |

## **1** Introduction

The TCM8030 baseband processor for analog cellular telephones provides all the baseband signal processing required for any of the following standards for mobile and hand-portable cellular telephones: advanced mobile telephone service (AMPS); extended advanced mobile telephone service (EAMPS); narrowband advanced mobile telephone service (NAMPS); total access communication system (TACS); extended total access communication system(ETACS); Japanese total access communication system (JTACS), and narrowband total access communications system (NTACS).

The analog section of the TCM8030 performs all filtering required for the speech, data, supervisory audio tone (SAT), and signaling tone (ST) paths. It has an integrated, International Telegraph and Telephone Consultative Committee (CCITT) compatible compandor as well as microphone preamplifiers and a differential,  $32-\Omega$  earpiece driver to complete the full integration of the baseband audio signal paths.

The digital section of the device implements the data transceiving, data processing, and SAT functions including data recovery, majority voting, Bose-Chaudhuri-Hocquenghem (BCH) decoding, BCH encoding, transmission (TX) frame assembly, and SAT generation, detection, and regeneration. The TCM8030 supports both narrowband standards, NTACS and NAMPS, with full implementation of the narrowband data, and digital supervisory audio tone (DSAT) and digital signaling tone (DST) filtering and processing functions. An on-chip, automatic frequency control (AFC) circuit also facilitates narrowband operation. Communication with the microcontroller is through a simple four-wire serial interface.

In addition to these basic signal processing requirements, the TCM8030 integrates many of the ancillary functions required in a typical FM cellular telephone. Included are three 8-bit digital-to-analog converters (DACs), a dual-tone multiple-frequency (DTMF) generator, an 8-bit programmable counter/timer, an independent watchdog timer, two 8-bit microcontroller expansion ports, and a 4-bit keyboard interrupt port. Clock operation is through a pin-selectable on-chip crystal-referenced oscillator, an external clock source, or an external temperature-controlled crystal oscillator (TCXO).

The TCM8030 is designed for ultra low-power applications and is manufactured using a low-power complementary metal-oxide semiconductor (CMOS) process. It operates from a single 2.7-V to 5.5-V supply and has five power-saving modes in addition to normal operation. The TCM8030 also features a total power-down mode in which the TCM8030 waits for the user to press the power-on key located on the telephone keyboard. Also implemented are two features that extend idle mode operation time.

One feature enables a reduction in the duty cycle of the microcontroller, and the other periodically shuts down the RF receiver. These features reduce the system power consumption to a minimum during idle mode and significantly increase the telephone standby time.

The gain and signal selection paths are software configurable so that audio trimming functions do not require manual intervention during telephone calibration on the production line. This production-time reduction feature, together with its high level of integration and low-power design, makes the TCM8030 an ideal solution for FM analog cellular telephones.

#### 1.1 TCM8030 Features

The TCM8030 provides all data and audio processing functions for AMPS, NAMPS, TACS, ETACS, NTACS, and JTACS in a compact, low-power, baseband processor enclosed in an 80-pin TQFP package.

#### 1.1.1 Data Processing Features

The TCM8030 provides data transceiver, data processing, and SAT functions, and includes the following data processing features:

- Single-chip processing for AMPS, NAMPS, TACS, ETACS, NTACS, JTACS, SAT, and DSAT

- 2.7-V to 5.5-V operation

- Serial interface

- User-configurable interrupt structure

- Transmit (TX) and receive (RX) data buffers

- Integrated RX and TX data filters

- TX wideband (WB) SAT filter

- RX WB and narrowband (NB) SAT filters

- RX WB and NB data comparator

- Programmable timer

- Independent watchdog timer

- RX/TX automatic mute functions

- Arbitration processing

- Twenty programmable expansion I/O ports

- WB and NB-RX recovery

- Automatic frequency control (AFC)

- Multiple power-saving mode implementation

- Separate encoder for WB-TX and NB-TX

#### 1.1.2 Audio Processing Features

The TCM8030 provides the following audio processing features:

- AMPS, NAMPS, TACS, ETACS, NTACS, and JTACS operation

- Integrated RX and TX voice filters

- Microphone amplifiers and loud speaker drivers

- Pre-emphasis and de-emphasis filtering

- Digitally-controlled gains and signal selection or muting

- Adjustable TX limiter

- Three 8-bit digital-to-analog converters (DAC) with output buffers

- Dual-tone multifrequency (DTMF) generator

- On-chip compandor

- Flexible clock and oscillator operation

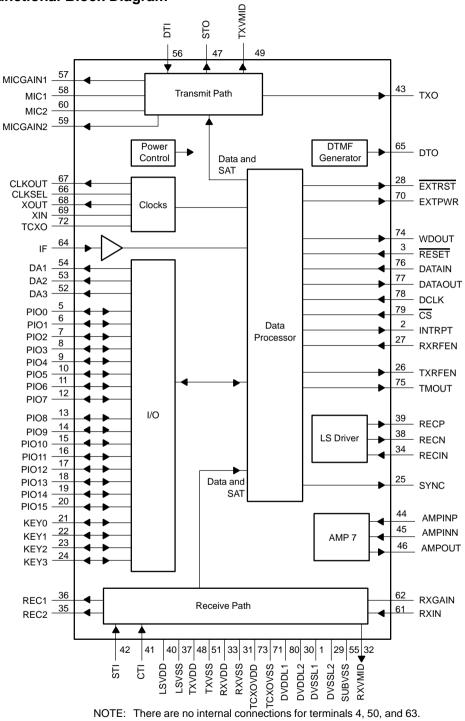

#### 1.2 Functional Block Diagram

Figure 1–1. Functional Block Diagram

#### **1.3 Terminal Assignments**

QFP PACKAGE (TOP VIEW)

NC - No internal connection

Figure 1–2. Terminal Assignments

## **1.4 Terminal Functions**

| TERMINAL          |        | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                      |  |

|-------------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME NO.          |        | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                      |  |

| AMPINN            | 45     | I   | Operational amplifier inverting input (analog). AMPINN is the inverting analog input to the uncommitted operational amplifier, AMP7.                                                                                                                             |  |

| AMPINP            | 44     | I   | Operational amplifier noninverting input (analog). AMPINP is the noninverting analog input to the uncommitted operational amplifier, AMP7.                                                                                                                       |  |

| AMPOUT            | 46     | 0   | Operational amplifier output (analog). AMPOUT is the analog output from the uncommitted operational amplifier, AMP7.                                                                                                                                             |  |

| CLKOUT            | 67     | 0   | Clock output (digital). CLKOUT provides an external digital clock that is one-half the frequency of either the temperature compensated crystal oscillator (TCXO) or the internal crystal oscillator (XTALOSC). The source chosen depends on the value of CLKSEL. |  |

| CLKSEL            | 66     | I   | Clock source select (digital). CLKSEL selects either the TCXO or the internal crystal XTALOSC as the frequency source for CLKOUT through the internal divide-by-two counter.                                                                                     |  |

| CS                | 79     | I   | Chip select. $\overline{CS}$ , active low (digital), selects the write function. When $\overline{CS}$ is high, the read function is selected.                                                                                                                    |  |

| CTI               | 41     | I   | Call tone input (analog). CTI is the DTMF call tone input terminal.                                                                                                                                                                                              |  |

| DA1 – DA3         | 54–52  | 0   | Digital-to-analog converter output (analog). DA1 through DA3 are the output terminals for DACs 1 through 3.                                                                                                                                                      |  |

| DATAIN            | 76     | I   | Data input (digital). DATAIN is the digital data input that the TCM8030 microcontroller read (address) and write (address and data) operation.                                                                                                                   |  |

| DATAOUT           | 77     | 0   | Data output (digital). DATAOUT is the digital output signal for the TCM8030 read (data) operation.                                                                                                                                                               |  |

| DCLK              | 78     | I   | Data clock input (digital). DCLK input provides a clocking source for the TCM8030 read and write operation.                                                                                                                                                      |  |

| DTI               | 56     | I   | DTMF Transmit input (analog). DTI is the analog DTMF signal and is selected for input to the transmit path by the transmission switch (TXSW).                                                                                                                    |  |

| DTO               | 65     | 0   | DTMF generator output (analog). DTO is the analog output from the DTMF generator.                                                                                                                                                                                |  |

| DVDDL1,<br>DVDDL2 | 80, 30 |     | Digital power supply No. 1 and No. 2. DVDDL1 and DVDDL2 are digital power supplies.                                                                                                                                                                              |  |

| DVSSL1,<br>DVSSL2 | 1, 29  |     | Digital ground No. 1 and No. 2. DVSSL1 and DVSSL2 are the grounds for the digital power supplies No. 1 and No. 2.                                                                                                                                                |  |

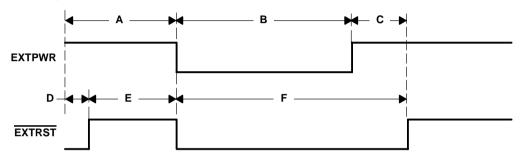

| EXTRST            | 28     | 0   | External reset (digital). EXTRST is the output to the rest of the telephone (used in total power-down mode).                                                                                                                                                     |  |

| EXTPWR            | 70     | 0   | External power-on enable (digital). EXTPWR is a digital signal that is applied to the rest of the telephone (used in total-power-down mode).                                                                                                                     |  |

| IF                | 64     | I   | Intermediate frequency (analog). IF is the input from the receiver second IF to the AFC circuit.                                                                                                                                                                 |  |

| INTRPT            | 2      | 0   | Interrupt output (digital). INTRPT is a digital output from the TCM8030 to signal the telephone microcontroller that a specific event has occurred.                                                                                                              |  |

| KEY0 – KEY3       | 21–24  | I/O | Keyboard interrupts 0 through 3 (digital). KEY0 through KEY3 are programmable as input or output ports to/from the TCM8030 keyboard scan circuit.                                                                                                                |  |

| LSVDD             | 40     |     | Loudspeaker power supply                                                                                                                                                                                                                                         |  |

| LSVSS             | 37     |     | Loudspeaker ground                                                                                                                                                                                                                                               |  |

| 1.4 | Terminal | Functions | (Continued) |

|-----|----------|-----------|-------------|

|-----|----------|-----------|-------------|

| TERMINAL             |              |     | DECODUCTION                                                                                                                                         |  |

|----------------------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                 | NO.          | 1/0 | DESCRIPTION                                                                                                                                         |  |

| MIC1, MIC2           | 58, 60       | I   | Microphone amplifier No. 1 and No. 2 (analog). MIC1 and MIC2 are analog inputs to the TCM8030 transmit audio path.                                  |  |

| MICGAIN1<br>MICGAIN2 | 57, 59       | 0   | Microphone amplifier No. 1 and 2 outputs (analog). MICGAIN1 and MICGAIN2 are amplified outputs that are applied to the TCM8030 transmit audio path. |  |

| NC                   | 4, 50,<br>63 |     | No internal connection                                                                                                                              |  |

| PIO0 – PIO15         | 5–20         | I/O | Programmable input or output ports 0 through 15 (digital). PIO0 through PIO15 can be programmed as either an input or output port.                  |  |

| REC1, REC2           | 35, 36       | 0   | Receive output No. 1 and No. 2 (analog). REC1 and REC2 are analog outputs from the TCM8030 receive audio path.                                      |  |

| RECIN                | 34           | I   | Earpiece amplifier input (analog). RECIN is the analog input to the TCM8030 uncommitted loudspeaker driver circuit.                                 |  |

| RECN                 | 38           | 0   | Earpiece amplifier differential output, negative (analog). RECN is the output from the TCM8030 uncommitted loudspeaker driver circuit.              |  |

| RECP                 | 39           | 0   | Earpiece amplifier differential output, positive (analog). RECP is the analog output from the TCM8030 uncommitted loudspeaker driver circuit.       |  |

| RESET                | 3            | I   | Reset input, active low (digital). RESET is used to hard-reset the TCM8030.                                                                         |  |

| RXGAIN               | 62           | 0   | Receive amplifier output gain (analog). RXGAIN is the amplified signal that is applied to the TCM8030 receive audio path.                           |  |

| RXIN                 | 61           | I   | Receive amplifier input (analog). RXIN is the analog input to the TCM8030 receive audio path.                                                       |  |

| RXRFEN               | 27           | 0   | Receiver RF enable (digital). RXRFEN is an enable signal generated by the idle mode logic circuit.                                                  |  |

| RXVDD                | 33           |     | Receive-analog power supply                                                                                                                         |  |

| RXVMID               | 32           | 0   | Receive midsupply voltage (analog). RXVMID is a midrail voltage reference for internal audio circuits.                                              |  |

| RXVSS                | 31           |     | Receive-analog ground                                                                                                                               |  |

| STI                  | 42           | I   | Sidetone input (analog). STI is the sidetone input to the summing circuitry (RECSUM) in the receiver audio path.                                    |  |

| STO                  | 47           | 0   | Sidetone output (analog). STO is the sidetone output from the TCM8030 transmit audio path.                                                          |  |

| SUBVSS               | 55           |     | Substrate ground connection                                                                                                                         |  |

| SYNC                 | 25           | 0   | Word sync (digital). SYNC is the digital output from the data processor wideband receive recovery circuitry.                                        |  |

| тсхо                 | 72           | I   | Temperature controlled crystal oscillator (analog). TCXO is the signal input from the TCXO to the input buffer, AFC and clock circuits.             |  |

| TCXOVDD              | 73           |     | XTALOSC and TCXO input buffer power supply                                                                                                          |  |

| TCXOVSS              | 71           |     | XTALOSC and TCXO input buffer ground                                                                                                                |  |

| TMOUT                | 75           | 0   | Counter/timer output (digital). TMOUT is the digital output from the data processor counter/timer circuit.                                          |  |

| ТХО                  | 43           | 0   | Transmit output (analog). TXO is the analog output from the TCM8030 transmit audio path.                                                            |  |

| TERMINAL |     |     | DECODIDEION                                                                                                                                          |  |

|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                          |  |

| TXRFEN   | 26  | 0   | Transmit RF enable (digital). TXRFEN is a digital output from the data processor arbitration logic circuit.                                          |  |

| TXVDD    | 48  |     | Transmit analog supply                                                                                                                               |  |

| TXVMID   | 49  | 0   | K midsupply voltage (analog). TXVMID is a midrail voltage reference for internal dio circuits.                                                       |  |

| TXVSS    | 51  |     | ansmit analog ground                                                                                                                                 |  |

| WDOUT    | 74  | 0   | atchdog timer output (digital). WDOUT is the output from the watchdog timer circuit.<br>hen WDOUT times out, the telephone microcontroller is reset. |  |

| XIN      | 69  | I   | xternal crystal input (analog). XIN is clock input terminal or, in conjunction with XOUT rminal, provides the means to connect an external crystal.  |  |

| XOUT     | 68  | 0   | External crystal output (analog). XOUT in conjunction with terminal XIN provides the means to connect an external crystal.                           |  |

## 1.4 Terminal Functions (Continued)

## 2 Electrical Specifications

## 2.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range (see Note 1) $^{\dagger}$

| Supply voltage range, V <sub>DD</sub>                                                                       | –0.5 V to 6.0 V                  |

|-------------------------------------------------------------------------------------------------------------|----------------------------------|

| Input voltage range, VI                                                                                     | 0.5 V to V <sub>DD</sub> + 0.5 V |

| Output voltage range (includes open drain outputs), VO                                                      | $0.5$ V to $V_{DD} + 0.5$ V      |

| Operating free-air temperature range, T <sub>A</sub>                                                        | −40 <sup>◦</sup> C to 85°C       |

| Continuous total power dissipation at (or below), $T_A = 25^{\circ}C$                                       | 500 mW                           |

| Storage temperature range, T <sub>stg</sub><br>NOTE 1: Voltage values are with respect to V <sub>ss</sub> . | –65°C to 150°C                   |

| NOTE 1: Voltage values are with respect to $V_{SS}$ .                                                       |                                  |

<sup>1</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 2.2 Recommended Operating Conditions

|                 | PARAMETER                      | MIN | NOM | MAX | UNIT |

|-----------------|--------------------------------|-----|-----|-----|------|

| V <sub>DD</sub> | Supply voltage (see Note 2)    | 2.7 | 3   | 3.3 | V    |

| ТJ              | Operating junction temperature | -40 |     | 85  | °C   |

NOTE 2: TCM8030 is designed such that all signal levels including trim settings, 0 dB (unity gain level) of compressor/expandor, limiter output level, TXVMID, and RXVMID scale proportionally with V<sub>DD</sub> as follows:

Correction value:  $k = 20 \log(V_{DDX}/3)$  [dB]

For example 0 dB ( $V_{ref}$ ) = - 23.43 + k [dBV] for  $V_{DDX}$

# 2.3 Electrical Characteristics Over Recommended Range of Supply Voltages and Operating Conditions (unless otherwise noted)

| PARAMETER                           | TEST CONDITIONS                                            | MIN | TYP  | MAX   | UNIT |

|-------------------------------------|------------------------------------------------------------|-----|------|-------|------|

| IDD <sub>PM1</sub> Power mode No. 1 | Total power-down mode,<br>AUXPE (write address 30) = 0H    |     | 41   | 96    | μA   |

| IDD <sub>PM2</sub> Power mode No. 2 | Shutdown mode,<br>AUXPE (write address 30) = 0H            |     | 0.34 | 0.5   | mA   |

| IDD <sub>PM3</sub> Power mode No. 3 | Idle mode, AUXPE (write address 30) = 0H                   |     | 2.2  | 4.0   | mA   |

| IDD <sub>PM4</sub> Power mode No. 4 | Tone mode, AUXPE (write address 30) = 0H                   |     | 5    | 8.5   | mA   |

| IDD <sub>PM5</sub> Power mode No. 5 | Full operation, DTMF off,<br>AUXPE (write address 30) = 0H |     | 21   | 36    | mA   |

| IDD <sub>PM6</sub> Power mode No. 6 | Full operation, DTMF on,<br>AUXPE (write address 30) = 0H  |     | 22   | 37    | mA   |

|                                     | DAC1, AUXPE (write address 30) = 01H                       |     | 0.6  | 0.85  | mA   |

|                                     | DAC1 + DAC2,<br>AUXPE (write address 30) = 03H             |     | 0.7  | 1.00  | mA   |

| Auxiliary power modes               | DAC1 + DAC2 + DAC3,<br>AUXPE (write address 30) = 07H      |     | 0.8  | 1.225 | mA   |

|                                     | AMP7, AUXPE (write address 30) = 08H                       |     | 0.4  | 0.5   | mA   |

|                                     | IFAMP, AUXPE (write address 30) = 10H                      |     | 0.25 | 0.5   | mA   |

|                                     | LS DRIVER, single ended,<br>AUXPE (write address 30)= 20H  |     | 2    | 2.5   | mA   |

| TXVMID                              |                                                            | 1.3 | 1.5  | 1.7   | V    |

| RXVMID                              |                                                            | 1.3 | 1.5  | 1.7   | V    |

# 2.3.1 Electrical Characteristics Over Recommended Operating Conditions, $V_{DD}$ =3.0 V, clocked by a crystal oscillator at 5.12 MHz

| F                  | PARAMETER                                         | TEST CONDITIONS                | MIN                   | TYP                 | MAX                   | UNIT  |

|--------------------|---------------------------------------------------|--------------------------------|-----------------------|---------------------|-----------------------|-------|

| lo                 | Source/sink current                               | All terminals except<br>CLKOUT | 1                     |                     |                       | mA    |

| -                  |                                                   | CLKOUT                         | 2                     |                     |                       | mA    |

|                    | Open-drain output, sink current                   |                                | 1                     |                     |                       | mA    |

| V <sub>OH</sub>    | High-level output voltage                         |                                | V <sub>DD</sub> – 0.4 |                     |                       | V     |

| V <sub>OL</sub>    | Low-level output voltage                          |                                |                       |                     | V <sub>SS</sub> + 0.4 | V     |

| Τ <sub>Ρ</sub>     | Intrinsic delay                                   |                                |                       | 1                   |                       | ns    |

| $\Delta T_{P}$     | Delta delay, rise or fall                         |                                |                       | 40                  |                       | ns/pF |

| V <sub>IT+</sub>   | Positive - going input threshold voltage          |                                | 0.7 V <sub>DD</sub>   |                     |                       | V     |

| V <sub>IT-</sub>   | Negative - going input<br>threshold voltage       |                                |                       |                     | 0.3 V <sub>DD</sub>   | V     |

| V <sub>Hys</sub>   | Hysteresis (V <sub>IT+</sub> – V <sub>IT–</sub> ) |                                |                       | 0.2 V <sub>DD</sub> |                       | V     |

| I <sub>IH</sub>    | High-level input current                          | $V_{I} = V_{DD}$               |                       |                     | 1                     | μΑ    |

| IIL                | Low-level input current                           | $V_{I} = V_{SS}$               |                       |                     | 1                     | μA    |

| f <sub>clock</sub> | Serial clock frequency                            |                                |                       | 1                   | 1.28                  | MHz   |

| KEY0 - KEY3        | Internal pullup current                           |                                | -25                   |                     | -1                    | μΑ    |

## 2.3.2 DIGITAL I/Os, V<sub>DD</sub> = 3 V

### 2.4 Transmit Path Specifications, $V_{DD}$ = 2.7 V to 3.3 V

#### 2.4.1 MICAMP1 and MICAMP2

| PARAMETER                                        | TEST CONDITIONS                                              | MIN | TYP | MAX | UNIT  |

|--------------------------------------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| Unity gain frequency                             |                                                              |     | 1.5 |     | MHz   |

| Input current at MIC1 and MIC2                   |                                                              |     | 1   |     | μA    |

| Input offset voltage                             |                                                              |     | ±10 |     | mV    |

| Output load resistance at MICGAIN1 and MICGAIN2  |                                                              | 47  |     |     | kΩ    |

| Output load capacitance at MICGAIN1 and MICGAIN2 |                                                              |     |     | 20  | pF    |

| Input noise                                      | $R_{in} = 50 \text{ k}\Omega$ ,<br>psophometrically weighted |     | 0.1 |     | mVrms |

| Open loop gain                                   |                                                              |     | 80  |     | dB    |

| Close loop gain                                  |                                                              |     | 15  | 26  | dB    |

#### 2.4.2 Voice and DTMF (V/D) Trim, MIC1 to TXO

| PARAMETER           | TEST CONDITIONS | MIN   | TYP   | MAX   | UNIT |

|---------------------|-----------------|-------|-------|-------|------|

| Positive trim range | Code FH         | 3.225 | 3.725 | 4.225 | dB   |

| Negative trim range | Code 0H         | -4.8  | -4.3  | -3.8  | dB   |

| Step size           |                 | 0.3   | 0.5   | 0.7   | dB   |

| Nominal             | Code 8H         |       | 0     |       | dB   |

#### 2.4.3 COMPRESSOR, MIC1 to TXO

| PARAMETER                                                       | TEST CONDITIONS                                        | MIN  | TYP    | MAX   | UNIT |

|-----------------------------------------------------------------|--------------------------------------------------------|------|--------|-------|------|

| 0dB unity gain level (V <sub>ref</sub> )                        |                                                        | -26  | -24.43 | -23.3 | dBV  |

| Linearity<br>(relative error with respect to V <sub>ref</sub> ) | $V_{\rm I}$ = (V_{ref} - 5.56 dB) to (V_{ref} + 15 dB) |      |        | ± 0.5 | dB   |

| (see Note 3)                                                    | $V_{I}$ = (V_{ref} - 40 dB) to (V_{ref} - 5.56 dB)     |      |        | ± 1   | ub   |

| Attack time (see Note 4)                                        |                                                        | 2.4  | 3      | 3.6   | ms   |

| Recovery time (see Note 5)                                      |                                                        | 10.8 | 13.5   | 16.2  | ms   |

NOTES: 3. Compressor Vref (-24.43 dBV) = -3.23 dBV with respect to 2.9 kHz FM deviation.

4. Time taken for the output to settle to 1.5 times the final value with a 12 dB input step

5. Time taken for the output to settle to 0.75 times the final value with a -12 dB input step

#### 2.4.4 LIMITER, MIC1 to TXO

| PARAME                                | TER          | TEST CONDITIONS                       | MIN    | TYP   | MAX    | UNIT                        |

|---------------------------------------|--------------|---------------------------------------|--------|-------|--------|-----------------------------|

| Maximum output                        | AMPS, TACS   | Code AH, max. deviation,              | -10.86 | -9.80 | -8.86  |                             |

| signal, with the limiter limiting and | NAMPS        | $V_{DD} = 3 V$ , compressor bypassed, | -18.40 |       | -16.16 | dBV<br>dB<br>dB<br>dB<br>dB |

| nominal settings                      | NTACS        | V <sub>I</sub> = - 2 dBV, f = 1 kHz   | -16.16 |       | -14.22 |                             |

| Positive trim range                   |              | Code FH                               | 2      | 2.5   | 3      | dB                          |

| Negative trim range                   |              | Code 0H                               | -5.5   | -5    | -4.5   | dB                          |

| Step size                             |              |                                       | 0.3    | 0.5   | 0.7    | dB                          |

| Nominal                               | _            | Code AH                               |        | 0     |        | dB                          |

| Distortion                            | AMPS, TACS   | 2/3 of max. output signal,            |        | 0.4   | 3      | %                           |

| Distortion                            | NAMPS, NTACS | f = 1 kHz                             |        | 0.4   | 3      | 70                          |

| Limiter gain                          |              |                                       | 4.75   |       | 6.75   | dB                          |

## 2.4.5 TXTRIM, MIC1 to TXO

| PARAMETER           | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|---------------------|-----------------|------|------|------|------|

| Positive trim range | Code 1FH        | 3.5  | 4    | 4.5  | dB   |

| Negative trim range | Code 0H         | -4.9 | -4.4 | -3.9 | dB   |

| Step size           |                 | 0.18 | 0.28 | 0.38 | dB   |

| Nominal             | Code 10H        |      | 0    |      | dB   |

#### 2.4.6 Transmit Path, MIC1 to TXO

| PARA                   | METER                       | TEST CONDITION                                                         | IS                                                        | MIN    | TYP    | MAX   | UNIT  |

|------------------------|-----------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|--------|--------|-------|-------|

|                        | AMPS, TACS                  |                                                                        |                                                           | 4.75   | 5.75   | 6.75  |       |

| Total transmit<br>gain | NAMPS                       | Compressor bypassed, V <sub>I</sub> =<br>f = 1 kHz                     | –30 dBV,                                                  | -2.3   |        | -1.3  | dB    |

| guin                   | NTACS                       |                                                                        |                                                           | -0.2   |        | 0.8   |       |

| Output level           | AMPS, TACS                  | Compressor bypassed, $V_I = f = 1 \text{ kHz}$                         | -25.25                                                    | -24.25 | -23.25 | dBV   |       |

| TXSUM mute at          | ttenuation (voice)          | $V_1 = -30 \text{ dBV}, f = 1 \text{ kHz}$                             |                                                           | -50    | -80    |       | dB    |

| Distortion             | AMPS, TACS,<br>NAMPS, NTACS | Compressor enabled, $f = 1 I$<br>V <sub>1</sub> = -30 dBV              | Compressor enabled, $f = 1 \text{ kHz}$ ,<br>f = -30  dBV |        |        | 1     | %     |

|                        | AMPS, TACS                  | MIC1, MIC2 = TXVMID,                                                   | 2.3 2.3                                                   |        | 4      |       |       |

| Output noise           | NAMPS                       | Compressor enabled,                                                    |                                                           |        | 1.0    | 1.5   | mVrms |

|                        | NTACS                       | psophometrically weighted                                              |                                                           |        | 0.76   |       |       |

| Crosstalk in TX        | SW                          | $f = 1 \text{ kHz}, V_1 = -30 \text{ dBV}$                             |                                                           | 50     | 70     |       | dB    |

| Crosstalk RX ar        | nd TX path                  | $f = 1 \text{ kHz}, V_1 = -30 \text{ dBV},$<br>MIC1/REC1, RXIN grounde | d                                                         | 60     | 70     |       | dB    |

|                        |                             |                                                                        | <200 Hz                                                   |        |        | -20   |       |

|                        |                             |                                                                        | 300 Hz                                                    | -13.46 |        | -9.46 |       |

|                        |                             |                                                                        | 500 Hz                                                    | -9.02  |        | -5.02 |       |

| Fraguanay roop         |                             | 0 dB reference, f = 1 kHz,<br>$V_1 = -30$ dBV,                         | 2 kHz                                                     | 3.02   |        | 7.02  | - ID  |

| Frequency response     |                             | Compressor bypassed                                                    | 2.5 kHz                                                   | 4.96   |        | 8.96  | dB    |

|                        |                             |                                                                        | 3 kHz                                                     | 4.96   |        | 10.54 |       |

|                        |                             |                                                                        | 5.9 kHz                                                   |        |        | -35   |       |

|                        |                             |                                                                        | >6 kHz                                                    |        |        | -35   |       |

#### 2.4.7 Transmit Data at TXO

| P             | ARAMETER     | TEST CON                | DITIONS                 | MIN   | TYP   | MAX   | UNIT           |

|---------------|--------------|-------------------------|-------------------------|-------|-------|-------|----------------|

| Mute at TXSUM |              |                         |                         | -50   | -80   |       | dB             |

|               | AMPS, TACS   |                         |                         | -14.0 | -12.4 | -10.8 | dB<br>dBV<br>% |

| Output level  | NAMPS        | f = 10 kHz, ST          |                         | -35.1 | -33.6 | -32.1 |                |

|               | NTACS        | 1 = 100 Hz, dat         | f = 100 Hz, data -31.58 |       |       |       |                |

| Distortion    | AMPS, TACS   | f = 10 kHz              |                         |       | 0.4   | 3.7   | %              |

|               |              |                         | 8 kHz                   | -0.5  |       | 0.5   |                |

|               |              |                         | 10 kHz                  | -0.5  |       | 0.5   |                |

|               | AMPS, TACS   | 0 dB                    | 14.4 kHz                | -4    |       | -1.7  | %              |

|               | AIVIFS, TACS | reference,<br>f = 1 kHz | 17 kHz                  | -8.0  |       | -5.5  |                |

| TXDATLPF      |              |                         | 24 kHz                  |       |       | -20   |                |

|               |              |                         | 40 kHz                  |       |       | -50   |                |

|               | NAMPS, NTACS | 0 dB<br>reference,      | 180 Hz                  | -7.0  |       | -5.75 | dB             |

|               |              | f = 50  Hz              | 1 kHz                   |       |       | -20   | uD             |

#### 2.4.8 TX-DAT TRIM at TXO

| PARAMETER           | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|---------------------|-----------------|------|------|------|------|

| Positive trim range | Code 7H         | 1.4  | 1.8  | 2.2  | dB   |

| Negative trim range | Code 0H         | -2.7 | -2.3 | -1.9 | dB   |

| Step size           |                 | 0.4  | 0.6  | 0.8  | dB   |

| Nominal             | Code 4H         |      | 0    |      | dB   |

#### 2.4.9 Transmit SAT at TXO

| PARAMETER              | र          | TEST CONDITIONS             | MIN    | TYP    | MAX    | UNIT |

|------------------------|------------|-----------------------------|--------|--------|--------|------|

| Output level           | AMPS, TACS | f = 6 kHz, nominal settings | -26.04 | -24.44 | -22.84 | dBV  |

| Distortion             |            | f = 6 kHz, nominal settings |        |        | 0.5    | %    |

| TXSUM mute attenuation |            |                             | -50    | -80    |        | dB   |

|                        |            | 3 kHz                       |        |        | -35    |      |

|                        |            | 4.8 kHz                     |        |        | -25    |      |

|                        |            | 5.1 kHz                     |        |        | -20    |      |

|                        |            | 5.8 kHz                     | -5     |        | 0.5    |      |

| frequency response     |            | 5.94 kHz                    | -0.5   |        | 0.5    | dB   |

|                        |            | 6.06 kHz                    | -0.5   |        | 0.5    |      |

|                        |            | 6.2 kHz                     | -5     |        | 0.5    |      |

|                        |            | 7.2 kHz                     |        |        | -20    |      |

|                        |            |                             |        |        | -35    |      |

#### 2.4.10 SAT TRIM at TXO

| PARAMETER           | TEST CONDITIONS | MIN  | TYP   | MAX | UNIT |

|---------------------|-----------------|------|-------|-----|------|

| Positive trim range | Code FH         | 2    | 2.25  | 2.5 | dB   |

| Negative trim range | Code 0H         | -2.5 | -2.25 | -2  | dB   |

| Step size           |                 | 0.2  | 0.3   | 0.4 | dB   |

| Nominal             | Code 8H         |      | 0     |     | dB   |

## 2.5 Receive Path Specifications, $V_{DD} = 2.7$ V to 3.3 V, $V_I = 171.2$ mVrms

#### 2.5.1 RXAMP

| PARAMETER                         | TEST CONDITIONS                                   | MIN | TYP | MAX | UNIT  |

|-----------------------------------|---------------------------------------------------|-----|-----|-----|-------|

| Unity gain frequency              |                                                   |     | 1.5 |     | MHz   |

| Input current                     |                                                   |     | 1   |     | μΑ    |

| Output load resistance at RXGAIN  |                                                   | 47  |     |     | kΩ    |

| Output load capacitance at RXGAIN |                                                   |     |     | 20  | pF    |

| Input noise                       | $R_{in} = 50 k\Omega$ , psophometrically weighted |     |     | 0.1 | mVrms |

| Open loop gain                    |                                                   |     | 80  |     | dB    |

| Close loop gain                   |                                                   |     | 15  | 26  | dB    |

| Distortion                        | f = 1 kHz                                         |     |     | 0.5 | %     |

#### 2.5.2 RXTRIM, RXGAIN to REC1

| PARAMETER           | TEST CONDITIONS | MIN   | TYP   | MAX   | UNIT |

|---------------------|-----------------|-------|-------|-------|------|

| Positive trim range | Code FH         | 3.2   | 3.7   | 4.2   | dB   |

| Negative trim range | Code 0H         | - 4.8 | - 4.3 | - 3.8 | dB   |

| Step size           |                 | 0.35  | 0.5   | 0.65  | dB   |

| Nominal             | Code 8H         |       | 0     |       | dB   |

#### 2.5.3 EXPANDOR, RXGAIN to REC1

| PARAMETER                                 | TEST CONDITIONS                                                                            | MIN    | TYP  | MAX    | UNIT |

|-------------------------------------------|--------------------------------------------------------------------------------------------|--------|------|--------|------|

| 0dB unity gain level (V <sub>ref</sub> )  | V <sub>DD</sub> = 3 V                                                                      | - 4.23 | - 3  | - 2.24 | dBV  |

| Linearity (relative error with respect to | $V_I = V_{ref}$ to ( $V_{ref}$ – 12.34 dB)                                                 |        |      | ± 1    | dB   |

| V <sub>ref</sub> ), (see Note 6)          | $V_{\text{I}}$ = (V_{\text{ref}} - 12.34 \text{ dB}) to (V_{\text{ref}} - 33.5 \text{ dB}) |        |      | ± 2    | uБ   |

| Attack time (see Note 7)                  |                                                                                            | 2.4    | 3    | 3.6    | ms   |

| Recovery time (see Note 8)                |                                                                                            | 10.8   | 13.5 | 16.2   | ms   |

NOTES: 6. Expandor  $V_{ref}$  (- 3 dBV) = - 12.34 dBV with respect to 2.9 kHz FM deviation.

7. Time taken for the output to settle to 0.57 times the final value with a 6 dB input step.

8. Time taken for the output to settle to 1.5 times the final value with a -6 dB input step.

| PARAM                    | ETER                | TEST CO                                            | NDITIONS                                | MIN  | TYP  | MAX  | UNIT  |

|--------------------------|---------------------|----------------------------------------------------|-----------------------------------------|------|------|------|-------|

| REC1SW mute a            | ttenuation          | RXIN = - 15.3 dBV, f :                             | = 1 kHz                                 | 50   | 80   |      | dB    |

| Distantian at DEC        |                     | RXIN = - 15.3 dBV,                                 | Expandor bypassed                       |      |      | 0.2  | %     |

| Distortion at REC        | 1/REC2              | f = 1 kHz, No load                                 | Expandor enabled                        |      |      | 1    | %     |

| Noise at<br>REC1/REC2    | AMPS, TACS<br>NAMPS | RXIN = RXVMID, exp<br>psophometrically weig        |                                         |      | 0.05 | 3    | mVrms |