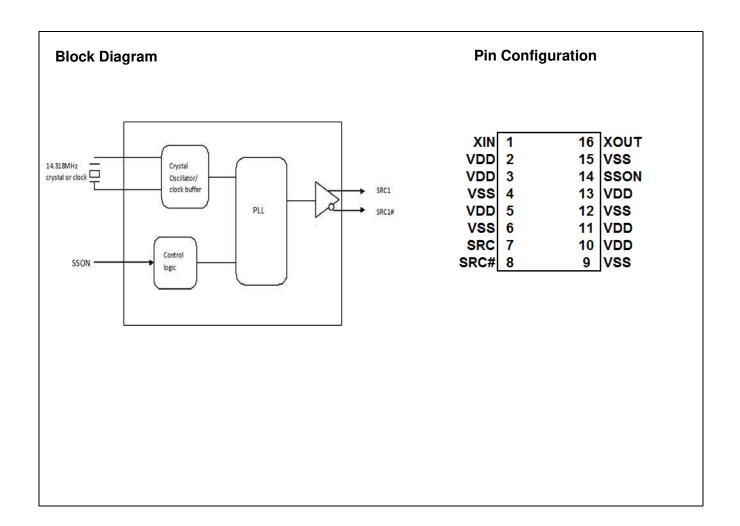

# PCI Express Gen 2 & Gen 3 Clock Generator

#### **Features**

- · Low power PCI Express Gen 2 & Gen 3clock generator

- · One100-MHz differential SRC clocks

- Low power push-pull output buffers (no 50ohm to ground needed)

- · Integrated 33ohm series termination resistors

- Low jitter (<50pS)</li>

- · SSON input for enabling spread spectrum clock

- Triangular Spread Spectrum profile for maximum electromagnetic interference (EMI) reduction

- Input frequency of 14.318MHz

- Industrial Temperature -40°C to 85°C

- 3.3V power supply

- 16-pin TSSOP package

www.silabs.com

#### **Pin Definitions**

| Pin No. | Name  | Type   | Description                                                                                                                                     |

|---------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | XIN   | I      | 14.318 MHz Crystal input.                                                                                                                       |

| 2       | VDD   | PWR    | 3.3V power supply                                                                                                                               |

| 3       | VDD   | PWR    | 3.3V power supply                                                                                                                               |

| 4       | VSS   | GND    | Ground                                                                                                                                          |

| 5       | VDD   | PWR    | 3.3V power supply                                                                                                                               |

| 6       | VSS   | GND    | Ground                                                                                                                                          |

| 7       | SRC1  | O, DIF | 100 MHz Differential serial reference clocks.                                                                                                   |

| 8       | SRC1# | O, DIF | 100 MHz Differential serial reference clocks.                                                                                                   |

| 9       | VSS   | GND    | Ground                                                                                                                                          |

| 10      | VDD   | PWR    | 3.3V power supply                                                                                                                               |

| 11      | VDD   | PWR    | 3.3V power supply                                                                                                                               |

| 12      | VSS   | GND    | Ground                                                                                                                                          |

| 13      | VDD   | PWR    | 3.3V power supply                                                                                                                               |

| 14      | SSON  | I      | 3.3V LVTTL input for enabling spread spectrum clock 0 = Disable, 1 = Enable (-0.5% SS)  Extrenal 10K ohm pull-up or pull-down resistor required |

| 15      | VSS   | GND    | Ground                                                                                                                                          |

| 16      | XOUT  | 0      | 14.318 MHz Crystal output.                                                                                                                      |

**Table 1. Crystal Recommendations**

| Frequency<br>(Fund) | Cut | Loading  | Load Cap | Drive<br>(max.) | Shunt Cap<br>(max.) | Motional (max.) | Tolerance<br>(max.) | Stability (max.) | Aging (max.) |

|---------------------|-----|----------|----------|-----------------|---------------------|-----------------|---------------------|------------------|--------------|

| 14.31818 MHz        | AT  | Parallel | 20 pF    | 0.1 mW          | 5 pF                | 0.016 pF        | 35 ppm              | 30 ppm           | 5 ppm        |

The SL28SRC01 requires a Parallel Resonance Crystal. Substituting a series resonance crystal causes the SL28SRC01 to operate at the wrong frequency and violates the ppm specification. For most applications there is a 300-ppm frequency shift between series and parallel crystals due to incorrect loading.

#### **Crystal Loading**

Crystal loading plays a critical role in achieving low ppm performance. To realize low ppm performance, use the total capacitance the crystal sees to calculate the appropriate capacitive loading (CL).

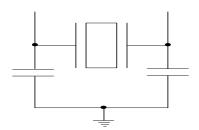

Figure 1 shows a typical crystal configuration using the two trim capacitors. It is important that the trim capacitors are in series with the crystal. It is not true that load capacitors are in parallel with the crystal and are approximately equal to the load capacitance of the crystal.

Figure 1. Crystal Capacitive Clarification

## **Calculating Load Capacitors**

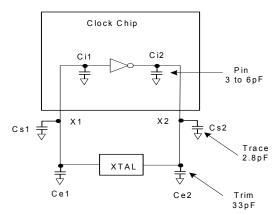

In addition to the standard external trim capacitors, consider the trace capacitance and pin capacitance to calculate the crystal loading correctly. Again, the capacitance on each side is in series with the crystal. The total capacitance on both side is twice the specified crystal load capacitance (CL). Trim

capacitors are calculated to provide equal capacitive loading on both sides.

Figure 2. Crystal Loading Example

Use the following formulas to calculate the trim capacitor values for Ce1 and Ce2.

#### Load Capacitance (each side)

$$Ce = 2 * CL - (Cs + Ci)$$

### Total Capacitance (as seen by the crystal)

CLe =

$$\frac{1}{(\frac{1}{Ce1 + Cs1 + Ci1} + \frac{1}{Ce2 + Cs2 + Ci2})}$$

#### **Absolute Maximum Conditions**

| Parameter                   | Description                                | Condition                   | Min. | Max. | Unit     |

|-----------------------------|--------------------------------------------|-----------------------------|------|------|----------|

| $V_{DD}$                    | Core Supply Voltage                        |                             | _    | 4.6  | V        |

| V <sub>IN</sub>             | Input Voltage                              | Relative to V <sub>SS</sub> | -0.5 | 4.6  | $V_{DC}$ |

| T <sub>S</sub>              | Temperature, Storage                       | Non-functional              | -65  | 150  | °C       |

| T <sub>A (commercial)</sub> | Temperature, Operating Ambient, Commercial | Functional                  | 0    | 85   | °C       |

| T <sub>A (industrial)</sub> | Temperature, Operating Ambient, Industrial | Functional                  | -40  | 85   | °C       |

| T <sub>J</sub>              | Temperature, Junction                      | Functional                  | -    | 150  | °C       |

| Ø <sub>JC</sub>             | Dissipation, Junction to Case              | JEDEC (JESD 51)             | _    | 20   | °C/<br>W |

| Ø <sub>JA</sub>             | Dissipation, Junction to Ambient           | JEDEC (JESD 51)             | -    | 60   | °C/<br>W |

| ESD <sub>HBM</sub>          | ESD Protection (Human Body Model)          | JEDEC (JESD 22 - A114)      | 2000 | -    | V        |

| UL-94                       | Flammability Rating                        | UL (Class)                  | V-   | -0   |          |

## **DC Electrical Specifications**

| Parameter       | Description                      | Condition                                                                | Min.           | Max.                  | Unit |

|-----------------|----------------------------------|--------------------------------------------------------------------------|----------------|-----------------------|------|

| VDD             | 3.3V Operating Voltage           | 3.3 ± 5%                                                                 | 3.135          | 3.465                 | V    |

| V <sub>IH</sub> | 3.3V Input High Voltage          |                                                                          | 2.0            | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub> | 3.3V Input Low Voltage           |                                                                          | $V_{SS} - 0.3$ | 0.8                   | V    |

| I <sub>IH</sub> | Input High Leakage Current       | Except internal pull-down resistors, $0 < V_{IN} < V_{DD}$               | -              | 5                     | μА   |

| I <sub>IL</sub> | Input Low Leakage Current        | Except internal pull-up resistors, 0 < V <sub>IN</sub> < V <sub>DD</sub> | <b>-</b> 5     | _                     | μА   |

| V <sub>OH</sub> | 3.3V Output High Voltage         | I <sub>OH</sub> = -1 mA                                                  | 2.4            | -                     | V    |

| V <sub>OL</sub> | 3.3V Output Low Voltage          | I <sub>OL</sub> = 1 mA                                                   | _              | 0.4                   | V    |

| I <sub>OZ</sub> | High-impedance Output<br>Current |                                                                          | -10            | 10                    | μА   |

## **DC Electrical Specifications**

| Parameter           | Description            | Condition | Min.               | Max.               | Unit |

|---------------------|------------------------|-----------|--------------------|--------------------|------|

| C <sub>IN</sub>     | Input Pin Capacitance  |           | 1.5                | 5                  | pF   |

| C <sub>OUT</sub>    | Output Pin Capacitance |           |                    | 6                  | pF   |

| L <sub>IN</sub>     | Pin Inductance         |           | _                  | 7                  | nΗ   |

| V <sub>XIH</sub>    | Xin High Voltage       |           | 0.7V <sub>DD</sub> | $V_{DD}$           | V    |

| V <sub>XIL</sub>    | Xin Low Voltage        |           | 0                  | 0.3V <sub>DD</sub> | V    |

| I <sub>DD3.3V</sub> | Dynamic Supply Current |           | _                  | 40                 | mA   |

## **AC Electrical Specifications**

| Parameter                       | Description                                | Condition                                                                                                                     | Min.     | Max.     | Unit     |

|---------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|

| Crystal                         |                                            |                                                                                                                               |          |          |          |

| T <sub>DC</sub>                 | XIN Duty Cycle                             | The device operates reliably with input duty cycles up to 30/70 but the REF clock duty cycle will not be within specification | 47.5     | 52.5     | %        |

| T <sub>PERIOD</sub>             | XIN Period                                 | When XIN is driven from an external clock source                                                                              | 69.841   | 71.0     | ns       |

| T <sub>R</sub> /T <sub>F</sub>  | XIN Rise and Fall Times                    | Measured between $0.3V_{DD}$ and $0.7V_{DD}$                                                                                  | -        | 10.0     | ns       |

| T <sub>CCJ</sub>                | XIN Cycle to Cycle Jitter                  | As an average over 1-μs duration                                                                                              | -        | 500      | ps       |

| L <sub>ACC</sub>                | Long-term Accuracy                         | Measured at VDD/2 differential                                                                                                | -        | 250      | ppm      |

| Clock Input                     |                                            |                                                                                                                               |          |          |          |

| T <sub>DC</sub>                 | CLKIN Duty Cycle                           | Measured at VDD/2                                                                                                             | 47       | 53       | %        |

| T <sub>R</sub> /T <sub>F</sub>  | CLKIN Rise and Fall Times                  | Measured between 0.2V <sub>DD</sub> and 0.8V <sub>DD</sub>                                                                    | 0.5      | 4.0      | V/ns     |

| T <sub>CCJ</sub>                | CLKIN Cycle to Cycle Jitter                | Measured at VDD/2                                                                                                             | -        | 250      | ps       |

| T <sub>LTJ</sub>                | CLKIN Long Term Jitter                     | Measured at VDD/2                                                                                                             | -        | 350      | ps       |

| V <sub>IL</sub>                 | Input Low Voltage                          | XIN / CLKIN pin                                                                                                               | _        | 0.8      | V        |

| V <sub>IH</sub>                 | Input High Voltage                         | XIN / CLKIN pin                                                                                                               | 2        | VDD+0.3  | V        |

| I <sub>IL</sub>                 | Input LowCurrent                           | XIN / CLKIN pin, 0 < VIN <0.8                                                                                                 | _        | 20       | uA       |

| I <sub>IH</sub>                 | Input HighCurrent                          | XIN / CLKIN pin, VIN = VDD                                                                                                    | _        | 35       | uA       |

| SRC                             |                                            |                                                                                                                               |          |          | 1        |

| T <sub>DC</sub>                 | SRC Duty Cycle                             | Measured at 0V differential                                                                                                   | 45       | 55       | %        |

| T <sub>PERIOD</sub>             | 100 MHz SRC Period                         | Measured at 0V differential at 0.1s                                                                                           | 9.99900  | 10.0010  | ns       |

| T <sub>PERIODSS</sub>           | 100 MHz SRC Period, SSC                    | Measured at 0V differential at 0.1s                                                                                           | 10.02406 | 10.02607 | ns       |

| T <sub>PERIODAbs</sub>          | 100 MHz SRC Absolute Period                | Measured at 0V differential at 1 clock                                                                                        | 9.87400  | 10.1260  | ns       |

| T <sub>PERIODSSAbs</sub>        | 100 MHz SRC Absolute Period, SSC           | Measured at 0V differential at 1 clock                                                                                        | 9.87406  | 10.1762  | ns       |

| T <sub>CCJ</sub>                | SRC Cycle to Cycle Jitter                  | Measured at 0V differential                                                                                                   | _        | 50       | ps       |

| RMS <sub>GEN1</sub>             | Output PCle* Gen1 REFCLK phase             | BER = 1E-12 (including PLL BW 8 - 16                                                                                          |          |          | <u>'</u> |

| <u>GENT</u>                     | jitter                                     | MHz, ζ = 0.54, Td=10 ns,<br>Ftrk=1.5 MHz)                                                                                     | 0        | 108      | ps       |

| RMS <sub>GEN2</sub>             | Output PCle* Gen2 REFCLK phase jitter      | Includes PLL BW 8 - 16 MHz, Jitter<br>Peaking = 3dB, ζ = 0.54, Td=10 ns),<br>Low Band, F < 1.5MHz                             | 0        | 3.0      | ps       |

| RMS <sub>GEN2</sub>             | Output PCIe* Gen2 REFCLK phase jitter      | Includes PLL BW 8 - 16 MHz, Jitter<br>Peaking = 3dB, ζ = 0.54, Td=10 ns),<br>Low Band, F < 1.5MHz                             | 0        | 3.1      | ps       |

| RMS <sub>GEN3</sub>             | Output phase jitter impact – PCIe*<br>Gen3 | Includes PLL BW 2 - 4 MHz,<br>CDR = 10MHz)                                                                                    | 0        | 1.0      | ps       |

| L <sub>ACC</sub>                | SRC Long Term Accuracy                     | Measured at 0V differential                                                                                                   | _        | 100      | ppm      |

| T <sub>R</sub> / T <sub>F</sub> | SRC Rising/Falling Slew Rate               | Measured differentially from ±150 mV                                                                                          | 2.5      | 8        | V/ns     |

| T <sub>RFM</sub>                | Rise/Fall Matching                         | Measured single-endedly from ±75 mV                                                                                           | _        | 20       | %        |

| V <sub>HIGH</sub>               | Voltage High                               |                                                                                                                               |          | 1.15     | V        |

| V <sub>LOW</sub>                | Voltage Low                                |                                                                                                                               | -0.3     | _        | V        |

| V <sub>OX</sub>                 | Crossing Point Voltage at 0.7V Swing       |                                                                                                                               | 300      | 550      | mV       |

## **AC Electrical Specifications**

| Parameter              | Description                               | Condition | Min. | Max. | Unit |  |  |  |

|------------------------|-------------------------------------------|-----------|------|------|------|--|--|--|

| T <sub>jphasepll</sub> | Phase Jitter<br>(PLL BW 8-16MHz, 5-16MHz) | RMS value |      | 3.1  | pS   |  |  |  |

| ENABLE/DISA            | ENABLE/DISABLE and SET-UP                 |           |      |      |      |  |  |  |

| T <sub>STABLE</sub>    | Clock Stabilization from Power-up         |           | _    | 1.8  | ms   |  |  |  |

| T <sub>SS</sub>        | Stopclock Set-up Time                     |           | 10.0 | _    | ns   |  |  |  |

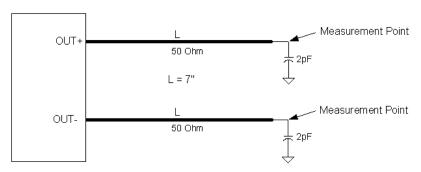

## **Test and Measurement Set-up**

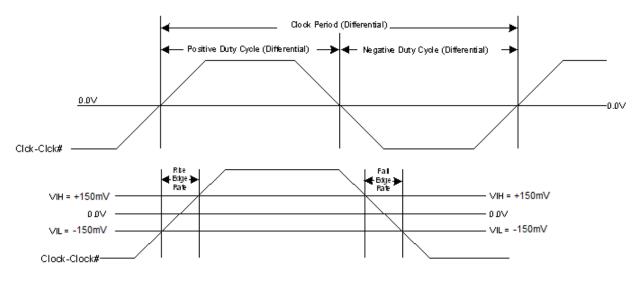

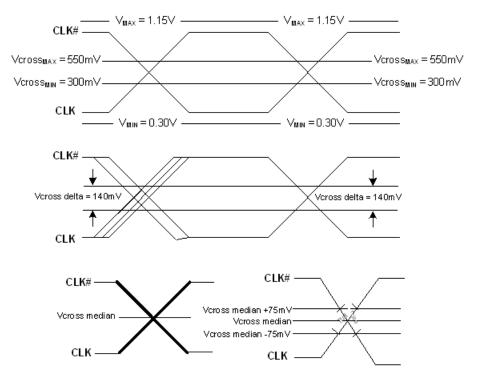

## For SRC Signals

This diagram shows the test load configuration for the differential SRC outputs

Figure 3. 0.7V Differential Load Configuration

Figure 4. Differential Measurement for Differential Output Signals (for AC Parameters Measurement)

Figure 5. Single-ended Measurement for Differential Output Signals (for AC Parameters Measurement)

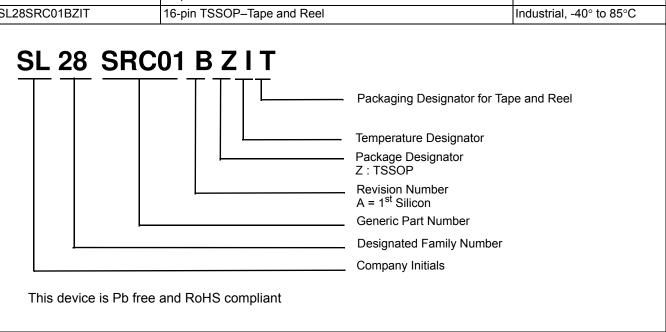

## **Ordering Information**

| Part Number   | Package Type               | Product Flow             |

|---------------|----------------------------|--------------------------|

| Lead-free     |                            |                          |

| SL28SRC01BZI  | 16-pin TSSOP               | Industrial, -40° to 85°C |

| SL28SRC01BZIT | 16-pin TSSOP–Tape and Reel | Industrial, -40° to 85°C |

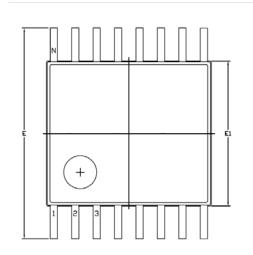

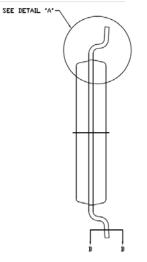

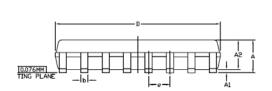

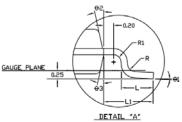

## **Package Diagrams**

## 16-pin TSSOP

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. DIMENSION 'D' DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR GATE BURRS, MOLD FLASH,

PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED

0.15 PER SIDE.

- 3. DIMENSION "E!" DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION. SHALL NOT EXCEED 0.25 PER SIDE.

4. "N" IS THE NUMBER OF TERMINAL POSITIONS.

- 5. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY

- 6. REFERENCE DRAWING JEDEC MO-153, VARIATION AB.

| SYMBOL         | DIMEN | NDIS   | IN MM | DIMEN     | ISION I | N INCH |

|----------------|-------|--------|-------|-----------|---------|--------|

| 3 IMBUL        | MIN.  | NOM.   | MAX.  | MIN.      | NDM.    | MAX.   |

| Α              |       |        | 1.20  |           |         | .047   |

| A1             | 0.05  |        | 0.15  | .002      |         | .006   |

| A2             | 0.80  | 0.90   | 1.05  | .031      | .035    | .041   |

| b              | 0.19  |        | 0.30  | .007      |         | .012   |

| b1             | 0.19  | 0.22   | 0.25  | .007      | .009    | .010   |

| С              | 0,09  |        | 0.20  | .004      |         | .008   |

| c1             | 0.09  |        | 0.16  | .004      |         | .006   |

| D              | 4.90  | 5.00   | 5.10  | .193      | .197    | .200   |

| e              | 0.    | 65 BS  | C.    | .026 BSC. |         |        |

| Ε              | 6     | 40 BS  | c.    | .252 BSC. |         |        |

| E1             | 4,30  | 4,40   | 4,50  | .169      | .173    | .177   |

| L              | 0.50  | 0.60   | 0.75  | .020      | .024    | .030   |

| L1             | 1.    | 00 REF | F.    | .0        | 39 REI  | F.     |

| R              | 0,09  |        |       | ,004      |         |        |

| R1             | 0.09  |        |       | .004      |         |        |

| <del>0</del> 1 | 0     |        | 8     | 0         |         | 8      |

| 92             | 1     | 2 REF  | ,     | 1         | 2 REF   |        |

| <del>0</del> 3 | 1     | 12 PFF |       |           | 2 REE   |        |

## **Document History Page**

| REV. | ECR# | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                          |  |

|------|------|------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0  |      | 09/13/09   | JMA                | New datasheet                                                                                                                                                                  |  |

| 1.1  |      | 11/06/09   | JMA                | Updated Figure 4                                                                                                                                                               |  |

| AA   | 1454 | 04/25/10   | JMA                | Updated pin 6 definition on page 2     Updated revision to be ISO compliant     Updated package information     Added commercial temperature grade     Added clock in features |  |

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are not designed or authorized for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701