### MSL2010

# Single String Linear constant current LED Controller with Integrated DC/DC Boost Controller

#### **Features**

- Integrated Boost Controller

- Drives external N-Ch MOSFETS

- Over-Temperature Fault Detection

- 8-bit DAC for peak current control

- PWM Input for Dimming Duty Cycle

- Linear current control for ripple-free LED current regulation

- 8-bit Efficiency Optimizer Minimizes Power Use

- ± 3% Current Accuracy

- I<sup>2</sup>C Serial Interface (use Optional)

- 32 Bytes Free RAM, 32 Bytes Free EEPROM

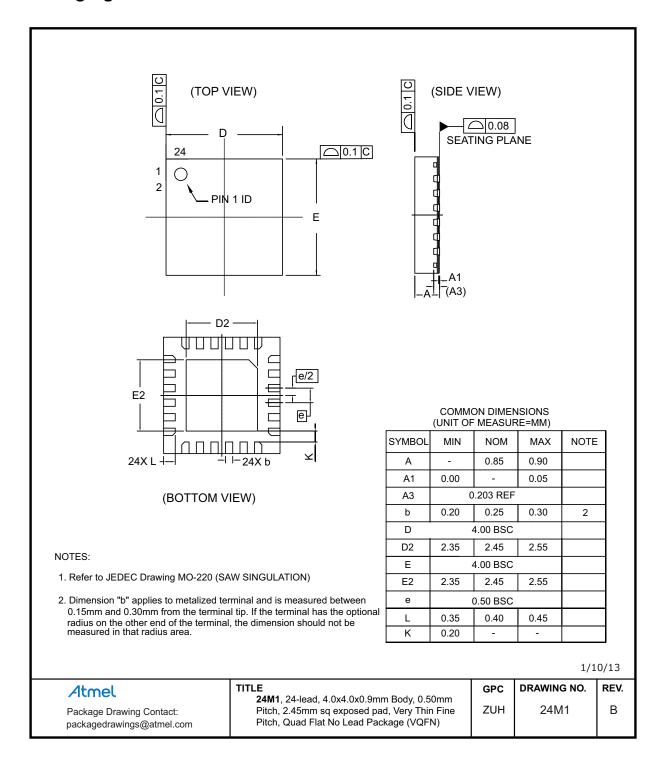

- 24-Pin QFN Package

- -40°C To +105°C Operating Temperature Range

### **Typical Applications**

- General and Architectural Lamps

- Down Lights and Recessed Lights

- PAR Lamps

- DC Input LED lamps

### 1. Introduction

The MSL2010 LED string driver features a constant off-time Boost Controller and provides very accurate, no ripple, linear controlled string current. The Atmel patent-pending Efficiency Optimizer (EO) controls the switch-mode converter output, optimizing the output voltage to achieve maximum power efficiency. Both the switching and linear controllers drive external MOSFETs to provide flexibility over a wide range of power levels (LED currents and voltages) and extremely low LED ripple current.

The MSL2010 operates from a 9.5V to 15V power supply. The Boost controller voltage regulation loop uses a constant off-time control algorithm to achieve stable control with good transient behavior. For flexibility of design, off-time is set with an external resistor. External loop compensation offers additional flexibility for the Boost Controller.

An I<sup>2</sup>C interface provides access to the control registers, and to 32 bytes of RAM. Integrated non-volatile EEPROM memory, also accessed through the I<sup>2</sup>C serial interface, allows configuration at final test in the case that the factory default settings must be modified.

The MSL2010 is available in the space-saving 24-pin 4x4mm QFN package and operates over the extended -40°C to 105°C operating range.

## 2. Ordering Information

| Ordering code | Description                                 | Package <sup>(1)</sup> |

|---------------|---------------------------------------------|------------------------|

| MSL2010       | One String LED Driver with DC-DC Controller | 4 x 4mm 24-pin QFN     |

Note: 1. Lead-Free, Halogen-Free, RoHS Compliant Package

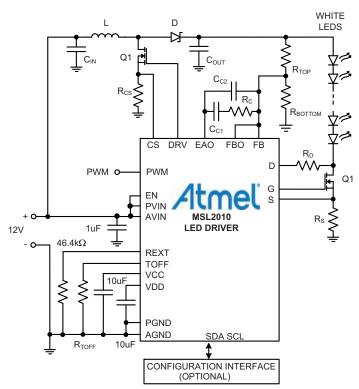

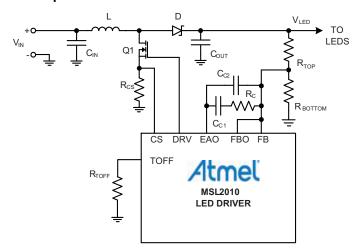

## 3. Application Circuit

## 4. Absolute Maximum Ratings

| Voltage | with respect to AGND                      |                   |

|---------|-------------------------------------------|-------------------|

|         | AVIN, PVIN, EN                            | -0.3V to +16.5V   |

|         | VCC, PWM, FLTB, SDA, SCL, TOFF, REXT, FBO | -0.3V to +5.5V    |

|         | VDD                                       | -0.3V to +2.75V   |

|         | CS, S                                     | -0.3V to VDD+0.3V |

|         | D                                         | -0.3V to +22V     |

|         | G, DRV                                    | -0.3V to VIN+0.3V |

|         | PGND, AGND                                | -0.3V to +0.3V    |

| Current | (into pin)                   |        |

|---------|------------------------------|--------|

|         | AVIN, PVIN, DRV, G (average) | 100mA  |

|         | PVIN (peak, ≤1% duty)        | 1A     |

|         | DRV, G (peak, ≤1% duty)      | ±1A    |

|         | PGND (peak, ≤1% duty)        | -1A    |

|         | AGND, PGND (average)         | -100mA |

|         | All other pins               | ±10mA  |

| Continu | ous Power Dissipation at 70°C                             |        |

|---------|-----------------------------------------------------------|--------|

|         | 24-Pin 4mm x 4mm VQFN (derate 21.8mW/°C above TA = +70°C) | 1200mW |

| Ambient Operating Temperature Range | -40°C to +105°C |

|-------------------------------------|-----------------|

| Junction Temperature                | +125°C          |

| Storage Temperature Range           | -65°C to +125°C |

| Lead Soldering Temperature, 10s     | +300°C          |

## 5. Electrical Characteristics

AVIN = PVIN = 12V, -40°C  $\leq$ T<sub>A</sub>  $\leq$  105°C, Typical Operating Circuit, unless otherwise noted. Typical values at T<sub>A</sub> = +25°C.

Table 5-1. DC electrical characteristics

| Parameter                                                     | Conditions                                                            | Min.                 | Тур. | Max.                 | Unit   |

|---------------------------------------------------------------|-----------------------------------------------------------------------|----------------------|------|----------------------|--------|

| AVIN, PVIN Operating Supply Voltage                           |                                                                       | 9.5                  | 12   | 15                   | V      |

| AVIN Operating Supply Current                                 | LEDs on at PWM = 100%, serial interface idle                          |                      | 10   |                      | mA     |

| AVIN Disable Supply Current                                   | V <sub>EN</sub> = 0, all digital inputs = 0                           |                      |      | 5                    | μA     |

| VCC Regulation Voltage                                        | I <sub>VCC</sub> = 10mApeak <sup>(1)</sup>                            | 4.5                  | 5    | 5.5                  | V      |

| VDD Regulation Voltage                                        | I <sub>VDD</sub> = 10mApeak <sup>(1)</sup>                            | 2.25                 | 2.5  | 2.75                 | V      |

| PWM, SCL, SDA Input High Voltage                              |                                                                       | 0.7*V <sub>VDD</sub> |      |                      | V      |

| PWM, SCL, SDA Input Low Voltage                               |                                                                       |                      |      | 0.3*V <sub>VDD</sub> | V      |

| EN Input High Voltage                                         |                                                                       | 2                    |      |                      | V      |

| EN Input Low Voltage                                          |                                                                       |                      |      | 0.5                  | V      |

| EN Input Hysteresis                                           |                                                                       |                      | 100  |                      | mV     |

| SDA, FLTB Output Low Voltage                                  | Sinking 6mA                                                           |                      |      | 0.3                  | V      |

| SCL, SDA, PWM, FLTB leakage current                           |                                                                       | -5                   |      | 5                    | μА     |

| S Current Sense Regulation Voltage                            | MREF = 0x64                                                           | 194                  | 200  | 206                  | mV     |

| S Current Sense Regulation Voltage<br>Accuracy                | Main string at 100% duty cycle,<br>T <sub>A</sub> = 25°C, MREF = 0x64 | -3                   |      | +3                   | %      |

| S Current Sense Regulation Voltage<br>Temperature Coefficient |                                                                       |                      | -220 |                      | ppm/°C |

| G Maximum Output Voltage                                      |                                                                       | AVIN – 3.5           |      | AVIN – 2.0           | V      |

| D Regulation Threshold                                        | EOCTRL = 0xE5                                                         | 0.9                  | 1    | 1.1                  | V      |

| CS Current Sense Regulation Voltage                           | CAREF = 0x64                                                          |                      | 200  |                      | mV     |

| EA Unity Gain Bandwidth                                       |                                                                       |                      | 7    |                      | MHz    |

| EA Open Loop Gain                                             |                                                                       |                      | 100  |                      | dB     |

| DRV Impedance                                                 | V <sub>DRV</sub> = 12V, I <sub>DRV</sub> = 20mA                       |                      | 5.6  | 9                    | Ω      |

| DRV Impedance                                                 | $V_{DRV} = 0V$ , $I_{DRV} = -20$ mA                                   |                      | 5.6  | 9                    | Ω      |

| FBO Full Scale Current                                        |                                                                       | 170                  | 255  | 340                  | μΑ     |

| FBO LSB Current                                               |                                                                       |                      | 1.0  |                      | μΑ     |

| Thermal Shutdown Temperature                                  | Temperature rising                                                    |                      | 133  |                      | °C     |

| Thermal Shutdown Hysteresis                                   |                                                                       |                      | 15   |                      | °C     |

Note: 1. Additional decoupling may be required when pulling current from VCC and/or VDD in noisy environments

Table 5-2. AC electrical characteristics

| Parameter                   | Conditions               | Min. | Тур. | Max.   | Unit |

|-----------------------------|--------------------------|------|------|--------|------|

| DRV t <sub>OFF</sub> timing | $R_{TOFF} = 46.5k\Omega$ |      | 0.5  |        | μS   |

| PWM Input Frequency         | (1)                      | 60   |      | 10,000 | Hz   |

| PWM Duty Cycle              |                          | 1    |      | 100    | %    |

| PWM Duty Cycle Resolution   |                          |      | 0.4  |        | %    |

Note:

1. 2µs minimum on time, 0% duty cycle is supported. PWM between 0% and 1% not guaranteed

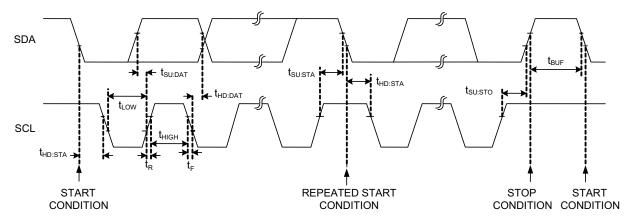

Table 5-3. I<sup>2</sup>C switching characteristics

| Parameter                                   | Symbol               | Conditions | Min. | Тур. | Max.  | Unit |

|---------------------------------------------|----------------------|------------|------|------|-------|------|

| SCL Clock Frequency                         |                      | (1)        | 0.05 |      | 1,000 | kHz  |

| STOP to START Condition Bus Free Time       | t <sub>BUF</sub>     |            | 0.5  |      |       | μs   |

| Repeated START condition Hold Time          | t <sub>HD:STA</sub>  |            | 0.26 |      |       | μs   |

| Repeated START condition Setup Time         | t <sub>SU:STA</sub>  |            | 0.26 |      |       | μs   |

| STOP Condition Setup Time                   | t <sub>SU:STOP</sub> |            | 0.26 |      |       | μs   |

| SDA Data Hold Time                          | t <sub>HD:DAT</sub>  |            | 5    |      |       | ns   |

| SDA Data Valid Acknowledge Time             |                      | (2)        | 0.05 |      | 0.55  | μs   |

| SDA Data Valid Time                         |                      | (3)        | 0.05 |      | 0.55  | μs   |

| SDA Data Set-Up Time                        | t <sub>SU:DAT</sub>  |            | 100  |      |       | ns   |

| SCL Clock Low Period                        | t <sub>LOW</sub>     |            | 0.5  |      |       | μs   |

| SCL Clock High Period                       | t <sub>HIGH</sub>    |            | 0.26 |      |       | μs   |

| SDA, SCL Fall Time                          | t <sub>F</sub>       | (4), (5)   |      |      | 120   | ns   |

| SDA, SCL Rise Time                          | t <sub>R</sub>       |            |      |      | 120   | ns   |

| SDA, SCL Input Suppression Filter<br>Period |                      | (6)        |      | 50   |       | ns   |

| Bus Timeout                                 | t <sub>TIMEOUT</sub> | (1)        |      | 25   |       | ms   |

Notes:

- 1. Minimum SCL clock frequency is limited by the bus timeout feature, which resets the serial bus interface when either SDA or SCL is held low for t<sub>TIMEOUT</sub>.

- 2. SDA Data Valid Acknowledge Time is SCL LOW to SDA (out) LOW acknowledge time.

- 3. SDA Data Valid Time is minimum SDA output data-valid time following SCL LOW transition.

- 4. A master device must internally provide an SDA hold time of at least 300ns to ensure an SCL low state.

- 5. The maximum SDA and SCL rise times is 300ns. The maximum SDA fall time is 250ns. This allows series protection resistors to be connected between SDA and SCL inputs and the SDA/SCL bus lines without exceeding the maximum allowable rise time.

- 6. Includes input filters on SDA and SCL that suppress noise less than 50ns.

## 6. Typical Operating Characteristics

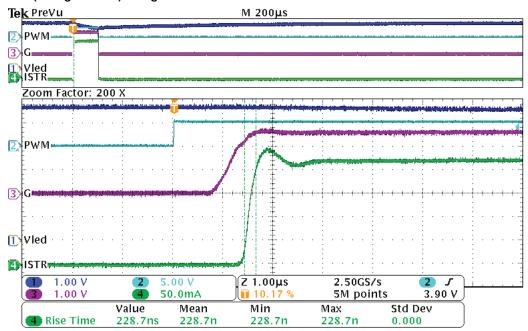

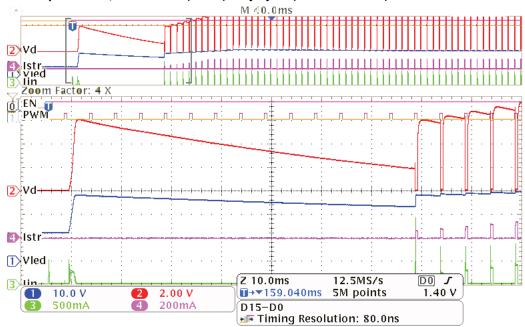

Figure 6-1. Istr (String Current) rising.

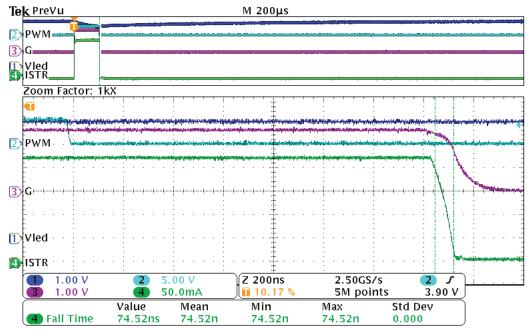

Figure 6-2. Istr (String Current) falling.

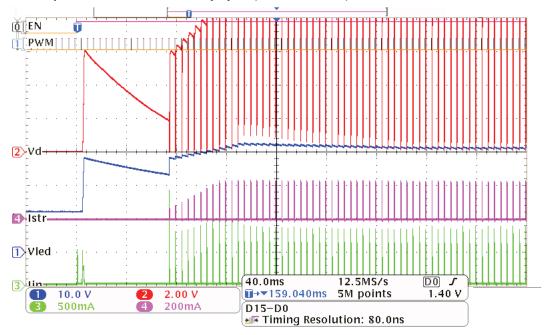

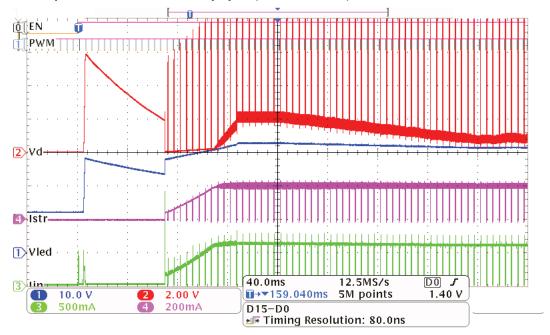

Figure 6-3. Start-up behavior, PWM = 10% duty cycle (Test conditions).

Figure 6-4. Start-up behavior, PWM = 10% (Zoom) duty cycle (Test conditions).

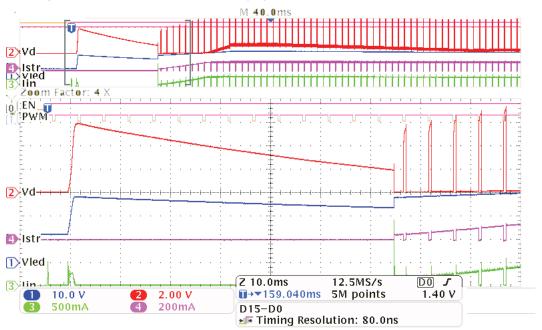

Figure 6-5. Start-up behavior, PWM = 90% duty cycle (Test conditions).

Figure 6-6. Start-up behavior,, PWM = 90%(zoom) duty cycle (Test conditions).

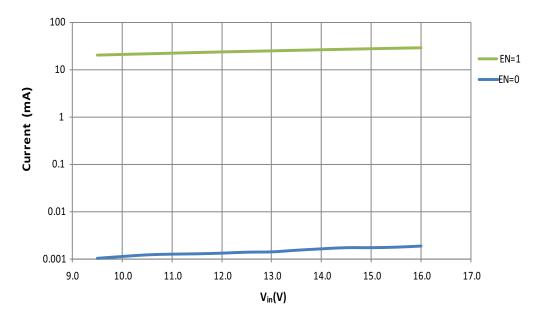

Figure 6-7. Operating current vs. input voltage

Figure 6-8.  $V_{CC}$  and  $V_{DD}$  regulation

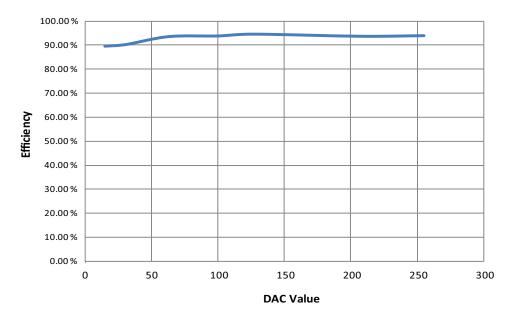

Figure 6-9. Efficiency vs DAC value

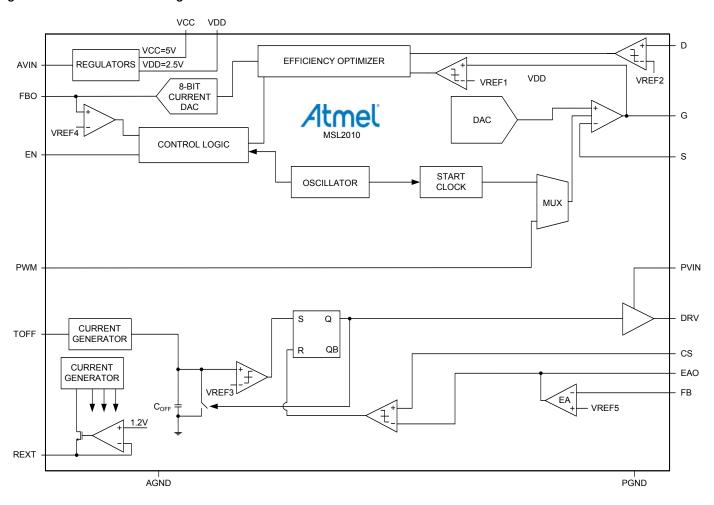

## 7. Block Diagram

Figure 7-1. MSL2010 block diagram

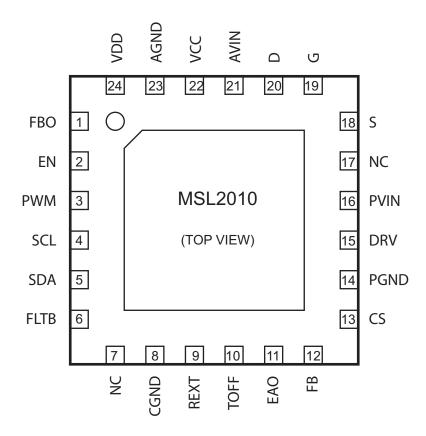

## 8. Pinout and Pin Description

## 8.1 Pinout MSL2010

## 8.2 Pin Descriptions

| Name | Pin   | Description                                                                                                                                                                           |

|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FBO  | 1     | Feedback Output Feedback output from Efficiency Optimizer. Connect FBO to the LED power supply regulation feedback node to control V <sub>LED</sub> . When unused connect FBO to VCC. |

| EN   | 2     | Enable Input (Active High) Drive EN high to turn on the MSL2010, drive EN low to turn it off. For automatic start-up connect EN to AVIN.                                              |

| PWM  | 3     | PWM Dimming Input Drive PWM with a pulse-width modulated signal to control LED brightness. See "PWM and LED Brightness" on page 17 for details.                                       |

| SCL  | 4     | Serial Clock Input SCL is the I <sup>2</sup> C serial interface clock input. See "I <sup>2</sup> C Serial Interface" on page 21 details.                                              |

| SDA  | 5     | Serial Data Input/Output SDA is the I <sup>2</sup> C serial interface data I/O. See "I <sup>2</sup> C Serial Interface" on page 21 details.                                           |

| FLTB | 6     | Fault Output  Open Collector FLTB pulls low when an overtemperature is detected (die temperature≥147°C). FLTB releases when the die temperature falls below 127°C.                    |

| NC   | 7, 17 | No Internal Connection                                                                                                                                                                |

| Name | Pin | Description                                                                                                                                                                                                                                                                                                                 |

|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CGND | 8   | Connect to Ground                                                                                                                                                                                                                                                                                                           |

| Canb |     | Connect CGND to AGND                                                                                                                                                                                                                                                                                                        |

| REXT | 9   | External Resistor Connect a $46.4k\Omega$ , 1% resistor from REXT to AGND.                                                                                                                                                                                                                                                  |

| TOFF | 10  | Off-Time Set Input A resistor from TOFF to AGND controls the constant off time for the Boost converter, where $R_{TOFF} = t_{OFF} * (90.9 \times 10^9)$ , with $t_{OFF}$ in seconds and $R_{TOFF}$ in Ohms. For example, an off time of $4.4 \mu s$ results in a resistor value of $402 k\Omega$ (to the nearest 1% value). |

|      |     | Error Amp Out                                                                                                                                                                                                                                                                                                               |

| EAO  | 11  | Output of the switch-mode error amplifier. Connect the compensation network between EAO and FB.                                                                                                                                                                                                                             |

| FB   | 12  | Feedback Input for Boost Regulator Connect FB to the middle node of the Boost regulator voltage setting resistor divider. Also, connect FBO to FB to allow the MSL2010 to optimize V <sub>LED</sub> .                                                                                                                       |

| CS   | 13  | Current Sense Input for the Boost Converter Connect CS to the external current sense resistor of the Boost regulator. The current sense threshold is 200mV. For more information see the section "Boost Reference Voltage register (CSREF, 0x21)" on page 20.                                                               |

|      |     | Power Ground                                                                                                                                                                                                                                                                                                                |

| PGND | 14  | PGND is the ground connection for the FET gate drivers. Connect PGND to AGDN close to the MSL2010.                                                                                                                                                                                                                          |

| DRV  | 15  | Gate Drive for Boost Regulator MOSFET Connect DRV to the gate of the Boost regulator power MOSFET.                                                                                                                                                                                                                          |

| PVIN | 16  | Power Voltage Input PVIN powers DRV, the Boost regulator FET gate driver. Connect PVIN to a power supply of 10V to 15V. Bypass PVIN to PGND with a 1.0μF or greater capacitor.                                                                                                                                              |

| S    | 18  | Source Sense Input for LED String Drive MOSFET Connect S to the source of the LED string drive external MOSFET, and to the current sense resistor for the LED string. The current sense threshold is 200mV. For more information see the section "LED String Reference Voltage register (SREF, 0x20)" on page 20.           |

| G    | 19  | Gate Output for LED String MOSFET Connect G to the gate of the LED string drive external MOSFET. Minimum on-time is 2µs.                                                                                                                                                                                                    |

| D    | 20  | Drain Output for LED String MOSFET Connect D to the drain of the LED string drive external MOSFET.                                                                                                                                                                                                                          |

| AVIN | 21  | Analog Voltage Input (12V) AVIN is the power input to the MSL2010. Bypass AVIN to AGND with a 1.0µF or greater capacitor placed close to AVIN.                                                                                                                                                                              |

| vcc  | 22  | 5V Internal Voltage Connect 10μF bypass capacitor from VCC to AGND.                                                                                                                                                                                                                                                         |

| AGND | 23  | Analog Ground Connect AGND to system ground.                                                                                                                                                                                                                                                                                |

| VDD  | 24  | 2.5V Internal Voltage Connect 10uF bypass capacitor from VDD to AGND.                                                                                                                                                                                                                                                       |

| EP   | EP  | Exposed Pad  EP is the main thermal path for heat to escape the die. Connect EP to a large copper plane connected to PGND and AGND.                                                                                                                                                                                         |

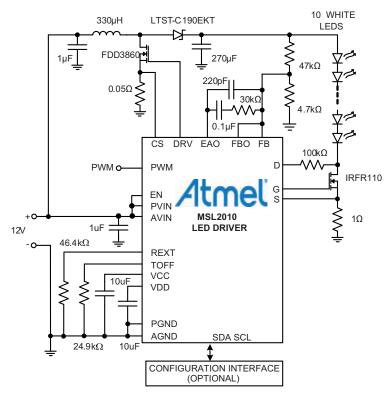

## 9. Typical Application Circuit

MSL2010 Boost Switcher and Linear Driver, Driving 10 White LEDs.

Figure 9-1. Typical application circuit

## 10. Detailed Description

The MSL2010 drives one LED string, and includes a Boost Regulator Controller to generate  $V_{LED}$ , the string voltage, from a low voltage input. An Efficiency Optimizer (EO) algorithm regulates  $V_{LED}$  to the minimum required to keep the LEDs in current regulation, minimizing power loss across the external string drive MOSFET. A PWM input accepts 1% to 100% duty cycle signal of 60Hz to 10kHz. The LED PWM output dimming duty cycle and frequency equal the PWM input duty cycle and frequency, with a 2µs minimum on time. LEDs are driven by a linear driver.

#### 11. Fault Conditions

Over Temperature Protection shuts down the device when the die temperature is above 133°C. The device turns back on when the die temperature falls below 118°C, as if EN is taken from low to high.

## 12. Applications Information

#### 12.1 Turn-On Sequence

When EN is taken high, the MSL2010 waits for 6ms, then optimizes  $V_{LED}$ , the LED string voltage, which typically takes about 250ms, then begins to drive the LEDs based on the PWM input.

#### 12.2 The Boost Regulator

MSL2010 includes a Constant Off-Time DC/DC Boost Controller to generate V<sub>LED</sub>, the voltage for the LED string. The Boost components are shown in Figure 12-1 on page 15, and include a voltage setting resistor divider, a MOSFET, a Schottky diode, a resistor to set the Off-Time, an Inductor, a current sense resistor, a Drain resistor, a few capacitors and a compensation network. The following sections discuss selecting these components.

Figure 12-1. Boost Regulator Components

#### 12.2.1 Setting the Boost Output Voltage, V<sub>LED</sub>

A resistor divider sets the nominal Boost output voltage, V<sub>LED</sub>. Select the two feedback resistors by first determining the minimum output voltage using:

$$V_{OUT(MIN)} \le (V_{fMIN}) * (N) + 0.2 \text{ V},$$

where  $V_{fMIN}$  is the minimum LED forward voltage at the expected LED current, N is the number of LEDs in the string, and 0.2V is the minimum overhead required for the current sense resistor and the FET. Then determine the maximum output voltage using:

$$V_{OUT(MAX)} = (V_{fMAX}) * (N) + 1.2 V,$$

where  $V_{fMAX}$  is the maximum LED forward voltage at the expected LED current, N is the number of LEDs in the string, and 1.2V is the maximum overhead required for the current sense resistor and the FET.

Determine the value for the upper voltage setting resistor using:

$$R_{TOP} = \frac{V_{OUT(MAX)} - V_{OUT(MIN)}}{340 \times 10^{-6}} \Omega,$$

where  $340\mu A$  is the guaranteed maximum FBO current from the "Electrical Characteristics" on page 4. Determine the lower resistor using:

$$R_{BOTTOM} = R_{TOP} * \frac{2.5}{V_{OUT(MIN)} - 2.5} \Omega,$$

where 2.5V is  $V_{FB}$ , the feedback regulation voltage of the FB input. The Efficiency Optimizer (EO) output, FBO, connects to FB and pulls current from the node to force the converter's output voltage up to the proper level to keep the LEDs in current regulation with the minimum power loss.

#### 12.2.2 The Boost MOSFET and Schottky Diode

Output DRV drives the gate of an external N-Channel MOSFET at up to  $V_{PVIN}$  – 1.5V. Select a MOSFET with a maximum drain-source voltage of at least 1V above  $V_{OUT(MAX)}$  (from above), a low gate charge and low  $R_{DS(ON)}$ . Use a Schottky diode with a maximum reverse voltage of at least  $V_{OUT(MAX)}$ .

#### 12.2.3 The Off-Time Resistor, R<sub>TOFF</sub>

The Boost driver uses a constant off-time algorithm. The MOSFET turns off when  $V_{CS}$  = 0.2V (Figure 12-1 on page 15). Control off-time with external resistor  $R_{TOFF}$  using:

$$R_{TOFF} = t_{OFF} * (90.9 \times 10^9) \Omega$$

where  $t_{OFF}$  is in seconds. For example, an off-time of  $4.4\mu s$  results in a resistor value of  $402k\Omega$  (to the nearest 1% value).

#### 12.2.4 Setting the Inductor Current with R<sub>CS</sub>

The Boost inductor peak current regulates by way of the voltage at CS, the Boost MOSFET source resistor connection. Connect the current sense resistor  $R_{CS}$  from the MOSFET source to ground. The default feedback voltage for CS is 0.2V. Choose the current sense resistor using:

$$R_{CS} = \frac{0.2}{I_L} \Omega,$$

where  $I_L$  is the inductor peak current. For example, for 350mA  $I_L$ , use  $R_{CS}$  of 0.56 Ohms. The 0.2V in this equation is set in the Current Sense Reference Voltage (CSREF) register 0x21. The default value for CSREF is 0x64, which sets the feedback voltage to 0.2V. For information about CSREF see "Boost Reference Voltage register (CSREF, 0x21)" on page 20.

#### 12.2.5 Sizing The Inductor, L

Current increases through the inductor until the voltage at CS reaches 0.2V. The MOSFET then turns off for the off-time programmed by  $R_{\text{TOFF}}$  (above). Estimate the inductor value using:

$$L = \frac{v(t)}{\left(\frac{di(t)}{dt}\right)} H,$$

where v(t) = the acceptable ripple voltage of  $V_{LED}$ , di(t) = acceptable peak to peak inductor ripple current, and dt = the off-time set by  $R_{TOFF}$ .

For example:

With an inductor ripple voltage of 0.5% of  $V_{OUT(MAX)}$  (from above), v(t) = 35.2 \* (0.005) = 176 mV.

With an average load current of 350mA and an inductor ripple current of 4%, di(t) = 0.35 \* 0.04 = 0.014A.

And, with a t<sub>OFF</sub> of 4.4µs, then:

$$L = \frac{0.176}{\left(0.014 / \frac{4.4 \times 10^{-6}}{1.0014 \times 10^{-6}}\right)} = 55 \,\mu\text{H} \, .$$

Assure that the inductor saturation current rating is greater than  $I_L$ , the peak inductor current from the  $R_{CS}$  equation above.

#### 12.2.6 The Drain Resistor, R<sub>D</sub>

The drain resistor,  $R_D$  in Figure 12-1 on page 15, connects the MSL2010 to the Drain of the LED string external MOSFET. Use a  $100k\Omega$  for  $R_D$ .

#### 12.2.7 The Input and Output Capacitors

The input and output capacitors carry the high frequency current of the Boost regulator switching. The input capacitor prevents this high frequency current from travelling back to the input voltage source, reducing conducted and radiated noise. The output capacitor prevents high frequency current to the load, in this case the LEDs, and also prevents conducted and radiated noise. The output capacitors also have a large effect on the Boost regulator loop stability and transient response, and so are critical to optimal Boost regulator operation. Use capacitors that keep their rated values at their expected operating voltages. The "Typical Application Circuit" on page 14 shows recommended values for these capacitors.

#### 12.2.8 The Compensation Network

The compensation components,  $R_C$ ,  $C_{C1}$  and  $C_{C2}$  in Figure 12-1 on page 15, effectively dampen the oscillation-producing high frequency response of the Boost regulator error amplifier. The "Typical Application Circuit" on page 14 shows recommended values for these capacitors.

#### 12.3 The LED string

#### 12.3.1 Selecting the LED String MOSFET

The LED string MOSFET sinks the LED current to ground through current sense resistor  $R_S$ . Output G drives the gate of the MOSFET with at up to at least  $V_{AVIN}$  – 1.5V. Select a FET with a maximum drain-source voltage of at least  $V_{OUT(MAX)}$  (from above), and a low  $R_{DS(ON)}$ .

#### 12.3.2 Setting LED String On-Current with R<sub>S</sub>

The LED string on-current regulates by monitoring the voltage at S, the MOSFET source resistor connection. Connect the current sense resistor  $R_S$  from the MOSFET source to ground. The default feedback voltage for S is 0.2V. Choose the string current sense resistor  $R_S$  using:

$$R_S = \frac{0.2}{I_{LED}} \Omega,$$

where I<sub>LED</sub> is the LED string regulation current. The LED String Reference Voltage (SREF), register 0x20, sets the 0.2V feedback voltage, at 2mV per LSB. For more information about SREF see the "LED String Reference Voltage register (SREF, 0x20)" on page 20.

#### 12.3.3 PWM and LED Brightness

MSL2010 uses the input signal at PWM to directly control the duty cycle (brightness) and frequency of the LED string driver output G. The PWM input accepts a signal of 60Hz to 10kHz, 1% to 100% duty cycle; output G operates with a minimum on time of 2µs.

## 13. Control Registers

Table 13-1. MSL2010 Register Map (Do not change unspecified registers or bits).

| Addro                        | ac and       |                                                              | Default |                                |               |           | Bit fu                | nctions    |       |         |    |

|------------------------------|--------------|--------------------------------------------------------------|---------|--------------------------------|---------------|-----------|-----------------------|------------|-------|---------|----|

| Address and<br>Register name |              | Function                                                     | value   | D7                             | D6            | D5        | D4                    | D3         | D2    | D1      | D0 |

|                              |              |                                                              |         | Control a                      | and Monitor I | Registers |                       | •          |       | ,       |    |

| 0x00                         | through 0x1F | RAM                                                          | 0xXX    |                                | Free RAM      |           |                       |            |       |         |    |

| 0x20                         | SREF         | LED String<br>MOSFET Source<br>Feedback<br>Reference Voltage | 0x64    | S <sub>REF</sub> = 2mV per LSB |               |           |                       |            |       |         |    |

| 0x21                         | CSREF        | Boost Current<br>Sense Reference<br>Feedback Voltage         | 0x64    |                                |               |           | CS <sub>REF</sub> = 2 | mV per LSB |       |         |    |

| 0x40                         | EOCTRL       | Efficiency<br>Optimizer                                      | 0xE5    |                                | Reserv        | /ed[4:0]  |                       |            | DThre | sh[3:0] |    |

| 0x60                         | E2ADDR       | EEPROM Address                                               | 0x00    | - EEPROM Address Pointer       |               |           |                       |            |       |         |    |

| 0x61                         | E2CTRL       | EEPROM Control                                               | 0x00    | RWCTRL[2:0]                    |               |           |                       |            |       |         |    |

|                              |              |                                                              |         | Unused a                       | nd Reserved   | Registers |                       |            |       |         |    |

### 13.1 EEPROM and Power-Up Defaults

An on-chip EEPROM holds all the default register values (Table 13-1 on page 18). At power-up the data in the EEPROM automatically copy directly to control registers 0x00 thru 0x51, setting up the device for operation.

Any changes made to registers 0x00 thru 0x51 after power-up are not reflected in the EEPROM and are lost when power is removed from the device, or when the enable input EN is forced low. If a different power-up condition is desired program the values into the EEPROM via the serial interface as explained in the next section, or contact the factory to inquire about ordering a customized power-up setting.

#### 13.2 EEPROM Address and Control/Status Registers

The EEPROM can be visualized as an image of the control registers from 0x00 thru 0x69. Change an EEPROM register value by writing the new value into the associated control register, and then instructing the device to program that value into the EEPROM. Two control registers facilitate this process, the EEPROM address register E2ADDR (0x60), and the EEPROM control register E2CTRL (0x61). Into E2ADDR write the location of the data that is to be programmed into the EEPROM, and write 0x03 to E2CTRL to command the device to program that data into the EEPROM. Programming the EEPROM takes a finite amount of time; after sending a command to E2CTRL wait 5ms, then end the write cycle by writing 0x00 to E2CTRL.

**Example:** Change the string current feedback voltage MREF to 100mV.

**Commands:** To register 0x20 (MREF) write 0x32 (the new value for MREF). To register 0x60 (E2ADDR) write 0x20 (the address of the MREF register). To register 0x61 (E2CTRL) write 0x03 (the command to copy the value to EEPROM). Wait 5ms. To register 0x61 (E2CTRL) write 0x00, to turn off EEPROM access.

**Result:** The value 0x32, located in the MREF register, is programmed into the EEPROM and becomes the new power-up default value for MREF.

#### Summary:

0x20 32

0x60 20

0x61 03

Wait 5ms

0x61 00

E2CTRL provides additional functions beyond simply programming a register's value into the EEPROM. Data may be transferred in either direction, from the registers to the EEPROM, or from the EEPROM to the registers. Register data may be transferred into or out of the EEPROM in groups of eight, a page at a time. The page address boundaries are predefined, and E2ADDR must be loaded with the address of the first byte of the page that is to be copied. Page addresses begin at 0x00 and increment by eight, with the second page beginning at 0x08, the third at 0x10, etc. To program a full page of data into the EEPROM, write the address of the page's first byte to E2ADDR, and write 0x04 to E2CTRL. Wait 5ms, and then end the write cycle by writing 0x00 to E2CTRL. When finished accessing the EEPROM always write 0x00 to E2CTRL to block inadvertent EEPROM read/writes. Table 13-2 on page 19 details the functions available through E2CTRL.

Table 13-2. EEPROM Address Register (E2ADDR, 0x60), defaults highlighted.

| Register                    | Address | Register data |             |    |    |    |    |    |    |

|-----------------------------|---------|---------------|-------------|----|----|----|----|----|----|

|                             | Addless | D7            | D6          | D5 | D4 | D3 | D2 | D1 | D0 |

| E2ADDR 0x60                 |         | -             | E2ADDR[6:0] |    |    |    |    |    |    |

| DEFAULT                     |         |               | 0           | 0  | 0  | 0  | 0  | 0  | 0  |

| EEPROM Minimum Address 0x00 |         |               | 0           | 0  | 0  | 0  | 0  | 0  | 0  |

| EEPROM Maximum Address 0x51 |         |               | 1           | 0  | 1  | 0  | 0  | 0  | 1  |

Table 13-3. EEPROM Status Register (E2CTRL, 0x61), defaults highlighted.

| Register                     | Address |    |    |    | Regist | er data |    |         |      |  |  |

|------------------------------|---------|----|----|----|--------|---------|----|---------|------|--|--|

|                              | Address | D7 | D6 | D5 | D4     | D3      | D2 | D1      | D0   |  |  |

| E2CTRL                       | 0x61    | -  | -  | -  | -      | -       | RV | VCTRL[2 | 2:0] |  |  |

| DEFAULT                      |         | 0  | 0  | 0  | 0      | 0       | 0  | 0       | 0    |  |  |

| EEPROM Read / Write Disabled |         | х  | х  | х  | х      | х       | 0  | 0       | 0    |  |  |

| Read 1 Byte from EEPROM      |         | х  | х  | х  | х      | х       | 0  | 0       | 1    |  |  |

| Read 8 Bytes from EEPROM     |         | х  | х  | х  | х      | х       | 0  | 1       | 0    |  |  |

| Write 1 Byte to EEPROM       |         | х  | х  | х  | х      | х       | 0  | 1       | 1    |  |  |

| Write 8 Bytes to EEPROM      |         | х  | х  | х  | х      | х       | 1  | 0       | 0    |  |  |

| Universal                    |         | х  | х  | х  | х      | х       | 1  | 0       | 1    |  |  |

| Unused                       |         | х  | х  | х  | х      | х       | 1  | 1       | х    |  |  |

## 14. Detailed Register Descriptions

The MSL2010 registers are summarized in "Control Registers" on page 18. Detailed register information follows.

### 14.1 RAM (0x00 through 0x1F)

32 Bytes of RAM accessible through the I<sup>2</sup>C serial interface. Copy data from RAM into EEPROM (see "EEPROM and Power-Up Defaults" on page 18) to have the data automatically load into the RAM at power up, and when EN is taken high.

Table 14-1. RAM (0x00 through 0x1F), defaults undetermined

|               |         | REGISTER DATA |    |    |    |    |    |    |    |  |  |

|---------------|---------|---------------|----|----|----|----|----|----|----|--|--|

| REGISTER NAME | ADDRESS | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

| DEFAULTS      |         | X             | X  | X  | X  | X  | X  | X  | X  |  |  |

#### 14.2 LED String Reference Voltage register (SREF, 0x20)

Holds the DAC value that controls the reference voltage for the LED string MOSFET source feedback. The reference voltage equals decimal value of this register times 2mV. The default value for SREF is 0x64, which equates to  $V_{SREF} = 200 \text{mV}$ .

Table 14-2. LED String Reference register (SREF, 0x20), defaults highlighted

|                                                       |         | REGISTER DATA |    |    |     |        |    |    |    |  |

|-------------------------------------------------------|---------|---------------|----|----|-----|--------|----|----|----|--|

| REGISTER NAME                                         | ADDRESS | <b>D</b> 7    | D6 | D5 | D4  | D3     | D2 | D1 | D0 |  |

| SREF                                                  | 0x20    |               |    |    | SRE | F[7:0] |    |    |    |  |

| DEFAULT: V <sub>SREF</sub> = 0x64 = 100 * 2mV = 200mV |         | 0             | 1  | 1  | 0   | 0      | 1  | 0  | 0  |  |

| V <sub>SREF</sub> = 0 * 2mV = 0V                      |         | 0             | 0  | 0  | 0   | 0      | 0  | 0  | 0  |  |

| V <sub>SREF</sub> = 255 * 2mV = 510mV                 |         | 1             | 1  | 1  | 1   | 1      | 1  | 1  | 1  |  |

#### 14.3 Boost Reference Voltage register (CSREF, 0x21)

Holds the DAC value that controls the reference voltage for the Boost MOSFET source feedback. The reference voltage equals decimal value of this register times 2mV. The default value for CSREF is 0x64, which equates to  $V_{CSREF} = 200$ mV.

Table 14-3. Boost Reference Voltage register (CSREF, 0x21), defaults highlighted

|                                                        |         | REGISTER DATA |    |    |    |    |    |    |    |

|--------------------------------------------------------|---------|---------------|----|----|----|----|----|----|----|

| REGISTER NAME                                          | ADDRESS | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| CSREF                                                  | 0x21    | CSREF[7:0]    |    |    |    |    |    |    |    |

| DEFAULT: V <sub>CSREF</sub> = 0x64 = 100 * 2mV = 200mV |         | 0             | 1  | 1  | 0  | 0  | 1  | 0  | 0  |

| V <sub>CSREF</sub> = 0 * 2mV = 0mV                     |         | 0             | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| V <sub>CSREF</sub> = 255 * 2mV = 510mV                 |         | 1             | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### 14.4 Efficiency Optimizer Control Register (EOCTRL, 0x40)

DThresh sets the voltage feedback threshold for D, The LED string MOSFET drain connection.

D Threshold = (<DThresh> \* 150mV) + 250mV. This is how the device monitors  $V_{LED}$  to control the magnitude of the EO current. The default value for DThresh is 1V.

Table 14-4. Efficiency Optimizer Control Register (FBOCTRL, 0x40), default highlighted

|                                           | Address/ | Register data |    |    |    |              |    |    |    |  |  |

|-------------------------------------------|----------|---------------|----|----|----|--------------|----|----|----|--|--|

| Register                                  | Default  | D7            | D6 | D5 | D4 | D3           | D2 | D1 | D0 |  |  |

| FBOCTRL                                   | 0x40     | Reserved[4:0] |    |    |    | DThresh[3:0] |    |    |    |  |  |

| Defaults                                  | 0xE5     | 1             | 1  | 1  | 0  | 0            | 1  | 0  | 1  |  |  |

| D Threshold = (0 * 150mV) + 250mV = 0.25V |          | 1             | 1  | 1  | 0  | 0            | 0  | 0  | 0  |  |  |

| D Threshold = (5 * 150mV) + 250mV = 1V    |          | 1             | 1  | 1  | 0  | 0            | 1  | 0  | 1  |  |  |

| D Threshold = (15 * 150mV) + 250mV = 2.5V |          | 1             | 1  | 1  | 0  | 1            | 1  | 1  | 1  |  |  |

These registers control access to the EEPROM. See "EEPROM and Power-Up Defaults" on page 18 and "EEPROM Address and Control/Status Registers" on page 18 for information.

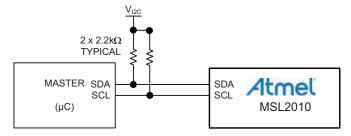

#### 15. I<sup>2</sup>C Serial Interface

The MSL2010 operates as a slave that sends and receives data through an I²C/SMBus compatible 2-wire serial interface. The interface is not needed for operation, but is provided to allow control and monitoring of device functions. These functions include changing the string current reference feedback voltages, reading and adjusting the fault response behavior and status, and programming the EEPROM. The I²C/SMBus compatible interface is suitable for 100kHz, 400kHz and 1MHz communication. The interface uses data I/O SDA and clock input SCL to achieve bidirectional communication between master and slaves.

The master, typically a microcontroller, initiates all data transfers, and generates the clock that synchronizes the transfers. SDA operates as both an input and an open-drain output. SCL operates only as an input, and does not perform clock-stretching. Pull-up resistors are required on SDA, and SCL.

Figure 15-1. I<sup>2</sup>C Interface Connections

A transmission consists of a START condition sent by a master, a 7-bit slave address plus one R/W bit, an acknowledge bit, none or many data bytes each separated by an acknowledge bit, and a STOP condition (Figure 15-2, Figure 15-4 and Figure 15-5 on page 23).

Figure 15-2. I<sup>2</sup>C Serial Interface Timing Details

#### 15.1 I<sup>2</sup>C Bus Timeout

The bus timeout feature allows the MSL2010 to reset the serial bus interface if a communication ceases before a STOP condition is sent. If SCL or SDA is low for more than 25ms (typical), then the MSL2010 terminates the transaction, releases SDA and waits for another START condition.

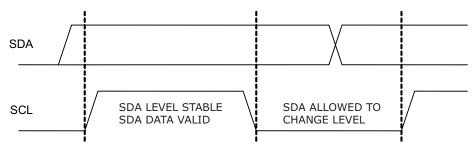

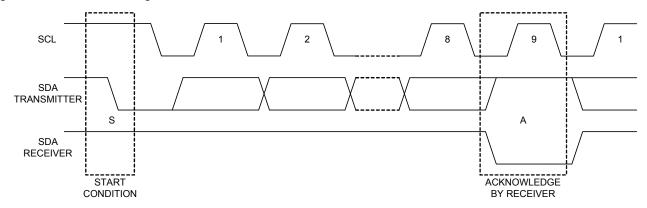

#### 15.2 I<sup>2</sup>C Bit Transfer

One data bit is transferred during each clock pulse. SDA must remain stable while SCL is high.

Figure 15-3. I<sup>2</sup>C Bit Transfer

#### 15.3 I<sup>2</sup>C START and STOP Conditions

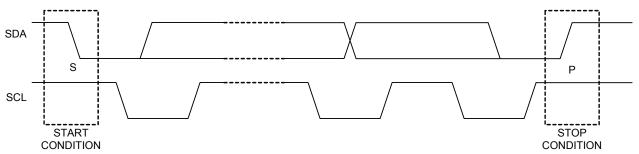

Both SCL and SDA remain high when the interface is free. The master signals a transmission with a START condition (S) by transitioning SDA from high to low while SCL is high. When the master has finished communicating with the slave, it issues a STOP condition (P) by transitioning SDA from low to high while SCL is high. The bus is then free.

Figure 15-4. I<sup>2</sup>C START and STOP Conditions

## 15.4 I<sup>2</sup>C Acknowledge Bit

The acknowledge bit is a clocked 9th bit which the recipient uses to handshake receipt of each byte of data. The master generates the 9th clock pulse, and the recipient holds SDA low during the high period of the clock pulse. When the master is transmitting to the MSL2010, the MSL2010 pulls SDA low because the MSL2010 is the recipient. When the MSL2010 is transmitting to the master, the master pulls SDA low because the master is the recipient.

Figure 15-5. I<sup>2</sup>C Acknowledge

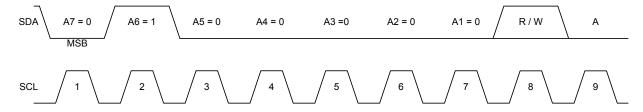

#### 15.5 I<sup>2</sup>C Slave Address

The MSL2021 has a 7-bit long slave address, 0b0100000, followed by an eighth bit, the R/W bit. The R/W bit is low for a write to the MSL2010, high for a read from the MSL2010. All MSL2010 devices have the same slave address; when using multiple devices and communicating with them through their serial interfaces, make external provision to route the serial interface to the appropriate device. Note that development systems that use I<sup>2</sup>C often left-shift the address one position before they insert the R/W bit, and thus expect a base address setting of 0x20 instead of 0x40.

Figure 15-6. I<sup>2</sup>C Slave Address

## 15.6 I<sup>2</sup>C Message Format for Writing to the MSL2010

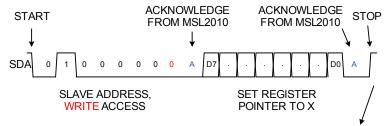

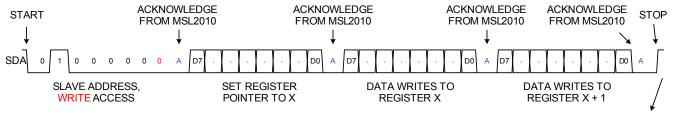

A write to the MSL2010 contains the MSL2010's slave address, the R/W bit cleared to 0, and at least 1 byte of information (Figure 15-7 on page 24). The first byte of information is the register address byte. The register address byte is stored as a register pointer, and determines which register the following byte is written into. If a STOP condition is detected after the register address byte is received, then the MSL2010 takes no further action beyond setting the register pointer.

Figure 15-7. I<sup>2</sup>C Writing a Register Pointer

THE REGISTER POINTER NOW POINTS TO X A SUBSEQUENT READ ACCESS READS FROM REGISTER ADDRESS X

When no STOP condition is detected, the byte transmitted after the register address byte is a data byte, and is placed into the register pointed to by the register address byte (Figure 15-8). To simplify writing to multiple consecutive registers, the register pointer auto-increments during each following acknowledge period. Further data bytes transmitted before a STOP condition fill subsequent registers.

Figure 15-8. I<sup>2</sup>C Writing Two Data Bytes

THE REGISTER POINTER NOW POINTS TO X+2; A SUBSEQUENT READ ACCESS BEGINS READING FROM REGISTER ADDRESS X+2

## I<sup>2</sup>C Message Format for Reading from the MSL2010

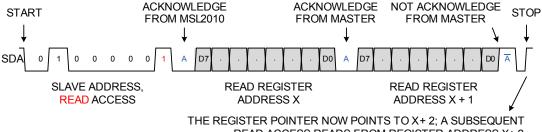

Read the MSL2010 registers using one of two techniques.

The first technique begins the same way as a write, by setting the register address pointer as shown in Figure 15-7. including the STOP condition (note that even though the final objective is to read data, the R/W bit is first sent as a write because the address pointer byte is being written into the device). Follow the Figure 15-7 transaction by what shown in Figure 15-9, with a new START condition and the slave address, this time with the R/W bit set to 1 to indicate a read. Then, after the slave initiated acknowledge bit, clock out as many bytes as desired, separated by master initiated acknowledges. The pointer auto-increments during each master initiated acknowledge period. End the transmission with a not-acknowledge followed by a stop condition.

Figure 15-9. I<sup>2</sup>C Reading Register Data with Preset Register Pointer

READ ACCESS READS FROM REGISTER ADDRESS X+ 2

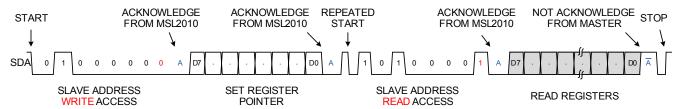

The second read technique is illustrated in Figure 15-10. Write to the MSL2010 to set the register pointer, send a repeated START condition after the second acknowledge bit, then send the slave address again with the R/W bit set to 1 to indicate a read. Then clock out the data bytes separated by master initiated acknowledge bits. The register pointer auto-increments during each master initiated acknowledge period. End the transmission with a not-acknowledge

followed by a stop condition. This technique is recommended for buses with multiple masters, because the read sequence is performed in one uninterruptible transaction.

Figure 15-10. I<sup>2</sup>C Reading Register Data Using a Repeated START

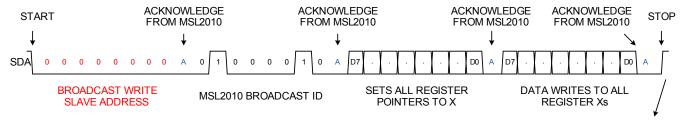

## 15.8 I<sup>2</sup>C Message Format for Broadcast Writing to Multiple devices

With a broadcast write to MSL2010, a master broadcasts the same register data to all MSL2010s on the bus. First send the broadcast write slave address of 0x00, followed by the MSL2010 broadcast device ID of 0x42. These two bytes are followed by the register address in the MSL2010's that the following data are to be written into, and finally the data byte(s) to be written into all devices.

A broadcast write example is shown in Figure 15-11. Here, the same register address in every MSL2010 is written to with identical data. If further data bytes are transmitted before the STOP condition, they are stored in subsequent internal registers of each MSL2010.

Figure 15-11. I<sup>2</sup>C Broadcast Writing a Data Byte

ALL REGISTER POINTERS NOW POINT TO X+1; THE FIRST SUBSEQUENT READ ACCESS OF EACH MSL2010 READS FROM REGISTER ADDRESS X+1

There is no broadcast read. However, a broadcast write may be used to set up the internal register pointers of all the MSL2010s in a system to speed up the subsequent individual reading of, for example, all the status registers. Figure 15-12 illustrates a broadcast write that sets all the register pointers, and issues a STOP.

Figure 15-12. I<sup>2</sup>C Broadcast Writing a Register Pointer

ALL REGISTER POINTERS NOW POINT TO X; THE FIRST SUBSEQUENT READ ACCESS

OF EACH MSL2010 BEGINS READING FROM REGISTER ADDRESS X

## 16. Packaging Information

No representation or warranties are made concerning third-party patents with regard to the use of Atmel<sup>®</sup> products. The mixing of red LEDs with phosphor-converted LEDs may be protected by certain third-party patents, such as U.S. Patent No. 7,213,940 and related patents of Cree, Inc.

## 17. Datasheet Revision History

## 17.1 42072A - 05/2013

1. Initial revision.

#### **Table of Contents**

- 1. Introduction 2

- 2. Ordering Information 2

- 3. Application Circuit 2

- 4. Absolute Maximum Ratings 3

- 5. Electrical Characteristics 4

- Typical Operating Characteristics 6

- 7. Block Diagram 11

- 8. Pinout and Pin Description 12

- 8.1 Pinout MSL2010 12

- 8.2 Pin Descriptions 12

- 9. Typical Application Circuit 14

- 10. Detailed Description 14

- 11. Fault Conditions 14

- 12. Applications Information 14

- 12.1 Turn-On Sequence 14

- 12.2 The Boost Regulator 15

- 12.3 The LED string 17

- 13. Control Registers 18

- 13.1 EEPROM and Power-Up Defaults 18

- 13.2 EEPROM Address and Control/Status Registers 18

- Detailed Register Descriptions 20

- 14.1 RAM (0x00 through 0x1F) 20

- 14.2 LED String Reference Voltage register (SREF, 0x20) 20

- 14.3 Boost Reference Voltage register (CSREF, 0x21) 20

- 14.4 Efficiency Optimizer Control Register (EOCTRL, 0x40) 21

- 15. I<sup>2</sup>C Serial Interface 21

- 15.1 I2C Bus Timeout 22

- 15.2 I2C Bit Transfer 22

- 15.3 I2C START and STOP Conditions 22

- 15.4 I2C Acknowledge Bit 23

- 15.5 I2C Slave Address 23

- 15.6 I2C Message Format for Writing to the MSL2010 23

- 15.7 I2C Message Format for Reading from the MSL2010 24

- 15.8 I2C Message Format for Broadcast Writing to Multiple devices 25

- 16. Packaging Information 26

- 17. Datasheet Revision History 27

- 17.1 42072A 05/2013 27

#### **Atmel Corporation**

1600 Technology Drive San Jose, CA 95110 USA

**Tel:** (+1) (408) 441-0311 **Fax:** (+1) (408) 487-2600

www.atmel.com

#### **Atmel Asia Limited**

Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Roa Kwun Tong, Kowloon HONG KONG

**Tel:** (+852) 2245-6100 **Fax:** (+852) 2722-1369

Atmel Munich GmbH

Business Campus

Parkring 4

D-85748 Garching b. Munich

D-85748 Garching b. Munich GERMANY

**Tel:** (+49) 89-31970-0

Fax: (+49) 89-3194621

Atmel Japan G.K.

16F Shin-Osaki Kangyo Bldg 1-6-4 Osaki, Shinagawa-ku

Tokyo 141-0032

**JAPAN**

**Tel:** (+81) (3) 6417-0300 **Fax:** (+81) (3) 6417-0370

© 2013 Atmel Corporation. All rights reserved. / Rev.: 42072A-LED-05/2013

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.