**OPT3101** SBAS883A - FEBRUARY 2018 - REVISED JUNE 2018

# **OPT3101 ToF-Based Long-Range Proximity and Distance Sensor AFE**

### **Features**

- Long-Range Distance Measurement, Obstacle Detection and Avoidance

- Flexibility to Customize Design With a Wide Variety of Photodiodes and Emitters

- Sample Rate up to 4 kHz

- 16-Bit Distance Output at 15-m Unambiguous Range

- De-Aliasing to Extend the Distance Range

- Supports 3 Transmitter Channels for Multi-Zone Operation

- **Excellent Ambient and Sunlight Rejection**

- 200-nA Full-Scale Signal Current

- 88-dB Signal Phase Dynamic Range at 1 kHz

- Supports DC Ambient up to 200 µA, 60-dB Rejection for Ambient at 1 kHz

- Distance Measurement Independent of Object Reflectivity

- Adaptive HDR to Save Power and Increase the Dynamic Range

- Configurable Event Detection and Interrupt Output Mechanism

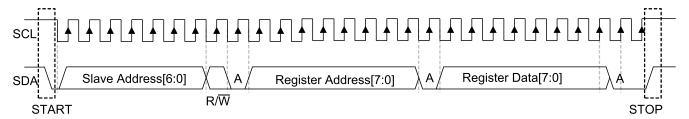

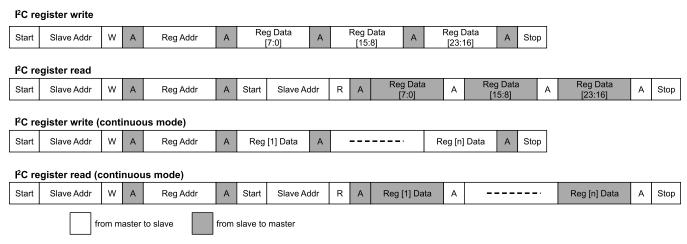

- I<sup>2</sup>C Interface for Control and Data

- Integrated Illumination Driver With Programmable Current Control up to 173 mA

- Integrated Temperature Sensor for Calibration

- Single 3.3-V or 1.8-V and 3.3-V Supply Operation

- Operating Ambient Temperature: -40 to 85°C

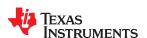

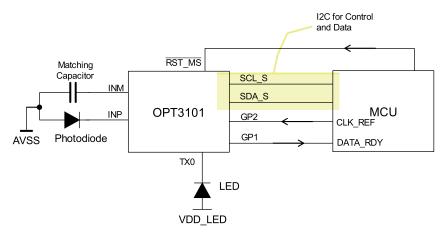

#### **Application Block Diagram**

# 2 Applications

- Precise Long-Range Distance Measurement

- Background Suppression and Accurate Object Counting in High-Speed Conveyor Belt Systems

- Precise Displacement Sensing in Factory Automation

- Non-Contact Distance and/or Level Measurement in Harsh Environments (High-Temperature or Hazardous Conditions)

- Obstacle Detection and Avoidance

- Precise Distance Measurement for Drone Landing and Navigation

- Cliff and Edge Detection in Vacuum Cleaners (No False Triggers From Dark Carpets)

- Perimeter Scan in Automatic Guided Vehicle Like Lawnmowers, Robots

- Obstruction Sensing in Applications Such as Smoke Detectors, Emergency Exits

# 3 Description

The OPT3101 device is a high-speed, high-resolution for continuous-wave, time-of-flight based proximity sensing and range finding. The device integrates the complete depth processing pipeline that includes the ADC, timing sequencer, and the digital processing engine. The device also has a builtin illumination driver that covers most of the target applications.

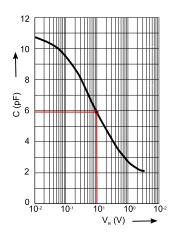

Given the high ambient rejection ratio, the device can support very high ambient conditions, including full sunlight of 130 klx.

The timing sequencer is highly configurable to provide for application-specific trade-offs of power versus performance.

The device provides depth data that consists of phase, amplitude, and ambient measurements. The calibration subsystem supports phase-data calibration for inaccuracies resulting from temperature and crosstalk.

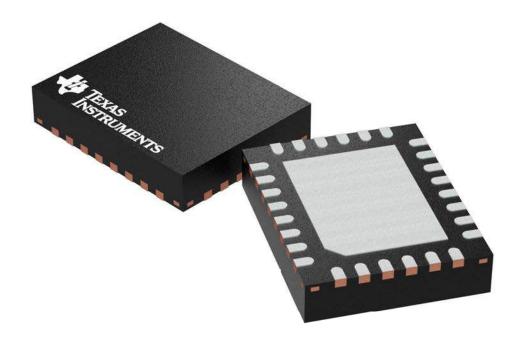

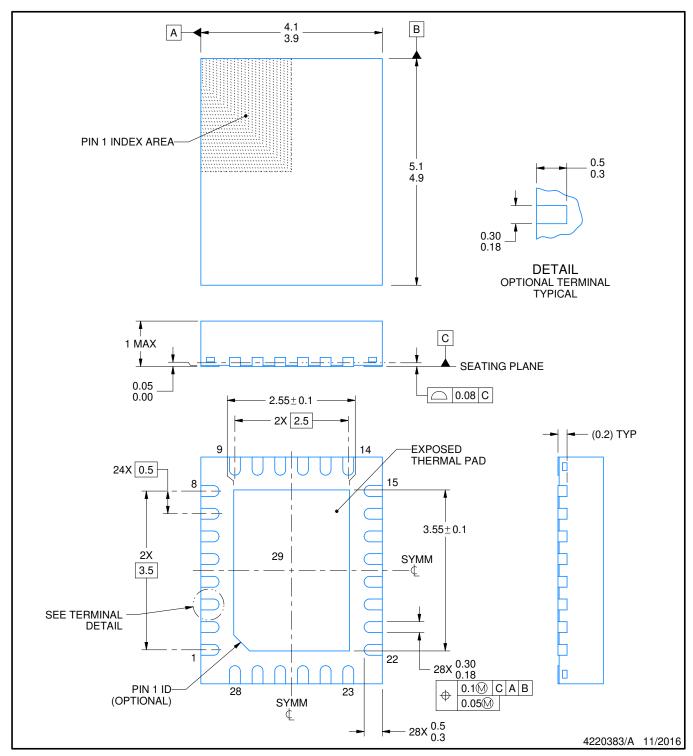

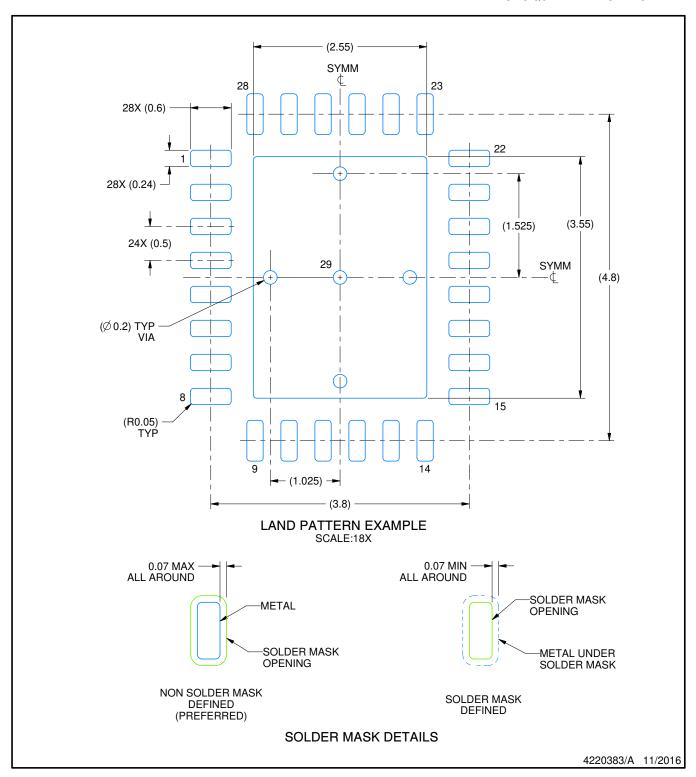

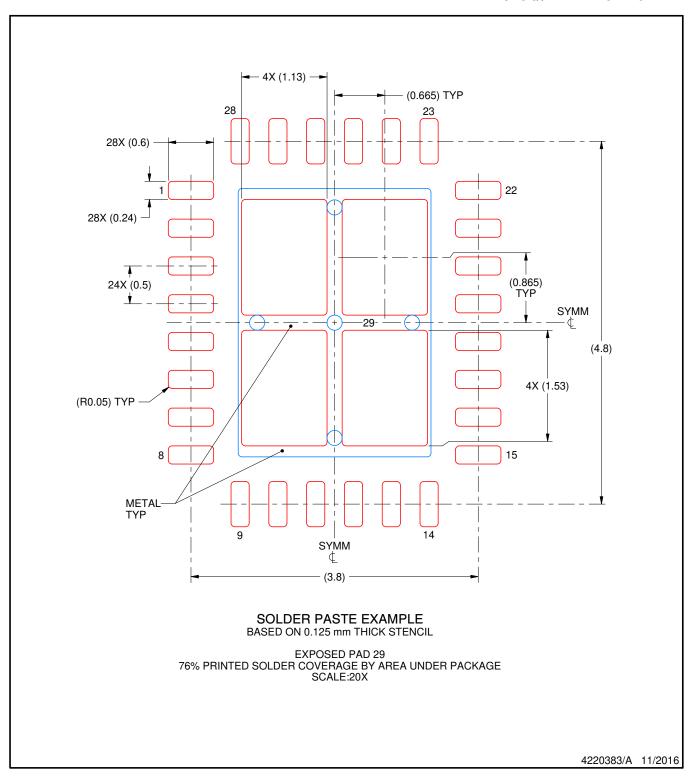

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| OPT3101     | VQFN (28) | 5.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# **Table of Contents**

| 1 | Features 1                           | 8 Application and Implementation 102                   |

|---|--------------------------------------|--------------------------------------------------------|

| 2 | Applications 1                       | 8.1 Application Information 102                        |

| 3 | Description 1                        | 8.2 Typical Application 102                            |

| 4 | Revision History2                    | 8.3 Initialization Set Up100                           |

| 5 | Pin Configuration and Functions3     | 9 Power Supply Recommendations 107                     |

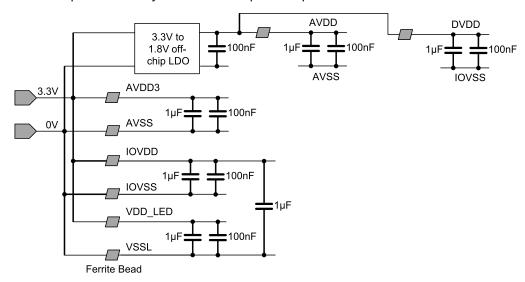

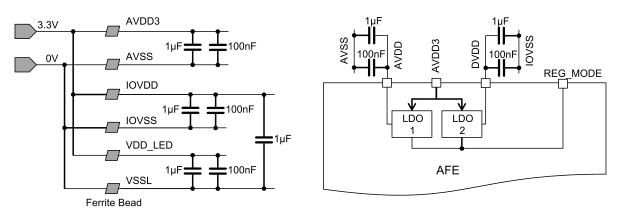

| 6 | Specifications5                      | 9.1 System With Off-Chip 1.8-V Regulator 10            |

| • | 6.1 Absolute Maximum Ratings 5       | 9.2 System With On-Chip 1.8-V Regulator 10             |

|   | 6.2 ESD Ratings                      | 10 Layout 108                                          |

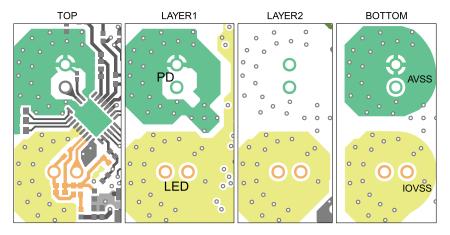

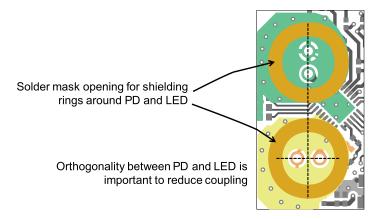

|   | 6.3 Recommended Operating Conditions | 10.1 Layout Guidelines 108                             |

|   | 6.4 Thermal Information              | 10.2 Layout Example 108                                |

|   | 6.5 Electrical Characteristics       | 11 Device and Documentation Support 11                 |

|   | 6.6 Timing Requirements              | 11.1 Documentation Support11                           |

|   | 6.7 Typical Characteristics 8        | 11.2 Receiving Notification of Documentation Updates11 |

| 7 | Detailed Description 12              | 11.3 Community Resources                               |

|   | 7.1 Overview                         | 11.4 Trademarks11                                      |

|   | 7.2 Functional Block Diagram 12      | 11.5 Electrostatic Discharge Caution                   |

|   | 7.3 Feature Description              | 11.6 Glossary11                                        |

|   | 7.4 Programming 30                   |                                                        |

|   | 7.5 Register Maps                    | 12 Mechanical, Packaging, and Orderable Information    |

# 4 Revision History

| Cł | hanges from Original (February 2018) to Revision A                                                          | Page |

|----|-------------------------------------------------------------------------------------------------------------|------|

| •  | Changged several items in the Features list                                                                 | 1    |

| •  | Changed the Application Block Diagram                                                                       | 1    |

| •  | Changed several items in the Applications section                                                           | 1    |

| •  | Changed all occurrences of "free-air temperature" in the data sheet to "junction temperature"               | 5    |

| •  | Changed all occurrances of VCC in the data sheet to V <sub>CC</sub>                                         | 5    |

| •  | Added a row to the Absolute Maximum Ratings table for Vo, Output voltage                                    | 5    |

| •  | Added two rows to the <i>Recommended Operating Conditions</i> table for V <sub>I</sub> and V <sub>O</sub>   |      |

| •  | Changed subscripting of some parameter symbols in the <i>Electrical Characteristics</i> condition statement | 6    |

| •  | Changed subscripting for t <sub>PU,Deepsleep</sub> and t <sub>PU,Standby</sub>                              | 6    |

| •  | Changed table rulings for V <sub>OH</sub> , V <sub>OL</sub> , and I <sub>I</sub>                            |      |

| •  | Changed Figure 15                                                                                           | 13   |

| •  | Changed Figure 16                                                                                           | 14   |

| •  | Changed the contents of numerous cells in the <i>Table 29</i> table                                         |      |

| •  | Added the Table 30 table                                                                                    | 40   |

| •  | Changed the content in most of the subsections of Register Descriptions                                     | 40   |

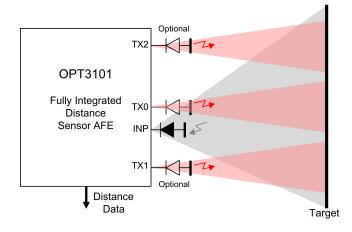

# 5 Pin Configuration and Functions

NC - No internal connection

### **Pin Functions**

| PIN      | 1          | 1/0 | TYPE <sup>(1)</sup> | DECORIDATION                                                                                                          |

|----------|------------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.        | I/O | TYPE                | DESCRIPTION                                                                                                           |

| A0       | 28         | l   | AVDD                | I <sup>2</sup> C slave LSB0 address bit                                                                               |

| A1       | 1          | l   | AVDD                | I <sup>2</sup> C slave LSB1 address bit                                                                               |

| A2       | 2          | ĺ   | AVDD                | I <sup>2</sup> C slave LSB2 address bit                                                                               |

| AVDD     | 21         | _   | _                   | 1.8-V analog supply                                                                                                   |

| AVDD3    | 20         | _   | _                   | 3.3-V analog supply                                                                                                   |

| AVSS     | 23, 26, 27 | _   | _                   | Analog ground                                                                                                         |

| DVDD     | 19         | _   | _                   | 1.8-V digital supply                                                                                                  |

| GP1      | 11         | 0   | IOVDD               | General-purpose output                                                                                                |

| GP2      | 12         | I/O | IOVDD               | General-purpose output, CLKREF input                                                                                  |

| INM      | 24         | 1   | AVDD                | AFE negative input. Connect photodiode equivalent capacitance. Connect the other end of the capacitor to ground AVSS. |

| INP      | 25         | I   | AVDD                | AFE positive input. Connect photodiode cathode. Connect the Anode of the photodiode to ground AVSS.                   |

| IOVDD    | 9, 10      | _   | _                   | Supply for I/O and illumination driver                                                                                |

| IOVSS    | 3, 8       | _   | _                   | Ground for digital and I/O                                                                                            |

| NC       | 22         | _   | _                   | No internal connection                                                                                                |

| REG_MODE | 18         | 1   | IOVDD               | Mode to select internal regulator for 1.8-V supplies (AVDD, DVDD)                                                     |

(1) This column provides the I/O voltage domain of the input and output pins.

# Pin Functions (continued)

| PIN         | N   | 1/0 | TYPE <sup>(1)</sup> | DECORIDATION                                                                                                                                          |  |

|-------------|-----|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO. | I/O | IYPE                | DESCRIPTION                                                                                                                                           |  |

| RST_MS      | 17  | I   | IOVDD               | Active-low global reset, monoshot trigger. There is no internal pullup on this pin. Connect this pin to the host controller or add a pullup resistor. |  |

| SCL_M       | 15  | 0   | IOVDD               | I <sup>2</sup> C master clock. Connect with a 10-kΩ resistor to a 3.3-V supply.                                                                       |  |

| SCL_S       | 13  | I   | IOVDD               | $I^2$ C slave clock. Connect with a 10-kΩ resistor to a 3.3-V supply.                                                                                 |  |

| SDA_M       | 16  | I/O | IOVDD               | $I^2C$ master data. Connect with a 10-k $\Omega$ resistor to a 3.3-V supply.                                                                          |  |

| SDA_S       | 14  | I/O | IOVDD               | VDD I <sup>2</sup> C slave data. Connect with a 10-kΩ resistor to a 3.3-V supply.                                                                     |  |

| TX0         | 7   | 0   | IOVDD               | Illumination driver output. Connect to LED cathode. Anode should be connected to a supply.                                                            |  |

| TX1         | 5   | 0   | IOVDD               | Illumination driver output. Connect to LED cathode. Anode should be connected to a supply.                                                            |  |

| TX2         | 4   | 0   | IOVDD               | Illumination driver output. Connect to LED cathode. Anode should be connected to a supply.                                                            |  |

| VSSL        | 6   | _   | _                   | Illumination driver ground.                                                                                                                           |  |

| Thermal pad | _   | _   | _                   | Thermal pad of the device. Connect thermal pad to AVSS PCB ground plane using multiple vias for good thermal performance.                             |  |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating junction temperature range (unless otherwise noted) (1)

|                  |                               | MIN  | MAX                               | UNIT |

|------------------|-------------------------------|------|-----------------------------------|------|

| IOVDD            | Digital I/O supply            | -0.3 | 4                                 | V    |

| AVDD3            | Analog supply                 | -0.3 | 4                                 | V    |

| AVDD             | Analog supply                 | -0.3 | 2.2                               | V    |

| DVDD             | Digital supply                | -0.3 | 2.2                               | V    |

| VI               | Input voltage at input pins   | -0.3 | $V_{\rm CC}$ + 0.3 $^{(2)}$       | V    |

| Vo               | Output voltage at output pins | -0.3 | $V_{\rm CC}$ + 0.3 <sup>(2)</sup> | V    |

| T <sub>J</sub>   | Junction temperature          | -40  | 125                               | °C   |

| T <sub>stg</sub> | Storage temperature           | -40  | 125                               | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|         |                         |                                                                               | VALUE | UNIT |

|---------|-------------------------|-------------------------------------------------------------------------------|-------|------|

| V       | Flactrostatia disebayas | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001, all pins (1)           | ±1000 | V    |

| V (ESD) | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating junction temperature range (unless otherwise noted)

|                  |                               | MIN  | NOM        | MAX                   | UNIT |

|------------------|-------------------------------|------|------------|-----------------------|------|

| IOVDD            | Digital I/O supply            | 1.7  | 1.8 to 3.3 | 3.6                   | V    |

| AVDD3            | Analog supply                 | 3    | 3.3        | 3.6                   | V    |

| AVDD             | Analog supply                 | 1.7  | 1.8        | 1.9                   | V    |

| DVDD             | Digital supply                | 1.7  | 1.8        | 1.9                   | V    |

| V <sub>DRV</sub> | TX0, TX1, TX2 pin voltage     | 0.7  |            | 3.6                   | V    |

| V <sub>I</sub>   | Input voltage at input pins   | -0.1 |            | V <sub>CC</sub> + 0.3 | V    |

| Vo               | Output voltage at output pins | -0.1 |            | V <sub>CC</sub> + 0.3 | ٧    |

| T <sub>A</sub>   | Ambient temperature           | -40  |            | 85                    | °C   |

<sup>(1)</sup> V<sub>CC</sub> is equal to IOVDD or AVDD, based on the I/O voltage domain listed in the *Pin Functions* table.

<sup>(2)</sup> V<sub>CC</sub> is equal to IOVDD or AVDD, based on the I/O voltage domain listed in the *Pin Functions* table.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.4 Thermal Information

|                        |                                              | OPT3101   |      |

|------------------------|----------------------------------------------|-----------|------|

|                        | THERMAL METRIC (1)                           | RHF (QFN) | UNIT |

|                        |                                              | 28 PINS   |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 32.9      | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 21.6      | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 10.8      | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.3       | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 10.7      | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1.6       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

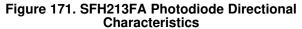

#### 6.5 Electrical Characteristics

All specifications at  $T_A$  = 25°C,  $V_{AVDD}$  = 1.8 V,  $V_{AVDD3}$  = 3.3 V,  $V_{DVDD}$  = 1.8 V,  $V_{IOVDD}$  = 3.3 V,  $I_{ambMax}$  = 20  $\mu$ A, photodiode with a capacitance of 2 pF at AFE input unless otherwise noted.

|                           | PARAMETER                                        | TEST CONDITIONS       | MIN | TYP M              | XX UNIT |

|---------------------------|--------------------------------------------------|-----------------------|-----|--------------------|---------|

| AFE                       |                                                  |                       |     |                    |         |

| I <sub>ref</sub>          | Full-scale signal current at f <sub>mod</sub>    |                       |     | 200                | nA      |

| I <sub>noise</sub>        | AFE input-referred current noise                 |                       |     | 1.5 <sup>(1)</sup> | pA/√Hz  |

| I <sub>ambMax</sub>       | Maximum ambient dc current at input              | AVDD3 = 3.3 V         |     | 200 (2)            | μΑ      |

| μ <sub>1000Hz</sub>       | Ambient attenuation at 1000 Hz                   |                       |     | 60                 | dB      |

| V <sub>R</sub>            | Bias voltage at INM, INP                         |                       |     | 1                  | V       |

| C <sub>in</sub>           | Maximum external photodiode capacitance at input |                       |     | 6                  | pF      |

| f <sub>mod</sub>          | Modulation frequency                             |                       |     | 10                 | MHz     |

| sps                       | Sample rate                                      |                       |     | 40                 | 00 Hz   |

| t <sub>PU,Deepsleep</sub> | Deep sleep recovery time                         | Monoshot mode only    |     | 1                  | ms      |

| t <sub>PU,Standby</sub>   | Standby recovery time (3)                        |                       |     | 50                 | μs      |

| ILLUMINATION              | ON DRIVER                                        |                       |     |                    |         |

| I <sub>DRV</sub>          | Maximum built-in illumination driver current     |                       |     | 173.6              | mA      |

| POWER (AC                 | TIVE MODE AT MAXIMUM FRAME RAT                   | TE)                   |     |                    |         |

| I <sub>AVDD</sub>         | 1.8-V analog supply current                      |                       |     | 11.6               | mA      |

| $I_{DVDD}$                | 1.8-V digital supply current                     |                       |     | 5.7                | mA      |

| I <sub>AVDD3</sub>        | 3.3-V analog supply current                      |                       |     | 0.5                | mA      |

| I <sub>IOVDD</sub>        | 3.3-V I/O supply current                         |                       |     | 0.7                | mA      |

| POWER (DE                 | EP SLEEP MODE)                                   |                       |     |                    |         |

| $I_{AVDD}$                | 1.8-V analog supply current                      |                       |     | 1                  | μΑ      |

| $I_{DVDD}$                | 1.8-V digital supply current                     |                       |     | 3                  | μΑ      |

| I <sub>AVDD3</sub>        | 3.3-V analog supply current                      |                       |     | 1                  | μΑ      |

| I <sub>IOVDD</sub>        | 3.3-V I/O current                                |                       |     | 2                  | μΑ      |

| POWER (AC                 | TIVE MODE AT MAXIMUM FRAME RAT                   | E), INTERNAL LDO MODE |     |                    |         |

| I <sub>AVDD3</sub>        | 3.3-V analog supply current                      | Internal LDO mode     |     | 17.9               | mA      |

| I <sub>IOVDD</sub>        | 3.3-V I/O supply current                         | Internal LDO mode     |     | 0.7                | mA      |

| POWER (DE                 | EP SLEEP MODE), INTERNAL LDO MO                  | DE                    |     |                    |         |

| I <sub>AVDD3</sub>        | 3.3-V analog supply current                      | Internal LDO mode     |     | 80                 | μΑ      |

| I <sub>IOVDD</sub>        | 3.3-V I/O supply current                         | Internal LDO mode     |     | 2                  | μΑ      |

| CMOS I/Os                 |                                                  |                       |     |                    |         |

- (1) Noise is higher by 20% with a photodiode capacitance of 6 pF at the AFE input.

- (2) I<sub>ambMax</sub> is programmable through register setting IAMB\_MAX\_SEL.

- (3) Reference, oscillator, and ambient cancellation are not powered down.

# **Electrical Characteristics (continued)**

All specifications at  $T_A$  = 25°C,  $V_{AVDD}$  = 1.8 V,  $V_{AVDD3}$  = 3.3 V,  $V_{DVDD}$  = 1.8 V,  $V_{IOVDD}$  = 3.3 V,  $I_{ambMax}$  = 20  $\mu$ A, photodiode with a capacitance of 2 pF at AFE input unless otherwise noted.

|                 | PARAMETER                         | TEST CONDITIONS                        | MIN                      | TYP                                   | MAX                      | UNIT |

|-----------------|-----------------------------------|----------------------------------------|--------------------------|---------------------------------------|--------------------------|------|

| V <sub>IH</sub> | Input high-level threshold        |                                        | 0.7 ×<br>V <sub>CC</sub> |                                       |                          | V    |

| V <sub>IL</sub> | Input low-level threshold         |                                        |                          |                                       | 0.3 ×<br>V <sub>CC</sub> | V    |

|                 | O to thick lovel                  | I <sub>OH</sub> = -2 mA                |                          | V <sub>CC</sub> <sup>(4)</sup> – 0.45 |                          |      |

| V <sub>OH</sub> | Output high level                 | I <sub>OH</sub> = -8 mA                |                          | V <sub>CC</sub> (4) – 0.5             |                          | V    |

| \/              | Output law laval                  | I <sub>OL</sub> = 2 mA                 |                          | 0.35                                  |                          | V    |

| $V_{OL}$        | Output low level                  | $I_{OL} = 8 \text{ mA}$                |                          | 0.65                                  |                          | V    |

|                 | land to be be a commont           | Pins with pullup, pulldown resistor    |                          | ±50                                   |                          |      |

| Ц               | Input pin leakage current         | Pins without pullup, pulldown resistor |                          |                                       | ±10                      | μΑ   |

| Cı              | Input capacitance                 |                                        |                          | 5                                     |                          | pF   |

| I <sub>OH</sub> | Maximum output current high level |                                        |                          | 10                                    |                          | mA   |

| I <sub>OL</sub> | Maximum output current low level  |                                        |                          | 10                                    |                          | mA   |

<sup>(4)</sup> V<sub>CC</sub> is equal to IOVDD or AVDD, based on the I/O voltage domain listed in the *Pin Functions* table.

# 6.6 Timing Requirements

|                         |                                                | MIN | NOM | MAX | UNIT |

|-------------------------|------------------------------------------------|-----|-----|-----|------|

| RSTZ_MS F               | Pin                                            |     |     |     |      |

| t <sub>PWMonoShot</sub> | Pulse duration of monoshot trigger             | 0.1 |     | 1   | μs   |

| t <sub>PWReset</sub>    | Reset pulse duration                           | 30  |     |     | μs   |

| I <sup>2</sup> C Slave  |                                                |     |     |     |      |

| f <sub>SCL</sub>        | I <sup>2</sup> C slave SCL operating frequency |     |     | 400 | kHz  |

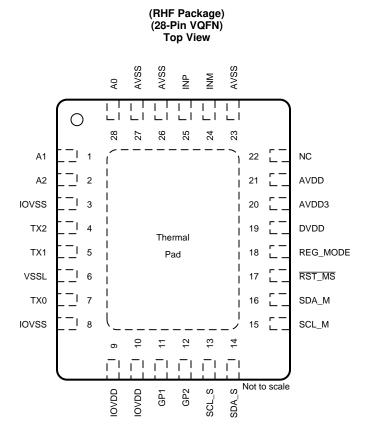

# 6.7 Typical Characteristics

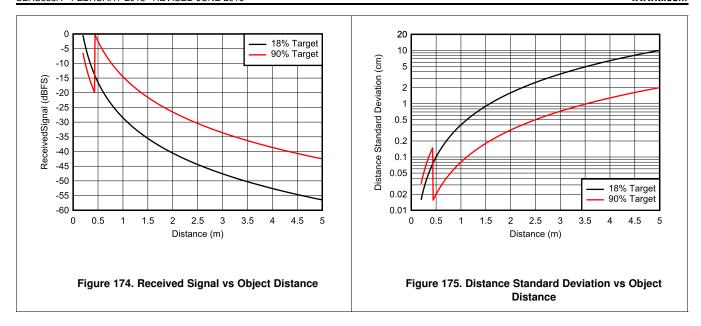

All specifications at  $T_A$  = 25°C,  $V_{AVDD}$  = 1.8 V,  $V_{AVDD3}$  = 3.3 V,  $V_{DVDD}$  = 1.8 V,  $V_{IOVDD}$  = 3.3 V,  $I_{ambMax}$  = 20  $\mu A$ , photodiode with a capacitance of 2 pF at INP and INM, unless otherwise noted.

Figure 1. Distance Standard Deviation vs AFE Input Signal

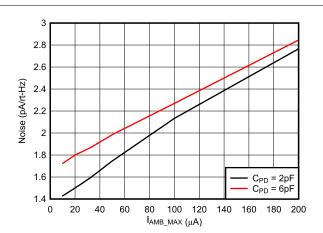

Figure 2. AFE Thermal Noise vs Maximum Ambient Current Supported

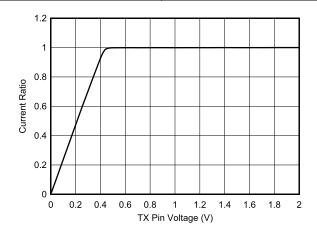

Figure 3. Illumination Driver I-V Characteristics

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

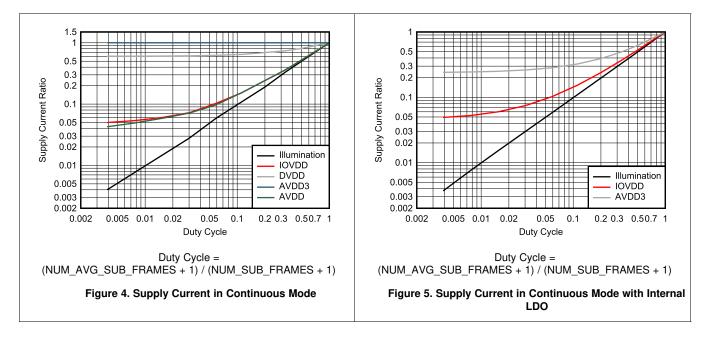

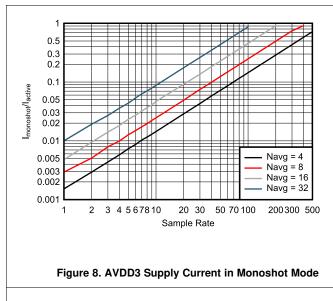

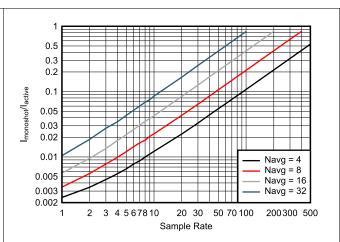

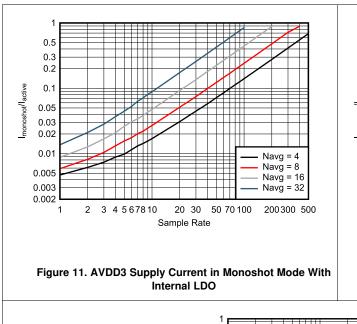

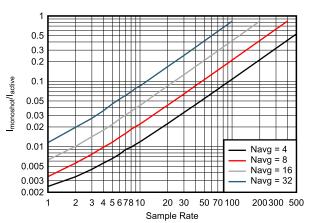

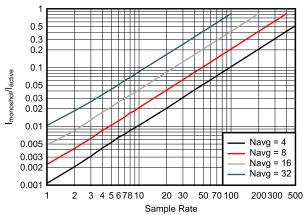

#### 6.7.1 Continuous Mode

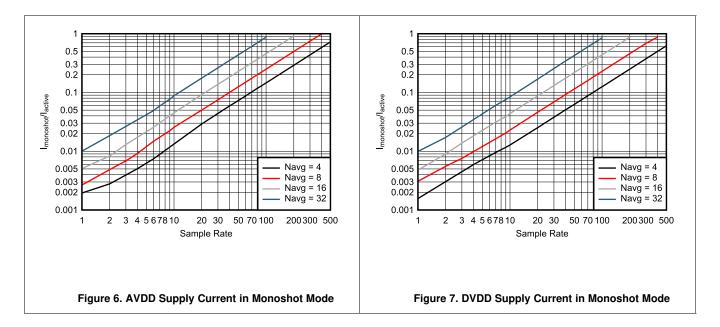

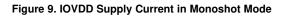

#### 6.7.2 Monoshot Mode

# TEXAS INSTRUMENTS

# **Monoshot Mode (continued)**

Figure 10. Illumination Supply Current in Monoshot Mode

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

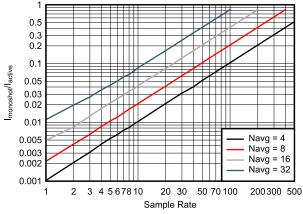

#### 6.7.3 Monoshot Mode With Internal LDO

Figure 12. IOVDD Supply Current in Monoshot Mode With Internal LDO

Figure 13. Illumination Supply Current in Monoshot Mode With Internal LDO

# 7 Detailed Description

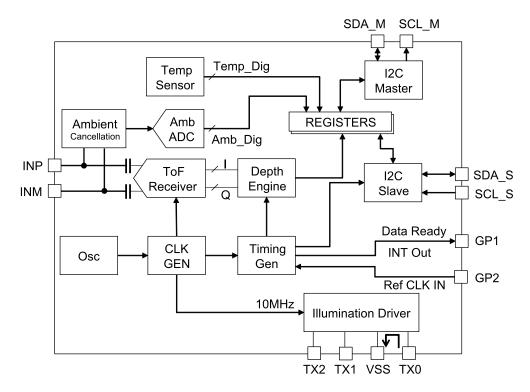

#### 7.1 Overview

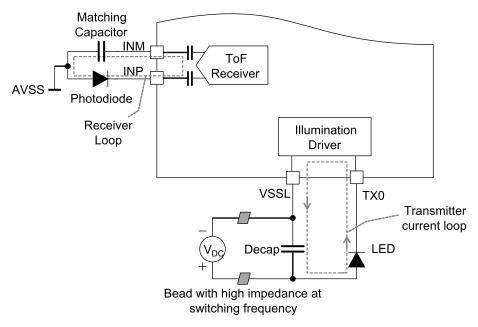

The OPT3101 device is a fully integrated analog front end (AFE) based on the time-of-flight (ToF) principle using active illumination. The OPT3101 AFE connects to an external illuminator (LED, VCSEL, or LASER) to transmit modulated optical signals, and reflected signals are received by an external photodiode which connects to the input of the AFE. The received signal is converted to amplitude and phase information by the AFE and depth engine. This output is stored in registers, which can be read out through the device I<sup>2</sup>C interface.

The OPT3101 AFE has the following blocks:

- Timing generator: generates the sequencing signals for the sensor, illumination, and depth processor

- · ToF receiver AFE

- Illumination driver

- Depth engine: calculates phase and amplitude

- I<sup>2</sup>C slave for configuration and output data interface of the device registers by the host processor

- I<sup>2</sup>C master for external temperature sensing, auto load registers from an external EEPROM

### 7.2 Functional Block Diagram

#### 7.3 Feature Description

### 7.3.1 Timing Generator

The timing generator (TG) generates the timing sequence for each frame. The TG has the following features:

- Frame rate control

- Sequencing

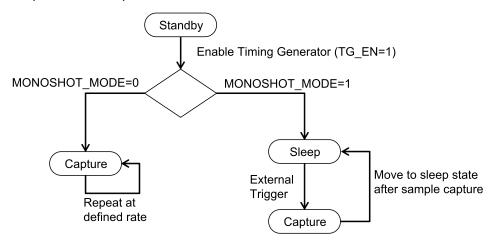

The following are various modes of operation:

- Continuous or monoshot mode

- Auto high-dynamic-range (HDR) mode or non-HDR mode

- Single-LED or multi-LED mode

### **Feature Description (continued)**

Different modes of operation are explained below.

Figure 14. Continuous and Monoshot Modes

#### 7.3.1.1 Continuous Operating Mode

In this mode, the device runs continuously at the programmed sample rate. More details about the frame timing are described in Non-HDR Mode and Auto HDR Mode.

#### 7.3.1.2 Monoshot Mode

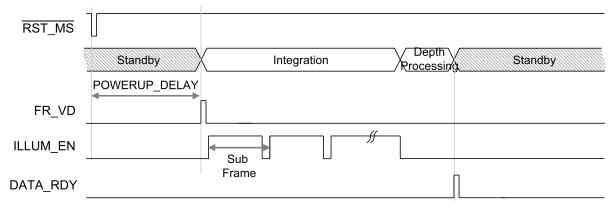

Monoshot mode is a low-power mode. In this mode, the device is in a deep sleep state and waits for an external trigger. The sample can be initiated by an  $\overline{RST_MS}$  pin (active-low) trigger or the register trigger (MONOSHOT\_BIT). On trigger, the device comes out of power down, waits for the programmed delay (POWERUP\_DELAY) to start a frame, captures the specified number of samples (MONOSHOT\_NUMFRAME), then goes into a deep sleep state to save power. A new interrupt is serviced only after completing the current frame capture. Any interrupt during the capture of a frame is discarded. Figure 15 shows the timing diagram of the monoshot mode with the  $\overline{RST_MS}$  pin trigger. From the trigger, the frame start can be delayed by setting the POWERUP\_DELAY register. The delay between the trigger and the sample start (FR\_VD signal in Figure 15) is (64 × POWERUP\_DELAY + 2) ×  $t_{CLK}$ . A minimum delay of 0.4 ms is required for the device to come out of the deep sleep state. A maximum of 26.2 ms delay can be programmed. This mode can also be used for synchronized capture from an external host.

The  $\overline{RST\_MS}$  pin is a dual-purpose pin used for reset and monoshot triggering. For reset, give a pulse duration that is > 30  $\mu$ s. For monoshot trigger, give a pulse duration that is < 1  $\mu$ s and > 100 ns.

Figure 15. Timing for Pin-Triggered Monoshot Mode With RST MS

### Feature Description (continued)

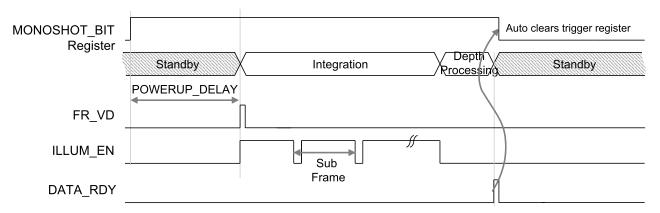

For register-triggered monoshot mode, the host writes 1 to the interrupt register (MONOSHOT\_BIT) to initiate sample capture. Once the data ready of the N<sup>th</sup> sample is available, the device automatically clears the interrupt register bit and goes into deep sleep state.

Figure 16. Timing for Register (MONOSHOT\_BIT) Triggered Monoshot Mode

|                   |            | <b>3 3</b>                                                                                                                                                         |

|-------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER         | ADDRESS    | DESCRIPTION                                                                                                                                                        |

| MONOSHOT_MODE     | 27h[1:0]   | 0: Continuous mode   3: Monoshot mode   Other values: Not valid                                                                                                    |

| MONOSHOT_NUMFRAME | 27h[7:2]   | Number of frames to be captured for every trigger.                                                                                                                 |

| POWERUP_DELAY     | 26h[23:10] | Register to program the delay from the external trigger to start of frame (FRAME_VD). Delay = $(64 \times POWERUP\_DELAY + 2) \times t_{CLK}$ , $t_{CLK} = 25$ ns. |

| MONOSHOT_BIT      | 0h[23]     | Monoshot trigger register. Write 1 to start sample capture. The bit is auto cleared after capture completion.                                                      |

**Table 1. Monoshot Mode Register Settings**

#### 7.3.1.3 Non-HDR Mode

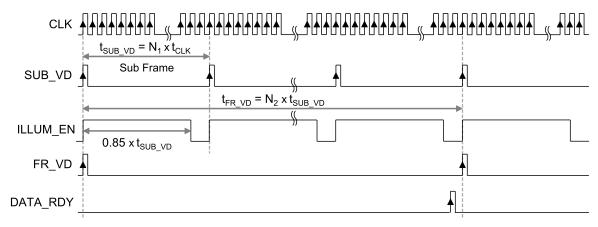

In this mode a fixed LED current is used for the Illumination driver. Figure 17 shows the frame timing. Each frame is divided into multiple sub-frames, which can be varied from 1 to  $2^{12}$ . Each sub-frame is 10,000 clocks of 40 MHz, which is equal to a 4-kHz sub-frame rate. In each sub-frame, 8192 clocks is the photodiode signal integration time and the remainder of the time is used for processing the signal and computing amplitude and phase. The device can be operated at the highest frame rate of 4 kHz by setting the number of sub-frames to 1 (NUM\_SUB\_FRAMES = 0) in a frame.

Sample Rate =

$$\frac{4000}{1 + \text{NUM\_SUB\_FRAMES}}$$

(1)

**Table 2. Sample-Rate Configuration Registers**

| PARAMETER          | ADDRESS    | DESCRIPTION                                                                                                                                                                             |

|--------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUM_SUB_FRAMES     | 9Fh[11:0]  | Total number of sub-frames in a frame. Each sub-frame is 0.25 ms.  Number of sub frames in a frame = NUM_SUB_FRAMES + 1.  This number must be equal or greater than NUM_AVG_SUB_FRAMES. |

| NUM_AVG_SUB_FRAMES | 9Fh[23:12] | Specifies the number of sub-frames to be averaged in a frame. Number of averaged sub-frames should be a power of 2 Averaging sub-frames = NUM_AVG_SUB_FRAMES + 1.                       |

If the number of averaged sub-frames is not a power of 2, the output amplitude AMP\_OUT scales according Equation 2. This is only a digital scaling factor and does not affect the distance noise of the measurement. It is recommended to use number of averaged sub-frames as a power of 2.

Amplitude Scaling Factor =

$$\frac{1 + \text{NUM\_AVG\_SUB\_FRAMES}}{2^{\left(\text{ceil}(\log_2^{(1+\text{NUM\_AVG\_SUB\_FRAMES})}\right)}}$$

(2)

- (1)  $N_1 = 10,000$ ; number of 40-MHz clocks in a sub-frame.

- (2)  $N_2 = NUM_SUB_FRAMES + 1$  is the number of sub-frames in a frame, programmable in the range of 1 to  $2^{12}$ .

Figure 17. Frame Timing Diagram

#### 7.3.1.4 Auto HDR Mode

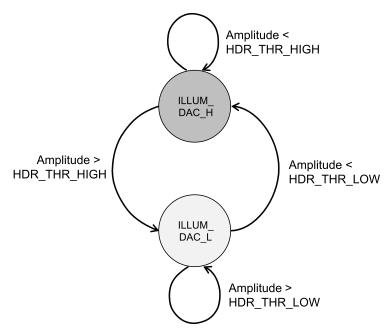

In this mode, the sequencer switches between two illumination driver currents to extend the dynamic range, depending on the signal saturation and lower amplitude threshold. The principle of operation is explained in Figure 18. When the illumination driver current is high and the amplitude exceeds the saturation threshold, HDR\_THR\_HIGH, the illumination driver is switched to the lower current. When the illumination driver current is low and the measured amplitude is below the lower threshold, HDR\_THR\_LOW, the illumination driver is switched to the higher current.

Figure 18. Auto HDR Mode: State Diagram

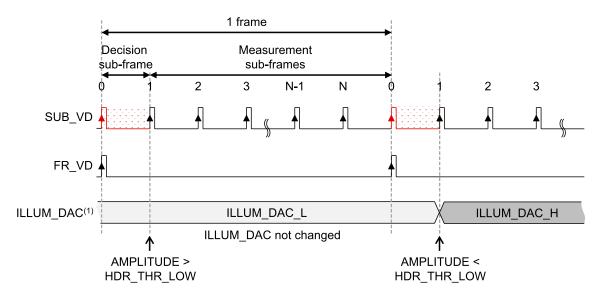

Figure 19 shows the frame timing diagram for HDR mode. In this mode, the first sub-frame information is used to make a decision about the validity of the output. If the first sub-frame output is valid, the same illumination DAC is used for the rest of the frame, otherwise the illumination driver is switched to the second illumination DAC current.

(1) The illumination driver DAC switching is shown for a particular scenario.

Figure 19. Auto HDR Mode Frame Timing Diagram

Amplitude thresholds for the HDR mode should be chosen according to Equation 3. Choice of the two illumination driver DAC currents depends on the end application.

$$\frac{\text{HDR\_THR\_HIGH}}{\text{HDR\_THR\_LOW}} > \frac{\text{ILLUM\_DAC\_H}}{\text{ILLUM\_DAC\_L}} \tag{3}$$

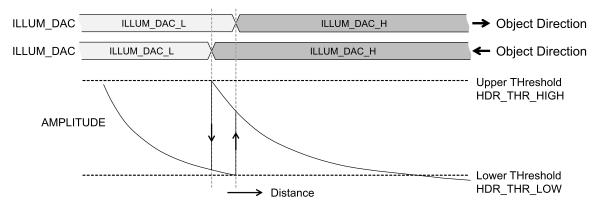

HDR THR HIGH is the saturation threshold for the HDR switching, and should be set slightly below the actual saturation amplitude (HDR should trigger before the AFE analog path saturates). HDR THR LOW is the accuracy threshold, the amplitude below which the distance accuracy is poor. Figure 20 shows an illustration of the HDR operation with distance. At a distance close to the sensor, the lower illumination DAC current is used. As the object moves away from the sensor, ILLUM DAC switches to a higher value once the amplitude falls below the lower threshold (HDR\_THR\_LOW). At the switching point, non-saturation is ensured by choosing the DAC currents according to Equation 3. As the object moves towards the sensor, ILLUM DAC switches to the lower value once the amplitude reaches the saturation level (HDR THR HIGH). At this transition, the amplitude with ILLUM DAC L is above HDR THR LOW.

Figure 20. HDR Mode Operation With Distance

Product Folder Links: OPT3101

Submit Documentation Feedback

#### **Table 3. HDR Mode Configuration Registers**

| PARAMETER       | ADDRESS                | DESCRIPTION                                                                                                                   |

|-----------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| EN_ADAPTIVE_HDR | 2Ah[15]                | Enable adaptive HDR mode.  Minimum number of sub-frames in a frame in this mode is 2 (NUM_SUB_FRAMES = 1)                     |

| SEL_HDR_MODE    | 2Ah[16]                | Chooses which current to use when EN_ADAPTIVE_HDR = 0. 0 - ILLUM_DAC_L   1 - ILLUM_DAC_H                                      |

| HDR_THR_HIGH    | 2Bh[15:0]              | Saturation amplitude threshold of the auto HDR for high DAC current (ILLUM_DAC_H) Write a value of 27000                      |

| HDR_THR_LOW     | 2Ch[15:0]              | Accuracy threshold of the auto HDR for low DAC current (ILLUM_DAC_L) = HDR_THR_HIGH × (ILLUM_DAC_L / ILLUM_DAC_H) × (1 / 1.2) |

| ILLUM_DAC_L_TX0 | 29h[4:0]               | ILLUM_DAC_L of TX0 channel                                                                                                    |

| ILLUM_DAC_H_TX0 | 29h[9:5]               | ILLUM_DAC_H of TX0 channel                                                                                                    |

| ILLUM_DAC_L_TX1 | 29h[14:10]             | ILLUM_DAC_L of TX1 channel                                                                                                    |

| ILLUM_DAC_H_TX1 | 29h[19:15]             | ILLUM_DAC_H of TX1 channel                                                                                                    |

| ILLUM_DAC_L_TX2 | 29h[23:20],<br>2Ah[23] | ILLUM_DAC_L of TX2 channel                                                                                                    |

| ILLUM_DAC_H_TX2 | 2Ah[22:18]             | ILLUM_DAC_H of TX2 channel                                                                                                    |

#### 7.3.1.5 Multi Channel Mode

The OPT3101 AFE supports up to three separate illumination channels. Only one illumination channel can be activated at a given point of time. In multi channel mode, the illumination driver switches current between different pins (TX0, TX1, and TX2) across samples. The sequence of switching is programmable (TX\_SEQ\_REG). In single channel mode, the channel to be used can be selected through SEL\_TX\_CH. Each illumination channel has separate current programmability, listed in Table 3. This mode can be combined with continuous mode, monoshot mode, non-HDR mode, or auto HDR mode.

**Table 4. Multi LED Configuration Registers**

| REGISTER     | ADDRESS   | DESCRIPTION                                                                                                                                 |

|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| EN_TX_SWITCH | 2Ah[0]    | Enable switching between Illumination channels TX0, TX1, TX2.                                                                               |

| SEL_TX_CH    | 2Ah[2:1]  | Selects the ILLUM channels when switching is disabled.                                                                                      |

| TX_SEQ_REG   | 2Ah[14:3] | Stores the sequence of ILLUM channel switching in this register. For example, register value: 2-1-0-2-1-0. The sequence will be 0-1-2-0-1-2 |

Separate calibration registers are provided for each illumination channel to support different currents for each channel in the same system.

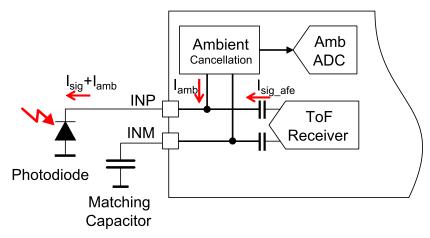

#### 7.3.2 AFE

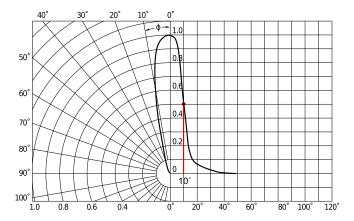

The diode current is capacitively coupled to the AFE as shown in Figure 21. The AFE processes the input signal and produces digitized in-phase and quadrature-phase components of the input signal. The AFE has a full-scale current of 200 nA peak-to-peak and supports a photodiode capacitance up to 6 pF.

Figure 21. AFE, Photodiode Interface

The signal-to-noise ratio (SNR) for a given signal current and sample rate can be calculated from the following equation.

$$\mathsf{SNR} = \frac{\mathsf{I}_{\mathsf{SIG\_AFE}}}{\mathsf{I}_{\mathsf{noise}} \times \sqrt{\mathsf{BW}}} = \frac{\mathsf{I}_{\mathsf{SIG\_AFE}}}{94.8 \; \mathsf{pA} \; / \; \sqrt{(\mathsf{NUM\_AVG\_SUB\_FRAMES} + 1)}}$$

#### where

- I<sub>sig afe</sub> = signal current entering the AFE

- $I_{noise}$  = Input referred current noise floor of the AFE = 1.5 pA/ $\sqrt{Hz}$  with  $I_{AMB\ MAX}$ =20  $\mu$ A and  $C_{PD}$ = 2pF (Figure 2)

$$\sigma_{phase} = \frac{1}{SNR} radians$$

#### where

- σ<sub>phase</sub>= Phase standard deviation in radians

- SNR is calculated from Equation 4

(5)

$$\sigma_{\text{distance}} = \frac{c / (2f_{\text{MOD}})}{2\pi} \times \frac{1}{\text{SNR}} \text{meters}$$

#### where

- $\sigma_{\text{distance}}$ = Distance standard deviation in meters

- c = Speed of light

For example, with an AFE signal current of 20 nA peak-to-peak (-20 dBFS), frame rate of 125 Hz (NUM\_AVG\_SUB\_FRAMES = 31), SNR = 1193 = 61.5 dB. Depth noise standard deviation for this scenario is  $\sigma_{distance} = 15 \text{ m} / (2\pi) / 1193 = 2 \text{ mm}$ .

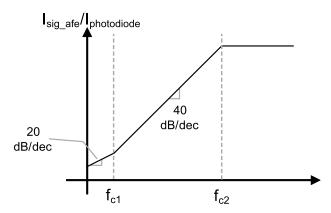

#### 7.3.3 Ambient Cancellation

The ambient cancellation circuit provides the dc and low-frequency diode current while biasing the diode at 1 V. Figure 22 shows the frequency response of the ambient cancellation circuit. A diode current with frequency below  $f_{c2}$  has second-order rejection. The corner frequency  $f_{c2}$  is designed to be at 50 kHz for IAMB\_MAX\_SEL = 0 (20  $\mu$ A ambient current support). Below frequency  $f_{c1}$  (approximately at 10 Hz), attenuation becomes first-order. So for a frequency of 1 kHz, the rejection would be (50 kHz / 1 kHz) × 2 = 2500 = 68 dB.

Submit Documentation Feedback

Product Folder Links: OPT3101

Figure 22. Ambient Cancellation Circuit Frequency Response

The maximum ambient current supported is programmable from 10  $\mu$ A to 200  $\mu$ A, listed in Table 5. Noise contribution from the ambient cancellation block increases with increase in ambient current support, shown in Figure 2. For low-ambient systems, the lower value of maximum ambient support should be used to reduce the noise contribution from the ambient cancellation. Ambient current is also converted to digital using an ADC (AMB\_DATA) at the output of the ambient cancellation block. Ambient ADC resolution is 0.104  $\mu$ A/LSB with 20- $\mu$ A support. Ambient ADC resolution scales linearly with maximum ambient current supported. Ambient current can be calculated from the AMB\_DATA using Equation 7.

$$I_{AMB} = \frac{AMB\_DATA - AMB\_CALIB}{192} \times I_{AMB\_MAX}$$

where

- I<sub>AMB MAX</sub>= Maximum ambient current supported. Listed in Table 5

- AMB\_CALIB = ambient ADC output in the dark. Typical value is 64, could vary by few codes from device to device. (7)

**Table 5. Ambient Cancellation Register Settings**

| PARAMETER    | ADDRESS  | DESCRIPTION                                                                                                                                                                        |

|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IAMB_MAX_SEL | 72h[7:4] | Selects the value of maximum ambient current support 0: 20 $\mu$ A   5: 10 $\mu$ A   10: 33 $\mu$ A   11: 50 $\mu$ A   12: 100 $\mu$ A   14: 200 $\mu$ A   Other values: Not valid |

#### 7.3.4 Oscillator

The system clock is generated using an on-chip oscillator with high stability across temperature. This oscillator is trimmed to a nominal frequency of 80 MHz within ±3%. For accurate distance conversion, this frequency is trimmed digitally to 10-bit accuracy. Additionally, the device can accept an external reference clock and correct for the on-chip oscillator variations for continuous background frequency calibration.

#### **7.3.5 CLKGEN**

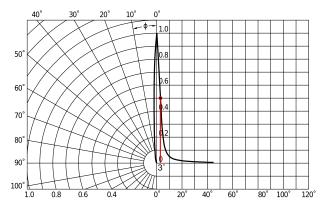

CLKGEN takes the clock from the oscillator and generates the clocks required for various blocks. CLKGEN generates a 10-MHz clock for the illumination driver. The phase of the illumination CLK can be changed in 16 steps. This feature is useful for phase nonlinearity correction resulting from square wave modulation. Phase nonlinearity from ideal square wave demodulation is approximately  $\pm 4$  degrees. OPT3101 has a filter to reject the higher-order harmonics of a square wave and the resulting nonlinearity is small,  $\pm 0.5$  degrees. For de-aliasing, CLKGEN also generates an additional frequency of  $10 \times (6 / 7)$  MHz or  $10 \times (6 / 5)$  MHz for the illumination clock.

Table 6. Register Settings to Change the Phase of Illumination

| PARAMETER         | ADDRESS  | DESCRIPTION                                                                                                       |

|-------------------|----------|-------------------------------------------------------------------------------------------------------------------|

| SHIFT_ILLUM_PHASE | 71h[6:3] | Mode to generate different Illumination clock phases. Illumination clock phase = SHIFT_ILLUM_PHASE × 22.5 degrees |

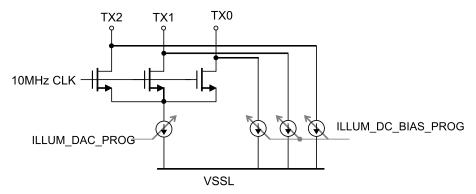

#### 7.3.6 Illumination Driver

Figure 23 shows the illumination driver block diagram. The illumination driver supports three illumination channels. The same current source is multiplexed onto three channels. Only one channel can be used at any given time.

Figure 23. Illumination Driver Block Diagram

Illumination driver current can be programmed using a 5-bit DAC, listed in Table 7. Step size of the DAC can also be scaled from 1.4 mA to 5.6 mA using ILLUM\_SCALE. A dc bias-current option is also provided. DC bias is useful if the system requires a very small switching illumination current. This dc bias can be programmed in the range of 0.5 mA to 7.5 mA in steps of 0.5 mA using ILLUM\_DC\_CURR\_DAC.

**Table 7. Illumination Driver Register Settings**

| REGISTER          | ADDRESS    | DESCRIPTION                                                                                                                               |

|-------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| EN_LED_DRV        | 79h[0]     | Enable the illumination driver                                                                                                            |

| ILLUM_DAC_L_TX0   | 29h[4:0]   | Illumination driver-current DAC register, ILLUM_DAC_L of TX0 channel. Illumination current = ILLUM_DAC_L_TX0 × DAC step                   |

| ILLUM_DAC_H_TX0   | 29h[9:5]   | Illumination driver current DAC register, ILLUM_DAC_H of TX0 channel. Illumination current = ILLUM_DAC_L_TX0 × DAC step                   |

| ILLUM_SCALE_L_TX0 | 2Bh[18:16] | Scale the illumination current DAC step size for ILLUM_DAC_L_TX0 0: 5.6 mA   1: 4.2 mA   2: 2.8 mA   3: 1.4 mA   Other values: Not valid. |

| ILLUM_SCALE_H_TX0 | 2Bh[21:19] | Scale the illumination current DAC step size for ILLUM_DAC_H_TX0 0: 5.6 mA   1: 4.2 mA   2: 2.8 mA   3: 1.4 mA   Other values: Not valid. |

| ILLUM_DC_CURR_DAC | 79h[11:8]  | Program the illumination driver DC bias current DC current = 0.5 mA × ILLUM_DC_CURR_DAC                                                   |

#### 7.3.7 Depth Engine

The depth engine computes the phase and amplitude from in-phase and quadrature-phase components of the received signal. The depth engine also performs the following calibrations:

- Phase offset

- Phase correction with temperature

- Crosstalk

- Frequency

- Square wave nonlinearity

- · Phase correction with ambient

For a detailed calibration procedure, see OPT3101 Distance Sensor System Calibration

**Table 8. Phase Offset Correction Registers**

| PARAMETER             | ADDRESS   | DESCRIPTION                                                               |

|-----------------------|-----------|---------------------------------------------------------------------------|

| EN_PHASE_CORR         | 43h [0]   | Enables phase offset correction                                           |

| PHASE_OFFSET_HDR0_TX0 | 42h[15:0] | Phase offset for TX0 illumination channel with current of ILLUM_DAC_L_TX0 |

| PHASE_OFFSET_HDR1_TX0 | 51h[15:0] | Phase offset for TX0 illumination channel with current of ILLUM_DAC_H_TX0 |

# Table 8. Phase Offset Correction Registers (continued)

| PARAMETER             | ADDRESS   | DESCRIPTION                                                               |

|-----------------------|-----------|---------------------------------------------------------------------------|

| PHASE_OFFSET_HDR0_TX1 | 52h[15:0] | Phase offset for TX1 illumination channel with current of ILLUM_DAC_L_TX1 |

| PHASE_OFFSET_HDR1_TX1 | 53h[15:0] | Phase offset for TX1 illumination channel with current of ILLUM_DAC_H_TX1 |

| PHASE_OFFSET_HDR0_TX2 | 54h[15:0] | Phase offset for TX2 illumination channel with current of ILLUM_DAC_L_TX2 |

| PHASE_OFFSET_HDR1_TX2 | 55h[15:0] | Phase offset for TX2 illumination channel with current of ILLUM_DAC_H_TX2 |

# **Table 9. Phase Temperature Coefficient Registers**

| PARAMETER                | ADDRESS                   | DESCRIPTION                                                                                                       |

|--------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------|

| EN_TEMP_CORR             | 43h[1]                    | Enable temperature correction                                                                                     |

| SCALE_PHASE_TEMP_COEFF   | 43h[8:6]                  | Adjust scale factor for temperature coefficient                                                                   |

| TMAIN_CALIB_HDR0_TX0     | 47h[11:0]                 | Calibration temperature for sensor offset for TX0 illumination channel with current of ILLUM_DAC_L_TX0            |

| TEMP_COEFF_MAIN_HDR0_TX0 | 45h[11:0]                 | Phase temperature coefficient for sensor temperature for TX0 illumination channel with current of ILLUM_DAC_L_TX0 |

| TMAIN_CALIB_HDR1_TX0     | 48h[11:0]                 | Calibration temperature for sensor offset for TX0 illumination channel with current of ILLUM_DAC_H_TX0            |

| TEMP_COEFF_MAIN_HDR1_TX0 | 2Dh[11:0]                 | Phase temperature coefficient for sensor temperature for TX0 illumination channel with current of ILLUM_DAC_H_TX0 |

| TMAIN_CALIB_HDR0_TX1     | 49h[11:0]                 | Calibration temperature for sensor offset for TX1 illumination channel with current of ILLUM_DAC_L_TX1            |

| TEMP_COEFF_MAIN_HDR0_TX1 | 2Dh[23:12]                | Phase temperature coefficient for sensor temperature for TX1 illumination channel with current of ILLUM_DAC_L_TX1 |

| TMAIN_CALIB_HDR1_TX1     | 41h[23:12]                | Calibration temperature for sensor offset for TX1 illumination channel with current of ILLUM_DAC_H_TX1            |

| TEMP_COEFF_MAIN_HDR1_TX1 | 2Fh[23:16],<br>30h[23:20] | Phase temperature coefficient for sensor temperature for TX1 illumination channel with current of ILLUM_DAC_H_TX1 |

| TMAIN_CALIB_HDR0_TX2     | 3Fh[11:0]                 | Calibration temperature for sensor offset for TX2 illumination channel with current of ILLUM_DAC_L_TX2            |

| TEMP_COEFF_MAIN_HDR0_TX2 | 31h[23:16],<br>32h[23:20] | Phase temperature coefficient for sensor temperature for TX2 illumination channel with current of ILLUM_DAC_L_TX2 |

| TMAIN_CALIB_HDR1_TX2     | 45h[23:12]                | Calibration temperature for sensor offset for TX2 illumination channel with current of ILLUM_DAC_H_TX2            |

| TEMP_COEFF_MAIN_HDR1_TX2 | 33h[23:16],<br>34h[23:20] | Phase temperature coefficient for sensor temperature for TX2 illumination channel with current of ILLUM_DAC_H_TX2 |

Table 10. Phase Temperature Coefficient Registers for External Temperature Sensor

| PARAMETER                 | ADDRESS                   | DESCRIPTION                                                                       |

|---------------------------|---------------------------|-----------------------------------------------------------------------------------|

| TILLUM_CALIB_HDR0_TX0     | 47h[23:12]                | Calibration temperature of external temperature sensor                            |

| TEMP_COEFF_ILLUM_HDR0_TX0 | 46h[11:0]                 | Phase temperature coefficient for illumination using external temperature sensor. |

| TILLUM_CALIB_HDR1_TX0     | 48h[23:12]                | Calibration temperature of external temperature sensor                            |

| TEMP_COEFF_ILLUM_HDR1_TX0 | 51h[23:16],<br>52h[23:20] | Phase temperature coefficient for illumination using external temperature sensor. |

| TILLUM_CALIB_HDR0_TX1     | 49h[23:12]                | Calibration temperature of external temperature sensor                            |

| TEMP_COEFF_ILLUM_HDR0_TX1 | 53h[23:16],<br>54h[23:20] | Phase temperature coefficient for illumination using external temperature sensor. |

| TILLUM_CALIB_HDR1_TX1     | 43h[23:12]                | Calibration temperature of external temperature sensor                            |

| TEMP_COEFF_ILLUM_HDR1_TX1 | 55h[23:16],<br>56h[23:20] | Phase temperature coefficient for illumination using external temperature sensor. |

| TILLUM_CALIB_HDR0_TX2     | 3Fh[23:12]                | Calibration temperature of external temperature sensor                            |

| TEMP_COEFF_ILLUM_HDR0_TX2 | 57h[23:16],<br>58h[23:20] | Phase temperature coefficient for illumination using external temperature sensor. |

| TILLUM_CALIB_HDR1_TX2     | 46h[23:12]                | Calibration temperature of external temperature sensor                            |

# Table 10. Phase Temperature Coefficient Registers for External Temperature Sensor (continued)

| PARAMETER                 | ADDRESS                   | DESCRIPTION                                                                       |

|---------------------------|---------------------------|-----------------------------------------------------------------------------------|

| TEMP_COEFF_ILLUM_HDR1_TX2 | 59h[23:16],<br>5Ah[23:20] | Phase temperature coefficient for illumination using external temperature sensor. |

# **Table 11. Ambient-Dependent Phase Correction Registers**

| REGISTER                   | ADDRESS    | DESCRIPTION                                                   |

|----------------------------|------------|---------------------------------------------------------------|

| AMB_PHASE_CORR_PWL_X0      | B8h[9:0]   | First knee point of PWL phase correction with ambient         |

| AMB_PHASE_CORR_PWL_X1      | B9h[19:10] | Second knee point of PWL phase correction with ambient        |

| AMB_PHASE_CORR_PWL_X2      | B9h[9:0]   | Third knee point of PWL phase correction with ambient         |

| AMB_PHASE_CORR_PWL_COEFF0  | 0Ch[23:16] | Slope of first segment for PWL phase correction with ambient  |

| AMB_PHASE_CORR_PWL_COEFF1  | B4h[7:0]   | Slope of second segment for PWL phase correction with ambient |

| AMB_PHASE_CORR_PWL_COEFF2  | B4h[15:8]  | Slope of third segment for PWL phase correction with ambient  |

| AMB_PHASE_CORR_PWL_COEFF3  | B4h[23:16] | Slope of fourth segment for PWL phase correction with ambient |

| SCALE_AMB_PHASE_CORR_COEFF | B5h[2:0]   | Scaling factor for ambient-based PWL phase correction.        |

# **Table 12. Internal Crosstalk Correction Registers**

| REGISTER              | ADDRESS    | DESCRIPTION                                                                                                                                                                                                                                                                     |

|-----------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT_XTALK_CALIB       | 2Eh[4]     | The device initializes the internal electrical crosstalk measurement upon setting this bit.  Use the following sequence: INT_XTALK_CALIB = 1 Delay (at least 5 × 2 <sup>XTALK_FILT_TIME_CONST</sup> frames) INT_XTALK_CALIB = 0 See OPT3101 Distance Sensor System Calibration. |

| XTALK_FILT_TIME_CONST | 2Eh[23:20] | Time constant for crosstalk filtering. Time constant $\tau = 2^{XTALK\_FILT\_TIME\_CONST}$ frames. At least $5\tau$ should be allowed for settling of crosstalk measurement.                                                                                                    |

| USE_XTALK_FILT_INT    | 2Eh[5]     | Select filter or direct sampling for internal crosstalk measurement.  0 - Direct sampling, 1 - Filter                                                                                                                                                                           |

| USE_XTALK_REG_INT     | 2Eh[6]     | Select register value or internally calibrated value for internal crosstalk 0 - Calibration value, 1 - Register value                                                                                                                                                           |

| IPHASE_XTALK_INT_REG  | 3D[15:0]   | Register for in-phase component of internal crosstalk                                                                                                                                                                                                                           |

| QPHASE_XTALK_INT_REG  | 3E[15:0]   | Register for quadrature-phase component of internal crosstalk                                                                                                                                                                                                                   |

| IPHASE_XTALK          | 3Bh[23:0]  | Read-only register. In-phase component. Different values can be selected to be read out with IQ_READ_DATA_SEL                                                                                                                                                                   |

| QPHASE_XTALK          | 3Ch[23:0]  | Read-only register. Quadrature-phase component. Different values can be selected to be read out with IQ_READ_DATA_SEL                                                                                                                                                           |

| IQ_READ_DATA_SEL      | 2Eh[11:9]  | Mux select for IPHASE_XTALK, QPHASE_XTALK 0 - Internal crosstalk   1 - Illum crosstalk   2 - Raw I, Q   3 - 16-bit frame counter                                                                                                                                                |

| INT_XTALK_REG_SCALE   | 2E[16:14]  | Scale factor for internal crosstalk register (IPHASE_XTALK_INT_REG, QPHASE_XTALK_INT_REG). Scale = 2 <sup>INT_XTALK_REG_SCALE</sup>                                                                                                                                             |

# **Table 13. Illumination Crosstalk Correction Registers**

| REGISTER             | ADDRESS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ILLUM_XTALK_CALIB    | 2Eh[12] | The device initializes the illumination crosstalk measurement upon setting this bit. This measurement should be done with the photodiode masked such that no modulated light is received.  Use following sequence:  ILLUM_XTALK_CALIB = 1  Delay (at least 5 × 2 <sup>XTALK_FILT_TIME_CONST</sup> frames)  ILLUM_XTALK_CALIB = 0  See OPT3101 Distance Sensor System Calibration. |

| USE_XTALK_FILT_ILLUM | 2Eh[7]  | Select filter or direct sampling for illumination crosstalk measurement.  0 - Direct sampling, 1 - Filter                                                                                                                                                                                                                                                                         |

# Table 13. Illumination Crosstalk Correction Registers (continued)

| REGISTER                  | ADDRESS   | DESCRIPTION                                                                                                                                                                        |

|---------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USE_XTALK_REG_ ILLUM      | 2Eh[8]    | Select register value or internally calibrated value for illumination crosstalk correction.  0 - Calibration value, 1 - Register value                                             |

| ILLUM_XTALK_REG_SCALE     | 2E[19-17] | Scale factor for Illumination crosstalk register (IPHASE_XTALK_REG_HDR <i>_TX<j>, QPHASE_XTALK_REG_HDR<i>_TX<j>, i = 0,1, j = 0,1,2). Scale = 2INT_XTALK_REG_SCALE</j></i></j></i> |

| IPHASE_XTALK_REG_HDR0_TX0 | 2Fh[15:0] | Register for illumination crosstalk in-phase component for TX0 channel with ILLUM_DAC_L_TX0 current                                                                                |

| QPHASE_XTALK_REG_HDR0_TX0 | 30h[15:0] | Register for illumination crosstalk quadrature-phase component for TX0 channel with ILLUM_DAC_L_TX0 current                                                                        |

| IPHASE_XTALK_REG_HDR1_TX0 | 31h[15:0] | Register for illumination crosstalk in-phase component for TX0 channel with ILLUM_DAC_H_TX0 current                                                                                |

| QPHASE_XTALK_REG_HDR1_TX0 | 32h[15:0] | Register for illumination crosstalk quadrature-phase component for TX0 channel with ILLUM_DAC_H_TX0 current                                                                        |

| IPHASE_XTALK_REG_HDR0_TX1 | 33h[15:0] | Register for illumination crosstalk in-phase component for TX1 channel with ILLUM_DAC_L_TX1 current                                                                                |

| QPHASE_XTALK_REG_HDR0_TX1 | 34h[15:0] | Register for illumination crosstalk in quadrature-phase component for TX1 channel with ILLUM_DAC_L_TX1 current                                                                     |

| IPHASE_XTALK_REG_HDR1_TX1 | 35h[15:0] | Register for illumination crosstalk in-phase component for TX1 channel with ILLUM_DAC_H_TX1 current                                                                                |

| QPHASE_XTALK_REG_HDR1_TX1 | 36h[15:0] | Register for illumination crosstalk quadrature-phase component for TX1 channel with ILLUM_DAC_H_TX1 current                                                                        |

| IPHASE_XTALK_REG_HDR0_TX2 | 37h[15:0] | Register for illumination crosstalk in-phase component for TX2 channel with ILLUM_DAC_L_TX2 current                                                                                |

| QPHASE_XTALK_REG_HDR0_TX2 | 38h[15:0] | Register for illumination crosstalk quadrature-phase component for TX2 channel with ILLUM_DAC_L_TX2 current                                                                        |

| IPHASE_XTALK_REG_HDR1_TX2 | 39h[15:0] | Register for illumination crosstalk in-phase component for TX2 channel with ILLUM_DAC_H_TX2 current                                                                                |

| QPHASE_XTALK_REG_HDR1_TX2 | 3Ah[15:0] | Register for illumination crosstalk quadrature-phase component for TX2 channel with ILLUM_DAC_H_TX2 current                                                                        |

# **Table 14. Frequency Correction Registers**

| rabio i il roquolog dell'obilon riogiciolo |            |                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|--------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| REGISTER                                   | ADDRESS    | DESCRIPTION                                                                                                                                                                                                                            |  |  |  |  |  |  |

| EN_AUTO_FREQ_COUNT                         | 0Fh[21]    | Determines which value to be used for frequency correction 0 – Trimmed value 1 – Measured value from frequency calibration                                                                                                             |  |  |  |  |  |  |

| EN_FLOOP                                   | 0Fh[22]    | Enables the frequency calibration block.                                                                                                                                                                                               |  |  |  |  |  |  |

| EN_FREQ_CORR                               | 0Fh[23]    | Enables frequency correction for the phase output                                                                                                                                                                                      |  |  |  |  |  |  |

| REF_COUNT_LIMIT                            | 0Fh[14:0]  | This sets the limit for reference-clock count. Write this register with value = $(40 \times 10^6 / 2^{SYS\_CLK\_DIVIDER}) / f_{EXT}$                                                                                                   |  |  |  |  |  |  |

| SYS_CLK_DIVIDER                            | 0Fh[20:17] | Programs system clock divider for frequency calibration. This should be adjusted to get it closer to the external reference frequency. The default is 10, system clock = 40 MHz / $2^{10}$ = 39.0625 kHz to bring close to 32.768 kHz. |  |  |  |  |  |  |

| EN_CONT_FCALIB                             | 10h[15]    | Enables continuous frequency calibration.  0 – Frequency is measured only when START_FREQ_CALIB = 1  1 – Frequency is continuously measured.                                                                                           |  |  |  |  |  |  |

| FREQ_COUNT_READ_REG                        | 10h[14:0]  | Read the register which holds the value of frequency calibration.                                                                                                                                                                      |  |  |  |  |  |  |

| START_FREQ_CALIB                           | 0Fh[16]    | Starts the frequency calibration.                                                                                                                                                                                                      |  |  |  |  |  |  |

# **Table 15. Phase Nonlinearity Correction Registers**

| REGISTER            | ADDRESS    | DESCRIPTION                                                                 |

|---------------------|------------|-----------------------------------------------------------------------------|

| EN_NL_CORR          | 4Ah[0]     | Enables square wave non-linearity correction                                |

| SCALE_NL_CORR_COEFF | 4Ah[19:18] | Scaling factor for nonlinearity correction coefficients (A*_COEFF_HDR*_TX*) |

| A0_COEFF_HDR0_TX0   | 4Ah[17:2]  | Oth-order coefficient for square wave nonlinearity correction               |

(8)

Table 15. Phase Nonlinearity Correction Registers (continued)

| REGISTER          | ADDRESS                 | DESCRIPTION                                                   |

|-------------------|-------------------------|---------------------------------------------------------------|

| A1_COEFF_HDR0_TX0 | 4Bh[15:0]               | 1st-order coefficient for square wave nonlinearity correction |

| A2_COEFF_HDR0_TX0 | 4Ch[15:0]               | 2nd-order coefficient for square wave nonlinearity correction |

| A3_COEFF_HDR0_TX0 | 4D[15:0]                | 3rd-order coefficient for square wave nonlinearity correction |

| A4_COEFF_HDR0_TX0 | 4Eh[15:0]               | 4th-order coefficient for square wave nonlinearity correction |

| A0_COEFF_HDR1_TX0 | A2[15:0]                | Oth-order coefficient for square wave nonlinearity correction |

| A1_COEFF_HDR1_TX0 | A7[15:0]                | 1st-order coefficient for square wave nonlinearity correction |

| A2_COEFF_HDR1_TX0 | AC[15:0]                | 2nd-order coefficient for square wave nonlinearity correction |

| A3_COEFF_HDR1_TX0 | B1[15:0]                | 3rd-order coefficient for square wave nonlinearity correction |

| A4_COEFF_HDR1_TX0 | AA[23:16],<br>AB[23:16] | 4th-order coefficient for square wave nonlinearity correction |

### 7.3.8 Output Data

Phase and amplitude information is stored in registers which can be read out using the  $I^2C$  interface. The device gives data ready after computation of the depth information on the general purpose I/O (GP1 or GP2) which can be used trigger the host to read the data from the device. Distance can be calculated from the phase using Equation 8. A single code of PHASE OUT is 228.7 $\mu$ m.

Distance =

$$\frac{PHASE\_OUT}{2^{16}} \times \frac{c}{2f_{MOD}}$$

meters

where

- c = Speed of light

- f<sub>MOD</sub> = 10 MHz, modulation frequency

Along with phase and amplitude of the signal, ambient ADC output and temperature sensor output are also stored in the registers. All the output data is stored in contiguous registers 8, 9, and 10.

#### **Table 16. Output Data Registers**

| REGIST<br>ER | 23           | 22           | 21       | 20           | 19                 | 18             | 17             | 16              | 15            | 14   | 13     | 12   | 11                      | 10    | 9     | 8   | 7 | 6     | 5    | 4     | 3     | 2    | 1               | 0   |

|--------------|--------------|--------------|----------|--------------|--------------------|----------------|----------------|-----------------|---------------|------|--------|------|-------------------------|-------|-------|-----|---|-------|------|-------|-------|------|-----------------|-----|

| REG 8        | FRAME_COUNT0 | AMB_OVL_FLAG | MOD_FREQ | FRAME_STATUS | TX CHANNE          |                | HDR_MODE       | PHASE_OVER_FLOW |               |      | РНА    | SE_C | TU(                     | 15:8] |       |     |   |       | PH#  | ASE_0 | J TUC | 7:0] |                 |     |

| REG 9        | DEA          | ALIAS        | s_BIN    | [3:0]        | PHASE_OVER FLOW_F2 | SIG_O VL_FL AG | EDAME COLINT 1 | 1               | AMP_OUT[15:8] |      |        |      | AMP_OUT[15:8] AMP_OUT[7 |       |       |     |   | υΤ[7: | 0]   |       |       |      |                 |     |

| REG 10       |              |              | 7        | ΓΜΑΙΝ        | N[11:4             |                |                |                 | -             | TMAI | N[3:0] |      | AM                      | 1B_D  | ATA[9 | :6] |   | AM    | 1B_D | ATA[5 | :0]   |      | FRA<br>COL<br>2 | JNT |

**Table 17. Output Data Registers Description**

| FIELD              | BIT        | DESCRIPTION                                                                                                      |

|--------------------|------------|------------------------------------------------------------------------------------------------------------------|

| PHASE_OUT          | 08h[15:0]  | Final calibrated phase.                                                                                          |

| PHASE_OVERFLOW     | 08h[16]    | Phase overflow during frequency correction.                                                                      |

| AMP_OUT            | 09h[15:0]  | Amplitude of the signal.                                                                                         |

| SIG_OVL_FLAG       | 09h[18]    | Overload flag to indicate signal saturation                                                                      |

| AMB_OVL_FLAG       | 08h[22]    | Overload flag to indicate ambient saturation                                                                     |

| HDR_MODE           | 08h[17]    | Indicates the illumination driver DAC current used. 0: ILLUM_DAC_L   1: ILLUM_DAC_H                              |

| TX_CHANNEL         | 08h[19:18] | Indicates which Illumination channel of TX0/TX1/TX2 is used.                                                     |

| FRAME_STATUS       | 08h[20]    | 0 = Invalid frame   1 = Valid frame. Frame can be invalid during crosstalk measurement.                          |

| MOD_FREQ           | 08h[21]    | Indicates the frequency used. 0: 10 MHz   1: De-alias frequency (10 MHz $\times$ 6 / 7 or 10 MHz $\times$ 6 / 5) |

| FRAME_COUNT0       | 08h[23]    | Frame counter LSB bit [0]                                                                                        |

| FRAME_COUNT1       | 09h[17:16] | Frame counter bits [2:1]                                                                                         |

| FRAME_COUNT2       | 0Ah[1:0]   | Frame counter bits [4:3]. Frame counter = FRAME_COUNT2 × 8 + FRAME_COUNT1 × 2 + FRAME_COUNT0                     |

| DEALIAS_BIN        | 09h[23:20] | Distance bin in de-alias mode                                                                                    |

| PHASE_OVER_FLOW_F2 | 09h[19]    | Phase overflow of second modulation frequency during frequency correction.                                       |

| AMB_DATA           | 0Ah[11:2]  | Ambient ADC output. Indicates the ambient light. In no ambient light condition AMB_DATA is 64 typically.         |

| TMAIN              | 0Ah[23:12] | Temperature sensor output<br>Temperature (°C) = (TMAIN / 8) – 256                                                |

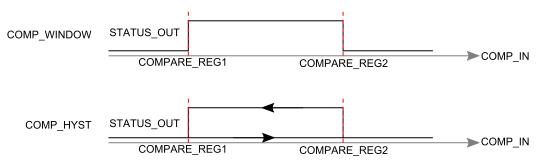

# 7.3.9 General Purpose I/O