# Up to 500 mA, 1 MHz, High Efficiency Synchronous Step-Down DC-DC Converter in DFN Package

The NCP1509 step-down PWM DC-DC converter is optimized for portable applications powered from 1-cell Li-ion or 3 cell Alkaline/NiCd/NiMH batteries. This DC-DC converter utilizes a current-mode control architecture for easy compensation and better line regulation. It also uses synchronous rectification to increase efficiency and reduce external part count. The NCP1509 optimizes efficiency in light load conditions when switched from a normal PWM mode to a "pulsed switching" mode. The device also has a built-in 1 MHz (nominal) oscillator for the PWM circuitry, or it can be synchronized to an external 500 kHz to 1000 kHz clock signal. Finally, it includes an integrated soft-start, cycle-by-cycle current limiting, and thermal shutdown protection. The NCP1509 is available in a space saving, low profile 3x3 mm 10 pin DFN package.

#### **Features**

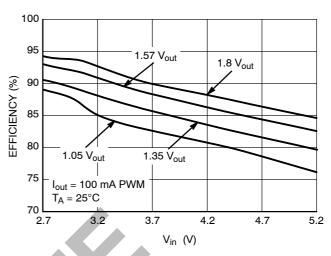

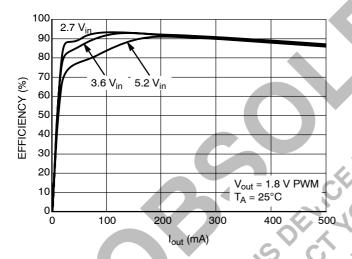

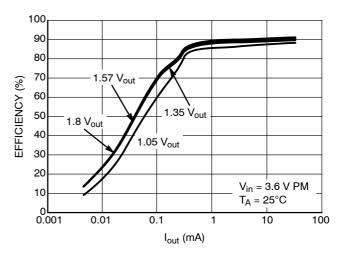

- High Efficiency:

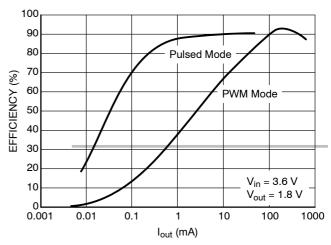

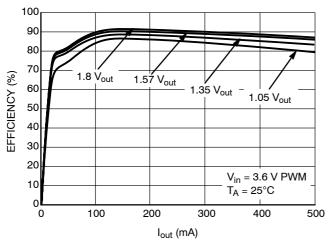

92.5% for 1.8 V Output at 3.6 V Input and 125 mA Load Current

91% for 1.8 V Output at 3.6 V Input and 300 mA Load Current

- Digital Programmable Output Voltages: 1.05, 1.35, 1.57 or 1.8 V

- Output Current up to 500 mA at  $V_{in} = 3.6 \text{ V}$

- Low Quiescent Current of 14 μA in Pulsed Switching Mode

- Low 0.2 µA Shutdown Current

- -30°C to 85°C Operation Temperature

- Low Profile DFN Package

- Pb-Free Package is Available

## **Application**

- Cellular Phones, Smart Phones and PDAs

- Digital Still Cameras

- MP3 Players and Portable Audio Systems

- Wireless and DSL Modems

- Portable Equipment

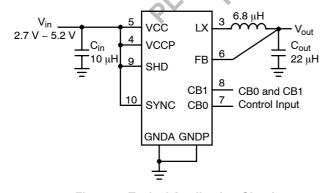

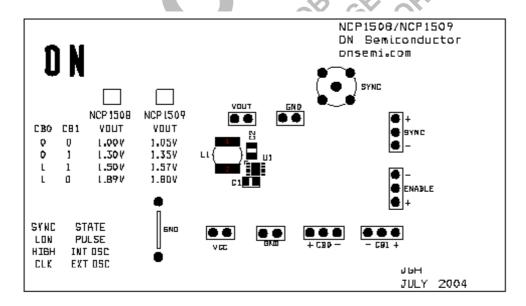

Figure 1. Typical Application Circuit

1

# ON Semiconductor®

http://onsemi.com

## MARKING DIAGRAM

10 PIN DFN MN SUFFIX CASE 485C

1509 = Specific Device Code A = Assembly Location

L = Wafer Lot Y = Year W = Work Week

#### ORDERING INFORMATION

| Device       | Package                 | Shipping†        |

|--------------|-------------------------|------------------|

| NCP1509MNR2  | 10 Pin DFN              | 3000 Tape & Reel |

| NCP1509MNR2G | 10 Pin DFN<br>(Pb-Free) | 3000 Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

Figure 2. Efficiency vs. Output Current

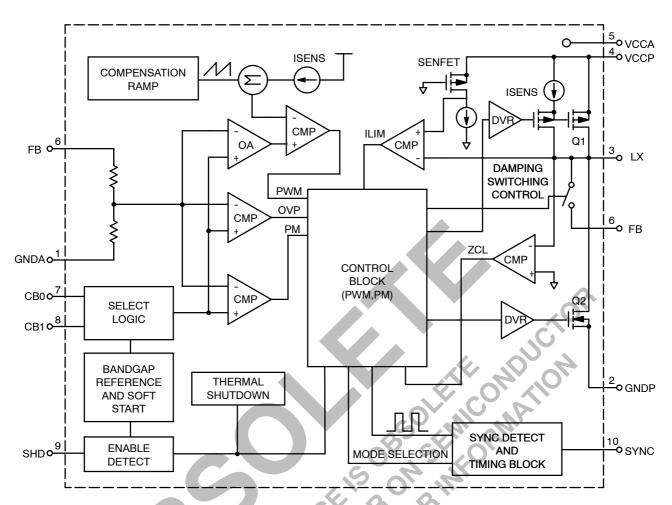

Figure 3. Simplified Block Diagram

# PIN FUNCTION DESCRIPTION

| Pin<br>Number | Name | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | GNDA | Analog GND   | Ground connection for the Analog Section of the IC. This is the GND for the FB, SYNC, CB0, CB1, PG and ENABLE pins.                                                                                                                                                                                                                                                            |

| 2             | GNDP | Power GND    | Ground connection for the N-FET Power Stage.                                                                                                                                                                                                                                                                                                                                   |

| 3             | LX   | Power Output | Connection from Power MOSFETs to the Inductor.                                                                                                                                                                                                                                                                                                                                 |

| 4             | VCCP | Power Input  | Power Supply Input for the Switching P-FET.                                                                                                                                                                                                                                                                                                                                    |

| 5             | VCCA | Power Input  | Power Supply Input for the Analog Section of the IC.                                                                                                                                                                                                                                                                                                                           |

| 6             | FB   | Analog Input | Feedback voltage from the output of the power supply.                                                                                                                                                                                                                                                                                                                          |

| 7             | CB0  | Analog Input | V <sub>out</sub> Selection Pin. This pin contains a pulldown resistor.                                                                                                                                                                                                                                                                                                         |

| 8             | CB1  | Analog Input | V <sub>out</sub> Selection Pin. This pin contains a pullup resistor.                                                                                                                                                                                                                                                                                                           |

| 9             | SHD  | Analog Input | Enable for Switching Regulator. This pin is active high to turn on the NCP1509. This pin contains an internal pulldown resistor.                                                                                                                                                                                                                                               |

| 10            | SYNC | Analog Input | Synchronization input for the PWM converter. If a clock signal is present, the converter uses the rising edge for the turn on of the PFET. If this pin is low, the converter is in Low Iq Pulse mode. If this pin is high, the converter uses the internal oscillator for the PWM mode. This pin has an internal pulldown resistor to force the operation into the Pulse mode. |

#### **MAXIMUM RATINGS**

| Rating                              |                                                     | Symbol           | Value           | Unit |

|-------------------------------------|-----------------------------------------------------|------------------|-----------------|------|

| Maximum Voltage All Pins            |                                                     | V <sub>max</sub> | 5.5             | V    |

| Maximum Operating Voltage All Pins  |                                                     | V <sub>max</sub> | 5.2             | V    |

| Thermal Resistance, Junction-to-Air |                                                     | $R_{	heta JA}$   | 68.5            | °C/W |

| Operating Ambient Temperature Range |                                                     | T <sub>A</sub>   | -30 to 85       | °C   |

| ESD Withstand Voltage               | Human Body Model (Note 1)<br>Machine Model (Note 1) | V <sub>ESD</sub> | > 2500<br>> 150 | V    |

| Moisture Sensitivity                |                                                     | MSL              | Level 1         |      |

| Storage Temperature Range           |                                                     | T <sub>stg</sub> | -55 to 150      | °C   |

| Junction Operating Temperature      |                                                     | TJ               | -30 to 125      | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Operation of American 1. This device series contains ESD protection and exceeds the following tests: Human Body Model, 100 pF discharge through a 1.5 k $\Omega$  following specification JESD22/A114. Machine Model, 200 pF discharged through all pins following specification JESD22/A115. Latchup as per JESD78 Class II: > 100 mA.

**ELECTRICAL CHARACTERISTICS** ( $V_{in} = 3.6 \text{ V}$ ,  $V_{o} = 1.57 \text{ V}$ ,  $T_{A} = 25^{\circ}\text{C}$ , Fsyn = 600 kHz 50% Duty Cycle square wave for PWM mode;  $T_{A} = -30 \text{ to } 85^{\circ}\text{C}$  for Min/Max values, unless otherwise noted.

| mode; T <sub>A</sub> = -30 to 85°C for Min/Max values, unless otherwise noted.                                                  | 1                    |       |       | -         | 1    |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|-------|-----------|------|

| Characteristic                                                                                                                  | Symbol               | Min   | Тур   | Max       | Unit |

| V <sub>CC</sub> Pin                                                                                                             |                      |       |       |           |      |

| Quiescent Current of SYNC Mode, I <sub>out</sub> = 0 mA                                                                         | Iq PWM               | -     | 175   | -         | μΑ   |

| Quiescent Current of PWM Mode, I <sub>out</sub> = 0 mA                                                                          | lq PWM               | _     | 185   | -         | μΑ   |

| Quiescent Current of Pulsed Mode, I <sub>out</sub> = 0 mA                                                                       | Iq Pulsed            | -     | 14    | _         | μΑ   |

| Quiescent Current, SHD Low                                                                                                      | Iq Off               | ı     | 0.1   | 1.0       | μΑ   |

| Input Voltage Range                                                                                                             | V <sub>in</sub>      | 2.5   | -     | 5.2       | V    |

| SYNC Pin                                                                                                                        |                      |       |       |           |      |

| Input Voltage                                                                                                                   | Vsync                | -0.3  | -     | Vcc + 0.3 | V    |

| Frequency Operational Range                                                                                                     | Fsync                | 500   | 600   | 1000      | kHz  |

| Minimum Synchronization Pulse Width                                                                                             | Dosyno Min           | 7     | 5.0   | -         | %    |

| Maximum Synchronization Pulse Width                                                                                             | Dcsync Max           | -     | 95    | O=        | %    |

| SYNC "H" Voltage Threshold                                                                                                      | Vsynch               | _     | 920   | 1200      | mV   |

| SYNC "L" Voltage Threshold                                                                                                      | Vsyncl               | 400   | 830   | -         | mV   |

| SYNC "H" Input Current, Vsync = 3.6 V                                                                                           | Isynch               | /     | 2.2   | -         | μΑ   |

| SYNC "L" Input Current, Vsync = 0 V                                                                                             | Isyncl               | -0.5  | -0    | _         | μΑ   |

| Output Level Selection Pins                                                                                                     |                      | °O,   | 1     |           |      |

| Input Voltage                                                                                                                   | Vcb                  | -0.3  | V -   | Vcc + 0.3 | V    |

| CB0, CB1 "H" Voltage Threshold                                                                                                  | Vcb h                |       | 920   | 1200      | mV   |

| CB0, CB1 "L" Voltage Threshold                                                                                                  | Vcb1                 | 400   | 830   | -         | mV   |

| CB0 "H" Input Current, CB = 3.6 V                                                                                               | lcb0 h               | -     | 2.2   | -         | μΑ   |

| CB0 "L" Input Current, CB = 0 V                                                                                                 | lcb0 l               | -0.5  | -     | -         | μΑ   |

| CB1 "H" Input Current, CB = 3.6 V                                                                                               | lcb1 h               | -     | 0.3   | 1.0       | μΑ   |

| CB1 "L" Input Current, CB = 0 V                                                                                                 | lcb1 l               | _     | -2.2  | _         | μΑ   |

| Shutdown Pin                                                                                                                    | <b>V</b>             |       |       |           |      |

| Input Voltage                                                                                                                   | Vshd                 | -0.3  | -     | Vcc + 0.3 | V    |

| SHD "H" Voltage Threshold                                                                                                       | Vshd h               | _     | 920   | 1200      | mV   |

| SHD "L" Voltage Threshold                                                                                                       | Vshd I               | 400   | 830   | -         | mV   |

| SHD "H" Input Current, SHD = 3.6 V                                                                                              | Ishd h               | _     | 2.2   | _         | μΑ   |

| SHD "L" Input Current, SHD = 0 V                                                                                                | Ishd I               | -0.5  | -     | _         | μΑ   |

| Feedback Pin                                                                                                                    |                      |       |       |           |      |

| Input Voltage                                                                                                                   | Vfb                  | -0.3  | _     | Vcc + 0.3 | V    |

| Input Current, Vfb = 1.5 V                                                                                                      | lfb                  | _     | 5.0   | 7.5       | μΑ   |

| SYNC PWM Mode Characteristics                                                                                                   |                      |       |       |           |      |

| Switching P-FET Current Limit                                                                                                   | I <sub>lim</sub>     | -     | 800   | -         | mA   |

| Duty Cycle (Note 2)                                                                                                             | DC                   | -     | -     | 100       | %    |

| Minimum On Time                                                                                                                 | T <sub>on(min)</sub> | -     | 75    | -         | nsec |

| R <sub>DS(on)</sub> Switching P–FET and N–FET                                                                                   | R <sub>DS(on)</sub>  | -     | 0.23  | -         | Ω    |

| Switching P-FET and N-FET Leakage Current                                                                                       | I <sub>leak</sub>    | _     | 0     | 10        | μΑ   |

| Output Overvoltage Threshold                                                                                                    | Vo                   | _     | 3.0   | -         | %    |

| Feedback Voltage Accuracy, V <sub>out</sub> Set = 1.05 V<br>C <sub>B0</sub> = L, C <sub>B1</sub> = L, I <sub>out</sub> = 300 mA | V <sub>out</sub>     | 1.018 | 1.050 | 1.082     | V    |

| DO DI OUL                                                                                                                       |                      |       |       |           |      |

**ELECTRICAL CHARACTERISTICS** ( $V_{in}$  = 3.6 V,  $V_{o}$  = 1.57 V,  $T_{A}$  = 25°C, Fsyn = 600 kHz 50% Duty Cycle square wave for PWM mode;  $T_{A}$  = -30 to 85°C for Min/Max values, unless otherwise noted.

| Characteristic                                                                                                                | Symbol               | Min        | Тур                                   | Max          | Unit     |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|---------------------------------------|--------------|----------|--|--|

| SYNC PWM Mode Characteristics (continued)                                                                                     |                      |            | , , , , , , , , , , , , , , , , , , , |              |          |  |  |

| Feedback Voltage Accuracy, V <sub>out</sub> Set = 1.35 V, C <sub>B0</sub> = L, C <sub>B1</sub> = H, I <sub>out</sub> = 300 mA | V <sub>out</sub>     | 1.309      | 1.350                                 | 1.391        | V        |  |  |

| Feedback Voltage Accuracy, $V_{out}$ Set = 1.57 V, $C_{B0}$ = H, $C_{B1}$ = H, $I_{out}$ = 300 mA                             | V <sub>out</sub>     | 1.523      | 1.570                                 | 1.617        | V        |  |  |

| Feedback Voltage Accuracy, $V_{out}$ Set = 1.8 V, $C_{B0}$ = H, $C_{B1}$ = L, $I_{out}$ = 300 mA                              | V <sub>out</sub>     | 1.746      | 1.800                                 | 1.854        | V        |  |  |

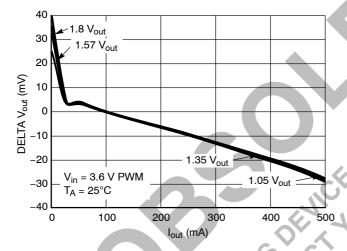

| Line Regulation, V <sub>in</sub> = 2.7 V-3.6 V, I <sub>out</sub> = 100 mA                                                     | -                    | -15        | -                                     | +15          | mV       |  |  |

| Line Regulation, V <sub>in</sub> = 3.6 V–5.2 V, I <sub>out</sub> = 100 mA                                                     | -                    | -15        | -                                     | +15          | mV       |  |  |

| Load Regulation, I <sub>out</sub> = 100 mA-300 mA                                                                             |                      | -15        | -                                     | +15          | mV       |  |  |

| Load Transient Response, 10 to 100 mA Load Step                                                                               | V <sub>out</sub>     | 7          | 50                                    | -            | mV       |  |  |

| Line Transient Response, I <sub>out</sub> = 100 mA, 3.0 to 3.6 V <sub>in</sub> Line Step                                      | V <sub>out</sub>     | -          | ±5.0                                  | 0-           | mVpp     |  |  |

| PWM Mode with Internal Oscillator Characteristics                                                                             |                      |            | /                                     | 2,           |          |  |  |

| Switching P-FET Current Limit                                                                                                 | I <sub>lim</sub>     | -          | 800                                   | -            | mA       |  |  |

| Duty Cycle (Note 2)                                                                                                           | DC                   |            |                                       | 100          | %        |  |  |

| Minimum On Time                                                                                                               | T <sub>on(min)</sub> | V- 2       | 75                                    | _            | nsec     |  |  |

| Internal Oscillator Frequency $-T_A = 25^{\circ}C$<br>$-30^{\circ}C \le T_A \le 85^{\circ}C$                                  | Fosc                 | 760<br>700 | 980<br>980                            | 1240<br>1240 | kHz      |  |  |

| R <sub>DS(on)</sub> Switching P-FET and N_FET                                                                                 | R <sub>DS(on)</sub>  | <u> </u>   | 0.23                                  | -            | Ω        |  |  |

| Switching P-FET and N-FET Leakage Current                                                                                     | I <sub>leak</sub>    | .0         | 0                                     | 10           | μΑ       |  |  |

| Output Overvoltage Threshold                                                                                                  | Vo                   | <b>-</b>   | 3.0                                   | _            | %        |  |  |

| Feedback Voltage Accuracy, $V_{out}$ Set = 1.05 V, $C_{B0}$ = L, $C_{B1}$ = L, $I_{out}$ = 300 mA                             | V <sub>out</sub>     | 1.018      | 1.050                                 | 1.082        | V        |  |  |

| Feedback Voltage Accuracy, $V_{out}$ Set = 1.35 V, $C_{B0}$ = L, $C_{B1}$ = H, $I_{out}$ = 300 mA                             | Vout                 | 1.309      | 1.350                                 | 1.391        | V        |  |  |

| Feedback Voltage Accuracy, $V_{out}$ Set = 1.57 V, $C_{B0}$ = H, $C_{B1}$ = H, $I_{out}$ = 300 mA                             | V <sub>out</sub>     | 1.523      | 1.570                                 | 1.617        | V        |  |  |

| Feedback Voltage Accuracy, $V_{out}$ Set = 1.8 V, $C_{B0}$ = H, $C_{B1}$ = L, $I_{out}$ = 300 mA                              | V <sub>out</sub>     | 1.746      | 1.800                                 | 1.854        | V        |  |  |

| Line Regulation, V <sub>in</sub> = 2.7 V–3.6 V, I <sub>out</sub> = 100 mA                                                     | _                    | -15        | _                                     | +15          | mV       |  |  |

| Line Regulation, V <sub>in</sub> = 3.6 V–5.2 V, I <sub>out</sub> = 100 mA                                                     | _                    | -15        | _                                     | +15          | mV       |  |  |

| Load Regulation, I <sub>out</sub> = 100 mA-300 mA                                                                             | -                    | -15        | _                                     | +15          | mV       |  |  |

| Load Transient Response, 10 to 100 mA Load Step                                                                               | V <sub>out</sub>     | -          | 50                                    | _            | mV       |  |  |

| Line Transient Response, I <sub>out</sub> = 100 mA, 3.0 to 3.6 Vin Line Step                                                  | V <sub>out</sub>     | -          | ±5.0                                  | -            | mVpp     |  |  |

| Pulsed Mode Characteristics                                                                                                   |                      |            |                                       |              |          |  |  |

| Peak Current Limit                                                                                                            | I <sub>lim</sub>     | -          | 200                                   | -            | mA       |  |  |

| Output Current                                                                                                                | l <sub>out</sub>     | 0.05       | -                                     | 30           | mA       |  |  |

| Output Ripple Voltage, I <sub>out</sub> = 100 μA                                                                              | V <sub>out</sub>     | -          | 22                                    | 100          | mV       |  |  |

| Feedback Voltage Accuracy, V <sub>out</sub> Set = 1.05 V, C <sub>B0</sub> = L, C <sub>B1</sub> = L                            | V <sub>out</sub>     | 1.018      | 1.050                                 | 1.082        | V        |  |  |

| Feedback Voltage Accuracy, V <sub>out</sub> Set = 1.35 V, C <sub>B0</sub> = L, C <sub>B1</sub> = H                            | V <sub>out</sub>     | 1.309      | 1.350                                 | 1.391        | V        |  |  |

| Feedback Voltage Accuracy, V <sub>out</sub> Set = 1.57 V, C <sub>B0</sub> = H, C <sub>B1</sub> = H                            | V <sub>out</sub>     | 1.523      | 1.570                                 | 1.617        | V        |  |  |

| Feedback Voltage Accuracy, V <sub>out</sub> Set = 1.8 V, C <sub>B0</sub> = H, C <sub>B1</sub> = L                             | V <sub>out</sub>     | 1.746      | 1.800                                 | 1.854        | V        |  |  |

|                                                                                                                               | L                    |            |                                       |              | <u> </u> |  |  |

<sup>2.</sup> Maximum value is guaranteed by design.

Figure 4. Efficiency vs. Output Current in PWM Mode

Figure 5. Efficiency vs. Input Voltage in PWM Mode

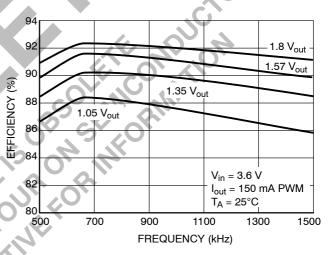

Figure 6. Efficiency vs. Output Current at Different Input Voltage

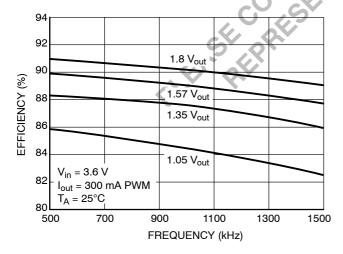

Figure 7. Efficiency vs. Frequency

Figure 8. Efficiency vs. Frequency

Figure 9. Efficiency vs. Output Current in Pulsed Mode

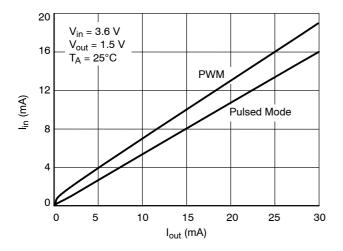

Figure 10. Input Current Comparison

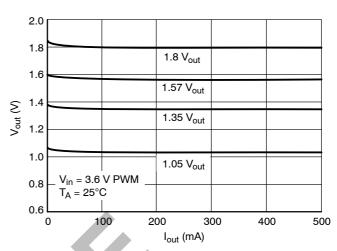

Figure 11. Output Voltage vs. Output Current

Figure 12. Load Regulation in PWM Mode

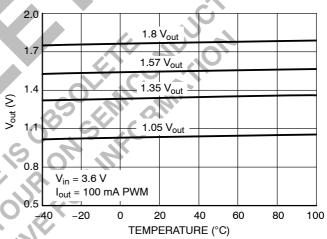

Figure 13. Output Voltage vs. Temperature

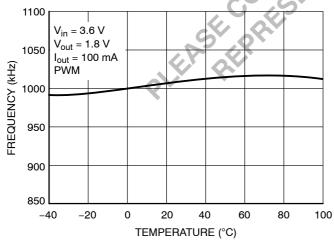

Figure 14. Oscillator Frequency vs. Temperature

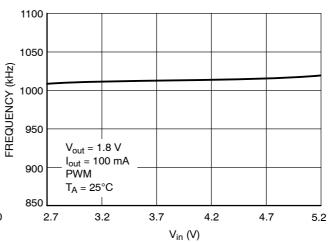

Figure 15. Oscillator Frequency vs. Input Voltage

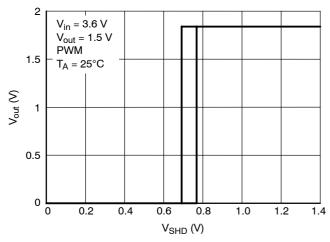

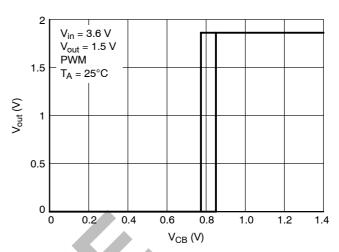

Figure 16. Output Voltage vs. Shutdown Pin Voltage

Figure 17. Transition Level of CB Pins

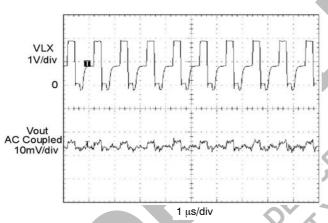

Figure 18. Light-Load PWM Switching Waveform ( $V_{in}$  = 3.6 V,  $V_{out}$  = 1.8 V,  $I_{out}$  = 30 mA)

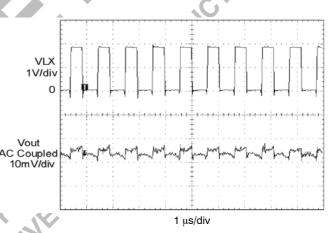

Figure 19. Heavy-Load PWM Switching Waveform (V<sub>in</sub> = 3.6 V, V<sub>out</sub> = 1.8 V, I<sub>out</sub> = 300 mA)

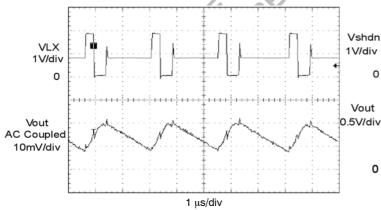

Figure 20. Pulsed Mode Switching Waveform ( $V_{in}$  = 3.6 V,  $V_{out}$  = 1.8 V,  $I_{out}$  = 30 mA)

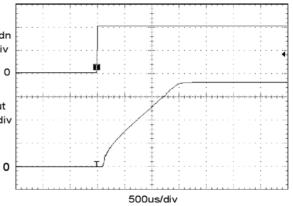

$\label{eq:continuity} \begin{aligned} & \text{Figure 21. Soft-Start} \\ & (V_{in} = 3.6 \text{ V}, V_{out} = 1.8 \text{ V}, I_{out} = 150 \text{ mA}) \end{aligned}$

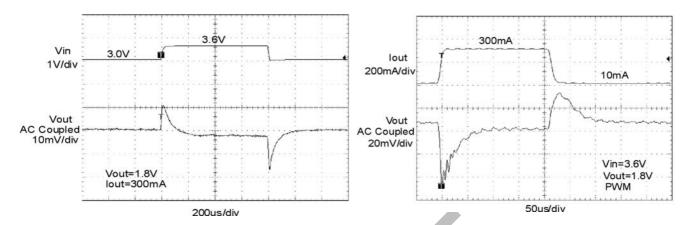

Figure 22. Line Transient Response

Figure 23. Load Transient Response

#### **DETAILED OPERATING DESCRIPTION**

#### Overview

The NCP1509 is a monolithic micro-power high frequency PWM step-down DC-DC converter specifically optimized for applications requiring high efficiency and a small PCB footprint such as portable battery powered products. It integrates synchronous rectification to improve efficiency as well as eliminate the external Schottky diode. High switching frequency allows for a low profile inductor and capacitors to be used. Four digital selectable output voltages (1.05, 1.35, 1.57 and 1.8 V) can be generated from the input supply that can range from 2.7–5.2 V. All loop compensation is integrated as well further reducing the external component count as well.

The DC-DC converter has two operating modes (normal PWM, pulsed switching), which are intended to allow for optimum efficiency under either light (up to 30 mA) or heavy loads. The user determines the operating mode by controlling the SYNC input. In addition the SYNC input can be used to synchronize the PWM to an external system clock signal in the range of 500–1000 kHz.

## **PWM Operating Mode**

The NCP1509 can be set to current mode PWM operation by connecting SYNC pin to V<sub>CC</sub>. In this mode, the output voltage is regulated by modulating on-time pulse width of the main switch Q1 at a fixed frequency of 1 MHz. The switching of the PMOS Q1 is controlled by a flip-flop driven by the internal oscillator and a comparator that compares the error signal from an error amplifier with the sum of the sensed current signal and compensation ramp. At the beginning of each cycle, the main switch Q1 is turned ON by the rising edge of the internal oscillation clock. The inductor current ramps up until the sum of the current sense signal and compensation ramp becomes higher than the error voltage amplifier. Once this has occurred, the PWM comparator resets the flip-flop, Q1 is turned OFF and the synchronous switch Q2 is turned ON. Q2 replaces the external Schottky diode to reduce the conduction loss and improve the efficiency. To avoid overall power loss, a certain amount of dead time is introduced to ensure Q1 is completely turned OFF before Q2 is being turned ON.

In continuous conduction mode (CCM), Q1 is turned ON after Q2 is completely turned OFF to start a new clock cycle. In discontinuous conduction mode (DCM), the zero crossing comparator (ZLC) will turn off Q2 when the inductor current drops to zero.

## **Overvoltage Protection**

The overvoltage protection circuit is present in PWM mode to prevent the output voltage from going too high under light load or fast load transient conditions. The output overvoltage threshold is 5% above nominal set value. If the output voltage rises above 5% of the nominal value, the OVP comparator is activated and switch Q1 is turned OFF.

Switching will continue when the output voltage falls below the threshold of OVP comparator.

## Pulsed Mode (PM)

Under light load conditions (< 30 mA), NCP1509 can be configured to enter a low current pulsed mode operation to reduce power consumption. This is accomplished by SYNC pin held LOW. The output regulation is implemented by pulse frequency modulation. If the output voltage drops below the threshold of PM comparator (typically Vnom-2%), a new cycle will be initiated by the PM comparator to turn on the switch Q1. Q1 remains ON until 200 mA inductor peak current is reached. Then ILIM comparator goes high to switch off Q1. After a short dead time delay, switch rectifier Q2 is turn ON. The zero crossing comparator will detect when the inductor current drops to zero and send the signal to turn off Q2. The output voltage continues to decrease through discharging the output capacitor. When the output voltage falls below the threshold of PM comparator again, a new cycle starts immediately.

## Cycle-by-Cycle Current Limit

From the block diagram (Figure 3), an ILIM comparator is used to realize cycle-by-cycle current limit protection. The comparator compares the LX pin voltages with the reference voltage from the SENFET, which is biased by constant current. If the inductor current reaches the limit, ILIM comparator detects the LX voltage falling below the reference voltage from SENFET and releases the signal to turn off the switch Q1. The cycle-by-cycle current limit is set at 800 mA in PWM and 200 mA in PM.

# Frequency Synchronization and Operating Mode Selection

The SYNC pin can also be used for frequency synchronization by connecting it with an external clock signal. It operates in PWM mode when synchronized to an external clock. The switching cycle initiates by the rising edge of the clock. The synchronization clock signals between 0.4 V and 1.2 V from 500 kHz to 1000 kHz.

Gating on and off the clock, the SYNC pin can also be used to select between PM and PWM modes. It allows efficient dynamical power management by adjusting the converter operation to the specific system requirement. Set SYNC pin low to select PM mode at light load conditions (up to 30 mA) and set SYNC pin high or connect with external clock to select PWM mode at heavy load condition to achieve optimum efficiency. Table 1 shows the mode selection with three different SYNC pin states.

**Table 1. Operating Mode Selection**

| SYNC Pin State | Operating Mode                 |

|----------------|--------------------------------|

| LOW            | Pulsed Mode (PM)               |

| HIGH           | PWM, 1 MHz Switch Frequency    |

| CLOCK          | PWM, Frequency Synchronization |

#### **Output Voltage Selection**

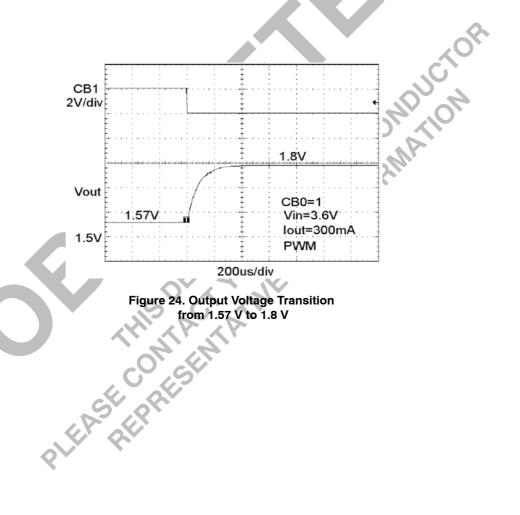

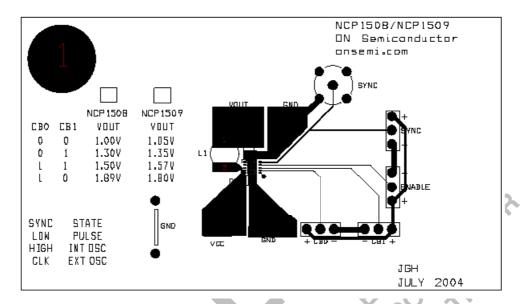

The output voltage is digitally programmed to one of four voltage levels depending on the logic state of CB0 and CB1. Therefore if the NCP1509's load, such as a digital cellular phone's baseband processor, supports dynamic power management, the device can lower or raise its core voltage under software control. When combined with the pulsed current mode function in low load situations, this active voltage management further stretches the useful operating life of the handset between charges. Figure 24 shows a typical transition between 1.57 to 1.8 volts.

The output voltage levels are listed in Table 2. The CB0 has a pull down resistor and the CB1 has a pullup resistor. The default output voltage is 1.35 V when CB0 and CB1 are floating.

Table 2. Truth Table for CB0 and CB1 with the corresponding output voltage

| CB0 | CB1   | Vout(V) | prote        |

|-----|-------|---------|--------------|

| 0   | 0     | 1.05    | junc<br>temp |

| 0   | 1     | 1.35    | mod          |

| 1   | 1     | 1.57    | turne        |

| 1   | 0     | 1.8     | temp<br>prev |

|     |       |         | over         |

|     |       | ~ O . Y | heats        |

|     | PLEAS | CONSER  |              |

#### Soft-Start

The NCP1509 uses soft-start to limit the inrush current when the device is initially powered up or enabled. Soft-start is implemented by gradually increasing the reference voltage until it reaches the full reference voltage. During startup, a pulsed current source charges the internal soft-start capacitor to provide gradually increasing reference voltage for the PWM loop. When the voltage across the capacitor ramps up to the nominal reference voltage, the pulsed current source will be switched off and the reference voltage will switch to the regular reference voltage. From Figure 21, it show the soft-start time is about 1.5 ms.

#### Shutdown Mode

When the SHD pin has a voltage applied of less than 0.4 V, the NCP1509 will be disabled. In shutdown mode, the internal reference, oscillator and most of the control circuitries are turned off. Therefore, the typical current consumption will be  $0.1~\mu A$  (typical value).

Applying a voltage above 1.2 V to SHD pin will enable the device for normal operation. The device will go through soft–start to normal operation.

## Thermal Shutdown

Internal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. If the junction temperature exceeds 160°C, the device shuts down. In this mode switch Q1 and Q2 and the control circuits are all turned off. The device restarts in soft–start after the temperature drops below 135°C. This feature is provided to prevent catastrophic failures from accidental device overheating and it is not intended as a substitute for proper heatsinking.

#### **APPLICATIONS INFORMATION**

## **Component Selection**

# **Input Capacitor Selection**

In PWM operating mode, the input current is pulsating with large switching noise. Using an input bypass capacitor can reduce the peak current transients drawn from the input supply source, thereby reducing switching noise significantly. The capacitance needed for the input bypass capacitor depends on the source impedance of the input supply. The RMS capacitor current is calculated as:

IRMS

$$\approx IO\sqrt{D \cdot D'}$$

(eq. 1)

The maximum RMS current occurs at 50% duty cycle with maximum output current, which is  $I_{O,max}/2$ .

For NCP1509, a low profile ceramic capacitor of 10 µF should be used for most of the cases. For effective bypass results, the input capacitor should be placed as close as possible to the  $V_{CC}\ \mbox{Pin}.$

#### **Inductor Value Selection**

Selecting the proper inductor value is based on the desired ripple current. The relationship between the inductance and the inductor ripple current is given by the equation in below.

$$\Delta i_{L} = \frac{V_{out}}{Lf_{s}} \left( 1 - \frac{V_{out}}{V_{in}} \right)$$

(eq. 2)

Large value inductors will have small ripple current and low value inductor will have high ripple current. For NCP1509, the compensation is internally fixed and a fixed 6.8 µH inductor is needed for most of the applications.

#### **Output Capacitor Selection**

Selecting the proper output capacitor is based on the desired output ripple voltage. Ceramic capacitors with low ESR values will have the lowest output ripple voltage and are strongly recommended. The output ripple voltage is given by:

$$\Delta V_{C} = \Delta i_{L} \cdot \left( ESR + \frac{1}{4f_{S}C_{out}} \right)$$

(eq. 3)

The RMS output capacitor current is given by:

$$I_{RMS}(C_{out}) = \frac{V_O \cdot (1 - D)}{2\sqrt{3} \cdot L \cdot f_s}$$

(eq. 4)

Where f<sub>s</sub> is the switching frequency and ESR is the effective series resistance of the output capacitor. A low ESR, 22 µF ceramic capacitor is recommended for NCP1509 in most of applications. For example, with TDK C2012X5R0J226 output capacitor, the output ripple is less than 10 mV at 300 mA.

## **Design Example**

As a design example, assume that the NCP1509 is used in a single lithium-ion battery application. The input voltage, V<sub>in</sub>, is 3.0 V to 4.2 V. Output condition is V<sub>out</sub> at 1.8 V with a typical load current of 120 mA and a maximum of 300 mA. For NCP1509, the inductor has a predetermined value, 6.8 μH. The inductor ESR will factor into the overall efficiency of the converter. The inductor needs to be selected by the required peak current.

Equation 5 is the basic equation for an inductor and describes the voltage across the inductor. The inductance value determines the slope of the current of the inductor.

$$\frac{V_L}{L} = \frac{di_L}{dt}$$

(eq. 5)

Equation 5 is rearranged to solve for the change in current for the on-time of the converter in Continuous Conduction Mode.

$$i_{L, pk-pk} = \frac{(V_{in} - V_{out})}{L} \cdot DT_{S}$$

$$= \frac{(V_{in} - V_{out})}{L} \cdot \frac{V_{in}}{V_{out}} \cdot \frac{1}{f_{S}}$$

$$i_{L, max} = I_{O, max} + \frac{\Delta i_{L, pk-pk}}{2}$$

(eq. 6)

Utilizing Equations 6, the peak-to-peak inductor current is calculated using the following worst-case conditions.

$$V_{in, max} = 4.2 \text{ V}, V_{out} = 1.8 \text{ V}, f_s = 1 \text{ MHz-}20\%,$$

$$L\,=\,6.8~\mu H\text{--}10\%, i_{L,~pk\text{--}pk}\,=\,211~\text{mA}, i_{L,~max}\,=\,405~\text{mA}$$

Therefore, the inductor must have a maximum current exceeding 405 mA.

Since the compensation is fixed internally in the IC, the input and output capacitors as well as the inductor have a predetermined value too:  $C_{in} = 10 \,\mu\text{F}$  and  $C_{out} = 22 \,\mu\text{F}$ . Low ESR capacitors are needed for best performance. Therefore, ceramic capacitors are recommended. Please see Table 3 for recommended inductors and capacitors.

#### **PCB** Layout Recommendations

Good PCB layout plays an important role in switching mode power conversion. Careful PCB layout can help to minimize ground bounce, EMI noise and unwanted feedbacks that can affect the performance of the converter. Hints suggested below can be used as a guideline in most situations.

- 1. Use star-ground connection to connect the IC ground nodes and capacitor GND nodes together at one point. Keep them as close as possible. And then connect this to the ground plane (if it is used) through several vias. This will reduce noise in ground plane by preventing the switching currents from flowing through the ground plane.

- 2. Place the power components (i.e., input capacitor, inductor and output capacitor) as close together as possible for best performance. All connecting traces must be short, direct, and thick to reduce voltage errors caused by resistive losses across these traces.

- 3. Separate the feedback path of the output voltage from the power path. Keep this path close to the NCP1509 circuit. And also route it away from noisy components. This will prevent noise from coupling into voltage feedback trace.

4. Place the DC-DC converter away from noise sensitive circuitry, such as RF circuits. Interference with noise sensitive circuitry in the DC-DC converter can be reduced by distance between them.

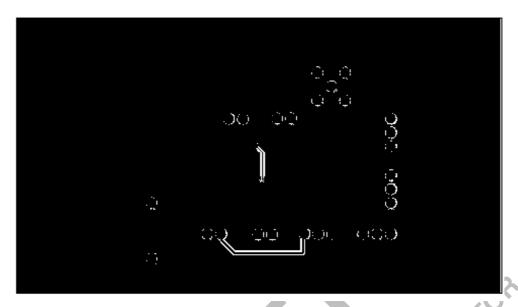

The following shows NCP1509 demo board layout and suggested bill of materials.

Figure 25. Top and Silkscreen Layer

Figure 26. Soldermask Top and Silkscreen Layer

Figure 27. Bottom Layer

Table 3. Bill of Materials

| Component        | Value             | Manufacturer  | Part Number                    | Size (mm)         | I <sub>out</sub> (mA) | ESR (m $\Omega$ ) |

|------------------|-------------------|---------------|--------------------------------|-------------------|-----------------------|-------------------|

| C <sub>in</sub>  | 10 μF, X5R, 6.3 V | TDK<br>Murata | C2012X5R0J106<br>GRM21BR60J106 | 2.0 x 1.25 x 1.25 | -                     | -                 |

| C <sub>out</sub> | 22 μF, X5R, 6.3 V | TDK<br>Murata | C2012X5R0J226<br>GRM21BR60J226 | 2.0 x 1.25 x 1.25 | -                     | -                 |

| L                | 6.8 μΗ            | TDK           | VLCF4020-6R8                   | 4.0 x 4.0 x 2.0   | 500**                 | 146               |

|                  |                   | Coilcraft     | 0805PS-682                     | 3.4 x 3.0 x 1.8   | 210*                  | 1260              |

|                  |                   | Coilcraft     | LP04812                        | 4.8 x 4.8 x 1.2   | 340*                  | 225               |

|                  |                   | Sumida        | CLS4D11                        | 4.9 x 4.9 x 1.2   | 500**                 | 220               |

<sup>\*</sup>Output current calculated from V<sub>CC</sub> = 4.2 V<sub>max</sub>, 1.5 V<sub>out</sub> and Freq = 700 kHz (1.0 MHz – 20 %).

\*\*Calculated output current from V<sub>CC</sub> = 4.2 V<sub>max</sub> and Freq = 700 kHz exceeds 640 mA (I<sub>lim</sub> – 20%). Therefore maximum output for these conditions shown as 500 mA.

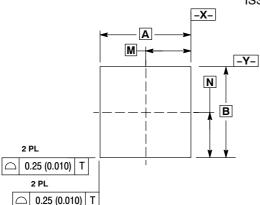

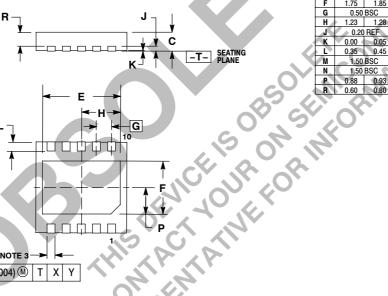

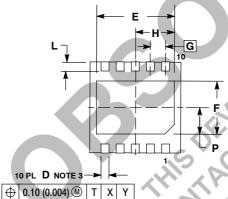

#### PACKAGE DIMENSIONS

# 10 PIN DFN **MN SUFFIX**

CASE 485C-01 **ISSUE O**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION D APPLIES TO PLATED TERMINAL

- AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |       | INCHES    |       |  |  |  |  |

|-----|-------------|-------|-----------|-------|--|--|--|--|

| DIM | MIN         | MAX   | MIN       | MAX   |  |  |  |  |

| Α   | 3.00        | BSC   | 0.118     | BSC   |  |  |  |  |

| В   | 3.00        | BSC   | 0.118     | BSC   |  |  |  |  |

| С   | 0.80        | 1.00  | 0.031     | 0.039 |  |  |  |  |

| D   | 0.20        | 0.30  | 0.008     | 0.012 |  |  |  |  |

| Е   | 2.45        | 2.55  | 0.096     | 0.100 |  |  |  |  |

| F   | 1.75        | 1.85  | 0.069     | 0.073 |  |  |  |  |

| G   | 0.50        | BSC a | 0.020     | BSC   |  |  |  |  |

| H_  | 1.23        | 1.28  | 0.048     | 0.050 |  |  |  |  |

| J   | 0.20        | REF   | 0.008     | REF   |  |  |  |  |

| K   | 0.00        | 0.05  | 0.000     | 0.002 |  |  |  |  |

| L   | 0.35        | 0.45  | 0.014     | 0.018 |  |  |  |  |

| M   | 1.50        | BSC   | 0.059 BSC |       |  |  |  |  |

| N_  | 1.50        | BSC 🦱 | 0.059 BSC |       |  |  |  |  |

| P   | 0.88        | 0.93  | 0.035     | 0.037 |  |  |  |  |

| R   | 0.60        | 0.80  | 0.024     | 0.031 |  |  |  |  |

| ~~  |             |       |           |       |  |  |  |  |

For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice on semiconductor and are registered traderlands of semiconduction Components industries, ILC (SCILLC). SciLLC reserves are right to finate changes without further holice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifically oxyr over itime. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative