# onsemi

# **Programmable USB Type-C<sup>®</sup>** and Power Delivery 3.1 Source Controller with PPS Support

# FUSB15101

The FUSB15101 is a highly integrated USB Power Delivery (PD) power source controller that can control the opto-coupler in the secondary side of an AC-DC adapter or a DC-DC port power regulator.

The FUSB15101 enables a complete solution for USB power sources through optimized hardware peripherals and complete open–source embedded firmware all in a compact solution.

It integrates a highly efficient Arm<sup>®</sup> Cortex<sup>®</sup>–M0+ processor with custom designed peripherals to seamlessly support USB PD 3.1 source applications. The FUSB15101 supports the PPS specification in USB PD, with a minimum of 3.3 V and a maximum of 21 V output voltage control. It includes Constant Voltage (CV) and Constant Current Limit (CL) control blocks, various protection mechanisms and high voltage tolerance on connector pins.

# **Key Features**

- 32-bit Arm Cortex-M0+ Processor

- 32 KB OTP (One Time Programmable) Program Memory

- USB PD 3.1 with PPS Support

- Power Management Unit with VIN Support from 3.3 V to 24 V

- Integrated VCONN Supply for Interrogating E–Marked Cables

- Idle and Sleep Modes to Meet CoC and DoE Requirements

- Peripherals

- USB Type-C / PD Detection and Communication Layer

- VBUS NMOS Gate Driver for Load Switch Control

- VBUS Discharge Functionality

- Programmable Constant Voltage & Constant Current Control

- Two 10-bit DAC's for Precise Voltage and Current Control

- Two NTC Temperature Measurements

- 10-bit ADC for Voltage, Current and Temperature Reporting

- Two General Purpose 32-bit Timers

- Watchdog Timer (WDT)

- I<sup>2</sup>C Master/Slave Peripheral

- ◆ UART on D+/- Pins

- Output Fault Protection

- ♦ Over–Voltage

- Under–Voltage

- Over–Current

- Over–Temperature

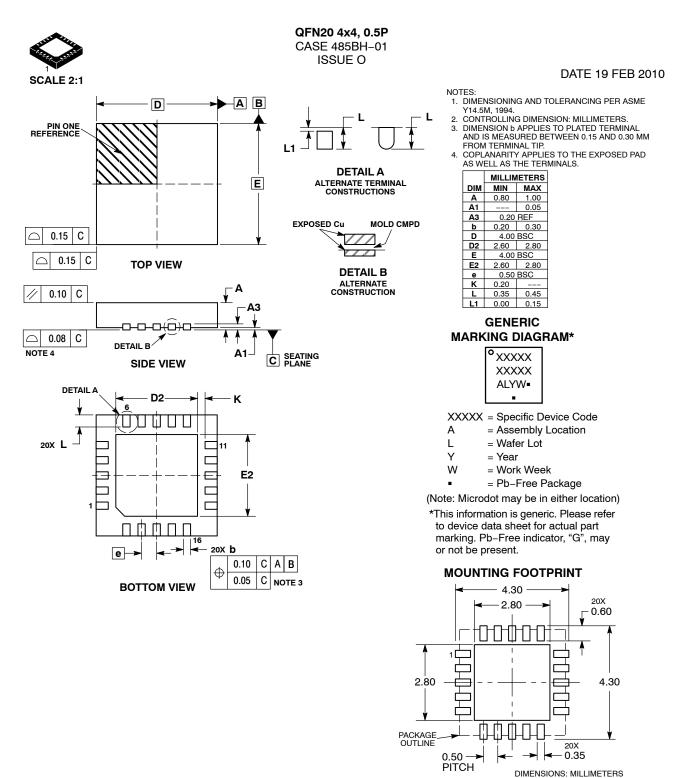

- 20-pin QFN Package (4 mm x 4 mm, 0.5 P)

QFN20 4x4, 0.5P CASE 485BH-01

MARKING DIAGRAM

(Note: Microdot may be in either location)

# **ORDERING INFORMATION**

| Device         | Package            | Shipping               |

|----------------|--------------------|------------------------|

| FUSB15101MNTWG | QFN20<br>(Pb–Free) | 4,000 / Tape &<br>Reel |

# **Typical Applications**

- Wall Chargers for Mobile Phones and Tablets and Computing Devices

- AC-DC USB PD Compliant Adapters

- Power Banks

- Cigarette Lighter Adapters

# Introduction

The FUSB15101 supports USB Type–C 2.1 and USB PD 3.1 specifications for power source applications with VBUS voltages ranging from 3.3 V to 21 V.

A highly flexible and open firmware environment allows hardware peripherals to be customized to meet a variety application needs.

Key integrated functions and peripherals are highlighted below:

- *Arm Cortex–M0+*: A 32–bit core with flexible clocking up to 12 MHz.

- *Memories*: A total of 32 kB of One Time Programmable Memory (OTP) is available to store program code; 2 KB of SRAM program memory.

- *USB Type–C and PD*: Integrated USB PD PHY and Type–C termination/comparators supporting latest USB–IF specification. Open and customizable USB PD firmware stack allows for tailored vendor specific functions.

- *Integrated VCONN Switch*: Provides power to cable eMarkers to interrogate current capabilities.

- *CC/CV Control*: Firmware controlled feedback voltage and current loop operation with programmable voltage and current DACs, Cable Drop Compensation, OVP, UVP and OCP.

- *Current Sense Amplifier*: Programmable for use with  $5 \text{ m}\Omega$  or  $10 \text{ m}\Omega$  sense resistors.

- *High Voltage Protection*: 26 V DC tolerant BLD, CC and D+/-.

- *ADC*: 10–bit ADC for accurate monitoring of VBUS voltage and current, external temperatures or voltages.

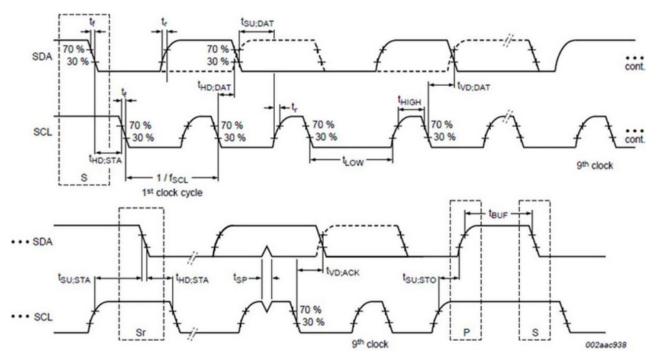

- *I*<sup>2</sup>*C*: Serial communication port capable of acting as a host or device.

- UART: UART peripheral available via HVDP/DM.

- *GPIOs*: Fully programmable I/Os with internal terminations. Configurable as input or output (CMOS or open-drain).

- *Multiple Timers*: Three independent 32-bit timers are available: 1 General Purpose, 1 Watchdog, and 1 Wake-up / General Purpose.

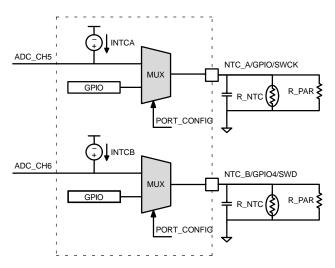

- *Dual External NTC*: Integrated current sources are used in conjunction with the ADC to monitor a variety of NTC resistors.

- *Low Power Operation Modes*: Programmable Sleep Modes allowing the device to minimize power usage as needed. Automatic USB–C detection and weak–up functionality from sleep modes.

- *Temperature Range*: Extended operating temperature range of -40°C to 105°C.

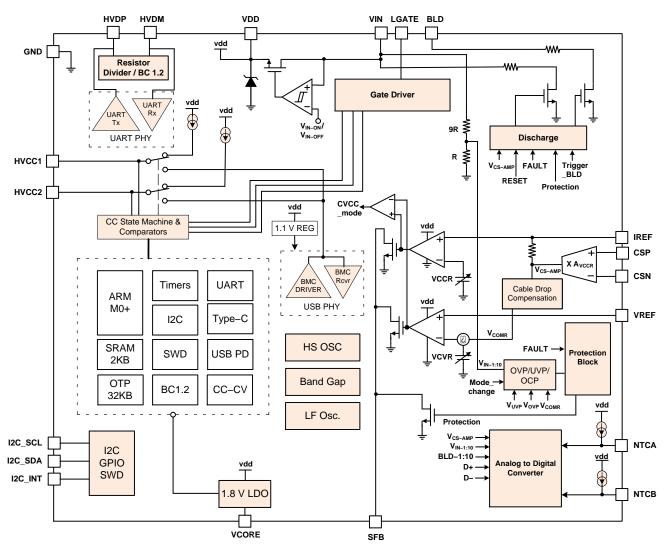

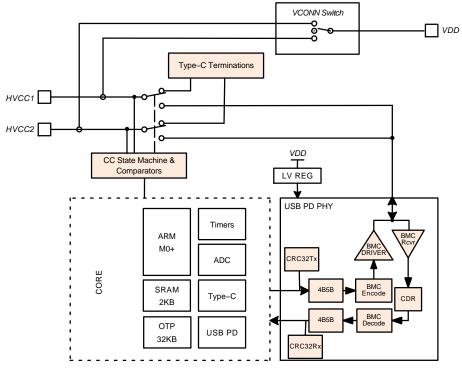

Figure 1. Simplified Block Diagram

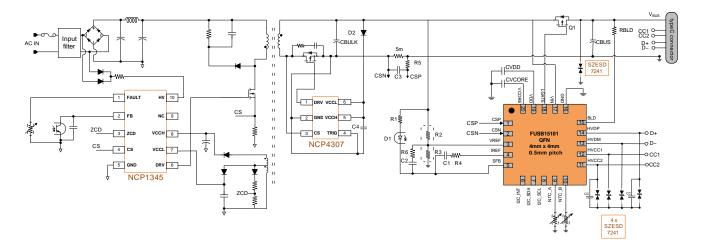

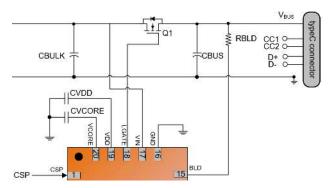

Figure 2. AC/DC Application Schematic

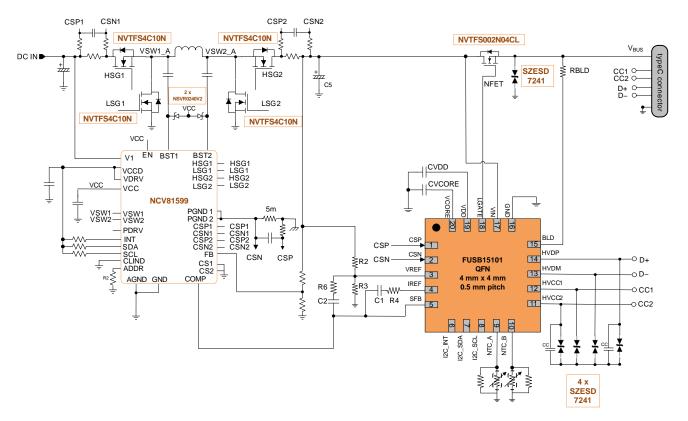

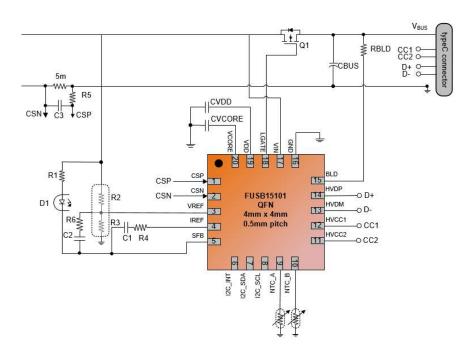

Figure 3. DC/DC Application Schematic

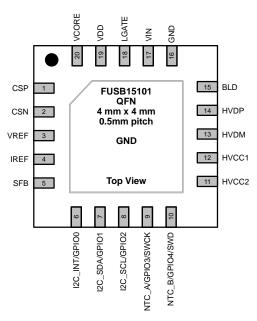

# **PIN CONNECTIONS**

Figure 4. QFN20 Top-View

# **PIN FUNCTION DESCRIPTION**

| Pin # | Name             | Description                                                                                                                                                                                           |

|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CSP              | Current Sensing Amplifier Positive Terminal. Connect this pin directly to the positive end of the current sense resistor with a short PCB trace.                                                      |

| 2     | CSN              | Current Sensing Amplifier Negative Terminal . Connect this pin directly to the negative end of the current sense resistor with a short PCB trace.                                                     |

| 3     | VREF             | Output Voltage Sensing Voltage. This pin is used for CV regulation, and it is tied to the internal CV loop amplifier non-inverting input terminal. It is tied to the output voltage resistor divider. |

| 4     | IREF             | Constant Current Amplifying Signal. The voltage level on this point is the amplified current sense signal. This pin is tied to the internal CC loop amplifier's non–inverting input terminal.         |

| 5     | SFB              | Secondary Feedback. Common output of the dual OTA open drain operational amplifiers. Typically, an opto-coupler is connected to this pin to provide feedback to the primary side PWM controller.      |

| 6     | I2C_INT/GPIO0    | I <sup>2</sup> C Interrupt Signal / General Purpose I/O                                                                                                                                               |

| 7     | I2C_SDA/GPIO1    | I <sup>2</sup> C Data Signal / General Purpose I/O                                                                                                                                                    |

| 8     | I2C_SCL/GPIO2    | I <sup>2</sup> C Clock Signal / General Purpose I/O                                                                                                                                                   |

| 9     | NTC_A/GPIO3/SWCK | An external NTC can be connected to this pin / General purpose I/O/SWCK.                                                                                                                              |

| 10    | NTC_B/GPIO4/SWD  | An external NTC can be connected to this pin / General purpose I/O/SWCK.                                                                                                                              |

| 11    | HVCC2            | Configuration Channel 2. This pin is used to detect USB Type–C devices and communicate over USB PD when applicable.                                                                                   |

| 12    | HVCC1            | Configuration Channel 1. This pin is used to detect USB Type–C devices and communicate over USB PD when applicable.                                                                                   |

| 13    | HVDM             | USB Communication Interface. This pin is tied to the USB D- data line input.                                                                                                                          |

| 14    | HVDP             | USB Communication Interface. This pin is tied to the USB D+ data line input.                                                                                                                          |

| 15    | BLD              | Bleeder pin. This pin is tied to VBUS after the load switch to discharge VBUS.                                                                                                                        |

| 16    | GND              | Ground reference for IC                                                                                                                                                                               |

| 17    | VIN              | Output voltage (Input voltage to the FUSB15101). This pin is tied to the output of the adapter to monitor its output voltage and supply internal bias.                                                |

| 18    | LGATE            | Load switch gate drive signal. This pin is tied to the gate of the load switch.                                                                                                                       |

| 19    | VDD              | Internal 5 V supply voltage.                                                                                                                                                                          |

| 20    | VCORE            | Internal 1.8 V supply voltage for the MCU core.                                                                                                                                                       |

| DAP   | GND              | Connect to GND Plane for thermal dissipation.                                                                                                                                                         |

# **ELECTRICAL SPECIFICATIONS**

# **MAXIMUM RATINGS** (Notes 1, 2)

| Symbol             | Parameter                                              | Min  | Тур | Max | Unit |

|--------------------|--------------------------------------------------------|------|-----|-----|------|

| V <sub>USB</sub>   | D+/- and CC Connector Pins                             | -0.3 | -   | 26  | V    |

| V <sub>IO</sub>    | I/O Voltage                                            | -0.5 | -   | 6.0 | V    |

| V <sub>NTC</sub>   | NTC_A and NTC_B Pin Voltage                            | -0.5 | -   | 6.0 | V    |

| $V_{VREF}$         | VREF Pin Input Voltage                                 | -0.5 | -   | 6.0 | V    |

| VIREF              | IREF Pin Input Voltage                                 | -0.5 | -   | 6.0 | V    |

| V <sub>CSx</sub>   | CSP and CSN Pins Input Voltages                        | -0.5 | -   | 6.0 | V    |

| V <sub>DC</sub>    | VDD Pin Input Voltage                                  | -0.5 | -   | 6.0 | V    |

| V <sub>CORE</sub>  | VCORE Pin Input Voltage                                | -0.5 | -   | 2.0 | V    |

| V <sub>LGATE</sub> | LGATE Pin Input Voltage                                | -0.3 | -   | 31  | V    |

| V <sub>SFB</sub>   | SFB Pin Input Voltage                                  | -0.3 | -   | 26  | V    |

| V <sub>IN</sub>    | VIN Pin Input Voltage                                  | -0.3 | -   | 26  | V    |

| V <sub>BLD</sub>   | BLD Pin Input Voltage                                  | -0.3 | -   | 26  | V    |

| ESD <sub>HBM</sub> | Human Body Model, ANSI/ESDA/JEDEC JS-001-2012 (Note 2) | 4    | -   | -   | kV   |

| ESD <sub>CDM</sub> | Charged Device Model, JESD22–C101 (Note 2)             | 2    | -   | -   | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe

Operating parameters. 2. Meets JEDEC standards JS-001-2012 and JESD 22-C101.

# **OPERATING RATINGS**

| Symbol               | Parameter                         | Min   | Тур | Max   | Unit |

|----------------------|-----------------------------------|-------|-----|-------|------|

| V <sub>IN</sub>      | Functional Range for Supply Input | 3.135 | 5.0 | 24    | V    |

| V <sub>HVCC</sub>    | Communication Channel Pins        | 0     | -   | 5.5   | V    |

| V <sub>HVDP/DM</sub> | D+/- USB Voltage                  | 0     | -   | 3.6   | V    |

| V <sub>IO</sub>      | GPIO, I2C, RESET                  | 0     | -   | 5.5   | V    |

| TJ                   | Junction Temperature              | -40   | -   | +125  | °C   |

| T <sub>A</sub>       | Operating Ambient Temperature     | -40   | -   | +105  | °C   |

| V <sub>CORE</sub>    | VCORE Pin Voltage                 | 0     | -   | 1.9   | V    |

| V <sub>VDD</sub>     | VDD Pin Voltage                   | 4.75  | -   | 5.5   | V    |

| V <sub>NTC_X</sub>   | NTC_/B Pin Voltage                | 0     | -   | 1.28  | V    |

| V <sub>REF</sub>     | VREF Pin Voltage                  | 0     | -   | 2.2   | V    |

| I <sub>REF</sub>     | IREF Pin Voltage                  | 0     | -   | 1.8   | V    |

| V <sub>CSP</sub>     | CSP Voltage                       | 0     | -   | 0.063 | V    |

| V <sub>CSN</sub>     | CSN Pin Voltage                   | -     | 0   | -     | V    |

| V <sub>SFB</sub>     | SFB Pin Voltage                   | 0     | -   | 22.5  | V    |

| V <sub>LGATE</sub>   | LGATE Pin Voltage                 | 0     | -   | 25    | V    |

| V <sub>BLD</sub>     | BLD Pin Voltage                   | 0     | -   | 22.5  | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# THERMAL CHARACTERISTICS (Note 3)

| Symbol        | Characteristic                         | Value | Unit |

|---------------|----------------------------------------|-------|------|

| $\theta_{JA}$ | Junction-to-Ambient Thermal Resistance | 38.6  | °C/W |

| $\theta_{JC}$ | Junction-to-Case Thermal Resistance    | 4.2   | °C/W |

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with two-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature T<sub>J</sub>(max) at a given ambient temperature T<sub>A</sub>.

| ELECTRICAL CHARACTERISTICS (Minimum and maximum values are at VIN = 3.135 V to 22.5 V, TA = -40°C to +105°C unless |  |

|--------------------------------------------------------------------------------------------------------------------|--|

| otherwise noted. Typical values are at TA = $25^{\circ}$ C, VIN = 5.0 V)                                           |  |

| Symbol | Parameter | Conditions | Min | Тур | Max | Unit |  |

|--------|-----------|------------|-----|-----|-----|------|--|

|        |           |            |     |     |     |      |  |

#### INTERNAL POWER SUPPLY

VIN

| I <sub>IN-OP-5</sub> v        | Operating Supply Current<br>at 5 V                | Attached, PD Communication<br>in progress, ADCs enabled,<br>NTCs enabled, CC & CV enabled,<br>Gate Driver Enabled. VIN = 5 V,<br>VCS = $-25$ mV, RCS = $5$ m $\Omega$                             | _     | 3.5   | _     | mA |

|-------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|----|

| I <sub>IN-OP-20V</sub>        | Operating Supply Current at 20 V                  | Attached, PD Communication<br>in progress, ADCs enabled,<br>NTCs enabled, CC & CV enabled,<br>Gate Driver Enabled. VIN = 20 V,<br>VCS = $-25$ mV, RCS = $5$ m $\Omega$                            | _     | 4.4   | -     | mA |

| I <sub>IN–Sleep</sub>         | Operating Supply Current<br>at Sleep Mode         | No Device Attached, Type–C enabled<br>& Gate Driver OFF or BC1.2 Detection<br>enabled & Gate Driver ON; VIN = 5 V,<br>VCS = 0 V excluding IP–CC1 and<br>IP–CC2 Supply Current and ISFB<br>Current | -     | -     | 0.75  | mA |

| V <sub>IN–ON</sub>            | IC Turn–On Threshold Voltage                      | Increase VIN                                                                                                                                                                                      | 2.9   | 3.2   | 3.4   | V  |

| V <sub>IN-OFF</sub>           | IC Turn–Off Threshold Voltage                     | VIN > VIN–ON then decrease VIN                                                                                                                                                                    | 2.75  | 2.875 | 3.0   | V  |

| t <sub>VIN-off-Debounce</sub> | IC Turn–Off Debounce Time                         | VIN > VIN–ON then decrease VIN                                                                                                                                                                    | -     | -     | 200   | μs |

| t√IN–OCP–Debounce             | Hardware OCP Debouce on Both Edges                | Entering and exiting OCP Mode                                                                                                                                                                     | -     | 50    | 100   | μs |

| V <sub>LATCH-OFF</sub>        | Output Voltage Release<br>Latch Mode              | VIN Falling                                                                                                                                                                                       | -     | -     | 1.55  | V  |

| t <sub>VIN-OVP-Debounce</sub> | VIN OVP Debounce Time                             |                                                                                                                                                                                                   | 35    | 75    | 110   | μs |

| V <sub>IN-OVP-MAX</sub>       | VIN Maximum Overvoltage Pro-<br>tection           |                                                                                                                                                                                                   | 24    | -     | 26    | V  |

| V <sub>IN-UVP-PPS</sub>       | Turn–Off Threshold Voltage when in a PPS Contract | VIN Falling in a PPS contract                                                                                                                                                                     | 2.805 | 2.97  | 3.135 | V  |

#### VIN UVP SECTION

| K <sub>IN-UVP-60</sub> | Ratio VIN                                | VCS = 0 mV | 57.5 | 60 | 62.5 | % |

|------------------------|------------------------------------------|------------|------|----|------|---|

| K <sub>IN-UVP-65</sub> | Under-Voltage-Protection (UVP)<br>to VIN | VCS = 0 mV | 60   | 65 | 70   |   |

| K <sub>IN-UVP-70</sub> |                                          | VCS = 0 mV | 67.5 | 70 | 72.5 |   |

| K <sub>IN-UVP-80</sub> |                                          | VCS = 0 mV | 77   | 80 | 83   |   |

| K <sub>IN-UVP-90</sub> |                                          | VCS = 0 mV | 87   | 90 | 93   |   |

| K <sub>IN-UVP-95</sub> |                                          | VCS = 0 mV | 92   | 95 | 98   |   |

| <b>ELECTRICAL CHARACTERISTICS</b> (Minimum and maximum values are at VIN = 3.135 V to 22.5 V, TA = -40°C to +105°C unless |

|---------------------------------------------------------------------------------------------------------------------------|

| otherwise noted. Typical values are at TA = $25^{\circ}$ C, VIN = 5.0 V) (continued)                                      |

| Symbol                  | Parameter                               | Conditions | Min | Тур | Max | Unit |

|-------------------------|-----------------------------------------|------------|-----|-----|-----|------|

| VIN OVP SECTION         | NC                                      |            |     |     |     |      |

| K <sub>IN-OVP-105</sub> | Ratio VIN                               | VCS = 0 mV | 102 | 105 | 108 | %    |

| K <sub>IN-OVP-110</sub> | Over-Voltage-Protection (OVP)<br>to VIN | VCS = 0 mV | 107 | 110 | 113 |      |

| K <sub>IN-OVP-115</sub> |                                         | VCS = 0 mV | 112 | 115 | 118 |      |

| K <sub>IN-OVP-120</sub> |                                         | VCS = 0 mV | 117 | 120 | 123 |      |

| K <sub>IN-OVP-125</sub> |                                         | VCS = 0 mV | 122 | 125 | 128 |      |

| K <sub>IN-OVP-130</sub> |                                         | VCS = 0 mV | 127 | 130 | 133 |      |

| K <sub>IN-OVP-135</sub> |                                         | VCS = 0 mV | 132 | 135 | 138 |      |

#### VDD

| V <sub>DD</sub> | VDD Source Voltage > 6 V         | VIN = 6 V  to  22.5 V, $IVDD = 10  mA$ | 4.75 | 5.125 | 5.5 | V  |

|-----------------|----------------------------------|----------------------------------------|------|-------|-----|----|

| I <sub>DD</sub> | VDD Source Current<br>Capability | VIN = 3.3 V, VDD = 2.9 V               | 10   | -     | -   | mA |

# TYPE-C AND PD

USB PD PHY

# TRANSMITTER

| UI                          | Unit Interval                                                                                                                    |                                                                               | 3.03 | 3.33  | 3.7  | μs |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|-------|------|----|

| PBitRate                    | Maximum Difference between the<br>bit-rate During the Payload and<br>Last 32 Bits of Preamble                                    |                                                                               | -    | -     | 0.25 | %  |

| t <sub>EndDriveBMC</sub>    | Time to Cease Driving the Line<br>after the End of the Last Bit of<br>the Frame                                                  |                                                                               | -    | -     | 23   | μs |

| <sup>t</sup> HoldLowBMC     | Time to Cease Driving the Line<br>after the Final High–to–low<br>Transition                                                      |                                                                               | 1    | -     | -    | μs |

| t <sub>Inter</sub> FrameGap | Any PD Transmission Cannot be<br>Sent out before a Dead Time of<br>at Least tInterFrameGap from<br>Receiving or Sending a Packet |                                                                               | 25   | -     | -    | μs |

| <sup>t</sup> Fall–CC        | Fall Time                                                                                                                        | 10 % and 90 % amplitude points,<br>minimum is under an unloaded<br>condition. | 300  | -     | -    | ns |

| t <sub>Rise-CC</sub>        | Rise Time                                                                                                                        | 10 % and 90 % amplitude points,<br>minimum is under an unloaded<br>condition. | 300  | -     | -    | ns |

| t <sub>StartDrive</sub>     | Time before the Start of the First<br>Bit of the Preamble when the<br>Transmitter Shall Start Driving<br>the Line                |                                                                               | -1   | _     | 1    | μs |

| V <sub>Swing</sub>          | BMC Voltage Swing                                                                                                                |                                                                               | 1.05 | 1.125 | 1.2  | V  |

| Z <sub>Driver</sub>         | TX Output Impedance at 750 kHz<br>with an External 220 pF or<br>Equivalent Load                                                  |                                                                               | 33   | -     | 75   | Ω  |

| RECEIVER                    | -                                                                                                                                | •                                                                             | -    | -     |      | -  |

| C <sub>Receiver</sub>       | Receiver Capacitance when                                                                                                        | Vrms = 0.371; Vdc = 0.5 V;<br>Freq = 1 MHz                                    | -    | 75    | -    | pF |

| CReceiver                      | Driver isn't Turned On             | Freq. = 1 MHz | -   | 75 | _  | рі |

|--------------------------------|------------------------------------|---------------|-----|----|----|----|

| t <sub>RxFilter</sub>          | Rx Bandwidth Limiting Filter       |               | 100 | -  | -  | ns |

| t <sub>Transition</sub> Window | Time Window for Detecting Non–idle |               | 12  | -  | 20 | μS |

| Z <sub>BmcRx</sub> (Note 5)    | Receiver Input Impedance           |               | 1   | 1  | -  | MΩ |

| •                                                                                                                                    | Parameter                                                                                                                                                                    | Conditions                                                               | Min                    | Тур         | Мах                 | Unit               |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------|-------------|---------------------|--------------------|

| TYPE-C FRONT                                                                                                                         | END                                                                                                                                                                          | · · · · · ·                                                              |                        |             |                     |                    |

| R <sub>BLD-LEAK</sub>                                                                                                                | BLD Pin Impedance to GND when VBUS is not Sourced                                                                                                                            | BLD = 0 V to 5.75 V; LGATE = OFF                                         | 72.4                   | -           | _                   | kΩ                 |

| I <sub>180_CCX</sub>                                                                                                                 | SRC 180 µA CC Current (1.5 A)                                                                                                                                                |                                                                          | 166                    | 180         | 194                 | μΑ                 |

| I <sub>330_CCX</sub>                                                                                                                 | SRC 330 µA CC Current (3 A)                                                                                                                                                  |                                                                          | 304                    | 330         | 356                 | μΑ                 |

| R <sub>DEVICE</sub>                                                                                                                  | Device Pull-down Resistance                                                                                                                                                  |                                                                          | 4.6                    | 5.1         | 5.6                 | kΩ                 |

| R <sub>A</sub>                                                                                                                       | Ra                                                                                                                                                                           |                                                                          | 800                    | -           | 1200                | Ω                  |

| Z <sub>OPEN</sub>                                                                                                                    | CC Resistance for Disabled<br>State, when VDD is Valid                                                                                                                       |                                                                          | 126                    | -           | -                   | kΩ                 |

| I <sub>VCONN</sub>                                                                                                                   | Maximum Current for VCONN<br>Source                                                                                                                                          | VIN = 4.75 V                                                             | 34                     | -           | _                   | mA                 |

| V <sub>RdSRC3.0</sub>                                                                                                                | Source Attach Threshold for CC<br>Pin at 3 A Current                                                                                                                         |                                                                          | 2.45                   | 2.6         | 2.75                | V                  |

| V <sub>RaSRC3.0</sub>                                                                                                                | Source Ra Threshold for CC Pin at 3 A Current                                                                                                                                |                                                                          | 0.75                   | 0.8         | 0.85                | V                  |

| V <sub>OVP_CC</sub>                                                                                                                  | CCx OVP Threshold                                                                                                                                                            |                                                                          | 5.6                    | -           | 6.0                 | V                  |

| t <sub>VCONN-OCP</sub>                                                                                                               | VCONN OCP Debounce Time                                                                                                                                                      |                                                                          | 2.5                    | 3.5         | 4.5                 | ms                 |

| CC-OVP-Debounce                                                                                                                      | CC1/CC2 OVP Debounce Time                                                                                                                                                    |                                                                          | _                      | 100         | 125                 | μs                 |

| t <sub>CC-OVP-</sub><br>Debounce-Recover                                                                                             | Debounce Time after CC OVP<br>Event                                                                                                                                          |                                                                          | -                      | 15          | _                   | ms                 |

| IVCONN_OCP                                                                                                                           | Over Current Protection (OCP)<br>Limit at which VCONN Switch<br>Shuts Off                                                                                                    |                                                                          | 50                     | -           | _                   | mA                 |

| V <sub>VCONN</sub>                                                                                                                   | Voltage Range for VCONN<br>Source                                                                                                                                            |                                                                          | 3.0                    | -           | 5.5                 | V                  |

| VBUS CONTRO                                                                                                                          | L                                                                                                                                                                            |                                                                          |                        |             |                     |                    |

| LOAD SWITCH                                                                                                                          |                                                                                                                                                                              |                                                                          |                        |             |                     |                    |

| V <sub>LGATE-3.3V</sub>                                                                                                              | Gate High Voltage at 3.3 V                                                                                                                                                   | VIN = 3.3 V                                                              | 8.1                    | -           | -                   | V                  |

|                                                                                                                                      | Gate High Voltage at 3.3 V<br>Gate High Voltage at 20 V                                                                                                                      | VIN = 3.3 V<br>VIN = 20 V                                                | 8.1<br>23.5            |             | -                   | V<br>V             |

| V <sub>LGATE-3.3V</sub><br>V <sub>LGATE-20V</sub>                                                                                    |                                                                                                                                                                              |                                                                          | -                      |             |                     | -                  |

| V <sub>LGATE-3.3V</sub><br>V <sub>LGATE-20V</sub>                                                                                    | Gate High Voltage at 20 V<br>Gate High Voltage                                                                                                                               | VIN = 20 V                                                               | 23.5                   | -           | _                   | V                  |

| V <sub>LGATE</sub> -3.3V<br>V <sub>LGATE</sub> -20V<br>V <sub>LGATE</sub> -OVP-Max                                                   | Gate High Voltage at 20 V<br>Gate High Voltage                                                                                                                               | VIN = 20 V                                                               | 23.5                   | -           | _                   | V                  |

| V <sub>LGATE</sub> -3.3V<br>V <sub>LGATE</sub> -20V<br>V <sub>LGATE</sub> -OVP-Max<br><b>BLEEDER</b>                                 | Gate High Voltage at 20 V<br>Gate High Voltage<br>at VIN–OVP–Max                                                                                                             | VIN = 20 V<br>VIN = VIN-OVP-Max                                          | 23.5                   | -           | _                   | V<br>V<br>mA       |

| V <sub>LGATE</sub> -3.3V<br>V <sub>LGATE</sub> -20V<br>V <sub>LGATE</sub> -OVP-Max<br>BLEEDER<br>IVIN-Sink<br>I <sub>BLD</sub> -Sink | Gate High Voltage at 20 V<br>Gate High Voltage<br>at VIN–OVP–Max<br>VIN Sinking Current During tBLD<br>BLD Sinking Current During tBLD                                       | VIN = 20 V<br>VIN = VIN–OVP–Max<br>Bleeding current on VIN at VIN = 20 V | 23.5<br>-<br>60        | -           | -<br>31.5<br>-      | V<br>V<br>mA       |

| V <sub>LGATE</sub> -3.3V<br>V <sub>LGATE</sub> -20V<br>V <sub>LGATE</sub> -OVP-Max<br>BLEEDER<br>IVIN-Sink<br>I <sub>BLD</sub> -Sink | Gate High Voltage at 20 V<br>Gate High Voltage<br>at VIN–OVP–Max<br>VIN Sinking Current During tBLD<br>BLD Sinking Current During tBLD                                       | VIN = 20 V<br>VIN = VIN–OVP–Max<br>Bleeding current on VIN at VIN = 20 V | 23.5<br>-<br>60        | -           | -<br>31.5<br>-      | V<br>V<br>mA       |

| VLGATE-3.3V<br>VLGATE-20V<br>VLGATE-OVP-Max<br>BLEEDER<br>IVIN-Sink<br>IBLD-Sink<br>VBUS MEASUR<br>VSafe0V-THR                       | Gate High Voltage at 20 V<br>Gate High Voltage<br>at VIN–OVP–Max<br>VIN Sinking Current During tBLD<br>BLD Sinking Current During tBLD<br>EMENT<br>Safe Operating Voltage at | VIN = 20 V<br>VIN = VIN–OVP–Max<br>Bleeding current on VIN at VIN = 20 V | 23.5<br>-<br>60<br>250 | -<br>-<br>- | -<br>31.5<br>-<br>- | V<br>V<br>MA<br>MA |

| VLGATE-3.3V<br>VLGATE-20V<br>VLGATE-OVP-Max<br>BLEEDER<br>IVIN-Sink<br>IBLD-Sink<br>VBUS MEASUR                                      | Gate High Voltage at 20 V<br>Gate High Voltage<br>at VIN–OVP–Max<br>VIN Sinking Current During tBLD<br>BLD Sinking Current During tBLD<br>EMENT<br>Safe Operating Voltage at | VIN = 20 V<br>VIN = VIN–OVP–Max<br>Bleeding current on VIN at VIN = 20 V | 23.5<br>-<br>60<br>250 | -<br>-<br>- | -<br>31.5<br>-<br>- | V<br>V<br>MA<br>MA |

| <b>ELECTRICAL CHARACTERISTICS</b> (Minimum and maximum values are at VIN = 3.135 V to 22.5 V, TA = -40°C to +105°C unless |

|---------------------------------------------------------------------------------------------------------------------------|

| otherwise noted. Typical values are at TA = $25^{\circ}$ C, VIN = 5.0 V) (continued)                                      |

# www.onsemi.com

°C

°C

\_

\_

\_

\_

145

10

Temperature Threshold for Internal Circuit Protection

Over Temperature Hysteresis

T<sub>SHUT</sub>

T<sub>HYS</sub>

| ELECTRICAL CHARACTERISTICS (Minimum and maximum values are at VIN = 3.135 V to 22.5 V, TA = -40°C to +105°C unless |

|--------------------------------------------------------------------------------------------------------------------|

| otherwise noted. Typical values are at TA = 25 $^{\circ}$ C, VIN = 5.0 V) (continued)                              |

| Symbol                   | Parameter                                     | Conditions                                                           | Min                    | Тур  | Max       | Unit |

|--------------------------|-----------------------------------------------|----------------------------------------------------------------------|------------------------|------|-----------|------|

| BC1.2                    |                                               |                                                                      | •                      |      |           |      |

| R <sub>DCP</sub>         | DCP Emulation Resistance                      | $V_{HVDP}$ or $V_{HVDM} = 0$ V, 1.0 V,<br>ION = 2 mA                 | -                      | 75   | 140       | Ω    |

| R <sub>Dx-DWN</sub>      | DP/DM Pull Down Resistance                    | $V_{HVDP}$ or $V_{HVDM} = 0 V - 3.6 V$                               | 16                     | 19.5 | 23        | kΩ   |

| I <sub>DX-SNK</sub>      | Sink Current to Dx                            | VDD = 3.0 V to 5.5 V                                                 | 25                     | 100  | 175       | μA   |

| R <sub>DAT-LKG</sub>     | Resistor Weak Pull–Down on D+<br>and D–       | $V_{HVDP}$ or $V_{HVDM} = 0$ V to 3.6 V                              | 300                    | 700  | 1100      | kΩ   |

| V <sub>Dx-SRC</sub>      | Source Voltage                                | VDD = 3.0 V to 5.5 V                                                 | 0.5                    | 0.6  | 0.7       | V    |

| USB2.0 PORT C            | HARACTERISTICS                                |                                                                      |                        |      |           | -    |

| I <sub>OFF-USB</sub>     | Power-Off Leakage Current                     | All data ports, $V_{HVDP}$ or $V_{HVDM} = 3.6 V$ , $VDD = 0 V$       | -                      | -    | 18        | μΑ   |

| C <sub>USB2</sub>        | HVDP/HVDM Capacitance                         | f=240 MHz;<br>V <sub>HVDP</sub> or V <sub>HVDM</sub> = 400 mV Vpk–pk | -                      | 2.4  | -         | pF   |

| V <sub>OVP-VIH-USB</sub> | HVDP/DM Rising over Voltage<br>Threshold      |                                                                      | 4.4                    | 4.55 | 4.7       | V    |

| V <sub>OVP-VIL-USB</sub> | HVDP/DM Falling over Voltage<br>Threshold     |                                                                      | -                      | 4.35 | _         |      |

| t <sub>OVP-USB</sub>     | USB OVP Event Recovery Time                   | HVDP/HVDM Over Voltage debounce                                      | -                      | 100  | 125       | μs   |

| OVP-USB-Recover          | USB OVP Event Recovery Time                   | USB OVP event removed                                                | -                      | 15   | -         | ms   |

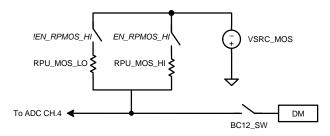

| MOISTURE DET             | ECTION (HVDM PIN)                             |                                                                      |                        |      |           | -    |

| V <sub>SRC-MOIS</sub>    | Voltage Source for Moisture<br>Detection      |                                                                      | .9                     | 1.0  | 1.1       | V    |

| R <sub>PU-MOIS</sub>     | High Pull up Resistor for Moisture Detection  |                                                                      | 250                    | 300  | 352       | kΩ   |

| R <sub>PU-MOS-LO</sub>   | Low Pull Up Resistor for Moisture Detection   |                                                                      | 2.25                   | 2.5  | 2.75      | kΩ   |

| SERIAL WIRE D            | EBUG INTERFACE                                | -                                                                    |                        |      |           |      |

| f <sub>SWD-CLK</sub>     | Serial Wire Debug Input Clock<br>Frequency    |                                                                      | -                      | -    | 4         | MHz  |

| t <sub>SWDI-SET</sub>    | Serial Wire Debug Data Setup<br>Timing        |                                                                      | 0.25 x (1/<br>SWD_CLK) | -    | -         | ns   |

| t <sub>SWDI-HOLD</sub>   | Serial Wire Debug Data Hold<br>Timing         |                                                                      | 0.25 x (1/<br>SWD_CLK) | -    | -         | ns   |

| V <sub>SWD-VIH</sub>     | Serial Wire Debug Input Voltage               | VIN = 3.1 V to 22.5 V                                                | 0.7 x VDD              | -    | -         | V    |

| V <sub>SWD-VIL</sub>     | Threshold                                     | VIN = 3.1 V to 22.5 V                                                | -                      | -    | 0.3 x VDD |      |

| V <sub>SWD-HYS</sub>     | Serial Wire Debug Input Voltage<br>Hysteresis | VIN = 3.1 V to 22.5 V                                                | -                      | 300  | -         | mV   |

| I <sub>SWD-LKG</sub>     | Serial Wire Debug Input Leakage               | VIN = 3.1 V to 22.5 V<br>Input Voltage 0 V to 5.5 V                  | -10                    | -    | +10       | μΑ   |

| V <sub>SWD-VOH</sub>     | Serial Wire Debug Output<br>Voltage High      | VIN = 3.1 V to 22.5 V, lout = -2 mA                                  | VDD – 0.5              | -    | -         | V    |

|                          |                                               |                                                                      |                        |      |           |      |

| <b>ELECTRICAL CHARACTERISTICS</b> (Minimum and maximum values are at VIN = 3.135 V to 22.5 V, TA = -40°C to +105°C unless |

|---------------------------------------------------------------------------------------------------------------------------|

| otherwise noted. Typical values are at TA = $25^{\circ}$ C, VIN = 5.0 V) (continued)                                      |

| Symbol | Parameter | Conditions | Min | Тур | Max | Unit |

|--------|-----------|------------|-----|-----|-----|------|

| I/OS   |           |            |     |     |     |      |

GPIO

| V <sub>GPIO-VIH</sub> | High Level Input Voltage | VIN = 3.1 V to 22.5 V                                | 0.7 x VDD | -   | -         | V  |

|-----------------------|--------------------------|------------------------------------------------------|-----------|-----|-----------|----|

| V <sub>GPIO-IL</sub>  | Low Level Input Voltage  | VIN = 3.1 V to 22.5 V                                | -         | -   | 0.3 x VDD | V  |

| V <sub>GPIO-VOH</sub> | Output High Voltage      | VIN = 3.1 V to 22.5 V, lout = -2 mA                  | VDD – 0.5 | -   | -         | V  |

| V <sub>GPIO-VOL</sub> | Ouptut Low Voltage       | VIN = 3.1 V to 22.5 V, lout = +4 mA                  | -         | -   | 0.4       | V  |

| V <sub>GPIO-HYS</sub> | Input Hysteresis         | VIN = 3.1 V to 22.5 V, 5.0 V Typ                     | -         | 300 | -         | mV |

| I <sub>IN-GPIO</sub>  | Input Leakage            | VIN = 3.1 V to 22.5 V,<br>Input Voltage 0 V to 5.5 V | -10       | -   | 5         | μΑ |

| I <sub>OFF-GPIO</sub> | Off Input Leakage        | VIN = 0 V, Input Voltage 0 V to 5.5 V                | -5        | -   | 5         | μA |

| R <sub>PD-GPIO</sub>  | Pull–Down Resistance     | PORT_PDx = 1                                         | -         | 100 | -         | kΩ |

| R <sub>PU-GPIO</sub>  | Pull–Up Resistance       | PORT_PUx = 1                                         | -         | 100 | -         | kΩ |

| C <sub>GPIO</sub>     | Pin Capacitance          |                                                      | _         | 5   | _         | pF |

| I <sub>NTCA</sub> | Current Source on NTCA | 55 | 60 | 65 | μΑ |

|-------------------|------------------------|----|----|----|----|

| I <sub>NTCB</sub> | Current Source on NTCB | 55 | 60 | 65 | μΑ |

| l <sup>2</sup> C  |                        |    |    |    |    |

10

| I <sub>CCTI2C</sub>  | VDD Current when SDA or SCL is HIGH                                  | VIN = 3.1 V to 22.5 V,<br>VSDA/VSCL = 1.8 V     | -10 | -   | 10  | μΑ |

|----------------------|----------------------------------------------------------------------|-------------------------------------------------|-----|-----|-----|----|

| I <sub>I2C</sub>     | Input Current of SDA and SCL<br>Pins                                 | VIN = 3.1 V to 22.5 V,<br>VI = 0 V to 5.5V      | -10 | -   | 10  | μΑ |

| V <sub>IH–I2C</sub>  | High-Level Input Voltage                                             | VIN = 3.1 V to 22.5 V                           | 1.2 | -   | -   | V  |

| V <sub>IL-I2C</sub>  | Low-Level Input Voltage                                              | VIN = 3.1 V to 22.5 V                           | -   | -   | 0.4 | V  |

| V <sub>OL1-I2C</sub> | Low–Level Output Voltage at<br>3 mA Sink Current (Open–Drain)        | VIN = 3.1 V to 22.5 V                           | -   | -   | 0.3 | V  |

| V <sub>hys-I2C</sub> | Hysteresis of Schmitt Trigger<br>Inputs                              | VIN = 3.1 V to 22.5 V                           | -   | 0.2 | -   | V  |

| I <sub>OL-SDA</sub>  | Low–Level Output Current<br>(Open–Drain)                             | VIN = 3.1 V to 22.5 V,<br>V_OL = 0.4 V (Note 4) | 20  | -   | -   | mA |

| V <sub>OL-INT</sub>  | INT_N Output Low Voltage                                             | VIN = 3.1 V to 22.5 V, I_OL = 4 mA              | -   | -   | 0.4 | V  |

| C <sub>I2C</sub>     | Capacitance for Each I/O Pin                                         | VIN = 3.1 V to 22.5 V                           | -   | 5   | -   | pF |

| V <sub>OL2-I2C</sub> | Low–Level Output Voltage at<br>2 mA Sink Current (Open–Drain)        | VIN = 3.1 V to 22.5 V                           | -   | -   | 0.3 | V  |

| t <sub>SP-I2C</sub>  | Pulse Width of Spikes that Must<br>Be Suppressed by the Input Filter |                                                 | -   | -   | 50  | ns |

| V <sub>IH_INT</sub>  | High-Level Input Voltage                                             | VIN = 3.1 V to 22.5 V                           | 1.2 | -   | -   | V  |

| V <sub>IL_INT</sub>  | Low-Level Input Voltage                                              | VIN = 3.1 V to 22.5 V                           | -   | -   | 0.4 | V  |

# CV/CC CONTROL

# CONSTANT CURRENT SENSE SECTION

| A <sub>V-CCR-40</sub> | Current Sense Amplifier Gain                                                     | $RCS = 5 m\Omega$                                  | _    | 40   | _    | V/V |

|-----------------------|----------------------------------------------------------------------------------|----------------------------------------------------|------|------|------|-----|

| A <sub>V-CCR-20</sub> |                                                                                  | $RCS = 10 m\Omega$                                 | _    | 20   | _    |     |

| I <sub>CS-1A</sub>    | Current Threshold on Sensing<br>Resistor between CSP and CSN<br>at IOUT = 1.00 A | Constant Current Limit mode<br>and VCC = 5 V, 20 V | 0.85 | 1.00 | 1.15 | A   |

| Symbol                 | Parameter                                                                             | Conditions                                                              | Min   | Тур   | Max   | Unit |

|------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------|-------|-------|------|

| CONSTANT CU            | RRENT SENSE SECTION                                                                   |                                                                         |       |       |       |      |

| I <sub>CS-2A</sub>     | Current Threshold on Sensing<br>Resistor between CSP and CSN<br>at IOUT = 2.00 A      | Constant Current Limit mode<br>and VCC = 5 V, 20 V                      | 1.85  | 2.00  | 2.15  | A    |

| I <sub>CS-3A</sub>     | Current Threshold on Sensing<br>Resistor between CSP and CSN<br>at IOUT = 3.00 A      | Constant Current Limit mode<br>and VCC = 5 V, 20 V                      | 2.85  | 3.00  | 3.15  | A    |

| I <sub>CS-4A</sub>     | Current Threshold on Sensing<br>Resistor between CSP and CSN<br>at IOUT = 4.00 A      | Constant Current Limit mode<br>and VCC = 5 V, 20 V                      | 3.80  | 4.00  | 4.20  | A    |

| I <sub>CS-5A</sub>     | Current Threshold on Sensing<br>Resistor between CSP and CSN<br>at IOUT = 5.00 A      | Constant Current Limit mode<br>and VCC = 5 V, 20 V                      | 4.75  | 5.00  | 5.25  | A    |

| I <sub>CS-STEP</sub>   | Current Threshold on Sensing Resistor between CSP and CSN at $\triangle$ IOUT = 50 mA | Constant Current Limit mode<br>and VCC = 5 V                            | 48    | 50    | 52    | mA   |

| I <sub>CS-EN-BLD</sub> | Real Current Threshold to<br>Enable Bleeder                                           | VBUS_BLD_EN = 1                                                         | 200   | 450   | 700   | mA   |

| t <sub>CS-EN-BLD</sub> | Enable Bleeder Debounce Time                                                          | VBUS_BLD_EN = 1                                                         | -     | 0.6   | 1     | ms   |

| OVER CURREN            | T PROTECTION SENSING SECTIO                                                           | N .                                                                     |       |       |       |      |

| V <sub>CS-3.6A</sub>   | Voltage Difference between CSP and CSN at Nominal 3.6 A                               | $Rcs = 5 m\Omega$ ; ccdac_refp = 10b (120%);<br>csa_multiplier =1 (40x) | 16.92 | 18    | 19.08 | mV   |

| V <sub>CS-6A</sub>     | Voltage Difference between CSP and CSN at Nominal 6.0 A                               | $Rcs = 5 m\Omega; ccdac_refp = 10b (120\%); csa_multiplier =1 (40x)$    | 28.5  | 30    | 31.5  | mV   |

| CONSTANT VO            | LTAGE SENSE SECTION                                                                   |                                                                         |       |       |       |      |

| V <sub>CVR-3.3V</sub>  | CV Reference Voltage at 3.3 V                                                         | VIN = 3.3 V, VCS = 0 V                                                  | 0.32  | 0.33  | 0.34  | V    |

| V <sub>CVR-5.0V</sub>  | CV Reference Voltage at 5.0 V                                                         | VIN = 5.0 V, VCS = 0 V                                                  | 0.485 | 0.5   | 0.515 | V    |

| V <sub>CVR-9.0V</sub>  | CV Reference Voltage at 9.0 V                                                         | VIN = 9.0 V, VCS = 0 V                                                  | 0.873 | 0.9   | 0.927 | V    |

| V <sub>CVR-12V</sub>   | CV Reference Voltage at 12 V                                                          | VIN = 12 V, VCS = 0 V                                                   | 1.164 | 1.200 | 1.236 | V    |

| V <sub>CVR-15V</sub>   | CV Reference Voltage at 15 V                                                          | VIN = 15 V, VCS = 0 V                                                   | 1.455 | 1.500 | 1.545 | V    |

| V <sub>CVR-20V</sub>   | CV Reference Voltage at 20 V                                                          | VIN = 20 V, VCS = 0 V                                                   | 1.940 | 2.000 | 2.060 | V    |

# CABLE DROP COMPENSATION

Step

CV Reference Voltage of 20 mV

V<sub>CVR-STEP-20mV</sub>

| V <sub>COMR-CDC-0</sub>    | Cable Compensation Voltage on VCVR for VOUT = 0 mV/A   | RCS = 5 m $\Omega$ , VCS = -5 mV                      | _ | 0  | - | mV |

|----------------------------|--------------------------------------------------------|-------------------------------------------------------|---|----|---|----|

| V <sub>COMR</sub> -CDC-50  | Cable Compensation Voltage on VCVR for VOUT = 50 mV/A  | RCS = 5 m $\Omega$ , VCS = -5 mV                      | - | 5  | - | mV |

| V <sub>COMR-CDC-100</sub>  | Cable Compensation Voltage on VCVR for VOUT = 100 mV/A | RCS = 5 m $\Omega$ , VCS = -5 mV                      | - | 10 | - | mV |

| V <sub>COMR</sub> -CDC-150 | Cable Compensation Voltage on VCVR for VOUT = 150 mV/A | RCS = 5 m $\Omega$ , VCS = -5 mV                      | - | 15 | - | mV |

| V <sub>COMR</sub> -CDC-200 | Cable Compensation Voltage on VCVR for VOUT = 200 mV/A | RCS = 5 m $\Omega$ , VCS = -5 mV                      | - | 20 | - | mV |

| V <sub>COMR</sub> -CDC-250 | Cable Compensation Voltage on VCVR for VOUT = 250 mV/A | RCS = 5 mΩ, VCS = $-5$ mV                             | - | 25 | - | mV |

| FEEDBACK SEC               | CTION                                                  |                                                       |   |    |   |    |

| I <sub>SFB-Sink-MAX</sub>  | SFB Maximum Sinking Current<br>During Regulation       | Minimum guaranteed sink current expected from SFB pin | 2 | _  | _ | mA |

delta VIN = 20 mV, VCS = 0 V

1.940

2.000

2.060

mV

| <b>ELECTRICAL CHARACTERISTICS</b> (Minimum and maximum values are at VIN = 3.135 V to 22.5 V, TA = -40°C to +105°C unless |

|---------------------------------------------------------------------------------------------------------------------------|

| otherwise noted. Typical values are at TA = $25^{\circ}$ C, VIN = 5.0 V) (continued)                                      |

| Symbol                  | Parameter                         | Conditions                                                                   | Min  | Тур | Max    | Unit |

|-------------------------|-----------------------------------|------------------------------------------------------------------------------|------|-----|--------|------|

| UART                    |                                   |                                                                              |      | -   |        |      |

| V <sub>UART-VIH</sub>   | High-Level Input Voltage          | VIN = 3.5 V - 22.5 V                                                         | 2    | _   | -      | V    |

| V <sub>UART-VIL</sub>   | Low-Level Input Voltage           | VIN = 3.5 V - 22.5 V                                                         | -    | _   | 0.8    | V    |

| V <sub>UART-HYS</sub>   | Input Hysteresis                  | VIN = 3.5 V - 22.5 V                                                         | -    | 200 | -      | mV   |

| V <sub>UART-VOL</sub>   | Output Low Voltage                | VIN = 3.5 V - 22.5 V, lout = 2 mA                                            | -    | _   | 0.4    | V    |

| V <sub>UART-VOH</sub>   | UART High Output Voltage          | VIN = 3.5 V - 22.5V, lout = -2 mA                                            | 2.9  | _   | -      | V    |

| <sup>t</sup> UART–tR    | Rise Time of UART Tx              | 10%–90%, VIN = 3.5 V – 22.5 V,<br>CI = 20 pF                                 | -    | 250 | -      | ns   |

| <sup>t</sup> UART-tFall | Fall Time of UART Tx              | 90% to 10%, VIN = 3.5 V – 22.5 V,<br>Cload = 20 pF                           | -    | 250 | -      | ns   |

| UART-BAUD<br>(Note 5)   | UART BAUD Rate Range<br>Supported | Transmit and receive fall within 10% of BAUD Rate set, including min and max | 9600 | -   | 230400 | bps  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. Note (20 mA guaranteed over -40°C to 85°C)

5. Guaranteed by Design

## Arm Cortex-M0+ Processor

The FUSB15101 integrates an Arm Cortex–M0+ processor with Nested Vector Interrupt Controller (NVIC), Wake–up Interrupt Controller (WIC), and Debug Access Port (DAP). The processor uses the Thumb instruction set and is optimized for high performance with reduced code size and low power operation. The Arm Cortex–M0+ efficiently handles multiple parallel peripherals and has integrated sleep modes. Test and debug capability are enhanced with the Arm Serial Wire Debug Port.

The Arm implementation in the FUSB15101 includes a 32 kB OTP and 2 kB of SRAM. The MCU, Memory and DAP are interconnected using the AMBA (Advanced Microcontroller Bus Architecture) AHB–Lite interface and peripherals are connected to the AHB via APB interface (Advanced Peripheral Bus).

In addition to the base Arm Cortex–M0+ processor interrupts, the FUSB15101 implements multiple external source interrupts for peripheral devices. A powerful nested, pre–emptive and priority–based interrupt handling system assures timely and flexible response to external events.

Low power features on FUSB15101 include the WIC, adjustable clock rates, and different software–controlled power modes to maximize opportunities to save power in the final application.

## **Reset Sources**

The FUSB15101 has various sources of reset including:

• *Internal Power–On Reset* – The Internal Power–On Reset asserts when VIN supply is below threshold levels for proper operation. It resets the entire chip including core, debug port, peripherals, wakeup timer, and watchdog.

- *Software Issued Reset* The software reset can be called by writing to a given register in the Cortex address space. It is typically called on exit from a processor exception. Software reset resets the entire chip including core, peripherals, wakeup timer, and watchdog.

- *Watchdog Timer Reset* The watchdog timer reset is caused by the watchdog timeout and is used to prevent errant software from locking up the device. The watchdog reset resets the entire chip including core, debug port, peripherals, and watchdog. The watchdog timer is disabled upon power up and must be enabled by software. The watchdog is not paused when the debugger halts the processor.

## **Power and Sleep Behavior**

The FUSB15101 has been optimized to conserve power by utilizing peripheral interrupts and hardware autonomy. The device can be configured via firmware to enter low power states, disable unneeded peripherals and scale clock frequencies based on different application needs.

The Type–C block is designed to function at the lowest power states and will automatically wake when a Type–C attach is detected. This minimizes total power consumption when no device is attached.

# **Clock Sources**

FUSB15101 implements a dual oscillator architecture to minimize power consumption.

- A 12 MHz internal RC oscillator to enable full functionality.

- A 240 kHz internal RC oscillator that can be used for very low power sleep modes

# Timers

- 32-bit General Purpose Timer FUSB15101 has a 32-bit down-counter that can generate an interrupt request signal, status, when the counter reaches 0. The timing resolution depends on the programmable clock source and pre-scale ratios/

- 32-bit Wake-up Timer (WUT) The main purpose of the wakeup timer is to facilitate scheduled exit from low power modes. It can also be used for general purpose event timing.

- 32-bit Watchdog Timer (WDT) The watchdog timer applies a reset to the system in the event of a software failure, providing a way to recover from software crashes. The watchdog timer is disabled by default and must be enabled through software. The watchdog is protected with a lock mechanism to prevent rogue software from disabling the watchdog functionality. A special value has to be written to the lock register to access watchdog control. The watchdog timer is clocked from the same oscillator as the core, which can be LS\_CLK or HS\_CLK.

# Serial Wire Debug Interface (SWD)

The Arm M0+ implementation includes a Debug Access Port (DAP). The debug mode implementation includes 4 hardware breakpoints and 2 hardware watch points. The Debug Access Port interface implementation is the Arm Serial Wire Debug Port (SW–DAP) connected to Pins SWCLK and SWDIO. The Serial Wire Debug Port Interface uses a single bi–directional data connection. Each operation consists of three phases: Packet request, Acknowledge response, and Data transfer phase. Use any Serial Wire Debug (SWD) compliant hardware debugger interface to interact with the internals of the FUSB15101.

# USB Type-C & PD Peripheral Overview

The USB Type–C and PD peripheral is a fully compliant USB solution. This peripheral consists of an analog front end and a digital state machine. Firmware implements the higher–level protocol and policy layers whereas the analog and digital components can perform lower–level PD protocol and PHY layer functions.

The Type–C block includes all terminations and comparators required for Source/Sink/DRP operation: plug orientation detection, power capability advertisement and power role detection.

Figure 5. USB Type-C and PD

# VCONN Switch

Some applications require that a VCONN voltage be sourced in order to provide additional source capabilities when sourcing greater than 3 A on VBUS. The level of over-current protection on VCONN is fixed at 50 mA.

# **USB PD PHY State Machine Logic**

The FUSB15101 PD module includes the following digital functions to enable USB PD messaging:

- Serialization and de-serialization

- Clock and data recovery (CDR)

- 4B5B coding

- BMC coding

- Packet CRC generation and checking

- Coding and detection of Power Delivery K-Codes

- Automatic GoodCRC packet response

# BC1.2 Support

The FUSB15101 has the circuitry to enable emulation BC1.2, QC2.0 and 2.4A Divider Mode via firmware.

# **VBUS** Operation

Gate Driver

VBUS from the USB–C connector is typically connected to a load switch NFET (Q1 in Figure 6) source terminal whose gate terminal is driven by the FUSB15101 gate driver via the LGATE pin. **onsemi** recommends NFETs with low  $I_{GSS}$  leakages (<1  $\mu$ A) for optimal gate drive.

Figure 6. VBUS Discharge via BLD Pin

# VBUS Discharge

VBUS is discharged through a resistor (RBLD) via the BLD pin of the FUSB15101 as shown in the highlighted section in Figure 6. The external resistor RBLD value is dependent on the total bulk capacitance (CBULK) of the power source so that VBUS is discharged within the time limits dictated by USB PD. A typical value for RBLD is  $30 \Omega$ , 1 W and in addition, there is internal resistance that limits the discharge current within the FUSB15101 (I<sub>BLD-SINK</sub> in the electrical tables above).

When the load current to the Sink is sufficient (exceeds  $I_{CS-EN-BLD}$  for  $t_{CS-EN-BLD}$  debounce time) such that the internal discharge is not needed, then the FUSB15101 will automatically disable internal discharge.

Upon power up, firmware in the FUSB15101 may discharge VBUS in case there is a voltage on VBUS since the only way a Sink can be attached per Type C specification is if VBUS is discharged to ground (below VSafe0V) upon attach.

The discharge resistance limits are governed by the Type C specification when not sourcing power on VBUS ( $R_{BLD-LEAK}$  in the electrical tables above). It is preferred that no external load/discharge resistor is connected to VBUS other than RBLD to the FUSB15101 discharge BLD pin. A TVS diode connected from VBUS to ground ([SZ]ESD7241) allow operating voltages up to 24 V covering the entire VBUS range of 3.3 V to 21 V for a USB PD PPS contract. This can be replaced by a TVS that covers the VBUS range for the use case of this design if needed.

# Voltage and Current Sensing Operation

The resistor ratio from VIN to ground formed by resistors R2 and R3 in Figure 7 (typically 1:10 ratio) is sensed via FUSB15101 VREF pin to set the output voltage.

For the offline design in Figure 2, this will be done via the FUSB15101 SFB pin, the opto-coupler, resistor R1 and the primary side PWM controller operation.

For DC–DC design in Figure 3, this will be done via the FUSB15101 SFB pin controlling the buck–boost PWM via its COMP pin.

The FUSB15101 will automatically control the SFB pin based on the desired voltage as determine by the USB PD contract and the existing VIN voltage sensed by VREF.

The external compensation network formed by C2/R2 and R4/C1 need to be selected to achieve stable operation over the range of VBUS voltage and current transitions as shown in Figure 7.

Figure 7. Compensation Network for AC/DC Constant Voltage / Constant Current (CC/CV) Feedback

For the DC–DC design in Figure 3, there may be a need for additional compensation networks from COMP pin to ground or from COMP to the DC–DC's supply.

The current is sensed via a small resistor (5 m $\Omega$  typically) connected between the USB–C connector ground and the main ground plane of the power source (secondary side ground for offline design) as shown in Figure 7. The gain of the current sense amplifier can be adjusted to work with 10 m $\Omega$  resistors if desired.

A low pass filter formed by R5/C3 provides a stable signal for CSP and CSN pins of the FUSB15101 to sense this current for over-current protection for fixed voltage PD contracts, constant current operation for PPS contracts and cable compensation (Table 1).

| Symbol                    | Cable Drop Compensation |

|---------------------------|-------------------------|

| V <sub>COMR-CDC-0</sub>   | 0 mV/A                  |

| V <sub>COMR-CDC-0</sub>   | 50 mV/A                 |

| V <sub>COMR-CDC-100</sub> | 100 mV/A                |

| V <sub>COMR-CDC15-0</sub> | 150 mV/A                |

| V <sub>COMR-CDC-200</sub> | 200 mV/A                |

| V <sub>COMR-CDC-250</sub> | 250 mV/A                |

Table 1. CABLE DROP COMPENSATION

It is expected that the USB–C connector ground is connected only to the current sense network resistors and the connector TVS ground connections and not to the main ground plane of the DC/DC design or secondary side power ground for the offline design (FUSB15101 ground connection). However, the FUSB15101 consumes very little current and so it should have a negligible impact on this current sensing if the FUSB15101 ground connection is on the USC–C connector ground if it is more convenient in the Printed Circuit Board (PCB) layout.

When in a PPS contract, if a PPS\_Status message is requested, the firmware in the FUSB15101 will measure the current with an internal 10-bit Analog to Digital Converter (ADC) based on the above description and report it back to the Sink on the PPS\_Status message. The voltage is also reported back but it is measured off VIN with the ADC not VREF pin since the VREF pin is only used for voltage feedback. Thus, if the voltage feedback resistor divider connected to VREF is modified to be slightly different from the 1:10 ratio expected, the voltage sensing for this PPS\_Status message will not be affected. BLD pin voltage can also be monitored by the ADC and it will be accurate as long as the discharge function is not enabled.

#### **Protection Operation**

FUSB15101 has several ways it protects itself as shown in Table 2.

OVP and UVP are sensed via an internal resistor divider that divides VIN by 10 to determine the voltage from the power source. HVCC1, HVCC2, HVDP and HVDM are directly sensed for over voltage. For external temperature monitoring (E\_OTP), two NTC pins are available that are connected to NTC resistors to ground usually in parallel with another resistor to ground for linearity. An internal temperature monitor (I\_OTP) is also used for protecting the devince under extreme die temperatures. For all faults capable of automatic hardware protection (when enabled), the FUSB15101 will disable the Type C connection with the Sink (no pull–up on CC), shut off VBUS load switch and discharge VIN to vSafe5V.

| able 2. PROTECTION FEATURES |                                 |             |                                           |  |  |  |

|-----------------------------|---------------------------------|-------------|-------------------------------------------|--|--|--|

| Symbol                      | Description                     | Pin(s) Used | Automatic Hardware<br>Protection Capable? |  |  |  |

| OVP                         | Output Over Voltage Protection  | VIN         | Yes                                       |  |  |  |

| UVP                         | Output Under Voltage Protection | VIN         | Firmware Controlled                       |  |  |  |

| OCP                         | Over Current Protection         | CSP & CSN   | Yes                                       |  |  |  |

| I_OTP                       | Internal Temperature Protection | N/A         | Yes                                       |  |  |  |

| E OTP                       | External Temperature Protection | NTCA / NTCB | Firmware Controlled                       |  |  |  |

HVCC1 or HVCC2 Over Voltage Protection

HVDP or HVDM Over Voltage Protection

VCONN Over Current Protection

VBUS or HVDM Pollution Detection

#### Та

CC\_OVP

USB\_OVP

VCONN\_OCP

Cable Fault

# **Output Over-Voltage Protection (OVP)**

FUSB15101 has built-in OVP based on firmware programmable values. Whenever VIN, as sensed by an internal 1:10 resistor divider, exceeds by K<sub>IN-OVP</sub> (Table 3) of the requested VIN from the power source for a debounce time of t<sub>VIN-OVP-Debounce</sub>, then the OVP fault would be triggered. If hardware auto-protection is enabled, the FUSB15101 will disable the Type C connection with the Sink (no pull-up on CC), shut off VBUS load switch and discharge VIN to vSafe5V.

During transitions between VIN voltages, the OVP circuitry can be blanked or disabled via firmware to ensure that false triggering of OVP doesn't occur. To ensure safe operation over all voltages of VIN, the maximum VIN voltage is limited to VIN-OVP-MAX.

Table 3. PROGRAMMABLE OVP SETTINGS

| Symbol                  | VIN / VIN Requested |

|-------------------------|---------------------|

| K <sub>IN-OVP-105</sub> | 105%                |

| K <sub>IN-OVP-110</sub> | 110%                |

| K <sub>IN-OVP-115</sub> | 115%                |

| K <sub>IN-OVP-120</sub> | 120%                |

| K <sub>IN-OVP-125</sub> | 125%                |

| K <sub>IN-OVP-130</sub> | 130%                |

| K <sub>IN-OVP-135</sub> | 135%                |

## **Output Under-Voltage Protection (UVP)**

FUSB15101 has a built-in firmware programmable UVP. Whenever VIN, as sensed internally, is below K<sub>IN-UVP</sub> (Table 4) of the requested output voltage from the power source, then the UVP fault would be triggered. During transitions between VIN voltages, the UVP circuitry can be blanked or disabled via firmware to ensure that false triggering of UVP doesn't occur. For PPS contracts, if current limiting causes the voltage to decrease, the UVP fault will not trigger at a percentage of VIN since all voltages from the requested voltage to VIN-OFF, the lowest voltage, are valid.

For compliance with the USB PD specification, the FUSB15101 will trigger UVP whenever VIN is below VIN-OFF. This allows protection for a direct short of VBUS to ground separately or in conjunction with the OCP fault described below. If VIN < VIN–OFF fault is triggered, then to resume normal operation, VIN has to go below VLATCH-OFF to reset the FUSB15101 to exit this fault condition.

Yes

Yes

Yes

Firmware Controlled

| Symbol                  | VIN / VIN Requested |

|-------------------------|---------------------|

| K <sub>IN-OVP-105</sub> | 105%                |

| K <sub>IN-UVP-60</sub>  | 60%                 |

| K <sub>IN-UVP-65</sub>  | 65%                 |

| K <sub>IN-UVP-70</sub>  | 70%                 |

| K <sub>IN-UVP-80</sub>  | 80%                 |

| K <sub>IN-UVP-90</sub>  | 90%                 |

| K <sub>IN-UVP-95</sub>  | 95%                 |

#### Table 4. PROGRAMMABLE UVP SETTINGS

HVCC1 / HVCC2

HVDP / HVDM

CC1 / CC2

BLD / HVDM

## **Over-Current Protection (OCP) and Constant Current** Limit (CL)