## LC<sup>2</sup>MOS 8-Bit μP-Compatible 12-Bit DAC

**AD7548**

#### **FEATURES**

8-Bit Bus Compatible 12-Bit DAC

All Grades 12-Bit Monotonic Over Full

Temperature Ranges

Operation Specified at +5V, +12V

or +15V Power Supply

Low Gain Drift of 5ppm/\*C Maximum

Full 4 Quadrant Multiplication

Skinny DIP and Surface Mount Packages

#### **APPLICATIONS**

8-Bit Microprocessor Based Control Systems Programmable Amplifiers Function Generation Servo Control

#### GENERAL DESCRIPTION

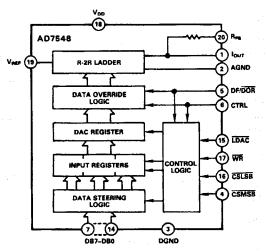

The AD7548 is a 12-bit monolithic CMOS D/A converter for use with 8-bit bus microprocessors. Data is loaded in two bytes to input holding registers as shown in the block diagram opposite. The AD7548 can be configured to accept either left- or right-justified data, least significant byte or most significant byte first, using standard TTL compatible control inputs.

A separate load DAC control input allows the user the choice of updating the analog output coincident with loading new data to the DAC input register or at any time after the data loading event. This feature is especially important in multi-DAC systems where simultaneous update of all DACs is required.

The new Linear Compatible CMOS (LC<sup>2</sup> MOS) process used in the manufacture of the AD7548 allows precision thin-film linear circuitry and high-speed low-power CMOS logic to be integrated on the same small chip. The high-speed logic allows direct interfacing to most of the popular 8-bit microprocessors.

#### AD7548 FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT HIGHLIGHTS

- Microprocessor Compatibility

High speed input control (TTL/5V CMOS compatible) allow

direct interfacing to most of the popular 8-bit

microprocessors.

- Guaranteed Monotonicity

The AD7548 is guaranteed monotonic to 12-bits over the full temperature range for all grades and at all specified supply voltages.

- Selectable Data Input Format

Left- or right-justified data, least significant or most significant

byte first. This allows the AD7548 to be interfaced with

microprocessors using either Motorola or Intel-type data

formatting.

- Monolithic Construction

For increased reliability and reduced package size 0.3"

20-pin DIP and 20-terminal surface mount packages.

- 5. Single Supply Operation See Figure 8.

- 6. Low Gain Error and Gain Error T.C.

## **AD7548\* Product Page Quick Links**

Last Content Update: 11/01/2016

### Comparable Parts

View a parametric search of comparable parts

### Documentation <a>□</a>

#### **Application Notes**

AN-225: 12-Bit Voltage-Output DACs for Single-Supply 5V and 12V Systems

#### **Data Sheet**

AD7548: LC<sup>2</sup>MOS 8-Bit μP Compatible 12-Bit DAC Scanned Data Sheet

### Reference Materials -

#### **Solutions Bulletins & Brochures**

• Digital to Analog Converters ICs Solutions Bulletin

## Design Resources -

- AD7548 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

### Discussions <a>□</a>

View all AD7548 EngineerZone Discussions

## Sample and Buy -

Visit the product page to see pricing options

## Technical Support <a> Image: Page 1</a> <a> Image: Page 2</a> <a> Image: Page 3</a> <a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# $SPECIFICATIONS^{1} \quad \text{($v_{\text{DO}} = +5$V$, $V_{\text{REF}} = +10$V$; $I_{\text{OUT}} = \text{AGND} = 0$V$. All specifications $T_{\text{min}}$ to $T_{\text{max}}$ unless otherwise specified)}$

| Parameter                                        | J, A<br>Versions | K, B<br>Versions | S Version | T Version | Units          | Test Conditions/Comments                                                                                                  |

|--------------------------------------------------|------------------|------------------|-----------|-----------|----------------|---------------------------------------------------------------------------------------------------------------------------|

| ACCURACY                                         |                  |                  |           |           |                |                                                                                                                           |

| Resolution                                       | 12               | 12               | 12        | 12        | Bits           |                                                                                                                           |

| Relative Accuracy                                | ±1               | ± 1/2            | ±1        | ± 1/2     | LSB max        |                                                                                                                           |

| Differential Nonlinearity                        | ± 1              | ± 1/2            | ±1        | ± 1/2     | LSB max        | All grades guaranteed monotonic to 12-bits over temperature.                                                              |

| Full Scale Error                                 | ±6               | ±3               | ±6        | ±3        | LSB max        | Measured using internal RFB and includes effects of leakage current and gain TC. Full Scale Error can be trimmed to zero. |

| Gain Temperature Coefficient <sup>2</sup> ;      |                  |                  |           |           |                |                                                                                                                           |

| ΔGain/ΔTemperature                               | ±5               | ±5               | ±5        | ± 5       | ppm/°C max     | Typical value is 2ppm/°C                                                                                                  |

| Output Leakage Current                           |                  | -                |           |           |                |                                                                                                                           |

| I <sub>OUT</sub> (Pin 1)                         |                  |                  |           |           |                |                                                                                                                           |

| +25°C                                            | ±5               | ±5               | ±5        | ±5        | nA max         | All digital inputs = 0V                                                                                                   |

| T <sub>min</sub> to T <sub>max</sub>             | ± 25             | ± 25 ····        | ± 150     | ± 150     | nA max         |                                                                                                                           |

| REFERENCE INPUT                                  |                  |                  |           |           |                |                                                                                                                           |

| Input Resistance, Pin 19                         | 7                | 7                | 7         | 7         | kΩ min         | Typical Input Resistance = $11k\Omega$                                                                                    |

|                                                  | 20               | 20               | 20        | 20        | kΩ max         |                                                                                                                           |

| DIGITAL INPUTS                                   |                  |                  |           |           |                |                                                                                                                           |

| VIH (Input High Voltage)                         | 2.4              | 2.4              | 2.4       | 2.4       | V min          |                                                                                                                           |

| VII. (Input Low Voltage)                         | 0.8              | 0.8              | 0.8       | 0.8       | V max          |                                                                                                                           |

| I <sub>IN</sub> (Input Current)                  |                  |                  |           |           |                |                                                                                                                           |

| + 25°C                                           | ± 1              | ±1 .             | ±1        | ±1        | μA max         | $V_{IN} = 0V \text{ or } V_{DD}$                                                                                          |

| Tmin to Tmax                                     | ±10              | ± 10             | ± 10      | ± 10      | μA max         |                                                                                                                           |

| C <sub>IN</sub> (Input Capacitance) <sup>2</sup> | 7                | 7                | 7         | 7         | pF max         |                                                                                                                           |

| POWER SUPPLY                                     |                  |                  |           |           |                |                                                                                                                           |

| V <sub>DD</sub> Range                            | 4.75/5.25        | 4.75/5.25        | 4.75/5.25 | 4.75/5.25 | V min/V max    | Specifications guaranteed over this range                                                                                 |

| I <sub>DD</sub>                                  | 2                | 2                | 2         | 2         | mA max         | All digital inputs $V_{IL}$ or $V_{IH}$                                                                                   |

|                                                  | 300              | 300              | 300       | 300       | μ <b>A max</b> | All digital inputs OV or V <sub>DD</sub>                                                                                  |

# $\label{eq:specifications} \textbf{SPECIFICATIONS}^{1} \begin{subarray}{ll} (V_{DD} = + 12V & to & + 15V, \ V_{REF} = + 10V; \ I_{OUT} = AGND = 0V. \\ All & specifications \ T_{min} & to \ T_{max} & unless & otherwise & specified) \\ \end{subarray}$

| Parameter                                        | J, A<br>Versions | K, B<br>Versions | S Version  | T Version  | Units          | Test Conditions/Comments                                                                     |

|--------------------------------------------------|------------------|------------------|------------|------------|----------------|----------------------------------------------------------------------------------------------|

| ACCURACY                                         |                  |                  |            |            |                |                                                                                              |

| Resolution                                       | 12               | 12               | 12         | 12         | Bits           |                                                                                              |

| Relative Accuracy                                | ± 1              | ± 1/2            | ± 1        | ± 1/2      | LSB max        |                                                                                              |

| Differential Nonlinearity                        | ±l               | ± 1/2            | ±1         | ± 1/2      | LSB max        | All grades guaranteed monotonic to 12-bits over temperature.                                 |

| Full Scale Error                                 | ±6               | ±3               | ±6         | = 3        | LSB max        | Measured using internal R <sub>FB</sub> and includes effects of leakage current and gain TC. |

|                                                  | , and the        |                  | 2          |            |                | Full Scale Error can be trimmed to zero.                                                     |

| Gain Temperature Coefficient <sup>2</sup> ;      |                  |                  |            |            | Property of    |                                                                                              |

| ΔGain/ΔTemperature                               | ±5               | ±5               | ±5         | ± 5        | ppm/°C max     | Typical value is 2ppm/°C                                                                     |

| Output Leakage Current                           |                  |                  |            |            | • -            |                                                                                              |

| IOUT (Pin 1)                                     |                  | + 1              |            |            |                |                                                                                              |

| + 25°C                                           | . ±5             | ±5               | ±5         | ±5         | nA max         | All digital inputs = 0V                                                                      |

| T <sub>min</sub> to T <sub>max</sub>             | ± 25             | ± 25             | ± 150      | ± 150      | nA max         |                                                                                              |

| REFERENCE INPUT                                  |                  |                  |            |            |                |                                                                                              |

| Input Resistance, Pin 19                         | 7                | 7                | 7          | 7          | kΩ min         | Typical Input Resistance = $11k\Omega$                                                       |

|                                                  | 20               | 20               | 20         | 20         | kΩ max         |                                                                                              |

| DIGITAL INPUTS                                   |                  |                  |            |            |                |                                                                                              |

| VIH (Input High Voltage)                         | 2.4              | 2.4              | 2.4        | 2.4        | V min          |                                                                                              |

| VII. (Input Low Voltage)                         | 0.8              | 0.8              | 0.8        | 0.8        | V max          |                                                                                              |

| IIN (Input Current)                              |                  |                  |            |            |                |                                                                                              |

| + 25℃                                            | ±1               | ±1               | ± l        | ± 1        | μA max         | $V_{IN} = 0V \text{ or } V_{DD}$                                                             |

| T <sub>min</sub> to T <sub>max</sub>             | ± 10             | ± 10             | ± 10       | ± 10       | μ <b>A</b> max |                                                                                              |

| C <sub>IN</sub> (Input Capacitance) <sup>2</sup> | 7                | 7                | 7          | 7          | pF max         |                                                                                              |

| POWER SUPPLY                                     |                  |                  |            |            |                |                                                                                              |

| V <sub>DD</sub> Range                            | 11.4/15.75       | 11.4/15.75       | 11.4/15.75 | 11.4/15.75 | V min/V max    | Specifications guaranteed over this range                                                    |

| $I_{DD}$                                         | 3                | 3                | 3          | 3          | mA max         | All digital inputs VIL or VIH                                                                |

|                                                  | 1                | 1                | 1          | 1          | mA max         | All digital inputs OV or VDD                                                                 |

NOTES

Temperature range as follows: J, K Versions; 0 to +70°C

A, B Versions; -40°C to +85°C

S, T Versions; -55°C to +125°C

Guaranteed by design but not production tested.

Specifications subject to change without notice.

## TIMING CHARACTERISTICS $(v_{no} = +5v, v_{res} = +10v, l_{out} = AGNO = 0v unless otherwise stated)$

| Parameter        | Limit at<br>T <sub>A</sub> =25°C | Limit <sup>2</sup> at<br>T <sub>A</sub> = 0 to +70°C<br>-40°C to +85°C | Limit $^2$ at<br>$T_A = -55^{\circ}C$<br>to $+125^{\circ}C$ | Units  | Test Conditions/Comments        |

|------------------|----------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------|--------|---------------------------------|

| t <sub>DS</sub>  | 240                              | 240                                                                    | 290                                                         | ns min | Data Valid Setup Time           |

| ton              | 50                               | 50                                                                     | 70                                                          | ns min | Data Valid Hold Time            |

| t <sub>CWS</sub> | 30                               | 40                                                                     | 50                                                          | ns min | CSMSB or CSLSB to WR Setup Time |

| t <sub>CWH</sub> | 15                               | 20                                                                     | 25                                                          | ns min | CSMSB or CSLSB to WR Hold Time  |

| tLWS             | 30                               | 40                                                                     | 50                                                          | ns min | LDAC to WR Setup Time           |

| LWH              | 15                               | 20                                                                     | 25                                                          | ns min | LDAC to WR Hold Time            |

| twr              | 250                              | 280                                                                    | 320                                                         | ns min | Write Pulse Width               |

## TIMING CHARACTERISTICS $(v_{00} = + 12V \text{ to } + 15V, v_{REF} = + 10V, l_{OUT} = AGND = 0V \text{ unless otherwise stated})$

| Parameter       | Limit at<br>T <sub>A</sub> =25°C | Limit 2 at T <sub>A</sub> = 0 to + 70°C - 40°C to + 85°C | Limit $^2$ at<br>$T_A = -55^{\circ}C$<br>to +125°C | Units  | Test Conditions/Comments        |

|-----------------|----------------------------------|----------------------------------------------------------|----------------------------------------------------|--------|---------------------------------|

| t <sub>DS</sub> | 160                              | 190                                                      | 230                                                | ns min | Data Valid Setup Time           |

| рн              | 30                               | 30                                                       | 50                                                 | ns min | Data Valid Hold Time            |

| cws             | - 30                             | 40                                                       | 50                                                 | ns min | CSMSB or CSLSB to WR Setup Time |

| CWH             | 15                               | 20                                                       | 25                                                 | ns min | CSMSB or CSLSB to WR Hold Time  |

| LWS             | 30                               | 40                                                       | 50                                                 | ns min | LDAC to WR Setup Time           |

| LWH             | 15                               | 20                                                       | 25                                                 | ns min | LDAC to WR Hold Time            |

| WR              | 170                              | 200                                                      | 240                                                | ns min | Write Pulse Width               |

# AC PERFORMANCE CHARACTERISTICS These characteristics are included for Design Guidance only and are not subject to test. $(V_{REF} = +\ 10V;\ l_{OUT} = AGND = 0V,\ Output\ Amplifier$ is AD544 except where stated)

| Parameter                                          | Version |            | = +5V<br>T <sub>A</sub> =T <sub>MIN</sub> , T <sub>MAX</sub> |            | 12V to + 15V $T_A = T_{MIN}, T_{MAX}$ | Units            | Test Conditions/Comments                                                                                                                |

|----------------------------------------------------|---------|------------|--------------------------------------------------------------|------------|---------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Output Current Settling Time                       |         | 1.5        | _                                                            | 1          |                                       | με тур           | To 0.01% of full scale range.  LOUT load = 100Ω, CEXT = 13pF.  DAC register alternately loaded with all 1s and all 0s                   |

| Digital to Analog Glitch<br>Impulse                |         | 400        | -                                                            | 330        | _                                     | nV-sec typ       | Measured with $V_{REF} = 0V$ , $I_{OUT}$ load = $100\Omega$ , $C_{EXT} = 13pF$ . DAC register alternately loaded with all 1s and all 0s |

| Multiplying Feedthrough Error <sup>3</sup>         | -       | 3          | 5                                                            | 3          | 5                                     | mV p-p typ       | V <sub>REF</sub> = ±5V, 10kHz sine wave<br>DAC register loaded with all 0s.                                                             |

| Total Harmonic Distortion                          |         | -85        | -                                                            | - 85       | -                                     | dB typ           | V <sub>REF</sub> = 6V rms @ 1kHz.<br>DAC register loaded with all 1s.                                                                   |

| Power Supply Rejection<br>Δ GAIN/Δ V <sub>DD</sub> |         | ±0.015     | ±0.03                                                        | ±0.01      | ± 0.02                                | % per % max      | ΔV <sub>DD</sub> = ±5%                                                                                                                  |

| Output Capacitance IOUT (Pin 1)                    |         | 200<br>100 | 200<br>100                                                   | 200<br>100 | 200<br>100                            | pF max<br>pF max | DAC register loaded with all 1s.<br>DAC register loaded with all 0s.                                                                    |

| Output Noise Voltage Density<br>(10Hz-100kHz)      |         | 15         | -                                                            | 15         | _                                     | nV/√Hz typ       | Measured between R <sub>FB</sub> and I <sub>OUT</sub>                                                                                   |

NOTES

Guaranteed by design but not production tested.

\*Temperature range as follows: J, K Varsions; 0 to +70°C A, B Varsions; -40°C to +85°C 5, T Varsions; -55°C to + 125°

Feedthrough can be further reduced by connecting the metal lid on the ceramic package (Suffix D) to DGNE

Specifications subject to change without notice.

| ABSOLUTE MAXIMUM RATINGS*                             | r   |                    |

|-------------------------------------------------------|-----|--------------------|

| $(T_A = +25^{\circ}C \text{ unless otherwise noted})$ |     |                    |

| V <sub>DD</sub> (Pin 18) to DGND                      |     | + 17V              |

| V <sub>REF</sub> (Pin 19) to AGND                     |     |                    |

| V <sub>RFB</sub> (Pin 20) to AGND                     |     |                    |

| Digital Input Voltage (Pins 4-17) to DO               | GND | $-0.3V$ , $V_{DD}$ |

| V <sub>PIN 1</sub> to DGND                            |     |                    |

| AGND to DGND                                          |     | $-0.3V, V_{DD}$    |

| Power Dissipation (Any Package)                       |     |                    |

| To +75°C                                              |     | 450mW              |

| Derates above +75°C                                   |     | 6mW/°C             |

| Operating Temperature Range       |                 |

|-----------------------------------|-----------------|

| Commercial (J, K Versions) .      | 0 to +70°C      |

| Industrial (A, B Versions)        |                 |

| Extended (S, T Versions)          | −55°C to +125°C |

| Storage Temperature               |                 |

| Lead Temperature (Soldering, 10se | ecs) + 300°C    |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### CAUTION:

ESD (Electro-Static-Discharge) sensitive device. The digital control inputs are Zener protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The foam should be discharged to the destination socket before devices are removed.

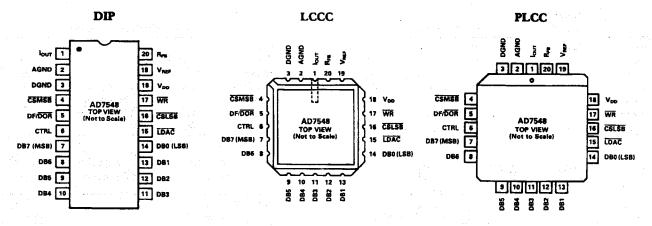

#### **PIN CONFIGURATIONS**

#### ORDERING INFORMATION1,2

| Relative Full-Scale Accuracy Error |                | Temperature Range and Package Options <sup>3</sup> |                      |                           |  |  |  |

|------------------------------------|----------------|----------------------------------------------------|----------------------|---------------------------|--|--|--|

| T <sub>min</sub> -T <sub>max</sub> | · •            | 0 to +70°C                                         | -25°C to +85°C       | -55°C to +125°C           |  |  |  |

|                                    |                | Plastic DIP (N-20)                                 | Hermetic (Q-20)      | Hermetic (Q-20)           |  |  |  |

| ± 1LSB<br>± 1/2LSB                 | ±6LSB<br>±3LSB | AD7548JN<br>AD7548KN                               | AD7548AQ<br>AD7548BQ | AD7548SQ<br>AD7548TQ      |  |  |  |

|                                    |                | PLCC <sup>4</sup> (P-20A)                          |                      | LCCC <sup>5</sup> (E-20A) |  |  |  |

| ± 1LSB<br>± 1/2LSB                 | ±6LSB<br>±3LSB | AD7548JP<br>AD7548KP                               |                      | AD7548SE<br>AD7548TE      |  |  |  |

#### NOTES

<sup>1</sup>To order MIL-STD-883, Class B processed parts, add/883B to part number.

Contact your local sales office for military data sheet.

<sup>3</sup>See Section 13 for package outline information.

<sup>&</sup>lt;sup>2</sup>Analog Devices reserves the right to ship ceramic (package outline D-20) packages in lieu of cerdip (package outline Q-20) packages.

<sup>&</sup>lt;sup>4</sup>PLCC: Plastic Leaded Chip Carrier. <sup>5</sup>LCCC: Leadless Ceramic Chip Carrier.

#### PIN FUNCTION DESCRIPTION DESCRIPTION MNEMONIC PIN DAC current OUT bus. Normally terminated at virtual ground of output amplifier. I<sub>OUT</sub> AGND Analog Ground. DG.ND CSMSB Digital Ground. Chip Select Most Significant (MS) Byte. Active Low Input. Used in combination with WR to load external data into the input register or in combination with WR and LDAC to load external data into both input and DAC registers. Data Format/Data Override. When this input is LOW, data in the DAC register is forced to one of DF/DOR two override codes selected by CTRL. When the override signal is removed, the DAC output returns to reflect the value in the DAC register. With DF/DOR HIGH, CTRL selects either a left or right justified input data format. For normal operation, DF/DOR is held HIGH. DF/DOR CTRL **FUNCTION** DAC register contents overridden by all 0's DAC register contents overriden by all 1's 0 Left-justified input data selected Right-justified input data selected CTRL Control Input. See pin 5 description. LEAST SIGNIFICANT BYTE \* L-MOST SIGNIFICANT BYTE-LEFT-JUSTIFIED DATA Х X CTRL = "0" CTRL="1" RIGHT-JUSTIFIED DATA X = Don't care states. DB7 Data Bit 7. Most Significant Bit (MSB). DB6 Data Bit 6. DB5 Data Bit 5. 10 DR4 Data Bit 4. Data Bit 3. 11 DB3 12 DB2 Data Bit 2. 13 Data Bit 1. Data Bit O. Least Significant Bit (LSB). 14 DB0 Load DAC Input, active LOW. This signal, in combination with others, is used to load the DAC 15 LDAC register from either the input register or the external data bus. Chip Select Least Significant (LS) Byte. Active LOW input. Used in combination with WR to load external data into the input register or in combination with WR and LDAC to load external data CSLSB 16 into both input and DAC registers. WR WRITE Input. This active low signal, in combination with others is used in loading external data 17 into the AD7548 input register and in transferring data from the input register to the DAC register. WR CSMSB CSLSB LDAC **FUNCTION** Load LS Byte to Input Register. 0 Load LS Byte to Input Register and DAC Register. Load MS Byte to Input Register. Load MS Byte to Input Register and DAC Register. Load Input Register to DAC Register. 0 Û 0 No Data Transfer 18 19 20 +5V to +15V Supply Input. $V_{REF}$ Reference Voltage Input Feedback Resistor. Used for normal D/A conversion.

#### CONTROL INPUT INFORMATION

Figure 1a shows the data load timing diagram for the AD7548.

CSMSS

COWR

CO

NOTES 1. ALL INPUT SIGNAL RISE AND FALL TIMES MEASURED FROM 10% TO 30% OF +5V.  $t_i = t_i = 20$ ns.

- 2. TIMING MEASUREMENT REFERENCE LEVEL IS  $\frac{V_{HI} + V_{L}}{2}$

- 3. CSMSB (PIN 4) AND CSLSB (PIN 16) MAY BE INTERCHANGED.

- 4. FOR LEFT-JUSTIFIED DATA CTRL = +8V WITH DF/DOR = +5V.

FOR RIGHT-JUSTIFIED DATA CTRL = +5V WITH DF/DOR = +5V.

Figure 1a. AD7548 Timing Diagram

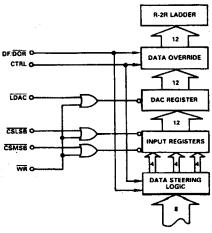

Figure 1b shows the simplified input control structure of the AD7548.

Figure 1b. Simplified AD7548 Input Control Structure

#### GENERAL CIRCUIT INFORMATION

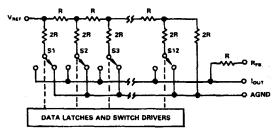

The simplified D/A circuit is shown in Figure 2. An inverted R-2R ladder structure is used, which steers binarily weighted currents between I<sub>OUT</sub> and AGND, thus maintaining a constant current in each ladder leg independent of the switch state.

The input resistance at  $V_{\rm REF}$  is constant and equal to the value "R" in Figure 2. Since the input resistance is constant, the reference terminal can be driven by a reference voltage or a reference current, ac or dc, of positive or negative polarity. (If a current source is used, a low temperature coefficient external  $R_{\rm FB}$  is recommended to define scale factor).

Figure 2. AD7548 Simplified Functional Diagram

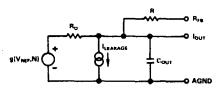

#### **EQUIVALENT CIRCUIT ANALYSIS**

Figure 3 shows an equivalent circuit for the analog section of the AD7548 D/A converter. The current source  $I_{LEAKAGE}$  is composed of surface and junction leakages. The resistor  $R_O$ , denotes the equivalent output resistance of the DAC which varies with input code (excluding all 0's code) from 0.8R to 2R, where R is typically  $11k\Omega$ .  $C_{OUT}$  is the capacitance due to the current steering switches and varies from about 50pF to 120pF (typical values) depending upon the digital input.  $g(V_{REF}, N)$  is the Thevenin equivalent voltage generator due to the reference input voltage,  $V_{REF}$ , and the transfer function of R-2R ladder, N.

For further information on CMOS multiplying D/A converters refer to "Application Guide to CMOS Multiplying D/A Converters" available from Analog Devices, Publication Number G479-15-8/78.

Figure 3. AD7548 Equivalent Analog Output Circuit

#### **DATA LOADING**

The AD7548 accepts incoming data in either left-justified format or right-justified format depending on the control inputs DF/DOR and CTRL.

(See pin description of DF/DOR and CTRL on preceding page).

Two operating modes are possible for controlling the transfer of data from the input register to the DAC register, the automatic transfer mode and the strobed transfer mode.

#### **AUTOMATIC TRANSFER MODE**

This is the simplest and fastest method of transferring data to the DAC register. It is facilitated by connecting  $\overline{\text{LDAC}}$  to either  $\overline{\text{CSMSB}}$ , as shown in Figure 10, or  $\overline{\text{CSLSB}}$ .

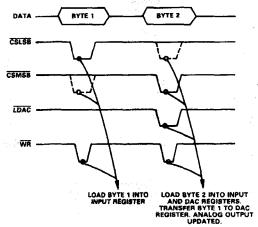

Figure 4 shows the timing diagram for automatic transfer of 8 +4-bit data to the DAC register. The first write cycle loads the first byte of data to the input register. The second write cycle loads the second byte of data to the input register and automatically transfers both bytes to the DAC register.

Updating a single byte (High or Low) in the DAC register can be achieved in one write cycle using the automatic transfer mode.

Figure 4. Automatic Transfer Mode

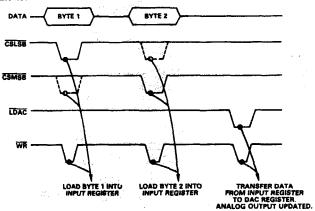

#### STROBED TRANSFER MODE

Figure 5 shows the timing diagram for the strobed transfer of 8 + 4-bit data to the DAC register. Three write cycles are required for this transfer mode. The first two write cycles sequentially load bytes 1 and 2 into the input register. The third write cycle transfers data from the input register to the DAC register.

The strobed transfer mode allows the DAC registers of several AD7548's to be updated simultaneously, as shown in Figure 13, by means of a master strobe signal connected to the LDAC of each device.

A single byte of data (High or Low) can be transferred to the DAC register in two write cycles using the strobed transfer mode.

Figure 5. Strobed Transfer Mode

#### **DATA OVERRIDE**

The contents of the DAC register can be overridden by pulling DF/DOR (pin 5) LOW. The CTRL (pin 6) input then determines whether the DAC register data is overidden by all 0s (CTRL LOW) or all 1s (CTRL HIGH). This feature allows the user to calibrate the AD7548 in circuits such as Figure 6 without calling on the microprocessor to load calibration data.

### **Applying the AD7548**

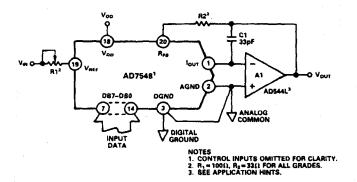

## UNIPOLAR BINARY OPERATION (2-QUADRANT MULTIPLICATION)

Figure 6 shows the analog circuit connections required for unipolar binary operation. With a dc input voltage or current (positive or negative polarity) applied at pin 19, the circuit is a unipolar D/A converter. With an ac input voltage the circuit provides 2-quadrant multiplication (digitally controlled attenuation).

Table I shows the code relationship for the circuit of Figure 6. For full scale trimming the DAC register is loaded with 1111 1111. This is most easily accomplished by using the data override function. R1 is then adjusted for  $V_{OUT} = -V_{IN}$  (4095/4096). Alternatively full scale can be adjusted by omitting R1 and R2 and trimming the reference voltage magnitude.

Capacitor C1 provides phase compensation and helps prevent overshoot and ringing when using high speed op amps.

Figure 6. Unipolar Binary Operation

|      | ary Num<br>OAC Regi |      | Analog Output, V <sub>OUT</sub>                      |

|------|---------------------|------|------------------------------------------------------|

| MSB  |                     | LSB  |                                                      |

| 1111 | 1111                | 1111 | $-V_{IN}\left(\frac{4095}{4096}\right)$              |

| 1000 | 0000                | 0000 | $-V_{IN}\left(\frac{2048}{4096}\right) = -1/2V_{IN}$ |

| 0000 | 0000                | 0001 | $-V_{IN}\left(\frac{1}{4096}\right)$                 |

| 0000 | 0000                | 0000 | 0V                                                   |

Table I. Unipolar Binary Code Table for Circuit of Figure 6

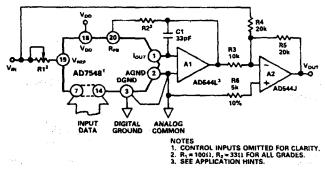

## BIPOLAR OPERATION (4-QUADRANT MULTIPLICATION)

Figure 7 and Table II illustrate the recommended circuit and code relationship for bipolar operation. The circuit uses offset binary input coding. However, 2's complement coding can be accommodated if the MSB is inverted (done in software) before data is loaded into the DAC.

With the DAC register loaded to 1000 0000 0000, adjust R1 for  $V_{OUT} = 0V$  (alternatively one can omit R1 and R2 and adjust the ratio of R3 and R4 for  $V_{OUT} = 0V$ ). Full scale trimming can be accomplished by adjusting the amplitude of  $V_{IN}$  or by varying the value of R5.

R3, R4 and R5 must be selected to match within 0.01% and they should be the same type of resistor (preferably metal film) so that their temperature coefficients match. Mismatch of R3 to R4 causes both offset and full scale error. Mismatch of R5 to R4 and R3 causes full scale error.

Figure 7. Bipolar Operation (Offset Binary Coding)

| MSB  | inary Nui<br>DAC Re |      | Analog Output, V <sub>OUT</sub>         |

|------|---------------------|------|-----------------------------------------|

| 1111 | 1111                | 1111 | $+V_{IN}\left(\frac{2047}{2048}\right)$ |

| 1000 | 0000                | 0001 | $+V_{IN}\left(\frac{1}{2048}\right)$    |

| 1000 | 0000                | 0000 | ov                                      |

| 0111 | 1111                | 1111 | $-v_{IN}\left(\frac{1}{2048}\right)$    |

| 0000 | 0000                | 0000 | $-V_{IN}\left(\frac{2048}{2048}\right)$ |

Table II. Bipolar Code Table for Offset Binary Circuit of Figure 7

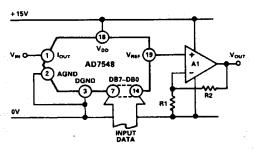

#### SINGLE SUPPLY OPERATION

Figure 8 shows the AD7548 connected in a voltage switching mode. The input voltage is connected to  $I_{OUT}$ . The D/A converter output voltage is taken from the  $V_{REF}$  pin and has a constant impedance equal to R.  $R_{FB}$  is not used in this circuit. The input voltage  $V_{IN}$  must always be positive with respect to AGND in order to prevent an internal diode from turning on. To maintain linearity the input voltage should remain within 2.5V of AGND with  $V_{DD}$  from +12V to +15V.

The output voltage V<sub>OUT</sub> of Figure 8 is expressed as

$$V_{OUT} = (V_{IN}) (D) \left( \frac{R_1 + R_2}{R_1} \right)$$

Where D is a fractional representation of the digital input word  $(0 \le D \le 4095/4096)$ .

Figure 8. Single Supply Operation Using Voltage Switching Mode

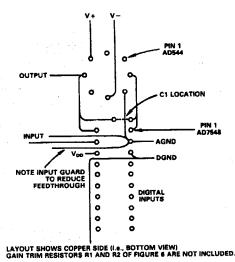

#### APPLICATION HINTS

Output Offset: CMOS D/A converters in circuits such as Figures 6 and 7 exhibit a code dependent output resistance which in turn cause a code dependent amplifier noise gain. The effect is a code dependent differential nonlinearity term at the amplifier output which, depends on  $V_{OS}$  where  $V_{OS}$  is the amplifier input offset voltage. To maintain monotonic operation it is recommended that  $V_{OS}$  be no greater than  $(25 \times 10^{-6})(V_{REF})$  over the temperature range of operation. Suitable op amps are AD517L and AD544L. The AD517L is best suited for fixed reference applications with low bandwidth requirements: it has extremely low offset  $(50\mu V)$  and in most applications will not require an offset trim. The AD544L has a much wider bandwidth and higher slew rate and is recommended for multiplying and other applications requiring fast settling. An offset trim on the AD544L may be necessary in some circuits.

General Ground Management: AC or transient voltages between AGND and DGND can cause noise injection into the analog output. The simplest method of ensuring that voltages at AGND and DGND are equal is to tie AGND and DGND together at

the AD7548. In more complex systems where the AGND and DGND intertie is on the backplane, it is recommended that two diodes be connected in inverse parallel between the AD7548 AGND and DGND pins (1N914 or equivalent).

Temperature Coefficients: The gain temperature coefficient of the AD7548 has a maximum value of 5ppm/°C and typical value of 2ppm/°C. This corresponds to worst case gain shifts of 2LSBs and 0.8LSBs respectively over a 100°C temperature range. When trim resistors R1 and R2 are used to adjust full scale range, the temperature coefficient of R1 and R2 should also be taken into account. The reader is referred to Analog Devices Application Note "Gain Error and Gain Temperature Coefficient of CMOS Multiplying DACs", Publication Number E630–10–6/81.

High Frequency Considerations: AD7548 output capacitance works in conjunction with the amplifier feedback resistance to add a pole to the open loop response. This can cause ringing or oscillation. Stability can be restored by adding a phase compensation capacitor in parallel with the feedback resistor.

Feedthrough: The dynamic performance of the AD7548 will depend upon the gain and phase stability of the output amplifier, together with the optimum choice of PC board layout and decoupling components. A suggested printed circuit layout for Figure 6 is shown in Figure 9 which minimizes feedthrough from V<sub>REF</sub> to the output in multiplying applications.

Figure 9. Suggested Layout for AD7548 and Op Amp

For additional information on multiplying DACs refer to "Application Guide to CMOS Multiplying D/A Converters", Publication Number G479-15-8/78, available from Analog Devices.

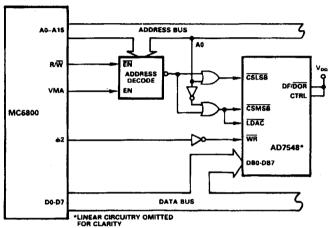

#### MICROPROCESSOR INTERFACING AD7548 - MC6800 INTERFACE

A typical 6800 configuration using the automatic transfer mode of the AD7548 is shown in Figure 10. Table III gives a sample loading routine written in re-entrant form. Data load and store instructions use extended addressing. The 12-bit data to be passed to the subroutine is stored in locations XXYY and XXYY + 1. The data is considered right-justified with the four most significant bits occupying the lower half of XXYY + 1. The AD7548 is assigned a base address of PPQQ. This address selects the low byte register of the AD7548. Address PPQQ + 1 selects both the high byte register and the LDAC control input.

Figure 10. AD7548 – MC6800 Interface (Automatic Transfer Mode)

| wwzz | JSR<br>PSH A<br>TPA | WWZZ                 | Jump to AD7548 subroutine<br>Push A onto stack |

|------|---------------------|----------------------|------------------------------------------------|

|      | PSH A<br>LDA A      | \$XXYY               | Push CCR onto stack                            |

|      | STA A               | \$PPQQ               | Load low byte to AD7548                        |

|      | LDA A<br>STA A      | \$XXYY+1<br>\$PPQQ+1 | Load high byte to AD7548                       |

|      | PULA                |                      | and update analog output                       |

|      | TAP                 |                      | Pull CCR from stack                            |

|      | <b>PULA</b>         |                      | Pull A from stack                              |

|      | RTS                 |                      | Return to main program                         |

Table III. Sample Routine for AD7548 - MC6800 Interface

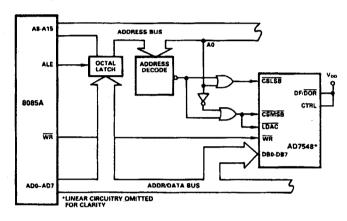

#### AD7548 - 8085A INTERFACE

Figure 11 shows a typical AD7548 to 8085A microprocessor interface configured for automatic transfer of 8 + 4-bit right-justified data. Table IV gives a sample loading routine written in re-entrant form. The 12-bit data to be passed to the subroutine is stored in locations XXYY and XXYY + 1. The four most significant data bits occupy the lower half of XXYY + 1. As before, addresses PPQQ and PPQQ + 1 select the CSLSB and CSMSB/LDAC control inputs respectively. Since only two instructions (LHLD, SHLD) are required to both fetch and load the 12-bit data word to the AD7548, it may be more efficient to insert these instructions as required in the main program rather than use a subroutine such as illustrated here.

Figure 11. AD7548 – 8085A Interface (Automatic Transfer Mode)

|                | CALL | 7548 |                        |

|----------------|------|------|------------------------|

| 7548           | PUSH | PSW  | Push register contents |

|                |      |      | onto stack             |

| and the second | PUSH | H    |                        |

|                | LHLD | XXYY | Fetch 12-bit data      |

|                | SHLD | PPQQ | Load 12-bit data       |

|                | POP  | Н    | Pop register contents  |

|                |      |      | from stack             |

|                | POP  | PSW  | •                      |

|                | RET  |      | Return to main program |

Table IV. Sample Routine for AD7548-8085A Interface

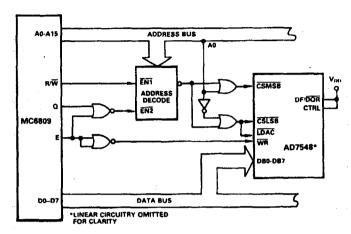

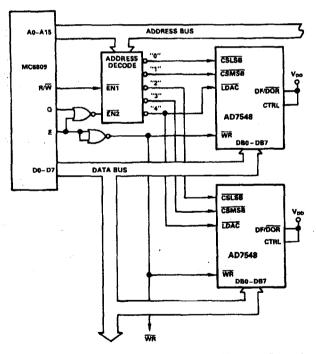

#### AD7548 - MC6809 INTERFACE

The AD7548 can be interfaced to the MC6809 microprocessor as shown in Figure 12 for automatic transfer of 8 +4-bit data. Similar to the 8085A instructions LHLD and SHLD, the 6809 has two instructions to fetch and store 12-bit (16-bit) data to the AD7548, LDD and STD. However, in the 6809, the high byte of data is moved first, then the low byte (this is the opposite of the 8085A). This means that if the 12-bit data is assumed to reside at addresses XXYY and XXYY+1 then XXYY must contain the high byte. It also means that the address decoding logic of Figure 11 must be slightly changed so that the even-order

AD7548 address, PPQQ from before, selects the CSMSB input to load the high byte first. In this automatic transfer configuration LDAC is tied to the CSLSB input. The AD7548 analog output can thus be updated using only two instructions as follows:

LDD \$XXYY STD \$PPQQ

The strobed transfer configuration is shown in Figure 13 with a dedicated decoder output assigned to each chip select input. The common LDAC signal allows simultaneous update of both AD7548 DAC registers.

Figure 12. AD7548 - MC6809 Interface (Automatic Transfer Mode)

Figure 13. AD7548 – MC6809 Interface (Strobed Transfer Mode)

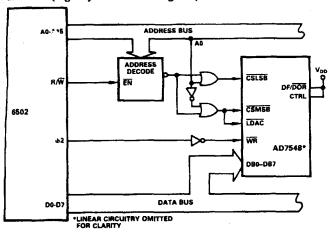

#### **AD7548 - 6502 INTERFACE**

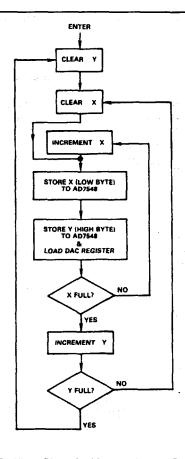

Figure 14 shows a typical AD7548 to 6502 microprocessor interface configured for automatic transfer of right-justified data. As a programming example, Figure 15 shows a flow chart for producing a 12-bit (4095-step-max) voltage ramp under 6502 control. Index registers X and Y of the 6502 form a 12-bit counter with the X-register holding the low byte of data and the Y-register the high byte. Table V shows the program listing. The X-register is compared with FF<sub>H</sub> and the Y-register with 10<sub>H</sub> to determine when the ramp voltage has reached its maximum value (FFF<sub>H</sub>). By changing the comparison data in the program the maximum ramp output voltage can be varied from levels corresponding to FFF<sub>H</sub> down to 000<sub>H</sub>. In the program listing of Table V the AD7548 has been assigned contiguous addresses 0400 (low byte) and 0401 (high byte and DAC register).

Figure 14. AD7548 – 6502 Interface (Automatic Transfer Mode)

Figure 15. Flow Chart for Voltage Ramp Generation

| ADDRESS | OP-CODE | MNEMONIC | OPERAND  |

|---------|---------|----------|----------|

| 0000    | A0      | LDY      | # 00     |

| 01      | 00      |          |          |

| 02      | A2      | LDX      | # 00     |

| 03      | 00      |          |          |

| 04      | 4C      | JMP      | 0008     |

| 05      | 08      |          |          |

| 06      | 00      |          |          |

| 07      | E8      | INX      |          |

| 08      | 8E      | STX      | 0400     |

| 09      | 00      |          |          |

| 0A      | 04      |          |          |

| 0B      | 8C      | STY      | 0401     |

| 0C      | 01      | · ·      | ł        |

| 0D      | 04      |          |          |

| 0E      | E0      | CPX      | # FF     |

| 0F      | FF      |          |          |

| 10      | D0      | BNE      | 0007     |

| 11      | F5      | Ì        |          |

| 12      | C8      | INY      |          |

| 13      | C0      | CPY      | # 10     |

| 14      | 10      | <b>,</b> | 1 .      |

| 15      | D0      | BNE      | 0002     |

| 16      | EB      | 1        | ł        |

| 17      | FO      | BEQ      | 0000     |

| 0018    | E7      |          | <u> </u> |

Table V. Program Listing for Figure 15

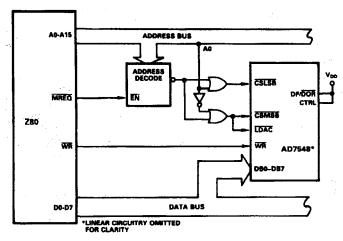

#### AD7548 - Z80 INTERFACE

Figure 16 shows a typical AD7548 to Z80 microprocessor interface configured for automatic transfer of right-justified data. Similar to the 8085A and 6809 cases, 16-bit load instructions are available in the Z80 which can fetch and load 12-bit data to the AD7548. Since the low byte of data is moved first and assuming the 12-bit data resides at addresses XXYY and XXYY + 1, address XXYY must contain the low byte. As before, addresses PPQQ and PPQQ + 1 select the AD7548 CSLSB and CSMSB/LDAC control inputs respectively. Choosing the Z80 register pair BC to hold the 12-bit data, the two instructions required to update the AD7548 analog output are as follows:

LD BC, (XXYY) LD (PPQQ), BC

Figure 16. AD7548 – Z80 Interface (Automatic Transfer Mode)

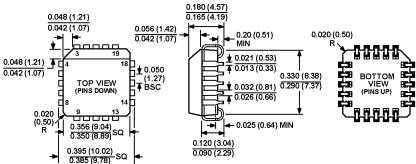

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

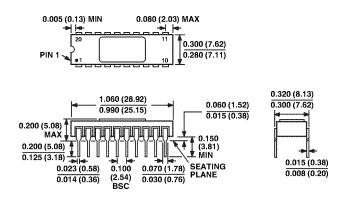

#### 20-Lead Plastic Dual In-Line Package [PDIP] (N-20)

Dimensions shown in inches and (millimeters)

COMPLIANT TO JEDEC STANDARDS MO-095-AE

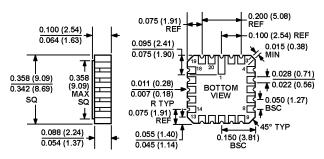

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

COMPLIANT TO JEDEC STANDARDS MO-047AA

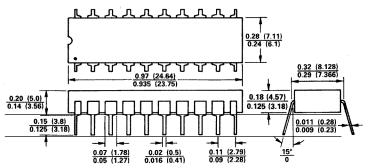

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

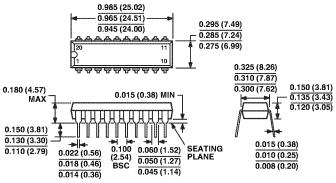

Figure 40. 20-Lead Plastic Leaded Chip Carrier [PLCC]

(P-20A)

Dimensions shown in inches and (mm)

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 24. 20-Terminal Ceramic Leadless Chip Carrier [LCC] (E-20)

Dimensions shown in inches and (millimeters)

20-Lead Cerdip (Q-20)