# CYBUS3384

Dual 5-Bit Bus Switch

SCDS103 - May 1994 - Revised February 2000

# Features

- Zero propagation delay

- + 2 $\Omega$  switches connect inputs to outputs

- Direct bus connection when switches are ON

- High (>500 Meg Ω) resistance when switch is OFF

Performs bidirectional translator function between

- 3.3V and 5.0V power supplies

- CMOS for low power dissipation

- Edge-rate control circuitry for significantly improved noise characteristics

- Inputs and outputs interface with 5.0V CMOS, TTL, or 3.3V CMOS

- ESD > 2000V

- · Power-off disable

# Functional Description

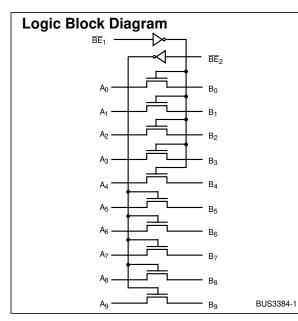

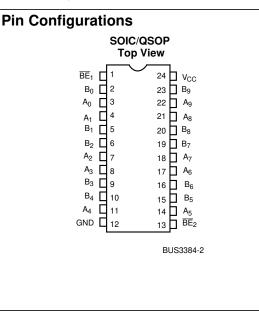

The CYBUS3384 is a ten-bit, two-port bidirectional bus switch that allows one bus to be connected directly to, or isolated from, another without introducing additional propagation delay or ground noise. The input and output voltage levels allow direct interface with TTL and CMOS devices. Two bus enable signals,  $\overline{BE}_1$  and  $\overline{BE}_2$ , turn on the upper and lower five bits, respectively.

Designed with a low resistance of  $2\Omega$ , the CYBUS3384 is ideal for use in VME or other high DC drive applications.

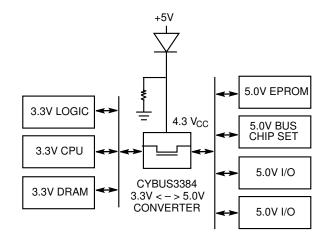

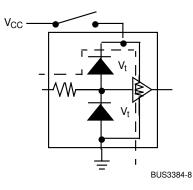

The power-off disable feature enables modules and cards to be either inserted or withdrawn from operating equipment without shutting down power. Additionally, the CYBUS3384 facilitates bidirectional interfacing between 3.3V and 5V systems by placing a single diode in series with the 5V V<sub>CC</sub> line and a resistor from pin 24 to ground.

The CYBUS3384 is also suitable for small signal analog applications where crosstalk and off isolation performance of -66 dB at 50 MHz are required.

# **Pin Description**

| Name                               | Description              |

|------------------------------------|--------------------------|

| A                                  | Bus A, Inputs or Outputs |

| В                                  | Bus B, Inputs or Outputs |

| $\overline{BE}_1, \overline{BE}_2$ | Bus Switch Enable        |

# Function Table<sup>[1]</sup>

| E <sub>2</sub> | B <sub>0-4</sub> | В <sub>5–9</sub> | Function                  |

|----------------|------------------|------------------|---------------------------|

| 1              |                  |                  |                           |

| - I            | High-Z           | High-Z           | Non-connect               |

| +              | A <sub>0-4</sub> | High-Z           | Connect                   |

| _              | High-Z           | A <sub>5-9</sub> | Connect                   |

| _              | A <sub>0-4</sub> | A <sub>5-9</sub> | Connect                   |

|                | - <br>           |                  | L High-Z A <sub>5–9</sub> |

Note:

1. H = HIGH Voltage Level. L = LOW Voltage Level. X = Don't Care.

# Maximum Ratings<sup>[2, 3]</sup>

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +165°C                       |

|---------------------------------------------------------|

| Ambient Temperature with<br>Power Applied65°C to +135°C |

| Supply Voltage to Ground Potential0.5V to +7.0V         |

| DC Input Voltage0.5V to +7.0V                           |

| DC Output Voltage0.5V to +7.0V                          |

| DC Output Current (Maximum Sink Current/Pin)120 mA      |

| Power Dissipation              | 0.5W    |

|--------------------------------|---------|

| Static Discharge Voltage       | .>2001V |

| (per MIL-STD-883, Method 3015) |         |

# **Operating Range**

| Range      | Ambient<br>Temperature | v <sub>cc</sub> |

|------------|------------------------|-----------------|

| Commercial | –40°C to +85°C         | 4.0V to 5.5V    |

Electrical Characteristics Over the Operating Bange

| Parameter        | Description                                 | Test Conditions                                                       | Min. | <b>Typ.</b> <sup>[4]</sup> | Max. | Unit |

|------------------|---------------------------------------------|-----------------------------------------------------------------------|------|----------------------------|------|------|

| V <sub>IH</sub>  | Input HIGH Voltage                          | Control Inputs Only                                                   | 2.0  |                            |      | V    |

| V <sub>IL</sub>  | Input LOW Voltage                           | Control Inputs Only                                                   |      |                            | 0.8  | V    |

| V <sub>H</sub>   | Hysteresis <sup>[5]</sup>                   | Control Inputs Only                                                   |      | 0.2                        |      | V    |

| V <sub>IK</sub>  | Input Clamp Diode Voltage                   | V <sub>CC</sub> =Min., I <sub>IN</sub> =-18 mA                        |      | -0.7                       | -1.2 | V    |

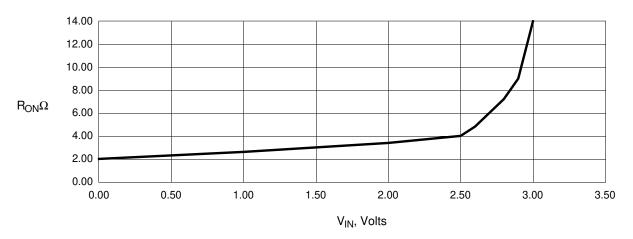

| R <sub>ON</sub>  | Switch On Resistance <sup>[6]</sup>         | V <sub>CC</sub> =4.75V, V <sub>IN</sub> =0.0V, I <sub>ON</sub> =30 mA |      | 2                          | 4    | W    |

|                  |                                             | V <sub>CC</sub> =4.75V, V <sub>IN</sub> =2.4V, I <sub>ON</sub> =15 mA |      | 4                          | 8    | W    |

| I <sub>IN</sub>  | Input Leakage Current                       | V <sub>CC</sub> =Max., V <sub>IN</sub> =V <sub>CC</sub>               |      |                            | ±1   | μA   |

| I <sub>OZ</sub>  | Off State Current (High-Z)                  | V <sub>CC</sub> =Max., V <sub>OUT</sub> =0.5V                         |      | 0.001                      | ±1   | μA   |

| I <sub>OFF</sub> | Power-Off Disable                           | $V_{CC}=0V, V_{OUT}=4.5V, V_{IN}=V_{CC}$                              |      |                            | ±1   | μA   |

| I <sub>OS</sub>  | Output Short Circuit Current <sup>[7]</sup> | V <sub>CC</sub> =Max., V <sub>OUT</sub> =0.0V                         |      | 100                        |      | mA   |

# On Resistance vs. $V_{IN} @ 4.75 V_{CC}$

#### Notes:

- 2. 3.

- 4.

- 5

- Unless otherwise noted, these limits are over the operating free-air temperature range. Unused inputs must always be connected to an appropriate logic voltage level, preferably either V<sub>CC</sub> or ground. Typical values are at V<sub>CC</sub>=5.0V, T<sub>A</sub>=+25°C ambient. This parameter is specified but not tested. Measured by voltage drop between A and B pin at indicated current through the switch. On resistance is determined by the lower of the voltages on pin A 6.

- Not more than one output should be shorted at a time. Duration of short should not exceed one second. The use of high-speed test apparatus and/or sample and hold techniques are preferable in order to minimize internal chip heating and more accurately reflect operational values. Otherwise prolonged shorting of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parametric tests. In any sequence of parameter tests, I<sub>OS</sub> tests should be performed last. 7.

# Capacitance<sup>[6]</sup>

| Parameter        | Description        | <b>Typ.</b> <sup>[4]</sup> | Max. | Unit |

|------------------|--------------------|----------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | 3                          | 4    | pF   |

| C <sub>OUT</sub> | Output Capacitance | 7                          | 8    | pF   |

### **Power Supply Characteristics**

| Parameter        | Description                                                   | Test Conditions <sup>[8]</sup>                                                                  |       | <b>Typ.</b> <sup>[4]</sup> | Max.       | Unit |

|------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------|----------------------------|------------|------|

| I <sub>CC</sub>  | Quiescent Power Supply Current                                | V <sub>CC</sub> =Max., V <sub>IN</sub> ≤GND or V <sub>CC</sub> , f=0                            | 3384  | 0.2                        | 3.0        | μA   |

|                  |                                                               |                                                                                                 | 3L384 | 0.2                        | 3.0        | μA   |

| Δl <sub>CC</sub> | Quiescent Power Supply Current<br>(Input HIGH) <sup>[9]</sup> | V <sub>CC</sub> =Max., V <sub>IN</sub> =3.4V, f=0, Per Control I                                | nput  |                            | 2.0        | mA   |

| ICCD             | Dynamic Power Supply Current <sup>[10]</sup>                  | V <sub>CC</sub> =Max., Control Input Toggling,<br>@ 50% Duty Cycle, A & B Pins Open             |       | 0.12                       | mA/<br>MHz |      |

| I <sub>C</sub>   | Total Power Supply Current <sup>[11, 12]</sup>                | V <sub>CC</sub> =Max.,                                                                          | 3384  |                            | 4.4        | mA   |

|                  |                                                               | Two Control Inputs Toggling, @ 50%<br>Duty Cycle, f <sub>1</sub> =10 MHz, V <sub>IN</sub> =3.4V | 3L384 |                            | 4.4        | mA   |

# Switching Characteristics Over the Operating Range<sup>[13]</sup>

|                                      |                                                                                      | Comme | ercial |      |

|--------------------------------------|--------------------------------------------------------------------------------------|-------|--------|------|

| Parameter                            | Description                                                                          | Min.  | Max.   | Unit |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>A to B <sup>[14, 15]</sup>                                      |       | .25    | ns   |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | Switch Turn On Delay,<br>$\overline{BE}_1$ , $\overline{BE}_2$ to A, $B^{[13]}$      | 1.5   | 6.5    | ns   |

| t <sub>PHZ</sub><br>t <sub>PHZ</sub> | Switch Turn Off Delay,<br>$\overline{BE}_1$ , $\overline{BE}_2$ to A, $B^{[13, 14]}$ | 1.5   | 5.5    | ns   |

| Q <sub>ci</sub>                      | Charge Injection, Typical <sup>[16, 17]</sup>                                        |       | 1.5    | рС   |

Notes:

8. 9.

For conditions shown as MIN or MAX use the appropriate values specified under DC specifications. Per TTL driven input ( $V_{IN}$ =3.4V); A and B pins do not contribute to I<sub>CC</sub>. All other inputs at V<sub>CC</sub> or GND. This current applies to the control inputs only and represents the current required to switch internal capacitance at the specified frequency. The A and B inputs generate no significant AC or DC currents as they transition. This parameter is not tested but is specified by design. I<sub>C</sub> = I<sub>QUIESCENT</sub> + I<sub>INPUTS</sub> + I<sub>DYNAMIC</sub> I<sub>C</sub> = U<sub>CC</sub>+ $\Delta$ I<sub>CC</sub>D<sub>H</sub>N<sub>T</sub>+I<sub>CCD</sub>( $f_0/2 + f_1$ N<sub>1</sub>) I<sub>CC</sub> = Quiescent Current with CMOS input levels  $\Delta$ I<sub>CC</sub> = Power Supply Current for a TTL HIGH input (V<sub>IN</sub>=3.4V) D<sub>H</sub> = Duty Cycle for TTL inputs HIGH 10. 11.

- D<sub>H</sub> N<sub>T</sub> = Duty Cycle for TTL inputs HIGH

- $N_T$  = Number of TTL inputs at  $D_H$  $I_{CCD}$  = Dynamic Current caused by an input transition pair (HLH or LHL)

- I<sub>CCD</sub> = Dynamic Current caused by an input transition pair (HLH or LHL)

f<sub>0</sub> = Clock frequency for registered devices, otherwise zero

f<sub>1</sub> = Input signal frequency

Number of inputs changing at f<sub>1</sub>

Note that activity on A or B inputs do not contribute to I<sub>C</sub>. The switches merely connect and pass through activity on these pins.

See Test Circuit and Waveform. Minimum limits are specified but not tested.

This parameter is specified by design but not tested.

The waveful experimentation of a part of a part of the part of th

- This parameter is specified by design but not tested.

The bus switch contributes no propagation delay other than the RC delay of the on resistance of the switch and the load capacitance. The time constant for the switch is much smaller than the rise/fall times of typical driving signals, it adds very little propagation delay to the system. Propagation delay of the bus switch when used in a system is determined by the driving circuit on the driving side of the switch and its interaction with the load on the driven side.

Measured at switch turn off, A to C, load=50 pF in parallel with 10 meg scope probe, V<sub>IN</sub> at A=0.0V.

# **Ordering Information CYBUS3384**

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                  | Operating<br>Range |

|---------------|---------------|-----------------|-------------------------------|--------------------|

| 0.25          | CYBUS3384QCT  | Q13             | 24-Lead (150-Mil) QSOP        | Commercial         |

|               | CYBUS3384SOCT | S13             | 24-Lead (300-Mil) Molded SOIC |                    |

Figure 1. CYBUS3384

# **Application Information**

The CYBUS3384 is a ten-channel bidirectional solid state bus switch with a "near zero" propagation delay.

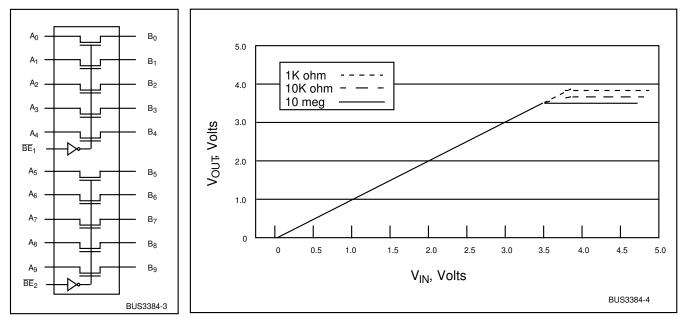

The CYBUS3384 is organized into two groups of five N-Channel MOSFETs. Each group has an independent control input for output enable (see *Figure 1*). Because the N-channel MOSFET is physically symmetric, the device pin can act as an input or an output.

The two enable input ( $\overline{BE}_1$  and  $\overline{BE}_2$ ) sense TTL level signals and drive the gates of the N-channel MOSFETs to VCC. With the gate at V<sub>CC</sub>, the output voltage will follow the input voltage up to V<sub>CC</sub> minus the threshold voltage. At this point the N-channel MOSFET begins to turn off, rapidly increasing the effective resistance (R<sub>ON</sub>) such that further increases to input voltage no longer increase the output voltage (see *Figure 2*).

When either the input or output of the CYBUS3384 is near zero volts and the gate is at  $V_{CC}$ , the device is fully on, (low resistance) and available to pass large currents in either direction. In this condition, the CYBUS3384 inputs are directly connected to the outputs.

The CYBUS3384 provides no signal drive itself. As a result the rise and fall times of the CYBUS3384 outputs are determined by the device driving the CYBUS3384 inputs rather than the CYBUS3384 itself.

The propagation delay contributed by the CYBUS3384 is essentially zero when the N-channel gate is at  $V_{CC}$ .

#### Figure 2. V<sub>OUT</sub> vs. Volts

When the device is unpowered, the CYBUS3384 draws no current from the I/O or control inputs, and there is no current path from the I/O or control to the power pins. There are no back power or current drain problems when the device is unpowered.

The CYBUS3384 provides an ideal interface between 5V and 3.3V components, since the CYBUS3384 provides no signal drive, the  $I_{CC}$  demands are small, limited to AC switching of the N-channel gates, control circuitry, and a minute amount of I/O leakage. Due to the low current demands of the CYBUS3384, it is possible to lower the CYBUS3384 VCC from a standard 5.0V supply with a small, inexpensive diode and a resistor to provide a low-current full-bidirectional signal compatibility between 5V logic family signals and 3.3V logic family signals.

By adding a small, inexpensive diode and a resistor, the CYBUS3384 V<sub>CC</sub> supply voltage can be shifted to 4.3V as shown in *Figure 3.* 5V signals will then be limited to 3.3V as they pass through the CYBUS3384. 3.3V signals will pass back through the CYBUS3384 unaltered and provide compatibility with 5V TTL input requirements. Note that the conversion is bidirectional and is limited to 3.3V independent of which side is driven to 5V. The CYBUS3384 could convert 5V signals for use on a 3.3V bus or convert a 5V bus to signals compatible with 3.3V components.

#### 3.3V/5V Supply Operation

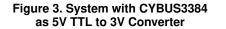

In certain system applications, the CYBUS3384 must operate from either a 5V or 3.3V power supply, depending on the state

of the system. If this occurs, the circuit shown in *Figure 4* can be added to step the 3.3V supply up to a nominal 5V level. The low-cost, high-efficiency Step Up regulator shown in the figure is available from Texas Instruments and other suppliers. The diode arrangement will automatically select the active supply. Standard silicon diodes can be used because the CYBUS3384  $V_{CC}$  is specified at 4.0V.

BUS3384-5

Figure 4. 3.3V/5V Supply Switch

#### Low Power Bus Isolation

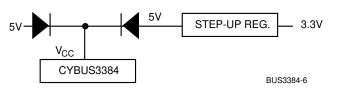

Modern battery-operated systems rely on internal power management schemes to disconnect power from subsystems not in use. Usually the subsystem bus input ESD protection circuits consist of a pair of clamp diodes to limit input voltage excursions to a maximum of  $V_{CC}$ +Vt and –Vt (see *Figure 5*). Removing power from these causes the VCC ESD clamp diode to connect the dead circuit inputs to GND, often significantly increasing bus loading and power dissipation (see *Figure 6*). The CYBUS3384 placed on the input of the load to be disconnected effectively prevents bus loading and its associated problems.

BUS3384-7

Figure 5. Gate Input (Power ON)

Figure 6. Gate Input (Power OFF)

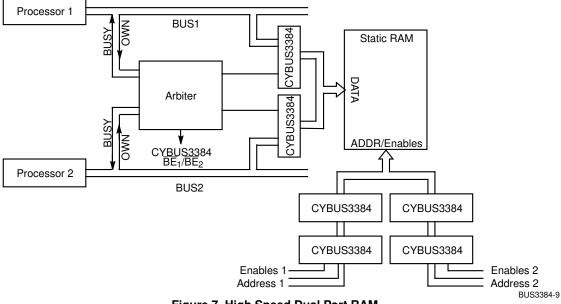

Figure 7. High Speed Dual Port RAM

### **High Speed Dual Port RAM**

As shown in Figure 7, a high-speed, dual-port memory is implemented using a combination of commodity SRAM, a simple arbitration circuit, and the CYBUS3384. Processor 1 is the system host processor while Processor 2 is dedicated peripheral processor (such as a DSP for acquiring and manipulating data). Either processor can own the SRAM by first reading the BUSY bit to determine if the SRAM is available. If so, the requesting processor takes control by writing the OWN bit (which redirects the bus through the CYBUS3384s and sets the BUSY bit notifying the other bus the SRAM is not available). Processor 1 owns the bus and may now access the SRAM as needed. When finished, Processor 1 resets the OWN bit releasing the SRAM. The SRAM access sequence is identical for Processor 2. In this application, the CYBUS3384 saves 10 ns compared to using an F244 address buffer and an F245 data bus transceiver. This, in turn, allows the use of slower, less expensive SRAM, resulting in lower system cost and power savings.

#### **Selectable Termination Loads**

In some applications, it is desirable to vary the characteristic termination impedance as the system configuration changes. This is a common problem in automatic test equipment applications. Because of their low ON resistance, miniature relays are often used to switch termination loads. A single CYBUS3384 can replace as many as 10 such relays resulting in faster switching operation, lower power, and significant cost savings.

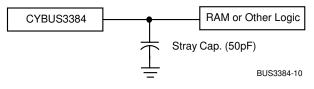

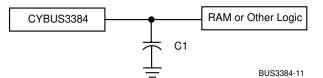

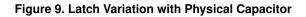

#### Fast Latch

*Figures 8* and *9* show variations of a latch having a sub 1-ns propagational delay time using the CYBUS3384 in combination with other components. This circuit has the advantage of being four to ten times faster than an equivalent implementation using a 373 latch—and with no added noise. *Figure 8* relies on the stray capacitance of the bus to maintain data when the CYBUS3384 opens. Assuming 50-pF stray capacitance

tance at room temperature and a 1 microampere input leakage current, a 1 volt "droop" from the initial voltage level would take 50 microseconds. *Figure 9* shows the addition of a physical capacitor if there is insufficient stray capacitance. *Figure 10* shows an active bus termination capable of sustaining the programmed logic for an indefinite period of time in the presence of  $V_{CC}$ .

Figure 8. Latch Variation with Spray Capacitance

Figure 10. Active Bus Termination

Document #: 38-00355

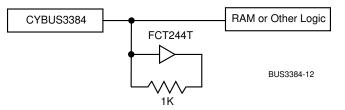

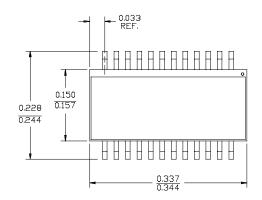

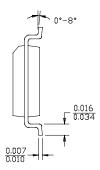

# **Package Diagrams**

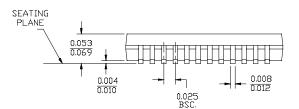

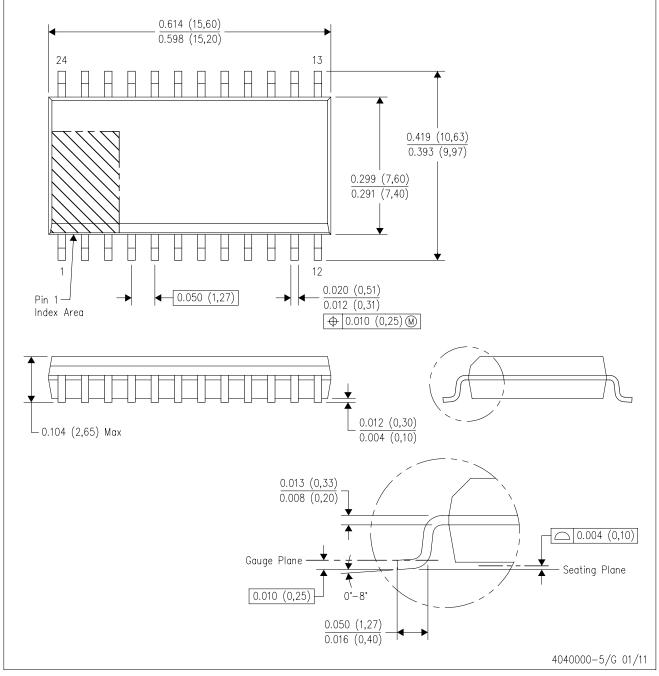

#### 24-Lead Quarter Size Outline Q13

DIMENSIONS IN INCHES  $\frac{\text{MIN.}}{\text{MAX.}}$ Lead Coplanarity 0.004 Max.

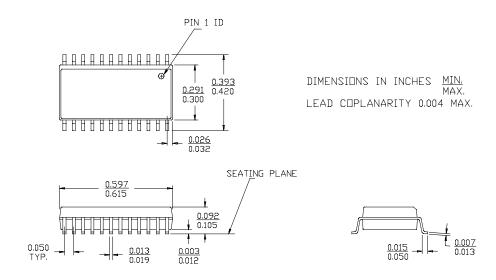

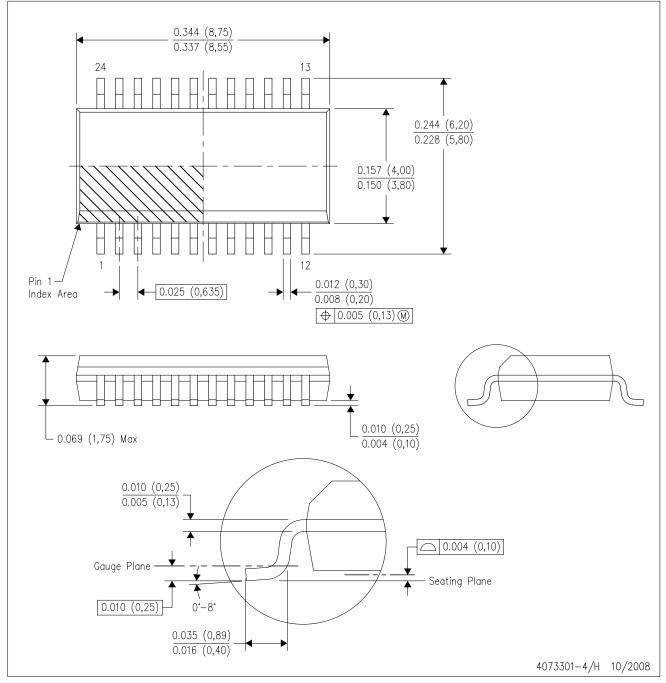

# 24-Lead (300-Mil) Molded SOIC S13

# PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| CYBUS3384QC      | OBSOLETE              | SSOP/<br>QSOP   | DBQ                | 24                  | TBD                     | Call TI          | Call TI                      |

| CYBUS3384QCT     | OBSOLETE              | SSOP/<br>QSOP   | DBQ                | 24                  | TBD                     | Call TI          | Call TI                      |

| CYBUS3384SOC     | OBSOLETE              | SOIC            | DW                 | 24                  | TBD                     | Call TI          | Call TI                      |

| CYBUS3384SOCT    | OBSOLETE              | SOIC            | DW                 | 24                  | TBD                     | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. **TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

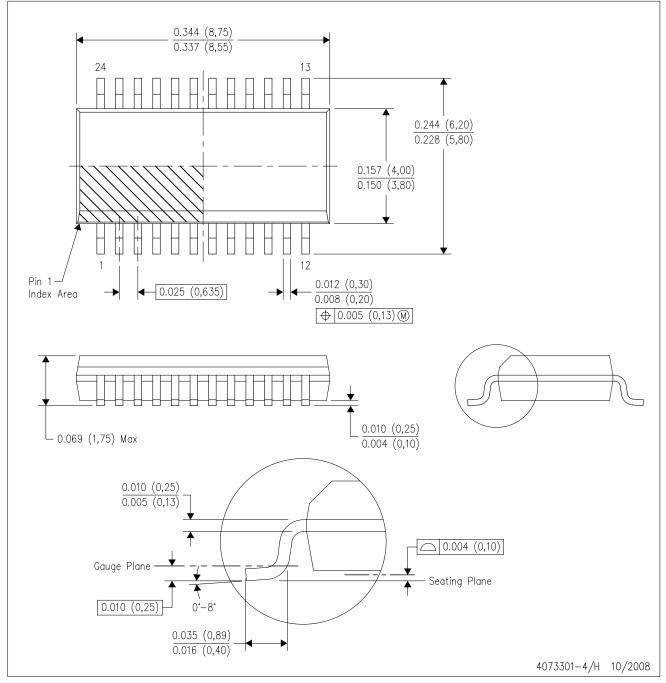

DBQ (R-PDSO-G24)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15) per side.

D. Falls within JEDEC MO-137 variation AE.

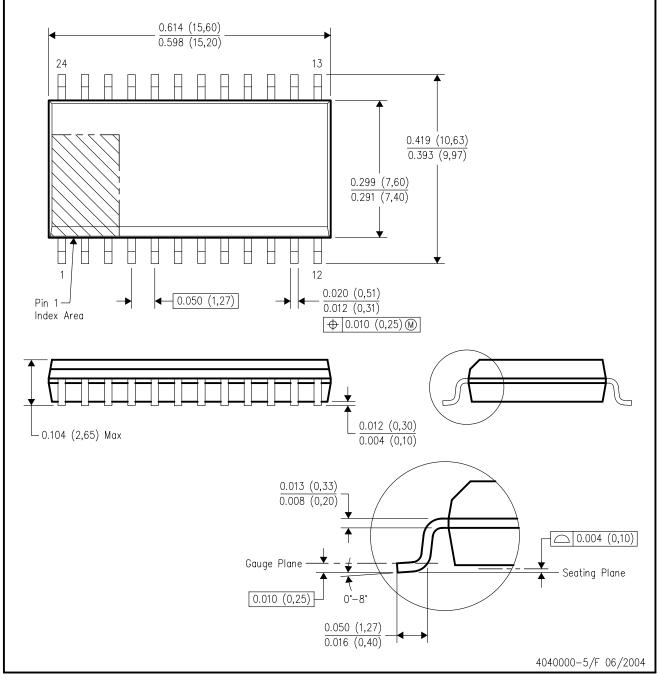

DW (R-PDSO-G24)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013 variation AD.

11-Apr-2013

# PACKAGING INFORMATION

| Orderable Device | Status   | Package Type | Package | Pins | Package | Eco Plan | Lead/Ball Finish | MSL Peak Temp | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|----------|--------------|---------|------|---------|----------|------------------|---------------|--------------|-------------------|---------|

|                  | (1)      |              | Drawing |      | Qty     | (2)      |                  | (3)           |              | (4)               |         |

| CYBUS3384QC      | OBSOLETE | SSOP         | DBQ     | 24   |         | TBD      | Call TI          | Call TI       | -40 to 85    |                   |         |

| CYBUS3384QCT     | OBSOLETE | SSOP         | DBQ     | 24   |         | TBD      | Call TI          | Call TI       | -40 to 85    |                   |         |

| CYBUS3384SOC     | OBSOLETE | SOIC         | DW      | 24   |         | TBD      | Call TI          | Call TI       | -40 to 85    |                   |         |

| CYBUS3384SOCT    | OBSOLETE | SOIC         | DW      | 24   |         | TBD      | Call TI          | Call TI       | -40 to 85    |                   |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and package, or 2) lead-based die adhesive used between the die and package, or 2) lead-based die adhesive used between the die and package.

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

DW (R-PDSO-G24)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters). Dimensioning and tolerancing per ASME Y14.5M-1994.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013 variation AD.

DBQ (R-PDSO-G24)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15) per side.

D. Falls within JEDEC MO-137 variation AE.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated