www.ti.com

## TRIPLE PROCESSOR SUPERVISORS

#### **FEATURES**

- Triple Supervisory Circuits for DSP and Processor-Based Systems

- Power-On Reset Generator With Fixed Delay Time of 200ms, No External Capacitor Needed

- Temperature-Compensated Voltage Reference

- Maximum Supply Current of 40μA

- Supply Voltage Range: 2V to 6V

- Defined RESET Output From V<sub>DD</sub> ≥ 1.1V

- MSOP-8 and SO-8 Packages

- Temperature Range: 40°C to +85°C

# SENSE1 1 8 V<sub>DD</sub> SENSE2 2 7 MR SENSE3 3 6 RESET GND 4 5 RESET

#### TYPICAL APPLICATIONS

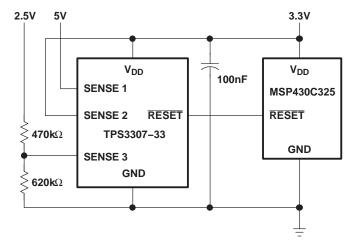

Figure 1 lists some of the typical applications for the TPS3307 family, and a schematic diagram for a processor-based system application. This application uses TI part numbers TPS3307-33 and MSP430C325.

- Applications using DSPs, Microcontrollers or Microprocessors

- Industrial Equipment

- Programmable Controls

- Automotive Systems

- Portable/Battery Powered Equipment

- Intelligent Instruments

- Wireless Communication Systems

- Notebook/Desktop Computers

Figure 1. Applications Using the TPS3307 Family

#### DESCRIPTION

The TPS3307 family is a series of micropower supply voltage supervisors designed for circuit initialization primarily in DSP and processor-based systems, which require more than one supply voltage.

The product spectrum of the TPS3307-xx is designed for monitoring three independent supply voltages: 3.3V/1.8V/adj, 3.3V/2.5V/adj or 3.3V/5V/adj. The adjustable SENSE input allows the monitoring of any supply voltage >1.25V.

The various supply voltage supervisors are designed to monitor the nominal supply voltage as shown in the following supply voltage monitoring table.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

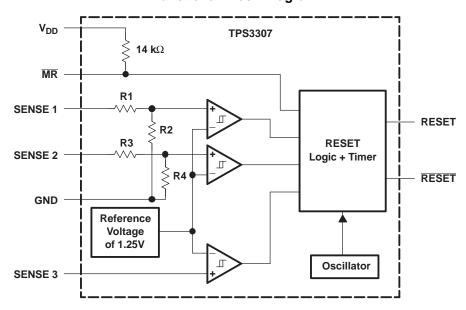

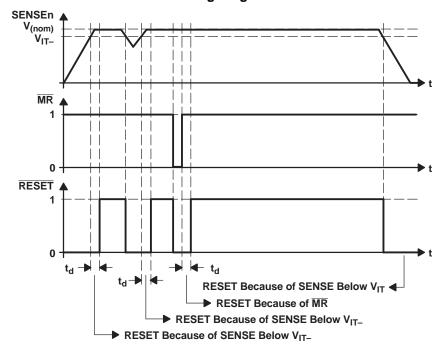

During power-on,  $\overline{\text{RESET}}$  is asserted when the supply voltage  $V_{DD}$  becomes higher than 1.1V. Thereafter, the supply voltage supervisor monitors the SENSEn inputs and keeps  $\overline{\text{RESET}}$  active as long as SENSEn remain below the threshold voltage  $V_{IT+}$ .

An internal timer delays the return of the  $\overline{\text{RESET}}$  output to the inactive state (high) to ensure proper system reset. The delay time,  $t_{d \text{ (typ)}} = 200 \text{ms}$ , starts after all SENSE *n* inputs have risen above the threshold voltage  $V_{\text{IT-}}$ . When the voltage at any SENSE input drops below the threshold voltage  $V_{\text{IT-}}$ , the  $\overline{\text{RESET}}$  output becomes active (low) again.

The TPS3307-xx family of devices incorporates a manual reset input,  $\overline{\text{MR}}$ . A low level at  $\overline{\text{MR}}$  causes  $\overline{\text{RESET}}$  to become active. In addition to the active-low  $\overline{\text{RESET}}$  output, the TPS3307-xx family includes an active-high RESET output.

The devices are available in either 8-pin MSOP or standard 8-pin SO packages.

The TPS3307-xx devices are characterized for operation over a temperature range of -40°C to +85°C.

#### SUPPLY VOLTAGE MONITORING

| DEVICE     | NON    | IINAL SUPERVISED V | OLTAGE       | THRESHOLD VOLTAGE (TYP) |        |                      |  |  |

|------------|--------|--------------------|--------------|-------------------------|--------|----------------------|--|--|

| DEVICE     | SENSE1 | SENSE2             | SENSE3       | SENSE1                  | SENSE2 | SENSE3               |  |  |

| TPS3307-18 | 3.3V   | 1.8V               | User defined | 2.93V                   | 1.68V  | 1.25V <sup>(1)</sup> |  |  |

| TPS3307-25 | 3.3V   | 2.5V               | User defined | 2.93V                   | 2.25V  | 1.25V <sup>(1)</sup> |  |  |

| TPS3307-33 | 5V     | 3.3V               | User defined | 4.55V                   | 2.93V  | 1.25V <sup>(1)</sup> |  |  |

(1) The actual sense voltage has to be adjusted by an external resistor divider according to the application requirements.

#### AVAILABLE OPTIONS(1)

|                | PACKAGI              | ED DEVICES                            |                        |                  |

|----------------|----------------------|---------------------------------------|------------------------|------------------|

| T <sub>A</sub> | SMALL OUTLINE<br>(D) | PowerPAD™<br>μ-SMALL OUTLINE<br>(DGN) | MARKING<br>DGN PACKAGE | CHIP FORM<br>(Y) |

|                | TPS3307-18D          | TPS3307-18DGN                         | TIAAP                  | TPS3307-18Y      |

| -40°C to +85°C | TPS3307-25D          | TPS3307-25DGN                         | TIAAQ                  | TPS3307-25Y      |

|                | TPS3307-33D          | TPS3307-33DGN                         | TIAAR                  | TPS3307-33Y      |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

#### **Function/Truth Tables**

| MR | SENSE1 > V <sub>IT1</sub> | SENSE2 > V <sub>IT2</sub> | SENSE3 > V <sub>IT3</sub> | RESET | RESET |

|----|---------------------------|---------------------------|---------------------------|-------|-------|

| L  | X <sup>(1)</sup>          | X <sup>(1)</sup>          | Х                         | L     | Н     |

| Н  | 0                         | 0                         | 0                         | L     | Н     |

| Н  | 0                         | 0                         | 1                         | L     | Н     |

| Н  | 0                         | 1                         | 0                         | L     | Н     |

| Н  | 0                         | 1                         | 1                         | L     | Н     |

| Н  | 1                         | 0                         | 0                         | L     | Н     |

| Н  | 1                         | 0                         | 1                         | L     | Н     |

| Н  | 1                         | 1                         | 0                         | L     | Н     |

| Н  | 1                         | 1                         | 1                         | Н     | L     |

(1) X = Don't care

#### **Functional Block Diagram**

## **Timing Diagram**

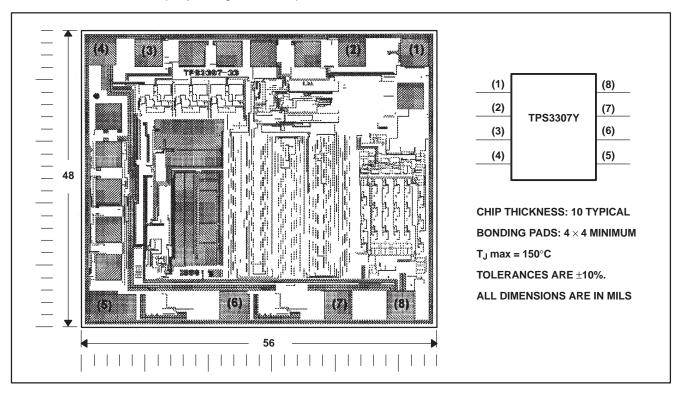

#### **TPS3307Y Chip Information**

These chips, when properly assembled, display characteristics similar to those of the TPS3307. Thermal compression or ultrasonic bonding may take place on the doped aluminium bonding pads. The chips may be mounted with conductive epoxy or a gold-silicon preform.

**Table 2. Terminal Functions**

| TERMIN   | TERMINAL |     | DESCRIPTION              |  |  |  |  |  |  |  |

|----------|----------|-----|--------------------------|--|--|--|--|--|--|--|

| NAME     | NO.      | I/O | DESCRIPTION              |  |  |  |  |  |  |  |

| GND      | 4        |     | Ground                   |  |  |  |  |  |  |  |

| MR       | 7        | I   | Manual reset             |  |  |  |  |  |  |  |

| RESET    | 5        | 0   | Active-low reset output  |  |  |  |  |  |  |  |

| RESET    | 6        | 0   | Active-high reset output |  |  |  |  |  |  |  |

| SENSE1   | 1        | I   | Sense voltage input 1    |  |  |  |  |  |  |  |

| SENSE2   | 2        | I   | Sense voltage input 2    |  |  |  |  |  |  |  |

| SENSE3   | 3        | I   | Sense voltage input 3    |  |  |  |  |  |  |  |

| $V_{DD}$ | 8        |     | Supply voltage           |  |  |  |  |  |  |  |

## Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted).

|                                                                                                | UNIT                           |

|------------------------------------------------------------------------------------------------|--------------------------------|

| Supply voltage, V <sub>DD</sub> <sup>(2)</sup>                                                 | 7V                             |

| MR pin                                                                                         | -0.3V to V <sub>DD</sub> +0.3V |

| All other pins <sup>(2)</sup>                                                                  | -0.3V to 7V                    |

| Maximum low output current, I <sub>OL</sub>                                                    | 5mA                            |

| Maximum high output current, I <sub>OH</sub>                                                   | −5mA                           |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>DD</sub> ) | ±20mA                          |

| Output clamp current, $I_{OK}$ ( $V_O < 0$ or $V_O > V_{DD}$ )                                 | ±20mA                          |

| Continuous total power dissipation                                                             | See Dissipation Rating Table   |

| Operating free-air temperature range, T <sub>A</sub>                                           | −40°C to +85°C                 |

| Storage temperature range, T <sub>stg</sub>                                                    | −65°C to +150°C                |

| Soldering temperature                                                                          | +260°C                         |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **Dissipation Rating Table**

| PACKAGE | T <sub>A</sub> ≤ +25°C<br>POWER RATING | ^         |       | T <sub>A</sub> = +85°C<br>POWER RATING |

|---------|----------------------------------------|-----------|-------|----------------------------------------|

| DGN     | 2.14W                                  | 17.1mW/°C | 1.37W | 1.11W                                  |

| D       | 725mW                                  | 5.8mW/°C  | 464mW | 377mW                                  |

#### **Recommended Operating Conditions**

At specified temperature range.

|                                                                              | MIN                   | MAX                                          | UNIT |

|------------------------------------------------------------------------------|-----------------------|----------------------------------------------|------|

| Supply voltage, V <sub>DD</sub>                                              | 2                     | 6                                            | V    |

| Input voltage at MR and SENSE3, VI                                           | 0                     | V <sub>DD</sub> + 0.3                        | V    |

| Input voltage at SENSE1 and SENSE2, V <sub>I</sub>                           | 0                     | (V <sub>DD</sub> +0.3)V <sub>IT</sub> /1.25V | V    |

| High-level input voltage at $\overline{MR}$ , $V_{IH}$                       | 0.7 x V <sub>DD</sub> |                                              | V    |

| Low-level input voltage at MR, V <sub>IL</sub>                               |                       | 0.3 × V <sub>DD</sub>                        | V    |

| Input transition rise and fall rate at $\overline{MR}$ , $\Delta t/\Delta V$ |                       | 50                                           | ns/V |

| Operating free-air temperature range, T <sub>A</sub>                         | -40                   | +85                                          | °C   |

<sup>(2)</sup> All voltage values are with respect to GND. For reliable operation the device must not be operated at 7V for more than t = 1000h continuously.

#### **Electrical Characteristics**

Over recommended operating free-air temperature range (unless otherwise noted).

|                | PARAMETER                                  |          | TEST CONDITIONS                                                                      | MIN                    | TYP  | MAX  | UNIT |

|----------------|--------------------------------------------|----------|--------------------------------------------------------------------------------------|------------------------|------|------|------|

|                |                                            |          | $V_{DD} = 2V \text{ to 6V}, I_{OH} = -20 \mu\text{A}$                                | V <sub>DD</sub> - 0.2V |      |      |      |

| $V_{OH}$       | High-level output voltage                  |          | $V_{DD} = 3.3V, I_{OH} = -2mA$                                                       | $V_{DD} - 0.4V$        |      |      | V    |

|                |                                            |          | $V_{DD} = 6V$ , $I_{OH} = -3mA$                                                      | $V_{DD} - 0.4V$        |      |      |      |

|                |                                            |          | $V_{DD} = 2V \text{ to 6V}, I_{OL} = 20\mu\text{A}$                                  |                        |      | 0.2  |      |

| $V_{OL}$       | Low-level output voltage                   |          | $V_{DD} = 3.3V, I_{OL} = 2mA$                                                        |                        |      | 0.4  | V    |

|                |                                            |          | $V_{DD} = 6V$ , $I_{OL} = 3mA$                                                       |                        |      | 0.4  |      |

|                | Power-up reset voltage <sup>(1)</sup>      |          | $V_{DD} \ge 1.1 V, I_{OL} = 20 \mu A$                                                |                        |      | 0.4  | V    |

|                |                                            | VSENSE3  | $V_{DD} = 2V \text{ to } 6V, T_A = 0^{\circ}C \text{ to } +85^{\circ}C$              | 1.22                   | 1.25 | 1.28 |      |

|                |                                            |          |                                                                                      | 1.64                   | 1.68 | 1.72 |      |

|                | Negative-going input threshold voltage (2) | VSENSE1, |                                                                                      | 2.20                   | 2.25 | 2.30 | V    |

|                |                                            | VSENSE2  |                                                                                      | 2.86                   | 2.93 | 3    |      |

|                |                                            |          |                                                                                      | 4.46                   | 4.55 | 4.64 |      |

| $V_{IT-}$      |                                            | VSENSE3  | $V_{DD} = 2V \text{ to } 6V,$<br>$T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ | 1.22                   | 1.25 | 1.29 | V    |

|                |                                            |          |                                                                                      | 1.64                   | 1.68 | 1.73 |      |

|                |                                            | VSENSE1, |                                                                                      | 2.20                   | 2.25 | 2.32 | V    |

|                |                                            | VSENSE2  |                                                                                      | 2.86                   | 2.93 | 3.02 | V    |

|                |                                            |          |                                                                                      | 4.46                   | 4.55 | 4.67 |      |

|                |                                            |          | V <sub>IT</sub> = 1.25V                                                              |                        | 10   |      |      |

|                |                                            |          | V <sub>IT</sub> = 1.68V                                                              |                        | 15   |      |      |

| $V_{hys}$      | Hysteresis at VSENSEn input                |          | V <sub>IT</sub> = 2.25V                                                              |                        | 20   |      | mV   |

|                |                                            |          | V <sub>IT</sub> = 2.93V                                                              |                        | 30   |      |      |

|                |                                            |          | V <sub>IT</sub> = 4.55V                                                              |                        | 40   |      |      |

|                |                                            | MR       | $\overline{MR} = 0.7 \times V_{DD}, V_{DD} = 6V$                                     |                        | -130 | -180 |      |

|                | High lovel input current                   | SENSE1   | VSENSE1 = V <sub>DD</sub> = 6V                                                       |                        | 5    | 8    | μΑ   |

| I <sub>H</sub> | I <sub>H</sub> High-level input current    | SENSE2   | $VSENSE2 = V_{DD} = 6V$                                                              |                        | 6    | 9    |      |

|                |                                            | SENSE3   | VSENSE3 = V <sub>DD</sub>                                                            | -25                    |      | 25   | nA   |

| 1.             | Low-level input current                    | MR       | $\overline{MR} = 0V, V_{DD} = 6V$                                                    |                        | -430 | -600 | μΑ   |

| IL             | Low-level input current                    | SENSEn   | VSENSE1,2,3 = 0V                                                                     | -25                    |      | 25   | nA   |

| $I_{DD}$       | Supply current                             |          |                                                                                      |                        |      | 40   | μΑ   |

| Ci             | Input capacitance                          |          | $V_I = 0V$ to $V_{DD}$                                                               |                        | 10   |      | pF   |

<sup>(1)</sup> The lowest supply voltage at which  $\overline{RESET}$  becomes active.  $t_r$ ,  $V_{DD} \ge 15 \mu s/V$  (2) To ensure best stability of the threshold voltage, a bypass capacitor (ceramic  $0.1 \mu F$ ) should be placed close to the supply terminals.

#### **Timing Requirements**

At  $V_{DD}$  = 2V to 6V,  $R_L$  = 1M $\Omega$ ,  $C_L$  = 50pF,  $T_A$  = +25°C.

| PARAMETER      |             |        | TEST CONDITIONS                                                 | MIN | TYP | MAX | UNIT |

|----------------|-------------|--------|-----------------------------------------------------------------|-----|-----|-----|------|

| t Dula a midth |             | SENSEn | $V_{SENSEnL} = V_{IT-} - 0.2V$ , $V_{SENSEnH} = V_{IT+} + 0.2V$ | 6   |     |     | μs   |

| ι <sub>w</sub> | Pulse width | MR     | $V_{IH} = 0.7 \times V_{DD}, V_{IL} = 0.3 \times V_{DD}$        | 100 |     |     | ns   |

## **Switching Characteristics**

At  $V_{DD}$  = 2V to 6V,  $R_L$  = 1M $\Omega$ ,  $C_L$  = 50pF,  $T_A$  = +25°C.

|                  | PARAMETER                                          |                                 | TEST CONDITIONS                                                                                     | MIN | TYP | MAX | UNIT |

|------------------|----------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>d</sub>   | Delay time                                         |                                 | $\frac{V_{I(SENSEn)} \geq V_{IT+} + 0.2V,}{MR \geq 0.7 \times V_{DD}. \text{ See Timing Diagram.}}$ | 140 | 200 | 280 | ms   |

| t <sub>PHL</sub> | Propagation (delay) time, high-to-low level output | MR to RESETMR to RESET          | $V_{I(SENSEn)} \ge V_{IT+} + 0.2V$                                                                  |     | 200 | 500 |      |

| t <sub>PLH</sub> | Propagation (delay) time, low-to-high level output | MR to RESETMR to RESET          | $V_{I(SENSEn)} \ge V_{IT+} + 0.2V,$<br>$V_{IH} = 0.7 \times V_{DD}, V_{IL} = 0.3 \times V_{DD}$     |     | 200 | 500 | ns   |

| t <sub>PHL</sub> | Propagation (delay) time, high-to-low level output | SENSEn to RESET SENSEn to RESET | $V_{IH} = V_{IT+} + 0.2V, V_{IL} = V_{IT-} - 0.2V,$                                                 |     | 4   | 5   |      |

| t <sub>PLH</sub> | Propagation (delay) time, low-to-high level output | SENSEn to RESET SENSEn to RESET | MR ≥ 0.7 × V <sub>DD</sub>                                                                          |     | 1   | 5   | μs   |

SENSEn = V<sub>DD</sub>

MR = Open T<sub>A</sub> = 25°C

#### **Typical Characteristics**

18

-4

-6

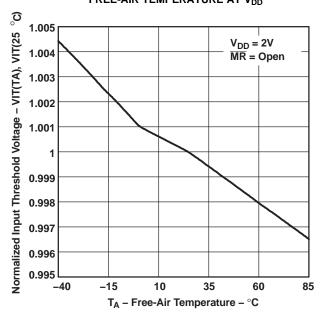

# NORMALIZED SENSE THRESHOLD VOLTAGE vs FREE-AIR TEMPERATURE AT $V_{DD}$

Figure 2.

##

SUPPLY CURRENT VS

SUPPLY VOLTAGE

Figure 3.

-0.5 0 0.5 1 1.5 2 2.5 3 3.5 4 4.5 5 5.5 6 6.5 7

V<sub>DD</sub> - Supply Voltage - V

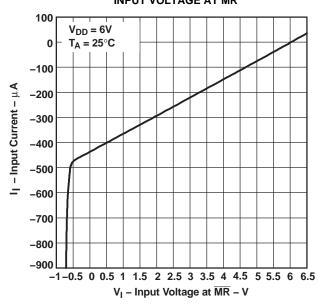

# INPUT CURRENT vs INPUT VOLTAGE AT MR

Figure 4.

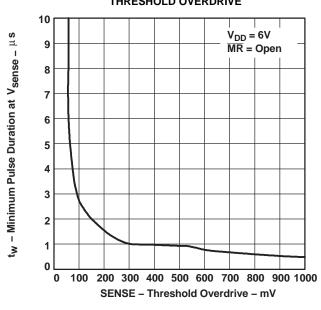

# MINIMUM PULSE DURATION AT SENSE VS THRESHOLD OVERDRIVE

Figure 5.

#### **Typical Characteristics (continued)**

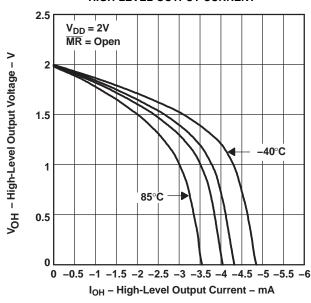

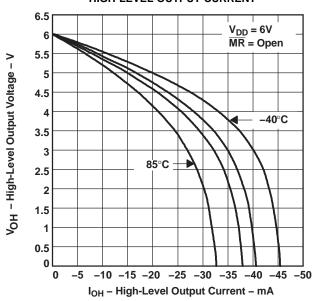

# HIGH-LEVEL OUTPUT VOLTAGE VS HIGH-LEVEL OUTPUT CURRENT

### Figure 6.

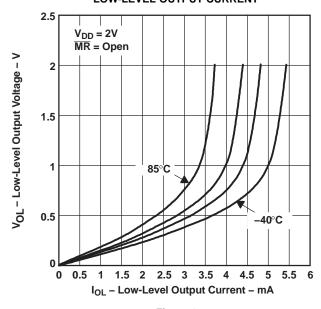

# LOW-LEVEL OUTPUT VOLTAGE vs LOW-LEVEL OUTPUT CURRENT

Figure 8.

# HIGH-LEVEL OUTPUT VOLTAGE VS HIGH-LEVEL OUTPUT CURRENT

Figure 7.

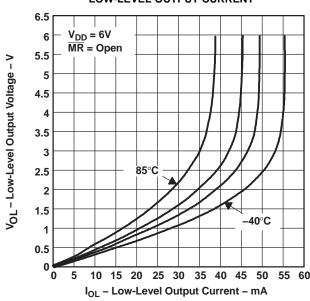

# LOW-LEVEL OUTPUT VOLTAGE VS LOW-LEVEL OUTPUT CURRENT

Figure 9.

www.ti.com

8-Sep-2023

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| TPS3307-18D      | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30718                   | Samples |

| TPS3307-18DG4    | LIFEBUY    | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30718                   |         |

| TPS3307-18DGN    | ACTIVE     | HVSSOP       | DGN                | 8    | 80             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAP                     | Samples |

| TPS3307-18DGNG4  | LIFEBUY    | HVSSOP       | DGN                | 8    | 80             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAP                     |         |

| TPS3307-18DGNR   | ACTIVE     | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAP                     | Samples |

| TPS3307-18DGNRG4 | LIFEBUY    | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAP                     |         |

| TPS3307-18DR     | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30718                   | Samples |

| TPS3307-18DRG4   | LIFEBUY    | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30718                   |         |

| TPS3307-25D      | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30725                   | Samples |

| TPS3307-25DG4    | LIFEBUY    | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30725                   |         |

| TPS3307-25DGN    | ACTIVE     | HVSSOP       | DGN                | 8    | 80             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAQ                     | Samples |

| TPS3307-25DGNG4  | LIFEBUY    | HVSSOP       | DGN                | 8    | 80             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAQ                     |         |

| TPS3307-25DGNR   | ACTIVE     | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAQ                     | Samples |

| TPS3307-25DR     | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30725                   | Samples |

| TPS3307-25DRG4   | LIFEBUY    | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30725                   |         |

| TPS3307-33D      | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30733                   | Samples |

| TPS3307-33DG4    | LIFEBUY    | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30733                   |         |

| TPS3307-33DGN    | ACTIVE     | HVSSOP       | DGN                | 8    | 80             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAR                     | Samples |

| TPS3307-33DGNR   | ACTIVE     | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAR                     | Samples |

| TPS3307-33DGNRG4 | LIFEBUY    | HVSSOP       | DGN                | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AAR                     |         |

| TPS3307-33DR     | ACTIVE     | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30733                   | Samples |

| TPS3307-33DRG4   | LIFEBUY    | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 30733                   |         |

<sup>(1)</sup> The marketing status values are defined as follows:

#### PACKAGE OPTION ADDENDUM

www.ti.com 8-Sep-2023

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS3307:

Enhanced Product: TPS3307-EP

NOTE: Qualified Version Definitions:

• Enhanced Product - Supports Defense, Aerospace and Medical Applications

**PACKAGE MATERIALS INFORMATION**

www.ti.com 5-Jan-2022

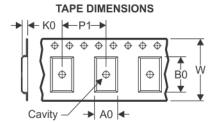

#### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

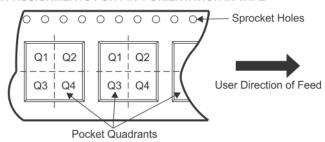

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS3307-18DGNR | HVSSOP          | DGN                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS3307-18DR   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS3307-25DGNR | HVSSOP          | DGN                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS3307-25DR   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TPS3307-33DGNR | HVSSOP          | DGN                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPS3307-33DR   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

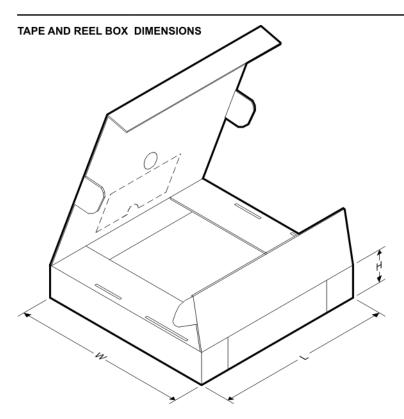

www.ti.com 5-Jan-2022

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS3307-18DGNR | HVSSOP       | DGN             | 8    | 2500 | 358.0       | 335.0      | 35.0        |

| TPS3307-18DR   | SOIC         | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS3307-25DGNR | HVSSOP       | DGN             | 8    | 2500 | 358.0       | 335.0      | 35.0        |

| TPS3307-25DR   | SOIC         | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

| TPS3307-33DGNR | HVSSOP       | DGN             | 8    | 2500 | 358.0       | 335.0      | 35.0        |

| TPS3307-33DR   | SOIC         | D               | 8    | 2500 | 350.0       | 350.0      | 43.0        |

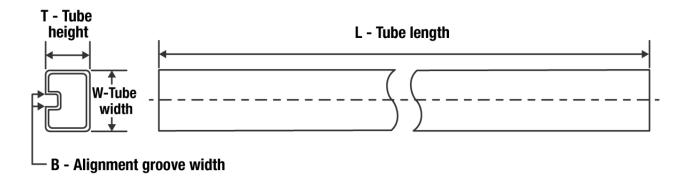

## PACKAGE MATERIALS INFORMATION

www.ti.com 5-Jan-2022

#### **TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPS3307-18D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS3307-18DG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS3307-25D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS3307-25DG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS3307-33D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| TPS3307-33DG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

3 x 3, 0.65 mm pitch

SMALL OUTLINE PACKAGE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

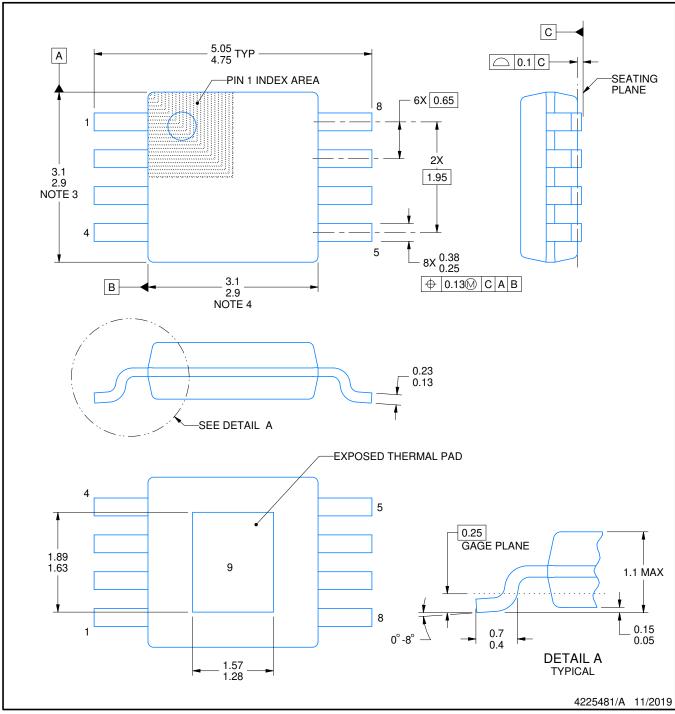

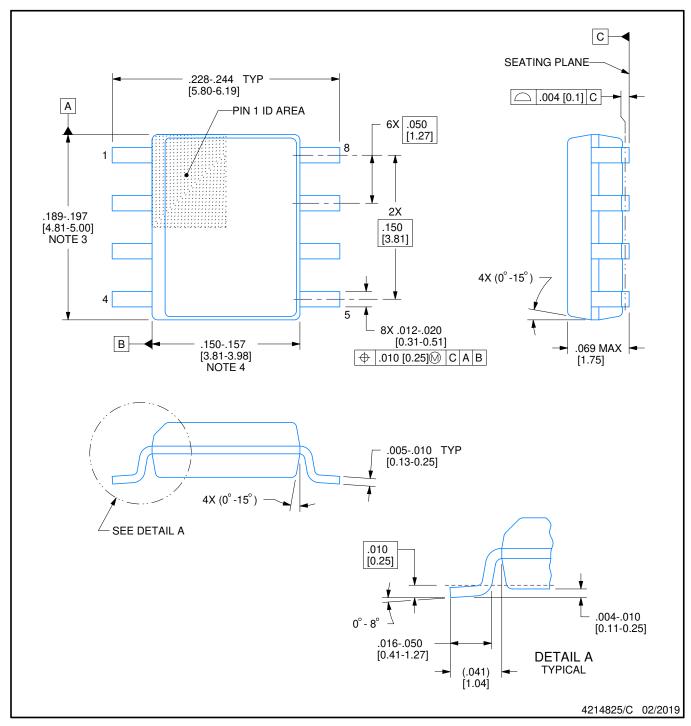

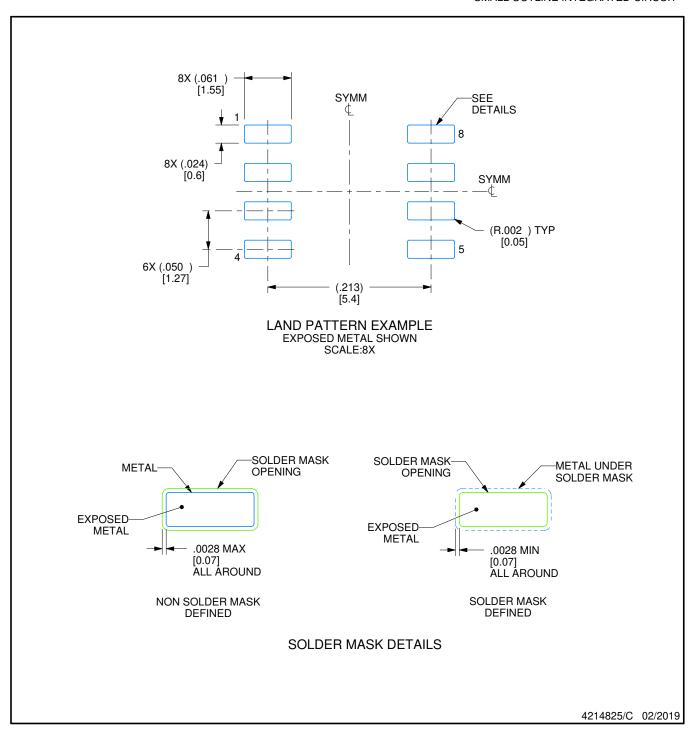

## PowerPAD<sup>™</sup> VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

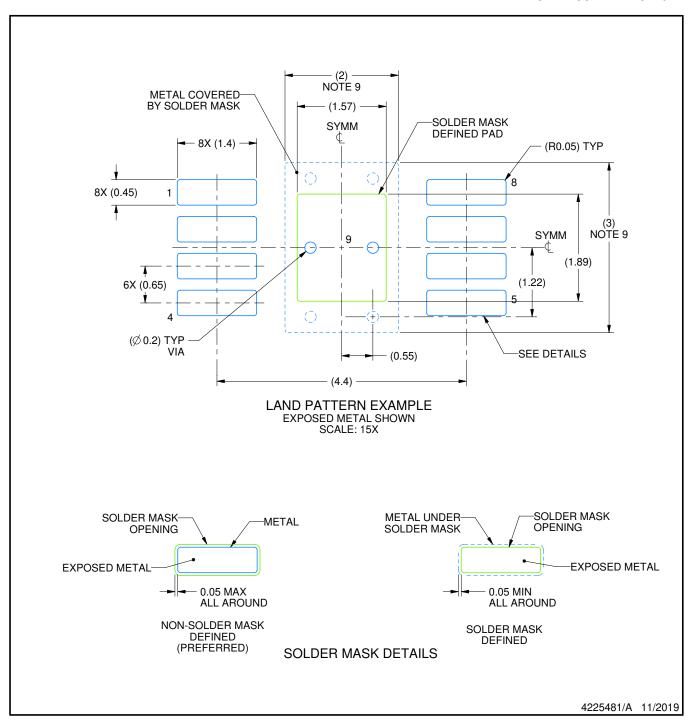

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

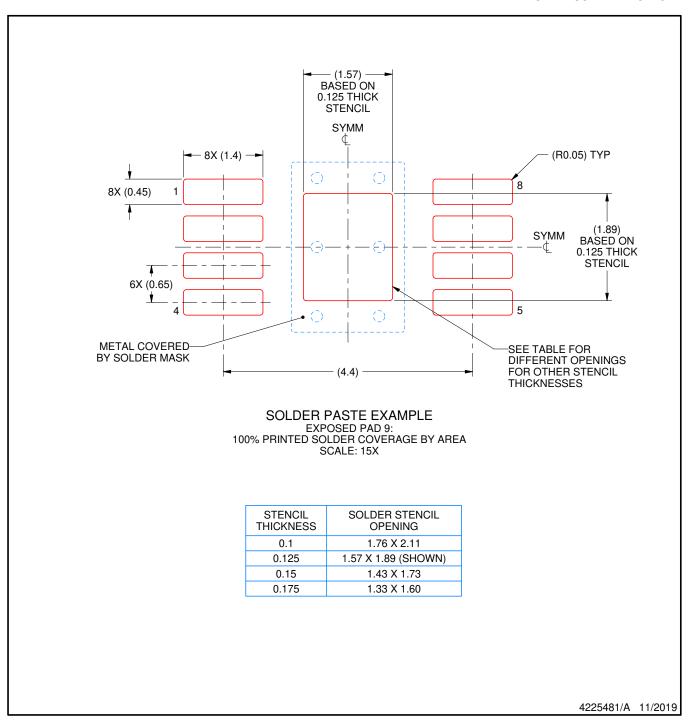

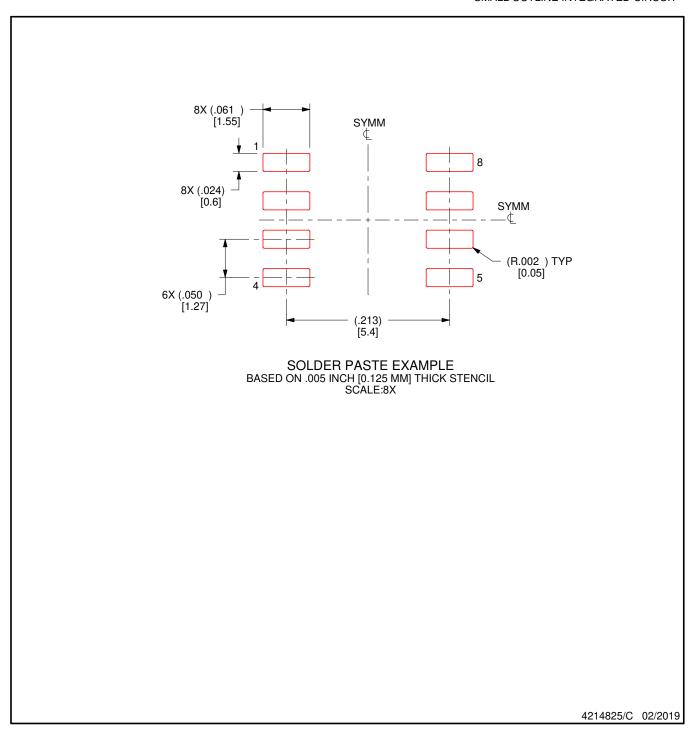

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 10. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 11. Board assembly site may have different recommendations for stencil design.

## **PACKAGE OUTLINE**

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.5. Reference JEDEC registration MS-012, variation AA.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated