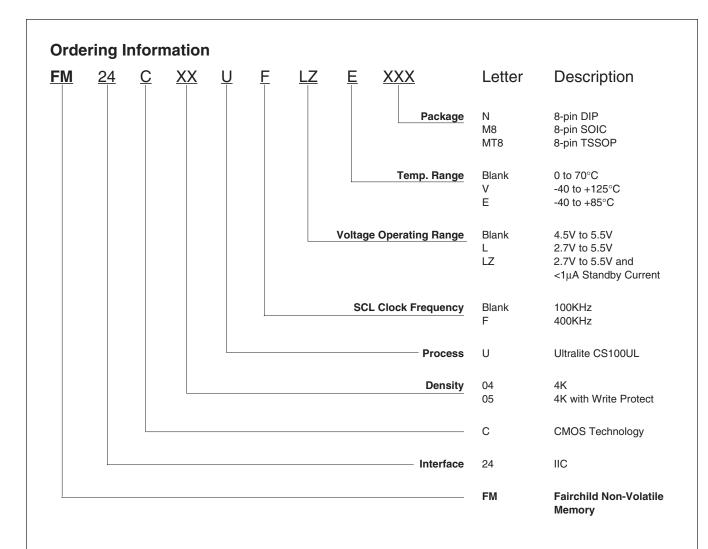

# FM24C04U/05U – 4K-Bit Standard 2-Wire Bus Interface Serial EEPROM

### **General Description**

The FM24C04U/05U devices are 4096 bits of CMOS non-volatile electrically erasable memory. These devices conform to all specifications in the Standard IIC 2-wire protocol. They are designed to minimize device pin count and simplify PC board layout requirements.

The upper half (upper 2Kbit) of the memory of the FM24C05U can be write protected by connecting the WP pin to  $V_{\rm CC}$ . This section of memory then becomes unalterable unless WP is switched to  $V_{\rm SS}$ .

This communications protocol uses CLOCK (SCL) and DATA I/O (SDA) lines to synchronously clock data between the master (for example a microprocessor) and the slave EEPROM device(s). The Standard IIC protocol allows for a maximum of 16K of EEPROM memory which is supported by the Fairchild family in 2K, 4K, 8K, and 16K devices, allowing the user to configure the memory as the application requires with any combination of EEPROMs. In order to implement higher EEPROM memory densities on the IIC bus, the Extended IIC protocol must be used. (Refer to the FM24C32 or FM24C65 datasheets for more information.)

Fairchild EEPROMs are designed and tested for applications requiring high endurance, high reliability and low power consumption.

### **Features**

- Extended operating voltage 2.7V 5.5V

- 400 KHz clock frequency (F) at 2.7V 5.5V

- 200μA active current typical

10μA standby current typical

1μA standby current typical (L)

- 0.1μA standby current typical (LZ)

- IIC compatible interface

- Provides bi-directional data transfer protocol

- Sixteen byte page write mode

- Minimizes total write time per byte

- Self timed write cycle

Typical write cycle time of 6ms

- Hardware Write Protect for upper half (FM24C05U only)

- Endurance: 1,000,000 data changes

- Data retention greater than 40 years

- Packages available: 8-pin DIP, 8-pin SO, and 8-pin TSSOP

- Available in three temperature ranges

- Commercial: 0° to +70°C

- Extended (E): -40° to +85C

- Automotive (V): -40° to +125°C

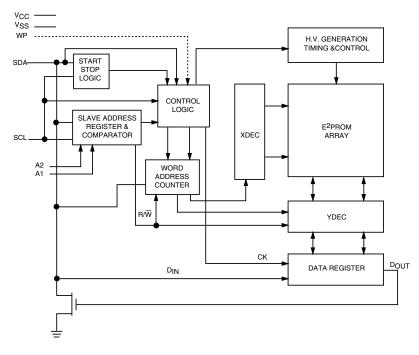

# **Block Diagram**

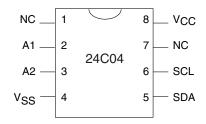

### **Connection Diagrams**

### Dual-in-Line Package (N), SO Package (M8) and TSSOP Package (MT8)

See Package Number N08E, M08A and MTC08

### **Pin Names**

| A1,A2           | Device Address Inputs |

|-----------------|-----------------------|

| V <sub>SS</sub> | Ground                |

| SDA             | Serial Data I/O       |

| SCL             | Serial Clock Input    |

| NC              | No Connection         |

| V <sub>CC</sub> | Power Supply          |

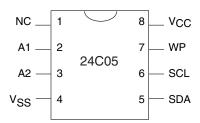

### Dual-in-Line Package (N), SO Package (M8) and TSSOP Package (MT8)

See Package Number N08E, M08A and MTC08

### **Pin Names**

| A1,A2           | Device Address Inputs |

|-----------------|-----------------------|

| V <sub>SS</sub> | Ground                |

| SDA             | Serial Data I/O       |

| SCL             | Serial Clock input    |

| WP              | Write Protect         |

| V <sub>CC</sub> | Power Supply          |

| NC              | No Connection         |

# **Product Specifications**

### **Absolute Maximum Ratings**

Ambient Storage Temperature -65°C to +150°C

All Input or Output Voltages

with Respect to Ground

Lead Temperature

(Soldering, 10 seconds)

ESD Rating

Ambient Operating

-0.3V to 6.5V

+300°C

2000V min.

Ambient Operating Temperature

**Operating Conditions**

FM24C04U/05U FM24C04UE/05UE FM24C04UV/05UV

-40°C to +85°C -40°C to +125°C

$0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$

Positive Power Supply

FM24C04U/05U FM24C04UL/05UL

FM24C04ULZ/05ULZ

4.5V to 5.5V 2.7V to 5.5V 2.7V to 5.5V

# DC Electrical Characteristics (2.7V to 5.5V)

| Symbol           | Symbol Parameter            |                                                          | t Conditions                                              |                       | Limits          |                       | Units |

|------------------|-----------------------------|----------------------------------------------------------|-----------------------------------------------------------|-----------------------|-----------------|-----------------------|-------|

|                  |                             |                                                          |                                                           | Min                   | Typ<br>(Note 1) | Max                   |       |

| I <sub>CCA</sub> | Active Power Supply Current | $f_{SCL}$ = 400 KHz ("F" version)<br>$f_{SCL}$ = 100 KHz |                                                           |                       | 0.2             | 1.0                   | mA    |

| I <sub>SB</sub>  | Standby Current             | V <sub>IN</sub> = GND                                    | V <sub>CC</sub> = 2.7V - 5.5V                             |                       | 10              | 50                    | μΑ    |

| (Note 3)         |                             | or V <sub>CC</sub>                                       | $V_{CC} = 2.7V - 5.5V (L)$<br>$V_{CC} = 2.7V - 4.5V (LZ)$ |                       | 1               | 10                    | μA    |

|                  |                             |                                                          | $V_{CC} = 2.7V - 4.5V (LZ)$                               |                       | 0.1             | 1                     | μΑ    |

| ILI              | Input Leakage Current       | V <sub>IN</sub> = GND                                    | A <sub>1</sub> , A <sub>2</sub> , WP                      |                       | 0.1             | 1                     | μΑ    |

|                  |                             | to V <sub>CC</sub>                                       | SCL                                                       |                       | 0.5             | 2                     | μΑ    |

| I <sub>LO</sub>  | Output Leakage Current      | V <sub>OUT</sub> = GNI                                   | $V_{OUT} = GND$ to $V_{CC}$                               |                       | 0.1             | 1                     | μА    |

| V <sub>IL</sub>  | Input Low Voltage           |                                                          |                                                           | -0.3                  |                 | V <sub>CC</sub> x 0.3 | V     |

| V <sub>IH</sub>  | Input High Voltage          |                                                          |                                                           | V <sub>CC</sub> x 0.7 |                 | V <sub>CC</sub> + 0.5 | V     |

| V <sub>OL</sub>  | Output Low Voltage          | $I_{OL} = 3 \text{ mA}$                                  |                                                           |                       |                 | 0.4                   | V     |

# Capacitance $T_A = +25$ °C, f = 100/400 KHz, $V_{CC} = 5V$ (Note 2)

| Symbol           | Test                                | Conditions     | Max | Units |

|------------------|-------------------------------------|----------------|-----|-------|

| C <sub>I/O</sub> | Input/Output Capacitance (SDA)      | $V_{I/O} = 0V$ | 8   | pF    |

| C <sub>IN</sub>  | Input Capacitance (A0, A1, A2, SCL) | $V_{IN} = 0V$  | 6   | pF    |

Note 1: Typical values are  $T_A = 25^{\circ}C$  and nominal supply voltage of 5V for 4.5V-5.5V operation and at 3V for 2.7V-4.5V operation.

Note 2: This parameter is periodically sampled and not 100% tested.

Note 3: The "L" and "LZ" versions can be operated in the 2.7V to 5.5V  $V_{CC}$  range. However, for a standby current (I<sub>SB</sub>) of  $1\mu$ A, the  $V_{CC}$  should be within 2.7V to 4.5V.

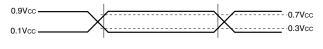

### **AC Test Conditions**

| Input Pulse Levels           | V <sub>CC</sub> x 0.1 to V <sub>CC</sub> x 0.9 |

|------------------------------|------------------------------------------------|

| Input Rise and Fall Times    | 10 ns                                          |

| Input & Output Timing Levels | V <sub>CC</sub> x 0.3 to V <sub>CC</sub> x 0.7 |

| Output Load                  | 1 TTL Gate and C <sub>L</sub> = 100 pF         |

### **AC Testing Input/Output Waveforms**

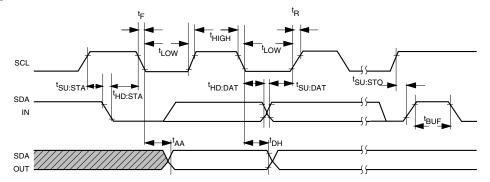

# Read and Write Cycle Limits (Standard and Low $V_{\text{CC}}$ Range 2.7V - 5.5V)

| Symbol                                                                                                    | Parameter                                                                       | 100 | KHz      | 400 | Units    |     |  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|----------|-----|----------|-----|--|

|                                                                                                           |                                                                                 | Min | Max      | Min | Max      |     |  |

| f <sub>SCL</sub> SCL Clock Frequency                                                                      |                                                                                 |     | 100      |     | 400      | KHz |  |

| T <sub>I</sub>                                                                                            |                                                                                 |     | 100      |     | 50       | ns  |  |

| t <sub>AA</sub>                                                                                           | SCL Low to SDA Data Out Valid                                                   | 0.3 | 3.5      | 0.1 | 0.9      | μs  |  |

| t <sub>BUF</sub>                                                                                          | Time the Bus Must Be Free before a New Transmission Can Start                   | 4.7 |          | 1.3 |          | μs  |  |

| t <sub>HD:STA</sub>                                                                                       | Start Condition Hold Time                                                       | 4.0 |          | 0.6 |          | μs  |  |

| t <sub>LOW</sub>                                                                                          | t <sub>LOW</sub> Clock Low Period                                               |     |          | 1.5 |          | μs  |  |

| t <sub>HIGH</sub>                                                                                         | t <sub>HIGH</sub> Clock High Period                                             |     |          | 0.6 |          | μs  |  |

| t <sub>SU:STA</sub>                                                                                       | t <sub>SU:STA</sub> Start Condition Setup Time (for a Repeated Start Condition) |     |          | 0.6 |          | μs  |  |

| t <sub>HD:DAT</sub>                                                                                       | Data in Hold Time                                                               | 0   |          | 0   |          | ns  |  |

| t <sub>SU:DAT</sub>                                                                                       | Data in Setup Time                                                              | 250 |          | 100 |          | ns  |  |

| t <sub>R</sub>                                                                                            | SDA and SCL Rise Time                                                           |     | 1        |     | 0.3      | μs  |  |

| t <sub>F</sub>                                                                                            | SDA and SCL Fall Time                                                           |     | 300      |     | 300      | ns  |  |

| t <sub>SU:STO</sub>                                                                                       | Stop Condition Setup Time                                                       | 4.7 |          | 0.6 |          | μs  |  |

| t <sub>DH</sub>                                                                                           | Data Out Hold Time                                                              | 300 |          | 50  |          | ns  |  |

| t <sub>WR</sub> Write Cycle Time<br>(Note 4) 4.5V to 5.5V V <sub>CC</sub><br>2.7V to 4.5V V <sub>CC</sub> |                                                                                 |     | 10<br>15 |     | 10<br>15 | ms  |  |

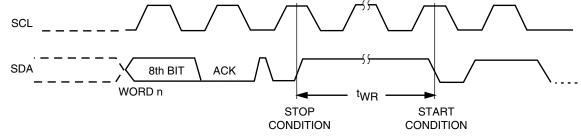

**Note 4**: The write cycle time (t<sub>WR</sub>) is the time from a valid stop condition of a write sequence to the end of the internal erase/program cycle. During the write cycle, the FM24C04U/05U bus interface circuits are disabled, SDA is allowed to remain high per the bus-level pull-up resistor, and the device does not respond to its slave address. Refer "Write Cycle Timing" diagram.

### **Bus Timing**

### **Write Cycle Timing**

Note: The write cycle time (t<sub>WR</sub>) is the time from a valid stop condition of a write sequence to the end of the internal erase/program cycle.

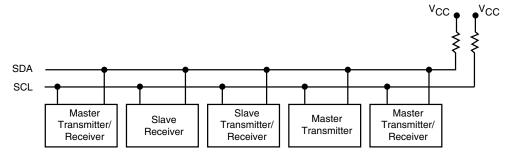

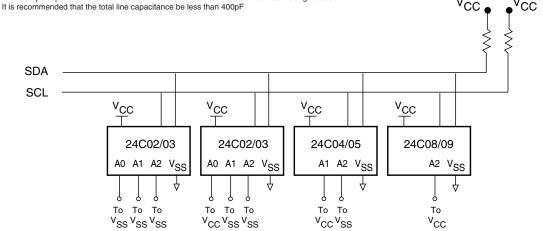

### **Typical System Configuration**

$\textbf{Note:} \qquad \text{Due to open drain configuration of SDA and SCL, a bus-level pull-up resistor is called for, (typical value = <math>4.7 \text{k}\Omega$ )}

### **Example of 16K of Memory on 2-Wire Bus**

Note: The SDA pull-up resistor is required due to the open-drain/open collector output of IIC bus devices. The SCL pull-up resistor is recommended because of the normal SCL line inactive 'high' state.

| Device       | Ac  | dress Pins Prese | Memory Size | # of Page   |        |

|--------------|-----|------------------|-------------|-------------|--------|

|              | A0  | A1               | A2          |             | Blocks |

| FM24C02U/03U | Yes | Yes              | Yes         | 2048 Bits   | 1      |

| FM24C04U/05U | No  | Yes              | Yes         | 4096 Bits   | 2      |

| FM24C08U/09U | No  | No               | Yes         | 8192 Bits   | 4      |

| FM24C16U/17U | No  | No               | No          | 16,384 Bits | 8      |

### **Background Information (IIC Bus)**

IIC bus allows synchronous bi-directional communication between a TRANSMITTER and a RECEIVER using a Clock signal (SCL) and a Data signal (SDA). Additionally there are up to three Address signals (A2, A1 and A0) which collectively serve as "chip select signal" to a device (example EEPROM) on the IIC bus.

All communication on the IIC bus must be started with a valid START condition (by a MASTER), followed by transmittal (by the MASTER) of byte(s) of information (Address/Data). For every byte of information received, the addressed RECEIVER provides a valid ACKNOWLEDGE pulse to further continue the communication unless the RECEIVER intends to discontinue the communication. Depending on the direction of transfer (Write or Read), the RECEIVER can be a SLAVE or the MASTER. A typical IIC communication concludes with a STOP condition (by the MASTER).

Addressing an EEPROM memory location involves sending a command string with the following information:

[DEVICE TYPE]—[DEVICE/PAGE BLOCK SELECTION]—[R/W BIT]—{acknowledge pulse}—[ARRAY ADDRESS]

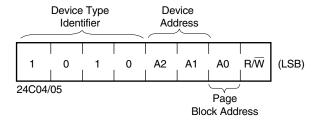

### **Slave Address**

Slave Address is an 8-bit information consisting of a Device type field (4bits), Device/Page block selection field (3bits) and Read/Write bit (1bit).

### **Slave Address Format**

| Device Type<br>Identifier |   |       |   | Device/Page Block<br>Selection |    |    |     |       |

|---------------------------|---|-------|---|--------------------------------|----|----|-----|-------|

| 1                         | 0 | 1<br> | 0 | A2                             | A1 | A0 | R/W | (LSB) |

### **Device Type**

IIC bus is designed to support a variety of devices such as RAMs, EPROMs etc., along with EEPROMS. Hence to properly identify various devices on the IIC bus, a 4-bit "Device Type" identifier string is used. For EEPROMS, this 4-bit string is 1-0-1-0. Every IIC device on the bus internally compares this 4-bit string to its own "Device Type" string to ensure proper device selection.

### **Device/Page Block Selection**

When multiple devices of the same type (e.g. multiple EEPROMS) are present on the IIC bus, then the A2, A1 and A0 address information bits are also used as part of the Slave Address. Every IIC device on the bus internally compares this 3-bit string to its own physical configuration (A2, A1 and A0 pins) to ensure proper device selection. This comparison is in addition to the "Device Type" comparison. In addition to selecting an EEPROM, these 3 bits are also used to select a "page block" within the selected EEPROM. Each page block is 2Kbit (256Bytes) in size. Depending on the density, an EEPROM can contain from a minimum of 1 to a maximum of 8 page blocks (in multiples of 2) and selection of a page block within a device is by using A2, A1 and A0 bits.

### Read/Write Bit

Last bit of the Slave Address indicates if the intended access is Read or Write. If the bit is "1," then the access is Read, whereas if the bit is "0," then the access is Write.

### **Acknowledge**

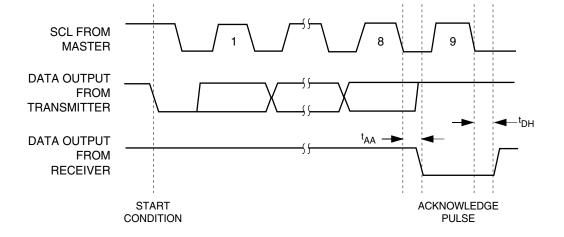

Acknowledge is an active LOW pulse on the SDA line driven by an addressed receiver to the addressing transmitter to indicate receipt of 8-bits of data. The receiver provides an ACK pulse for every 8-bits of data received. This handshake mechanism is done as follows: After transmitting 8-bits of data, the transmitter releases the SDA line and waits for the ACK pulse. The addressed receiver, if present, drives the ACK pulse on the SDA line during the 9th clock and releases the SDA line back (to the transmitter). Refer *Figure 3*.

### **Array Address**

Array address is an 8-bit information containing the address of a memory location to be selected within a page block of the device.

### 16K bit Addressing Limitation:

Standard IIC specification limits the maximum size of EEPROM memory on the bus to 16K bits. This limitation is due to the addressing protocol implemented which consists of the 8-bit Slave Address and an additional 8-bit field called Array Address. This Array Address selects 1 out of 256 locations (28=256). Since the data format of IIC specification is 8-bit wide, a total of 256 x 8 = 2048 = 2K bits now becomes addressable by this 8-bit Array Address. These 2K bits are typically referred as a "Page Block". Combining this 8-bit Array Address with the 3-bit Device/Page address (part of Slave Address) allows a maximum of 8 pages (2<sup>3</sup>=8) of memory that can be addressed. Since each page is 2K bits in size, 8 x 2K bits = 16K bits is the maximum size of memory that is addressable on the Standard IIC bus. This 16Kb of memory can be in the form of a single 16Kb EEPROM device or multiple EEPROMs of varying density (in 2Kb multiples) to a maximum total of 16Kb. To address the needs of systems that require more than 16Kb on the IIC bus, a different specification called "Extended IIC Specification" is used.

| DEFINITIONS                                                                                                                                       |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 8 bits (byte) of data                                                                                                                             |  |  |  |  |  |  |  |

| 16 sequential byte locations<br>starting at a 16-byte address<br>boundary, that may be pro-<br>grammed during a "page write"<br>programming cycle |  |  |  |  |  |  |  |

| 2048 (2K) bits organized into 16 pages of addressable memory. (8 bits) x (16 bytes) x (16 pages) = 2048 bits                                      |  |  |  |  |  |  |  |

| Any IIC device CONTROLLING the transfer of data (such as a microprocessor)                                                                        |  |  |  |  |  |  |  |

| Device being controlled<br>(EEPROMs are always considered<br>Slaves)                                                                              |  |  |  |  |  |  |  |

| Device currently SENDING data on the bus (may be either a Master or Slave).                                                                       |  |  |  |  |  |  |  |

| Device currently RECEIVING data on the bus (Master or Slave)                                                                                      |  |  |  |  |  |  |  |

|                                                                                                                                                   |  |  |  |  |  |  |  |

7

### **Pin Descriptions**

### Serial Clock (SCL)

The SCL input is used to clock all data into and out of the device.

### Serial Data (SDA)

SDA is a bi-directional pin used to transfer data into and out of the device. It is an open drain output and may be wire—ORed with any number of open drain or open collector outputs.

### Write Protect (WP) (FM24C05U Only)

If tied to  $V_{CC}$ , PROGRAM operations onto the upper half (upper 2Kbits) of the memory will not be executed. READ operations are possible. If tied to  $V_{SS}$ , normal operation is enabled, READ/WRITE over the entire memory is possible.

This feature allows the user to assign the upper half of the memory as ROM which can be protected against accidental programming. When write is disabled, slave address and word address will be acknowledged but data will not be acknowledged.

This pin has an internal pull-down circuit. However, on systems where write protection is not required it is recommended that this pin is tied to  $V_{\rm SS}$ .

# Device Selection Inputs A2, A1 and A0 (as appropriate)

These inputs collectively serve as "chip select" signal to an EEPROM when multiple EEPROMs are present on the same IIC bus. Hence these inputs, if present, should be connected to  $V_{\rm CC}$  or  $V_{\rm SS}$  in a unique manner to allow proper selection of an EEPROM amongst multiple EEPROMs. During a typical addressing sequence, every EEPROM on the IIC bus compares the configuration of these inputs to the respective 3 bit "Device/Page block selection" information (part of slave address) to determine a valid selection. For e.g. if the 3 bit "Device/Page block selection" is 1-0-1, then the EEPROM whose "Device Selection inputs" (A2, A1 and A0) are connected to  $V_{\rm CC}\textsc{-}V_{\rm SS}\textsc{-}V_{\rm CC}$  respectively, is selected.

Depending on the density, only appropriate numbers of "Device Selection inputs" are provided on an EEPROM. For every "Device selection input" that is not present on the device, the corresponding bit in the "Device/Page block selection" field is used to select a "Page Block" within the device instead of the device itself. Following table illustrates the above:

### **Device Operation**

The FM24C04U/05U supports a bi-directional bus oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter and the receiving device as the receiver. The device controlling the transfer is the master and the device that is controlled is the slave. The master will always initiate data transfers and provide the clock for both transmit and receive operations. Therefore, the FM24C04U/05U will be considered a slave in all applications.

### **Clock and Data Conventions**

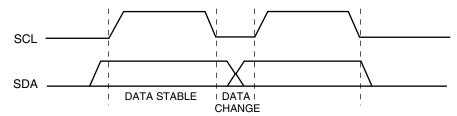

Data states on the SDA line can change only during SCL LOW. SDA state changes during SCL HIGH are reserved for indicating start and stop conditions. Refer to *Figure 1* and *Figure 2* on next page.

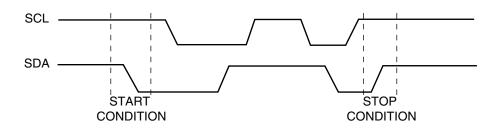

#### **Start Condition**

All commands are preceded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH. The FM24C04U/05U continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met.

### **Stop Condition**

All communications are terminated by a stop condition, which is a LOW to HIGH transition of SDA when SCL is HIGH. The stop condition is also used by the FM24C04U/05U to place the device in the standby power mode, except when a Write operation is being executed, in which case a second stop condition is required after  $t_{\rm WB}$  period, to place the device in standby mode.

| EEPROM Density | Number of Page Blocks | Device Selection Inputs Provided |    |    | Address Bits<br>Selecting Page Block |

|----------------|-----------------------|----------------------------------|----|----|--------------------------------------|

| 2k bit         | 1                     | A0                               | A1 | A2 | None                                 |

| 4k bit         | 2                     | _                                | A1 | A2 | A0                                   |

| 8k bit         | 4                     | _                                | _  | A2 | A0 and A1                            |

| 16k bit        | 8                     | _                                | _  | _  | A0, A1 and A2                        |

Note that even when just one EEPROM present on the IIC bus, these pins should be tied to  $\rm V_{\rm CC}$  or  $\rm V_{\rm SS}$  to ensure proper termination.

### Data Validity (Figure 1)

### **Start and Stop Definition (Figure 2)**

### **Acknowledge Response from Receiver (Figure 3)**

### **Acknowledge**

The FM24C04U/05U device will always respond with an acknowledge after recognition of a start condition and its slave address. If both the device and a write operation have been selected, the FM24C04U/05U will respond with an acknowledge after the receipt of each subsequent eight bit byte.

In the read mode the FM24C04U/05U slave will transmit eight bits of data, release the SDA line and monitor the line for an acknowledge. If an acknowledge is detected, FM24C04U/05U will continue to transmit data. If an acknowledge is not detected, FM24C04U/05U will terminate further data transmissions and await the stop condition to return to the standby power mode.

### **Device Addressing**

Following a start condition the master must output the address of the slave it is accessing. The most significant four bits of the slave address are those of the device type identifier. This is fixed as 1010 for all EEPROM devices.

Refer the following table for Slave Addresses string details:

| Device       | A0 | <b>A</b> 1 | A2 |   | Page Block<br>Addresses |

|--------------|----|------------|----|---|-------------------------|

| FM24C04U/05U | Р  | Α          | Α  | 2 | 0, 1                    |

- A: Refers to a hardware configured Device Address pin.

- P: Refers to an internal PAGE BLOCK.

All IIC EEPROMs use an internal protocol that defines a PAGE BLOCK size of 2K bits (for Word addresses 0x00 through 0xFF). Therefore, address bits A0, A1, or A2 (if designated 'P') are used to access a PAGE BLOCK in conjunction with the Word address used to access any individual data byte.

The last bit of the slave address defines whether a write or read condition is requested by the master. A '1' indicates that a read operation is to be executed, and a '0' initiates the write mode.

A simple review: After the FM24C04U/05U recognizes the start condition, the devices interfaced to the IIC bus wait for a slave address to be transmitted over the SDA line. If the transmitted slave address matches an address of one of the devices, the designated slave pulls the SDA line LOW with an acknowledge signal and awaits further transmissions.

### **Write Operations**

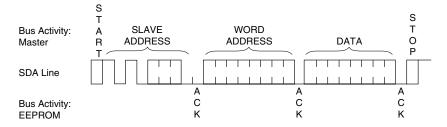

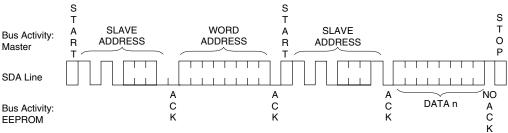

### **BYTE WRITE**

For a write operation, a second address field is required which is a word address that is comprised of eight bits and provides access to any one of the 256 bytes in the selected page of memory. Upon receipt of the byte address, the FM24C04U/05U responds with an acknowledge and waits for the next eight bits of data, again, responding with an acknowledge. The master then terminates the transfer by generating a stop condition at which time the FM24C04U/05U begins the internal write cycle to the nonvolatile memory. While the internal write cycle is in progress, the FM24C04U/05U inputs are disabled, and the device will not respond to any requests from the master for the duration of  $t_{\rm WR}$ . Refer to Figure 4 for the address, acknowledge, and data transfer sequence.

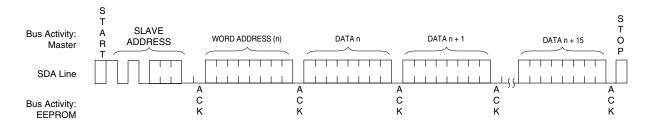

### **PAGE WRITE**

To minimize write cycle time, FM24C04U/05U offer Page Write feature, by which, up to a maximum of 16 contiguous byte locations can be programmed all at once (instead of 16 individual byte writes). To facilitate this feature, the memory array is organized in terms of "Pages." A Page consists of 16 contiguous byte locations starting at every 16-Byte address boundary (for example, starting at array address 0x00, 0x10, 0x20 etc.). Page Write operation limits access to byte locations within a page. In other words a single Page Write operation will not cross over to locations on another page but will "roll over" to the beginning of the page whenever end of Page is reached and additional locations are continued to be accessed. A Page Write operation can be initiated to begin at any location within a page (starting address of the Page Write operation need not be the starting address of a Page).

Page Write is initiated in the same manner as the Byte Write operation; but instead of terminating the cycle after transmitting the first data byte, the master can further transmit up to 15 more bytes. After the receipt of each byte, FM24C04U/05U will respond with an acknowledge pulse, increment the internal address counter to the next address, and is ready to accept the next data. If the master should transmit more than sixteen bytes prior to generating the STOP condition, the address counter will "roll over" and previously written data will be overwritten. As with the Byte Write operation, all inputs are disabled until completion of the internal write cycle. Refer to Figure 5 for the address, acknowledge, and data transfer sequence.

### **Acknowledge Polling**

Once the stop condition is issued to indicate the end of the host's write operation, the FM24C04U/05U initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the slave address for a write operation. If the FM24C04U/05U is still busy with the write operation no ACK will be returned. If the FM24C04U/05U has completed the write operation, an ACK will be returned and the host can then proceed with the next read or write operation.

### Write Protection (FM24C05U Only)

Programming of the upper half (upper 2Kbit) of the memory will not take place if the WP pin of the FM24C05U is connected to  $V_{CC}.$  The FM24C05U will respond to slave and byte addresses; but if the memory accessed is write protected by the WP pin, the FM24C05U will not generate an acknowledge after the first byte of data has been received. Thus, the program cycle will not be started when the stop condition is asserted.

### **Byte Write (Figure 4)**

### Page Write (Figure 5)

11

www.fairchildsemi.com

### **Read Operations**

Read operations are initiated in the same manner as write operations, with the exception that the  $R/\overline{W}$  bit of the slave address is set to a one. There are three basic read operations: current address read, random read, and sequential read.

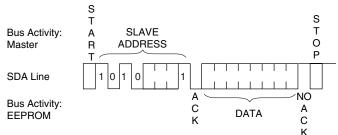

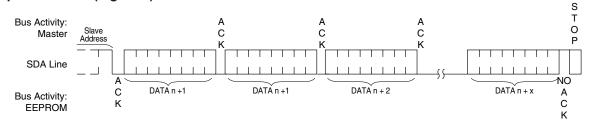

#### **Current Address Read**

Internally the FM24C04U/05U contains an address counter that maintains the address of the last byte accessed, incremented by one. Therefore, if the last access (either a read or write) was to address n, the next read operation would access data from address n + 1. Upon receipt of the slave address with R/W set to one, the FM24C04U/05U issues an acknowledge and transmits the eight bit word. The master will not acknowledge the transfer but does generate a stop condition, and therefore the FM24C04U/05U discontinues transmission. Refer to Figure 6 for the sequence of address, acknowledge and data transfer.

### **Random Read**

Random read operations allow the master to access any memory location in a random manner. Prior to issuing the slave address with the  $R/\overline{W}$  bit set to one, the master must first perform a "dummy" write operation. The master issues the start condition, slave address with the  $R/\overline{W}$  bit set to zero and then the byte address is read. After the byte address acknowledge, the master

immediately issues another start condition and the slave address with the  $R \overline{\rm W}$  bit set to one. This will be followed by an acknowledge from the FM24C04U/05U and then by the eight bit word. The master will not acknowledge the transfer but does generate the stop condition, and therefore the FM24C04U/05U discontinues transmission. Refer to Figure 7 for the address, acknowledge, and data transfer sequence.

### **Sequential Read**

Sequential reads can be initiated as either a current address read or random access read. The first word is transmitted in the same manner as the other read modes; however, the master now responds with an acknowledge, indicating it requires additional data. The FM24C04U/05U continues to output data for each acknowledge received. The read operation is terminated by the master not responding with an acknowledge or by generating a stop condition.

The data output is sequential with the data from address n followed by the data from n+1. The address counter for read operations increments all word address bits, allowing the entire memory contents to be serially read during one operation. After the entire memory has been read, the counter "rolls over" to the beginning of the memory. FM24C04U/05U continues to output data for each acknowledge received. Refer to *Figure 8* for the address, acknowledge, and data transfer sequence.

### **Current Address Read (Figure 6)**

### Random Read (Figure 7)

### **Sequential Read (Figure 8)**

12

www.fairchildsemi.com

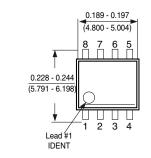

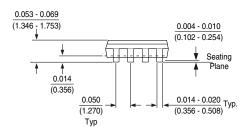

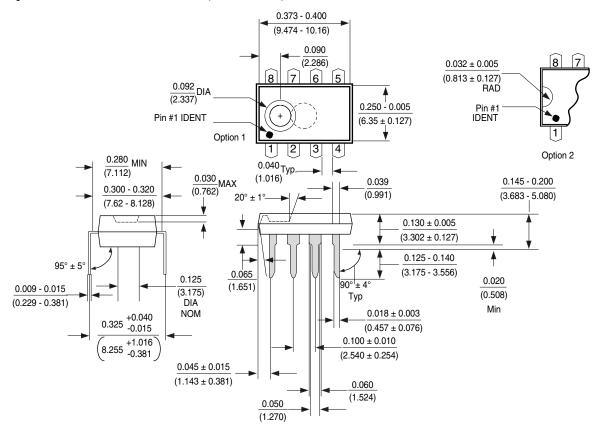

### Physical Dimensions inches (millimeters) unless otherwise noted

8-Pin Molded Small Outline Package (M8)

Package Number M08A

Land pattern recommendation

Notes: Unless otherwise specified

1. Reference JEDEC registration MO153. Variation AA. Dated 7/93

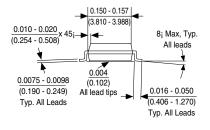

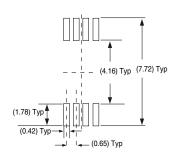

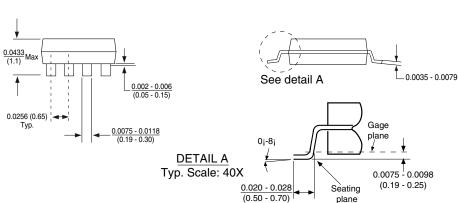

# 8-Pin Molded Thin Shrink Small Outline Package (MT8) Package Number MTC08

### Physical Dimensions inches (millimeters) unless otherwise noted

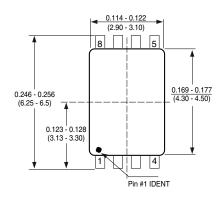

Molded Dual-In-Line Package (N) Package Number N08E

### Life Support Policy

Fairchild's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Fairchild Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which. (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Fairchild Semiconductor Deutsch +49 (0) 8141-6102-0 +44 (0) 1793-856856 +33 (0) 1-6930-3696 +39 (0) 2-249111-1 English Français Italiano

Fairchild Semiconductor Hong Kong 8/F, Room 808, Empire Centre 68 Mody Road, Tsimshatsui East

Kowloon. Hong Kong Tel; +852-2722-8338 Fax: +852-2722-8383

Fairchild Semiconductor

Fairchild Semiconductor Japan Ltd. 4F, Natsume Bldg. 2-18-6, Yushima, Bunkyo-ku Tokyo, 113-0034 Japan Tel: 81-3-3818-8840 Fax: 81-3-3818-8841

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.