# Quad-Output TFT LCD DC/DC Converters with Buffer

# **General Description**

The MAX1778/MAX1880—MAX1885 multiple-output DC-DC converters provide the regulated voltages required by active matrix thin-film transistor (TFT) liquid crystal displays (LCD) in a low-profile TSSOP package. One high-power step-up converter and two low-power charge pumps convert the 2.7V to 5.5V input voltage into three independent output voltages. A built-in linear regulator and VCOM buffer complete the power-supply requirements.

The main step-up converter accurately generates an externally set output voltage up to 13V that can supply the display's row/column drivers. The converter's high switching frequency and current-mode PWM architecture provide fast transient response and allow the use of small low-profile inductors and ceramic capacitors. The low-power BiCMOS control circuitry and internal 14V switch  $(0.35\Omega$  N-channel MOSFET) enable efficiencies up to 91%.

The dual low-power charge pumps (MAX1778/MAX1880/ MAX1881/MAX1882 only) independently regulate one positive output ( $V_{POS}$ ) and one negative output ( $V_{NEG}$ ). These low-power outputs use external diode and capacitor stages (as many stages as required) to regulate output voltages up to +40V and -40V. A unique control scheme minimizes output ripple as well as capacitor sizes for both charge pumps.

A resistor-programmable, 40mA, low-dropout linear regulator (MAX1778/MAX1881/MAX1883/MAX1884 only) provides preregulation or postregulation for any of the supplies. For higher current applications, an external transistor can be added. Additionally, the VCOM buffer provides a high current output that is ideal for driving the capacitive backplane of TFT LCD panels. The VCOM buffer's output voltage is preset with an internal 50% resistive-divider or can be externally adjusted for other voltages.

The MAX1778/MAX1880–MAX1885 are protected against output undervoltage and thermal overload conditions by a latched fault detection circuit that shuts down the device. All devices are available in the ultrathin TSSOP package (1.1mm max height).

### **Applications**

- TFT LCD Notebook Displays

- TFT LCD Desktop Monitor Panels

#### **Features**

- 500kHz/1MHz Current-Mode PWM Step-Up Regulator

- Up to +13V Main High-Power Output ±1% Accurate

- High Efficiency (91%)

- Dual Regulated Charge-Pump Outputs (MAX1778/ MAX1880–MAX1882 only)

- Up to +40V Positive Charge-Pump Output

- Up to -40V Negative Charge-Pump Output

- Low-Dropout 40mA Linear Regulator (MAX1778/ MAX1881/MAX1883/MAX1884 only)

- Up to +15V LDO Input

- Optional Higher Current with External Transistor

- 2.7V to 5.5V Input Supply

- Internal Supply Sequencing and Soft-Start

- Power-Ready Output

- Adjustable Fault-Detection Latch

- Thermal Protection (+160°C)

- 0.1µA Shutdown Current

- 0.7mA IN Quiescent Current

- Ultra-Small External Components

- Thin TSSOP Package (1.1mm max height)

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| MAX1778EUG  | -40°C to +85°C | 24 TSSOP    |

| MAX1778EUG+ | -40°C to +85°C | 24 TSSOP    |

| MAX1880EUG  | -40°C to +85°C | 24 TSSOP    |

| MAX1881EUG  | -40°C to +85°C | 24 TSSOP    |

| MAX1882EUG  | -40°C to +85°C | 24 TSSOP    |

| MAX1883EUP  | -40°C to +85°C | 20 TSSOP    |

| MAX1884EUP  | -40°C to +85°C | 20 TSSOP    |

| MAX1885EUP  | -40°C to +85°C | 20 TSSOP    |

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

Typical operating Circuit appears at end of data sheet. Pin Configurations and Selector Guide appear at end of data sheet.

# **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{IN} = +3.0V, \overline{SHDN} = IN, V_{SUPP} = V_{SUPN} = V_{SUPB} = V_{SUPL} = 10V, LDOOUT = FBL, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND, C_{REF} = 0.22\mu F, C_{BUF} = 1\mu F, T_A = 0^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                     | SYMBOL               |                                                                                    | CONDITIONS                                                         |     |     | MAX | UNITS |

|-------------------------------|----------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|-----|-------|

| Input Supply Range            | V <sub>IN</sub>      |                                                                                    |                                                                    |     |     | 5.5 | V     |

| Input Undervoltage Threshold  | V <sub>UVLO</sub>    | V <sub>IN</sub> rising, 40m                                                        | V hysteresis (typ)                                                 | 2.2 | 2.4 | 2.6 | V     |

|                               |                      | V <sub>FB</sub> = V <sub>FBP</sub> =                                               | MAX1778/MAX1880/<br>MAX1883 (f <sub>OSC</sub> = 1MHz)              |     | 0.7 | 1   |       |

| IN Quiescent Supply Current   | I <sub>IN</sub> 1.5V | 1.5V, V <sub>FBN</sub> = -0.2V                                                     | MAX1881/MAX1882/<br>MAX1884/MAX1885<br>(f <sub>OSC</sub> = 500kHz) |     | 0.6 | 1   | mA    |

| SUPP Quiescent Current Island | lauss                | V = 1 5V                                                                           | MAX1778/MAX1880<br>(f <sub>OSC</sub> = 1MHz)                       |     | 0.4 | 0.7 | mA    |

| SOFF Quiescent current        | I <sub>SUPP</sub>    | V <sub>FBP</sub> = 1.5V                                                            | MAX1881/MAX1882<br>(f <sub>OSC</sub> = 500kHz)                     |     | 0.3 | 0.5 | IIIA  |

| SUPN Quiescent Current        | 1                    | V <sub>FBN</sub> = -0.2V                                                           | MAX1778/MAX1880<br>(f <sub>OSC</sub> = 1MHz)                       |     | 0.4 | 0.7 | mA.   |

| SOFIN Quiescent Current       | ISUPN                | VFBN = -0.2V                                                                       | MAX1881/MAX1882<br>(f <sub>OSC</sub> = 500kHz)                     |     | 0.3 | 0.5 | IIIA  |

| IN Shutdown Current           |                      | V <sub>SHDN</sub> = 0, V <sub>IN</sub>                                             | = 5V                                                               |     | 0.1 | 10  | μA    |

| SUPP Shutdown Current         |                      | V <sub>SHDN</sub> = 0, V <sub>SI</sub><br>MAX1778/MAX                              | <sub>JPP</sub> = 13V,<br>1880/MAX1881/MAX1882                      |     | 0.1 | 10  | μA    |

| SUPN Shutdown Current         |                      | V <sub>SHDN</sub> = 0, V <sub>SUPN</sub> = 13V,<br>MAX1778/MAX1880/MAX1881/MAX1882 |                                                                    |     | 0.1 | 10  | μA    |

| SUPL Shutdown Current         |                      | V <sub>SHDN</sub> = 0, V <sub>SUPL</sub> = 13V<br>MAX1778/MAX1881/MAX1883/MAX1884  |                                                                    |     | 0.1 | 10  | μA    |

| SUPB Shutdown Current         |                      | $V_{\overline{SHDN}} = 0, V_{SU}$                                                  | <sub>JPB</sub> = 13V                                               |     | 6   | 13  | μA    |

# **Electrical Characteristics (continued)**

$(V_{IN} = +3.0V, \overline{SHDN} = IN, V_{SUPP} = V_{SUPN} = V_{SUPB} = V_{SUPL} = 10V, LDOOUT = FBL, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND, C_{REF} = 0.22\mu F, C_{BUF} = 1\mu F, T_{A} = 0^{\circ}C$  to +85°C. Typical values are at  $T_{A} = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                     | SYMBOL               | COI                                             | NDITIONS                                          | MIN             | TYP                     | MAX   | UNITS |

|-------------------------------|----------------------|-------------------------------------------------|---------------------------------------------------|-----------------|-------------------------|-------|-------|

| MAIN STEP-UP CONVERTER        |                      |                                                 |                                                   |                 |                         |       |       |

| Main Output Voltage Range     | V <sub>MAIN</sub>    |                                                 |                                                   | V <sub>IN</sub> |                         | 13    | V     |

| ED Decidetion Valteria        |                      | Integrator enabled,                             | C <sub>INTG</sub> = 1000pF                        | 1.234           | 1.247                   | 1.260 | .,    |

| FB Regulation Voltage         | V <sub>FB</sub>      | Integrator disabled                             | (INTG = REF)                                      | 1.220           |                         | 1.280 | V     |

| FB Input Bias Current         | I <sub>FB</sub>      | V <sub>FB</sub> = 1.25V, INTG                   | = GND                                             | -50             |                         | +50   | nA    |

| Operating Fraguency           | r                    | MAX1778/MAX188                                  | 0/MAX1883                                         | 0.85            | 1                       | 1.15  | MHz   |

| Operating Frequency           | fosc                 | MAX1881/MAX188                                  | 2/MAX1884/MAX1885                                 | 425             | 500                     | 575   | kHz   |

| Oscillator Maximum Duty Cycle |                      |                                                 |                                                   | 80              | 85                      | 91    | %     |

| Load Regulation               |                      | I <sub>LX</sub> = 0 to 200mA,                   | Integrator enabled,<br>C <sub>INTG</sub> = 1000pF |                 | 0.01                    |       | %     |

| Load Regulation               |                      | V <sub>MAIN</sub> = 10V                         | Integrator disabled (INTG = REF)                  |                 | 0.2                     |       | 70    |

| Line Regulation               |                      |                                                 |                                                   |                 | 0.1                     |       | %/V   |

| Integrator Transconductance   |                      |                                                 |                                                   |                 | 317                     |       | μS    |

| LX Switch On-Resistance       | R <sub>LX(ON)</sub>  | I <sub>LX</sub> = 100mA                         |                                                   |                 | 0.35                    | 0.7   | Ω     |

| LX Leakage Current            | I <sub>LX</sub>      | V <sub>LX</sub> = 13V                           |                                                   |                 | 0.01                    | 20    | μA    |

|                               |                      | Phase I = soft-start                            | (1024/f <sub>OSC</sub> )                          | 0.275           | 0.38                    | 0.5   |       |

| LX Current Limit              |                      | Phase II = soft-start (1024/f <sub>OSC</sub> )  |                                                   |                 | 0.75                    |       | _     |

| LA Guirent Limit              | I <sub>LIM</sub>     | Phase III = soft-start (1024/f <sub>OSC</sub> ) |                                                   |                 | 1.12                    |       | Α     |

|                               |                      | Phase IV = fully on                             | (after 3072/f <sub>OSC</sub> )                    | 1.15            | 1.5                     | 1.85  |       |

| Maximum RMS LX Current        |                      |                                                 |                                                   |                 | 1                       |       | Α     |

| Soft-Start Period             | t <sub>SS</sub>      | Power-up to the en                              | d of Phase III                                    | 3               | 072 / f <sub>OS</sub>   | С     | s     |

| FB Fault Trip Level           |                      | Falling edge, FLTS                              | ET = GND                                          | 1.07            | 1.1                     | 1.14  | V     |

| rb rault hip Level            |                      | Falling edge, FLTS                              | ET = 1V                                           | 0.955           | 0.99                    | 1.025 | \ \ \ |

| POSITIVE CHARGE PUMP (MA      | X1778/MAX18          | 80/MAX1881/MAX18                                | 382 only)                                         |                 |                         |       |       |

| SUPP Input Supply Range       | V <sub>SUPP</sub>    |                                                 |                                                   | 2.7             |                         | 13    | V     |

| Operating Frequency           | f <sub>CHP</sub>     |                                                 |                                                   | (               | 0.5 x f <sub>OS</sub> ( |       | Hz    |

| FBP Regulation Voltage        | V <sub>FBP</sub>     |                                                 |                                                   | 1.2             | 1.25                    | 1.3   | V     |

| FBP Input Bias Current        | I <sub>FBP</sub>     | V <sub>FBP</sub> = 1.5V                         |                                                   | -50             |                         | +50   | nA    |

| DRVP PCH On-Resistance        | R <sub>PCH(ON)</sub> |                                                 |                                                   |                 | 5                       | 10    | Ω     |

| DDVD NCH On Posistance        |                      | V <sub>FBP</sub> = 1.2V                         |                                                   |                 | 2                       | 4     | Ω     |

| DRVP NCH On-Resistance        | R <sub>NCH(ON)</sub> | V <sub>FBP</sub> = 1.3V                         |                                                   | 20              |                         |       | kΩ    |

| Maximum RMS DRVP Current      |                      |                                                 |                                                   |                 | 0.1                     |       | Α     |

| FBP Power-Ready Trip Level    |                      | Rising edge                                     |                                                   | 1.09            | 1.125                   | 1.16  | V     |

| EDD Foult Trip Lovel          |                      | Falling edge, FLTS                              | ET = GND                                          | 1.08            | 1.11                    | 1.16  | W     |

| FBP Fault Trip Level          | Level                |                                                 | Falling edge, FLTSET = 1V                         |                 |                         | 1.025 | V     |

# **Electrical Characteristics (continued)**

$(V_{IN} = +3.0V, \overline{SHDN} = IN, V_{SUPP} = V_{SUPN} = V_{SUPB} = V_{SUPL} = 10V, LDOOUT = FBL, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND, C_{REF} = 0.22\mu F, C_{BUF} = 1\mu F, T_{A} = 0^{\circ}C$  to +85°C. Typical values are at  $T_{A} = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                          | SYMBOL               | CONDITIONS                                                     |                                    | MIN   | TYP                     | MAX   | UNITS |

|------------------------------------|----------------------|----------------------------------------------------------------|------------------------------------|-------|-------------------------|-------|-------|

| NEGATIVE CHARGE PUMP (MA           | X1778/MAX1           | 880/MAX1881/MAX                                                | 1882 only)                         |       |                         |       |       |

| SUPN Input Supply Range            | V <sub>SUPN</sub>    |                                                                |                                    | 2.7   |                         | 13    | V     |

| Operating Frequency                | f <sub>CHP</sub>     |                                                                |                                    | C     | ).5 x f <sub>OS</sub> ( | <br>C | Hz    |

| FBN Regulation Voltage             | V <sub>FBN</sub>     |                                                                |                                    | -50   | 0                       | +50   | mV    |

| FBN Input Bias Current             | I <sub>FBN</sub>     | V <sub>FBN</sub> = 0                                           |                                    | -50   |                         | +50   | nA    |

| DRVN PCH On-Resistance             | R <sub>PCH(ON)</sub> |                                                                |                                    |       | 5                       | 10    | Ω     |

| DDV/N NCLL On Desigtance           | В                    | V <sub>FBN</sub> = +50mV                                       |                                    |       | 2                       | 4     | Ω     |

| DRVN NCH On-Resistance             | R <sub>NCH(ON)</sub> | V <sub>FBN</sub> = -50mV                                       |                                    | 20    |                         |       | kΩ    |

| Maximum RMS DRVN Current           |                      |                                                                |                                    |       | 0.1                     | -     | Α     |

| FBN Power-Ready Trip Level         |                      | Falling edge                                                   |                                    | 80    | 125                     | 165   | mV    |

| FBN Fault Trip Level               |                      | Rising edge                                                    |                                    | 80    | 140                     | 190   | mV    |

| LOW-DROPOUT LINEAR REGU            | LATOR (MAX           | 1778/MAX1881/MA                                                | X1883/MAX1884 only)                |       |                         |       |       |

| SUPL Input Supply Range            | V <sub>SUPL</sub>    |                                                                |                                    | 4.5   |                         | 15    | V     |

| SUPL Undervoltage Lockout          |                      | Rising edge, 50m\                                              | / hysteresis (typ)                 | 3.8   | 4                       | 4.3   | V     |

| SUPL Quiescent Current             | I <sub>SUPL</sub>    | I <sub>LDO</sub> = 100μA                                       |                                    |       | 120                     | 220   | μA    |

| Duna and Malta and (Nata 4)        |                      | LDO is set to                                                  | I <sub>LDO</sub> = 40mA            |       | 130                     | 300   | >/    |

| Dropout Voltage (Note 1)           | V <sub>DROP</sub>    | regulate at 9V                                                 | I <sub>LDO</sub> = 5mA             |       | 70                      |       | mV    |

| FBL Regulation Voltage             | V <sub>FBL</sub>     | V <sub>SUPL</sub> = 10V, LDC<br>I <sub>LDO</sub> = 15mA        | regulating at 9V,                  | 1.235 | 1.25                    | 1.265 | V     |

| LDO Load Regulation                |                      | V <sub>SUPL</sub> = 10V, LDC<br>I <sub>LDO</sub> = 100μA to 40 | o regulating at 9V,<br>OmA         |       |                         | 1.2   | %     |

| LDO Line Regulation                |                      | V <sub>SUPL</sub> = 4.5V to 1:<br>I <sub>LDO</sub> = 15mA      | 5V, FBL = LDOOUT,                  |       |                         | 0.02  | %/V   |

| FBL Input Bias Current             | I <sub>FBL</sub>     | V <sub>FBL</sub> = 1.25V                                       |                                    | -0.8  |                         | +0.8  | μA    |

| LDO Current Limit                  | I <sub>LDOLIM</sub>  | V <sub>SUPL</sub> = 10V, V <sub>LD</sub>                       | OOUT = 9V, V <sub>FBL</sub> = 1.2V | 40    | 130                     | 220   | mA    |

| VCOM BUFFER                        |                      |                                                                |                                    |       |                         |       |       |

| SUPB Input Supply Range            | V <sub>SUPB</sub>    |                                                                |                                    | 4.5   |                         | 13    | V     |

| SUPB Quiescent Current             | I <sub>SUPB</sub>    | V <sub>SUPB</sub> = 13V                                        |                                    |       | 420                     | 850   | μA    |

| BUFOUT Leakage Current             |                      |                                                                |                                    | -10   |                         | +10   | μA    |

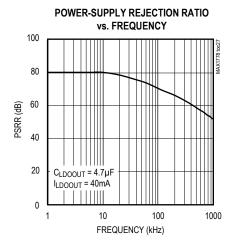

| Power-Supply Rejection Ratio       | PSRR                 | V <sub>SUPB</sub> = 4.5V to 13V, V <sub>CM</sub> = 2.25V       |                                    | 85    | 98                      |       | dB    |

| Input Common-Mode Voltage<br>Range | V <sub>CM</sub>      | V <sub>OS</sub>   < 10mV                                       |                                    | 1.2   |                         | 8.8   | V     |

| Common-Mode Rejection Ratio        | CMRR                 | V <sub>CM</sub> = 1.2V to 8.8V                                 |                                    | 75    |                         |       | dB    |

| Input Bias Current                 | I <sub>BIAS</sub>    | V <sub>CM</sub> = 5V                                           |                                    | -100  | -10                     | +100  | nA    |

| Input Offset Current               | los                  | V <sub>CM</sub> = 5V                                           |                                    | -100  |                         | +100  | nA    |

| Gain Bandwidth Product             | GBW                  | C <sub>BUF</sub> = 1µF                                         |                                    |       | 13                      |       | kHz   |

# **Electrical Characteristics (continued)**

$(V_{IN} = +3.0V, \overline{SHDN} = IN, V_{SUPP} = V_{SUPN} = V_{SUPB} = V_{SUPL} = 10V, \\ LDOOUT = FBL, \\ BUF- = BUFOUT, \\ BUF+ = FLTSET = TGND = PGND = GND, \\ C_{REF} = 0.22\mu F, \\ C_{BUF} = 1\mu F, \\ T_{A} = 0^{\circ}C \text{ to +85°C}. \\ Typical values are at \\ T_{A} = +25^{\circ}C, \\ unless otherwise noted.)$

| PARAMETER                            | SYMBOL              | COND                                                          | ITIONS                      | MIN                        | TYP  | MAX                        | UNITS |

|--------------------------------------|---------------------|---------------------------------------------------------------|-----------------------------|----------------------------|------|----------------------------|-------|

|                                      |                     |                                                               | I <sub>BUFOUT</sub> = 0     | 4.99                       |      | 5.01                       |       |

| Output Voltage                       | V <sub>BUFOUT</sub> | BUF+ = GND                                                    | I <sub>BUFOUT</sub> = ±5mA  | 4.97                       |      | 5.03                       | V     |

|                                      |                     |                                                               | I <sub>BUFOUT</sub> = ±45mA | 4.93                       |      | 5.07                       |       |

| Input Offset Voltage                 | V <sub>OS</sub>     | V <sub>SUPB</sub> = 4.5V to<br>13V, V <sub>CM</sub> = 1.2V to | I <sub>BUFOUT</sub> = ±5mA  | -30                        |      | +30                        | mV    |

|                                      | *05                 | (V <sub>SUPB</sub> - 1.2V)                                    | I <sub>BUFOUT</sub> = ±45mA | -70                        |      | +70                        | ****  |

| Output Voltage Swing High            | V <sub>OH</sub>     | I <sub>BUFOUT</sub> = -45mA, Δ\                               | <sub>OS</sub> = 1V          | 9                          | 9.6  |                            | V     |

| Output Voltage Swing Low             | V <sub>OL</sub>     | $I_{BUFOUT} = +45mA, \Delta'$                                 | V <sub>OS</sub> = 1V        |                            | 0.4  | 1                          | V     |

| Peak Buffer Output Current           |                     |                                                               |                             |                            | ±150 |                            | mA    |

| BUF+ Dual Mode™ Threshold<br>Voltage |                     | Falling edge, 20mV h                                          | ysteresis (typ)             | 80                         | 125  | 170                        | mV    |

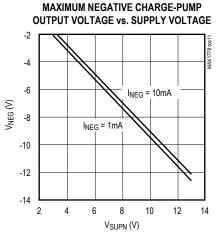

| REFERENCE                            |                     |                                                               |                             |                            |      |                            |       |

| Reference Voltage                    | V <sub>REF</sub>    | -2μA < I <sub>REF</sub> < 50μA                                |                             | 1.231                      | 1.25 | 1.269                      | V     |

| Reference Undervoltage<br>Threshold  |                     |                                                               |                             | 0.9                        | 1.05 | 1.2                        | V     |

| LOGIC SIGNALS                        |                     |                                                               |                             |                            |      |                            |       |

| SHDN Input Low Voltage               |                     |                                                               |                             |                            |      | 0.9                        | V     |

| SHDN Input High Voltage              |                     |                                                               |                             | 2.1                        |      |                            | V     |

| SHDN Input Current                   | I <sub>SHDN</sub>   |                                                               |                             |                            | 0.01 | 1                          | μA    |

| FLTSET Input Voltage Range           |                     |                                                               |                             | 0.67 x<br>V <sub>REF</sub> |      | 0.85 x<br>V <sub>REF</sub> | V     |

| FLTSET Threshold Voltage             |                     | Rising edge, 25mV hy                                          | steresis (typ)              | 80                         | 125  | 170                        | mV    |

| FLTSET Input Current                 |                     | V <sub>FLTSET</sub> = 1V                                      |                             |                            | 0.1  | 50                         | nA    |

| RDY Output Low Voltage               |                     | I <sub>SINK</sub> = 2mA                                       |                             |                            | 0.25 | 0.5                        | V     |

| RDY Output High Leakage              |                     | V <sub>RDY</sub> = 13V                                        |                             |                            | 0.01 | 1                          | μA    |

| Thermal Shutdown                     |                     | Rising temperature                                            |                             |                            | 160  |                            | °C    |

Dual Mode is a trademark of Maxim Integrated Products, Inc.

### **Electrical Characteristics**

$(V_{IN} = +3.0V, \overline{SHDN} = IN, V_{SUPP} = V_{SUPN} = V_{SUPB} = V_{SUPL} = 10V, LDOOUT = FBL, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND, C_{REF} = 0.22\mu F, C_{BUF} = 1\mu F, T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) \text{ (Note 2)}$

| PARAMETER                        | SYMBOL              |                                                     | CONDITIONS                                                      | MIN             | MAX   | UNITS |

|----------------------------------|---------------------|-----------------------------------------------------|-----------------------------------------------------------------|-----------------|-------|-------|

| Input Supply Range               | V <sub>IN</sub>     |                                                     |                                                                 | 2.7             | 5.5   | V     |

| Input Undervoltage Threshold     | V <sub>UVLO</sub>   | V <sub>IN</sub> Rising, 40r                         | mV hysteresis (typ)                                             | 2.2             | 2.6   | V     |

| IN Quiescent Supply Current      | 1                   | V <sub>FB</sub> =                                   | MAX1778/MAX1880/<br>MAX1883 (f <sub>OSC</sub> = 1MHz)           |                 | 1     | mA    |

| in Quiescent Supply Current      | I <sub>IN</sub>     | $V_{FBP} = 1.5V,$<br>$V_{FBN} = -0.2V$              | MAX1881/MAX1882/MAX1884/<br>MAX1885 (f <sub>OSC</sub> = 500kHz) |                 | 1     | IIIA  |

| SUPP Quiescent Current           | laaa                | V <sub>FBP</sub> = 1.5V                             | MAX1778/MAX1880<br>(f <sub>OSC</sub> = 1MHz)                    |                 | 0.7   | mA    |

| SUPP Quiescent Current           | I <sub>SUPP</sub>   | V <sub>FBP</sub> - 1.5V                             | MAX1881/MAX1882<br>(f <sub>OSC</sub> = 500kHz)                  |                 | 0.5   | IIIA  |

| SUPN Quiescent Current           | I                   | V <sub>FBN</sub> = -0.2V                            | MAX1778/MAX1880<br>(f <sub>OSC</sub> = 1MHz)                    |                 | 0.7   | mA    |

| SOFIN Quiescent Current          | I <sub>SUPN</sub>   | VFBN0.2V                                            | MAX1881/MAX1882<br>(f <sub>OSC</sub> = 500kHz)                  |                 | 0.5   | IIIA  |

| IN Shutdown Current              |                     | $V_{\overline{SHDN}} = 0, V_{II}$                   | <sub>N</sub> = 5V                                               |                 | 10    | μA    |

| SUPP Shutdown Current            |                     | V <sub>SHDN</sub> = 0, V <sub>S</sub><br>MAX1778/MA | <sub>SUPP</sub> = 13V,<br>(1880/MAX1881/MAX1882                 |                 | 10    | μA    |

| SUPN Shutdown Current            |                     | V <sub>SHDN</sub> = 0, V <sub>S</sub><br>MAX1778/MA | <sub>SUPN</sub> = 13V,<br>(1880/MAX1881/MAX1882                 |                 | 10    | μA    |

| SUPL Shutdown Current            |                     | V <sub>SHDN</sub> = 0, V <sub>S</sub><br>MAX1778/MA | <sub>SUPL</sub> = 13V,<br>(1881/MAX1883/MAX1884                 |                 | 10    | μA    |

| SUPB Shutdown Current            |                     | $V_{\overline{SHDN}} = 0, V_{S}$                    | <sub>SUPB</sub> = 13V                                           |                 | 13    | μA    |

| MAIN STEP-UP CONVERTER           |                     |                                                     |                                                                 |                 |       |       |

| Main Output Voltage Range        | $V_{MAIN}$          |                                                     |                                                                 | V <sub>IN</sub> | 13    | V     |

| FB Regulation Voltage            | $V_{FB}$            | Integrator enab                                     | oled, C <sub>INTG</sub> = 1000pF                                | 1.223           | 1.269 | V     |

| T B Negulation voltage           | v FB                | Integrator disal                                    | bled (INTG = REF)                                               | 1.21            | 1.29  | V     |

| FB Input Bias Current            | $I_{FB}$            | V <sub>FB</sub> = 1.25V, II                         | NTG = GND                                                       | -50             | +50   | nA    |

| Operating Frequency              | Face                | MAX1778/MAX                                         | (1880/MAX1883                                                   | 0.75            | 1.25  | MHz   |

| Operating Frequency              | Fosc                | MAX1881/MAX                                         | (1882/MAX1884/MAX1885                                           | 375             | 625   | kHz   |

| Oscillator Maximum Duty<br>Cycle |                     |                                                     |                                                                 | 79              | 91    | %     |

| LX Switch On-Resistance          | R <sub>LX(ON)</sub> | I <sub>LX</sub> = 100mA                             |                                                                 |                 | 0.7   | Ω     |

| LX Leakage Current               | I <sub>LX</sub>     | V <sub>LX</sub> = 13V                               |                                                                 |                 | 20    | μA    |

| LV Current Limit                 | 1.                  | Phase I = soft-start (1024/f <sub>OSC</sub> )       |                                                                 | 0.275           | 0.525 |       |

| LX Current Limit                 | I <sub>LIM</sub>    | Phase IV = full                                     | y on (after 3072/f <sub>OSC</sub> )                             | 1.1             | 2.05  | A     |

| FB Fault Trip Level              |                     | Falling edge, F                                     | LTSET = GND                                                     | 1.07            | 1.14  | V     |

# **Electrical Characteristics (continued)**

$(V_{IN} = +3.0V, \overline{SHDN} = IN, V_{SUPP} = V_{SUPN} = V_{SUPB} = V_{SUPL} = 10V, LDOOUT = FBL, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND, C_{REF} = 0.22\mu F, C_{BUF} = 1\mu F, T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) (Note 2)$

| PARAMETER                       | SYMBOL               | CONDITIONS                                                                         | MIN   | MAX   | UNITS |

|---------------------------------|----------------------|------------------------------------------------------------------------------------|-------|-------|-------|

| POSITIVE CHARGE PUMP (M         | AX1778/MAX1          | 880/MAX1881/MAX1882 only)                                                          |       |       |       |

| SUPP Input Supply Range         | V <sub>SUPP</sub>    |                                                                                    | 2.7   | 13    | V     |

| FBP Regulation Voltage          | V <sub>FBP</sub>     |                                                                                    | 1.2   | 1.3   | V     |

| FBP Input Bias Current          | I <sub>FBP</sub>     | V <sub>FBP</sub> = 1.5V                                                            | -50   | +50   | nA    |

| DRVP PCH On-Resistance          | R <sub>PCH(ON)</sub> |                                                                                    |       | 10    | Ω     |

| DRVP NCH On-Resistance          | D                    | V <sub>FBP</sub> = 1.2V                                                            |       | 4     | Ω     |

| DRVP NCH On-Resistance          | R <sub>NCH(ON)</sub> | V <sub>FBP</sub> = 1.3V                                                            | 20    |       | kΩ    |

| FBP Power-Ready Trip Level      |                      | Rising edge                                                                        | 1.09  | 1.16  | V     |

| NEGATIVE CHARGE PUMP (N         | MAX1778/MAX          | 1880/MAX1881/MAX1882 only)                                                         |       |       |       |

| SUPN Input Supply Range         | V <sub>SUPN</sub>    |                                                                                    | 2.7   | 13    | V     |

| FBN Regulation Voltage          | $V_{FBN}$            |                                                                                    | -50   | +50   | mV    |

| FBN Input Bias Current          | I <sub>FBN</sub>     | V <sub>FBN</sub> = 0                                                               | -50   | +50   | nA    |

| DRVN PCH On-Resistance          | R <sub>PCH(ON)</sub> |                                                                                    |       | 10    | Ω     |

| DDVN NCH On Begintenes          | D                    | V <sub>FBN</sub> = +50mV                                                           |       | 4     | Ω     |

| DRVN NCH On-Resistance          | R <sub>NCH(ON)</sub> | V <sub>FBN</sub> = -50mV                                                           | 20    | ,     | kΩ    |

| FBN Power-Ready Trip Level      |                      | Falling edge                                                                       | 80    | 165   | mV    |

| LOW DROPOUT LINEAR REG          | SULATOR (MA          | X1778/MAX1881/MAX1883/MAX1884 only)                                                |       |       |       |

| SUPL Input Supply Range         | V <sub>SUPL</sub>    |                                                                                    | 4.5   | 15    | V     |

| SUPL Undervoltage Lockout       |                      | Rising edge, 50mV hysteresis (typ)                                                 | 3.8   | 4.3   | V     |

| SUPL Quiescent Current          | I <sub>SUPL</sub>    | I <sub>LDO</sub> = 100μA                                                           |       | 240   | μA    |

| Dropout Voltage (Note 1)        | V <sub>DROP</sub>    | LDO regulating to 9V, I <sub>LDO</sub> = 40mA                                      |       | 330   | mV    |

| FBL Regulation Voltage          | V <sub>FBL</sub>     | V <sub>SUPL</sub> = 10V, LDO regulating to 9V,<br>I <sub>LDO</sub> = 15mA          | 1.222 | 1.265 | V     |

| LDO Load Regulation             |                      | V <sub>SUPL</sub> = 10V, LDO regulating to 9V,<br>I <sub>LDO</sub> = 100μA to 40mA |       | 1.2   | %     |

| LDO Line Regulation             |                      | V <sub>SUPL</sub> = 4.5V to 15V, FBL = LDOOUT,<br>I <sub>LDO</sub> = 15mA          |       | 0.02  | %/V   |

| FBL Input Bias Current          | I <sub>FBL</sub>     | V <sub>FBL</sub> = 1.25V                                                           | -1.2  | +1.2  | μA    |

| LDO Current Limit               | I <sub>LDOLIM</sub>  | V <sub>SUPL</sub> = 10V, V <sub>LDOOUT</sub> = 9V, V <sub>FBL</sub> = 1.2V         | 40    | 260   | mA    |

| VCOM BUFFER                     |                      |                                                                                    |       |       | -     |

| SUPB Input Supply Range         | V <sub>SUPB</sub>    |                                                                                    | 4.5   | 13    | V     |

| SUPB Quiescent Current          | I <sub>SUPB</sub>    | V <sub>SUPB</sub> = 13V                                                            |       | 850   | μA    |

| BUFOUT Leakage Current          |                      |                                                                                    | -10   | +10   | μA    |

| Input Common-Mode Voltage Range | V <sub>CM</sub>      | V <sub>OS</sub>   < 10mV                                                           | 1.2   | 8.8   | V     |

# **Electrical Characteristics (continued)**

$(V_{IN} = +3.0V, \overline{SHDN} = IN, V_{SUPP} = V_{SUPN} = V_{SUPB} = V_{SUPL} = 10V, LDOOUT = FBL, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND, C_{REF} = 0.22\mu F, C_{BUF} = 1\mu F, T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) (Note 2)$

| PARAMETER                           | SYMBOL              | CONDITIONS                                                   |                             | MIN                        | MAX                        | UNITS |

|-------------------------------------|---------------------|--------------------------------------------------------------|-----------------------------|----------------------------|----------------------------|-------|

| Input Bias Current                  | I <sub>BIAS</sub>   | V <sub>CM</sub> = 5V                                         |                             | -500                       | +500                       | nA    |

| Input Offset Current                | Ios                 | V <sub>CM</sub> = 5V                                         |                             | -500                       | +500                       | nA    |

|                                     |                     |                                                              | I <sub>BUFOUT</sub> = 0     | 4.988                      | 5.012                      |       |

| Output Voltage                      | V <sub>BUFOUT</sub> | BUF+ = GND                                                   | I <sub>BUFOUT</sub> = ±5mA  | 4.97                       | 5.03                       | V     |

|                                     |                     |                                                              | I <sub>BUFOUT</sub> = ±45mA | 4.93                       | 5.07                       |       |

| Input Offset Voltage                | Vos                 | V <sub>SUPB</sub> = 4.5V to 13V<br>V <sub>CM</sub> = 1.2V to | I <sub>BUFOUT</sub> = ±5mA  | -30                        | +30                        | mV    |

| input onset voltage                 | *05                 | (V <sub>SUPB</sub> - 1.2V)                                   | I <sub>BUFOUT</sub> = ±45mA | -70                        | +70                        | 111 V |

| Output Voltage Swing High           | V <sub>OH</sub>     | $I_{BUFOUT} = -45 \text{mA}, \Delta V_0$                     | <sub>OS</sub> = 1V          | 9                          |                            | V     |

| Output Voltage Swing Low            | V <sub>OL</sub>     | $I_{BUFOUT}$ = +45mA, $\Delta V$                             | <sub>OS</sub> = 1V          |                            | 1                          | V     |

| BUF+ Dual-Mode<br>Threshold Voltage |                     | Falling edge, 20mV hy                                        | steresis (typ)              | 80                         | 170                        | mV    |

| REFERENCE                           |                     | 1                                                            |                             |                            |                            |       |

| Reference Voltage                   | V <sub>REF</sub>    | -2μA < I <sub>REF</sub> < 50μA                               |                             | 1.223                      | 1.269                      | V     |

| Reference Undervoltage<br>Threshold |                     |                                                              |                             | 0.9                        | 1.2                        | V     |

| LOGIC SIGNALS                       | -                   |                                                              |                             |                            |                            |       |

| SHDN Input Low Voltage              |                     |                                                              |                             |                            | 0.9                        | V     |

| SHDN Input High Voltage             |                     |                                                              |                             | 2.1                        |                            | V     |

| SHDN Input Current                  | ISHDN               |                                                              |                             |                            | 1                          | μA    |

| FLTSET Input Voltage<br>Range       |                     |                                                              |                             | 0.74 x<br>V <sub>REF</sub> | 0.85 x<br>V <sub>REF</sub> | V     |

| FLTSET Threshold Voltage            |                     | Rising edge, 25mV hys                                        | steresis (typ)              | 80                         | 170                        | mV    |

| FLTSET Input Current                |                     | V <sub>FLTSET</sub> = 1V                                     |                             |                            | 50                         | nA    |

| RDY Output Low Voltage              |                     | I <sub>SINK</sub> = 2mA                                      |                             |                            | 0.5                        | V     |

| RDY Output High Leakage             |                     | V <sub>RDY</sub> = 13V                                       |                             |                            | 1                          | μA    |

Note 1: Dropout voltage is defined as the  $V_{SUPL}$  -  $V_{LDOOUT}$ , when  $V_{SUPL}$  is 100mV below the set value of  $V_{LDOOUT}$ . Note 2: Specifications to -40°C are guaranteed by design, not production tested.

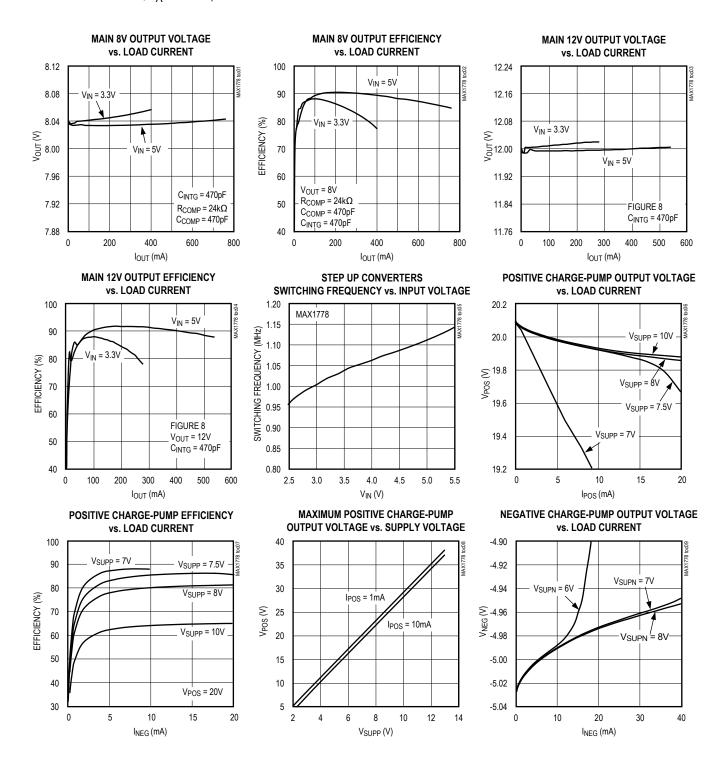

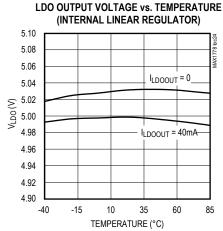

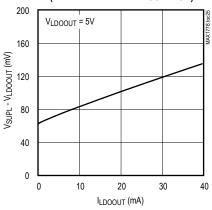

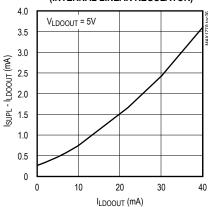

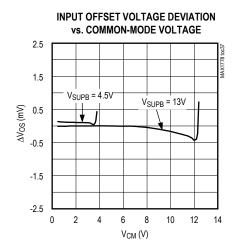

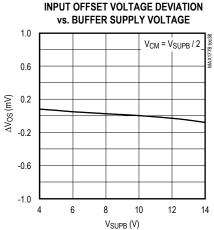

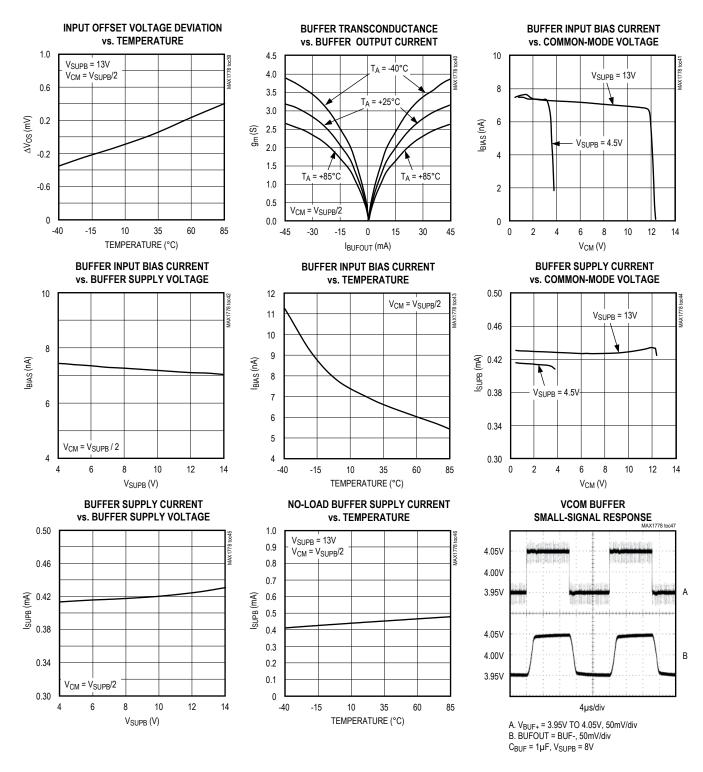

# **Typical Operating Characteristics**

(Circuit of Figure 1,  $V_{IN}$  = +3.3V,  $\overline{SHDN}$  = IN,  $V_{MAIN}$  =  $V_{SUPP}$  =  $V_{SUPN}$  =  $V_{SUPB}$  =  $V_{SUPL}$  = 8V, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND,  $T_A$  = +25°C.)

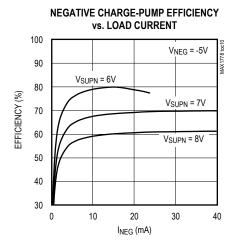

# **Typical Operating Characteristics (continued)**

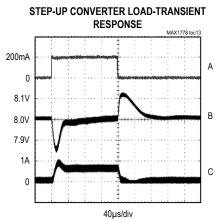

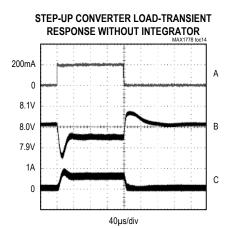

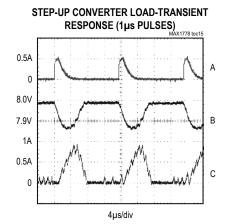

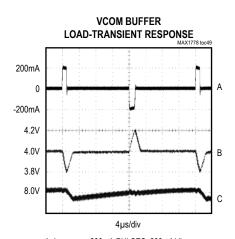

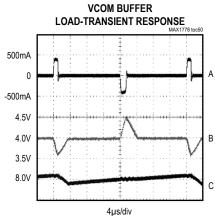

(Circuit of Figure 1,  $V_{IN}$  = +3.3V,  $\overline{SHDN}$  = IN,  $V_{MAIN}$  =  $V_{SUPP}$  =  $V_{SUPB}$  =  $V_{SUPL}$  = 8V, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND,  $T_A$  = +25°C.)

#### A. $I_{MAIN}$ = 20mA to 200mA, 200mA/div B. V<sub>MAIN</sub> = 8V, 100mV/div C. INDUCTOR CURRENT, 1A/div C<sub>INTG</sub> = 1000pF

A. I<sub>MAIN</sub> = 20mA to 200mA, 200mA/div B. V<sub>MAIN</sub> = 8V, 100mV/div C. INDUCTOR CURRENT, 1A/div INTG = REF

A. I<sub>MAIN</sub> = 0 to 500mA, 500mA/div B. V<sub>MAIN</sub> = 8V, 100mV/div C. INDUCTOR CURRENT, 500mA/div

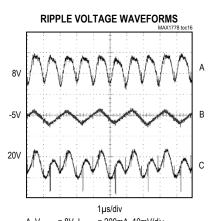

# **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN}$  = +3.3V,  $\overline{SHDN}$  = IN,  $V_{MAIN}$  =  $V_{SUPP}$  =  $V_{SUPB}$  =  $V_{SUPL}$  = 8V, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND,  $T_A$  = +25°C.)

A.  $V_{MAIN} = 8V$ ,  $I_{MAIN} = 200$ mA, 10mV/div B.  $V_{NEG}$  = -5V,  $I_{NEG}$  = 10mA, 20mV/div C.  $V_{POS} = 20V$ ,  $I_{POS} = 5mA$ , 20mV/div

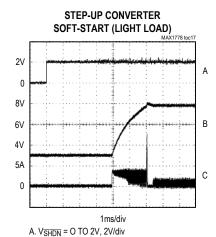

B. V<sub>MAIN</sub> = 8V, 2V/div C. INDUCTOR CURRENT, 500mA/div  $R_{LOAD}$  =  $400\Omega$

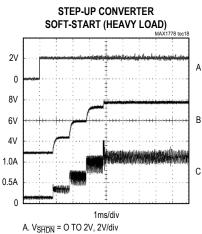

B. V<sub>MAIN</sub> = 8V, 2V/div C. INDUCTOR CURRENT, 500mA/div  $R_{LOAD} = 20\Omega$

POWER-UP INTO SHORT-CIRCUIT (CIRCUIT OF FIGURE 10)

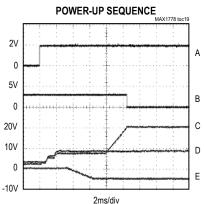

A. VSHDN = O TO 2V, 2V/div B. RDY, 5V/div

C. POSITIVE CHARGE PUMP =  $V_{POS}$  = 20V,  $R_{LOAD}$  =  $4k\Omega$ , 10V/divD. STEP-UP CONVERTER:  $V_{MAIN} = 8V$ ,  $R_{LOAD} = 40\Omega$ , 10V/divE. NEGATIVE CHARGE PUMP:  $V_{NEG} = -5V$ ,  $R_{LOAD} = 500\Omega$ , 10V/div

B. POSITIVE CHARGE PUMP, V<sub>POS(SYS)</sub> = 20V, 10V/div C. STEP-UP CONVERTER: V<sub>MAIN(SYS)</sub> = 8V, 10V/div D. NEGATIVE CHARGE PUMP, V<sub>NEG</sub> = -5V, -5V/div

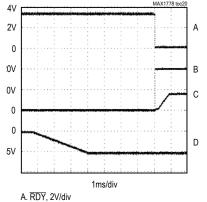

A. RDY, 2V/div B. GATE OF N-CH MOSFET, 5V/div

C. STEP-UP CONVERTER, V<sub>MAIN(START)</sub> = 8V, 5V/div  $V_{MAIN(SYS)} = GND$

# **Typical Operating Characteristics (continued)**

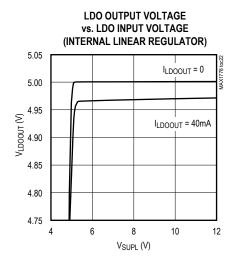

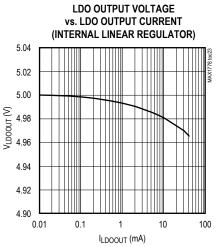

(Circuit of Figure 1,  $V_{IN}$  = +3.3V,  $\overline{SHDN}$  = IN,  $V_{MAIN}$  =  $V_{SUPP}$  =  $V_{SUPB}$  =  $V_{SUPL}$  = 8V, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND,  $T_A$  = +25°C.)

DROPOUT VOLTAGE vs. LDO LOAD CURRENT (INTERNAL LINEAR REGULATOR) 200 V<sub>LDOOUT</sub> = 5V

#### LDO SUPPLY CURRENT vs. LDO OUTPUT CURRENT (INTERNAL LINEAR REGULATOR)

# **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN}$  = +3.3V,  $\overline{SHDN}$  = IN,  $V_{MAIN}$  =  $V_{SUPP}$  =  $V_{SUPB}$  =  $V_{SUPL}$  = 8V, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND,  $T_A$  = +25°C.)

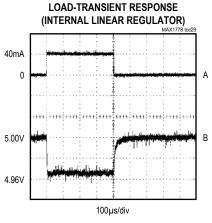

A.  $I_{LDO}$  = 100 $\mu$ A TO 40mA, 40mA/div B.  $V_{LDO}$  = 5V, 20mV/div  $V_{SUPL}$  =  $V_{LDO}$  + 500mV

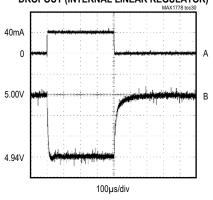

# LOAD-TRANSIENT RESPONSE NEAR DROPOUT (INTERNAL LINEAR REGULATOR)

A.  $I_{LDO}$  = 100 $\mu$ A TO 40mA, 40mA/div B.  $V_{LDO}$  = 5V, 20mV/div  $V_{IN}$  =  $V_{LDO}$  + 100mV

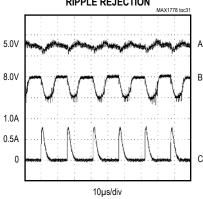

#### INTERNAL LINEAR-REGULATOR RIPPLE REJECTION

A.  $V_{LDOOUT}$  = 5V,  $I_{LDOOUT}$  = 40mA, 10mV/div B.  $V_{MAIN}$  =  $V_{SUPL}$  = 8V, 200mV/div C.  $I_{MAIN}$  = 0 TO 750mA, 500mA/div

# INTERNAL LINEAR-REGULATOR

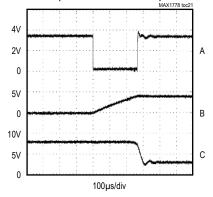

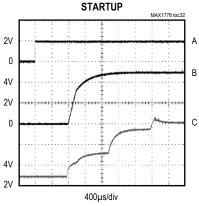

A.  $V_{\overline{S}H\overline{D}N}$  = 0 TO 2V, 2V/div B.  $V_{LDOOUT}$  = 5V,  $R_{LDOOUT}$  = 125 $\Omega$ , 2V/div C.  $V_{MAIN}$  = 8V,  $R_{MAIN}$  = 40 $\Omega$ , 2V/div

# **Typical Operating Characteristics (continued)**

(Circuit of Figure 1, V<sub>IN</sub> = +3.3V, SHDN = IN, V<sub>MAIN</sub> = V<sub>SUPP</sub> = V<sub>SUPN</sub> = V<sub>SUPB</sub> = V<sub>SUPL</sub> = 8V, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND,  $T_A = +25^{\circ}C$ .)

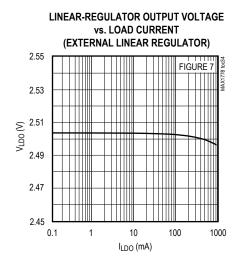

#### LINEAR-REGULATOR OUTPUT VOLTAGE vs. INPUT VOLTAGE (EXTERNAL LINEAR REGULATOR) 2.55 2.53 $I_{LDO} = 0$ 2.51 $I_{LDO} = 750 \text{mA}$ 2.49 2.47 FIGURE 7 2 45 3.5 3.0 4.0 4.5 5.0 2.5 5.5

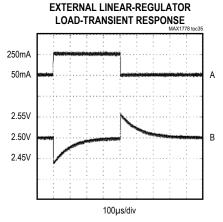

A.  $I_{LDO}$  = 50mA TO 250mA, 200mA/div B.  $V_{LDO} = 2.5V$ , 50mV/divFIGURE 7

$V_{IN}\left(V\right)$

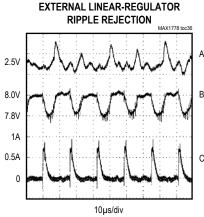

A.  $V_{LDO}$  = 2.5V,  $I_{LDO}$  = 200mA, 10mV/div B. V<sub>MAIN</sub> = V<sub>SUPL</sub> = 8V, 200mV/div C. I<sub>MAIN</sub> = 0 TO 750mA, 500mA/div FIGURE 7

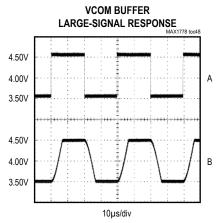

# **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN} = +3.3V$ ,  $\overline{SHDN} = IN$ ,  $V_{MAIN} = V_{SUPP} = V_{SUPN} = V_{SUPB} = V_{SUPL} = 8V$ , BUF - = BUFOUT, BUF + = FLTSET = 10.00TGND = PGND = GND,  $T_A = +25$ °C.)

# **Typical Operating Characteristics (continued)**

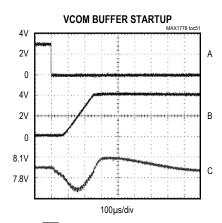

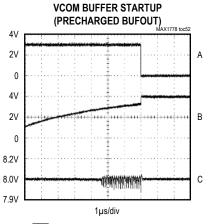

(Circuit of Figure 1,  $V_{IN}$  = +3.3V,  $\overline{SHDN}$  = IN,  $V_{MAIN}$  =  $V_{SUPP}$  =  $V_{SUPB}$  =  $V_{SUPL}$  = 8V, BUF- = BUFOUT, BUF+ = FLTSET = TGND = PGND = GND,  $T_A$  = +25°C.)

A.  $V_{BUF}$ + = 3.50V TO 4.50V, 0.5V/div B. BUFOUT = BUF-, 0.5V/div  $C_{BUF}$  = 1 $\mu$ F,  $V_{SUPB}$  = 8V

A.  $I_{BUFOUT}$  = 200mA PULSES, 200mA/div B. BUFOUT = BUF-, 200mV/div C.  $V_{MAIN}$  = 8V, 50mV/div  $V_{SUPB}$  =  $V_{MAIN}$ , BUF+ = GND,  $C_{BUF}$  = 1 $\mu$ F

A.  $I_{BUFOUT}$  = 400mA PULSES, 500mA/div B. BUFOUT = BUF-, 0.5V/div C.  $V_{MAIN}$  = 8V, 100mV/div  $V_{SUPB}$  =  $V_{MAIN}$ , BUF+ = GND,  $C_{BUF}$  = 1 $\mu$ F

A.  $\overline{RDY}$ , 2V/div B. BUFOUT = BUF-,  $C_{BUF}$  = 1 $\mu$ F, 2V/div C.  $V_{SUPB}$  =  $V_{MAIN}$  = 8V,  $I_{MAIN}$  = 20mA, 200mV/div BUF+ = GND

A.  $\overline{RDY}$ , 2V/div B. BUFOUT = BUF-,  $C_{BUF}$  = 1 $\mu$ F, 2V/div C.  $V_{SUPB}$  =  $V_{MAIN}$  = 8V,  $I_{MAIN}$  = 20mA, 200mV/div FIGURE 11

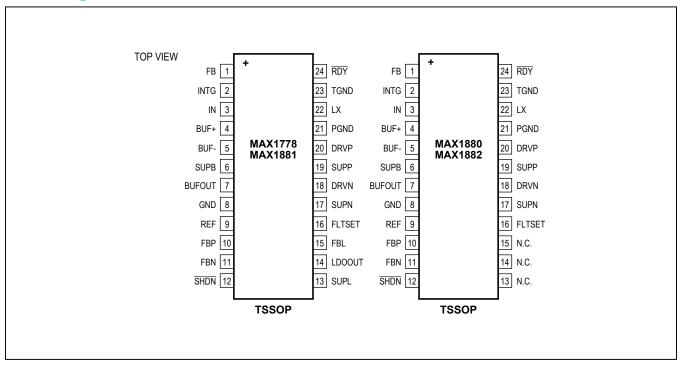

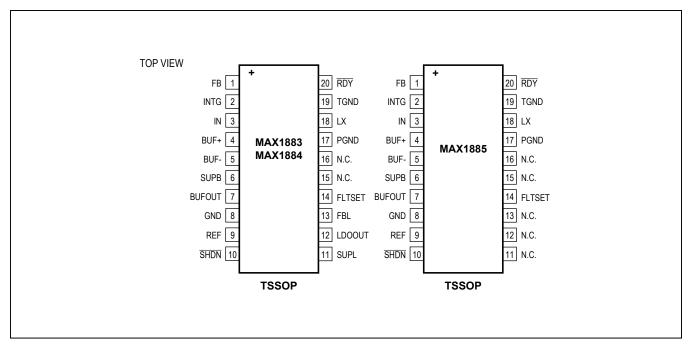

# **Pin Description**

|                    | PIN                |                    |         |        |                                                                                                                                                                                                                                        |

|--------------------|--------------------|--------------------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1778<br>MAX1881 | MAX1880<br>MAX1882 | MAX1883<br>MAX1884 | MAX1885 | NAME   | FUNCTION                                                                                                                                                                                                                               |

| 1                  | 1                  | 1                  | 1       | FB     | Main Step-Up Regulator Feedback Input. Regulates to 1.25V nominal. Connect a resistive divider from the output (V <sub>MAIN</sub> ) to FB to analog ground (GND).                                                                      |

| 2                  | 2                  | 2                  | 2       | INTG   | Main Step-Up Integrator Output. When using the integrator, connect 1000pF to analog ground (GND). To disable the integrator, connect INTG to REF.                                                                                      |

| 3                  | 3                  | 3                  | 3       | IN     | Main Supply Voltage. The supply voltage powers the control circuitry for all the regulators and can range from 2.7V to 5.5V. Bypass with a 0.1µF capacitor between IN and GND, as close to the pins as possible.                       |

| 4                  | 4                  | 4                  | 4       | BUF+   | VCOM Buffer (Operational Transconductance Amplifier) Positive Feedback Input. Connect to GND to select the internal resistive divider that sets the positive input to half the amplifier's supply voltage ( $V_{BUF+} = V_{SUPB}/2$ ). |

| 5                  | 5                  | 5                  | 5       | BUF-   | VCOM Buffer (Operational Transconductance Amplifier) Negative Feedback Input                                                                                                                                                           |

| 6                  | 6                  | 6                  | 6       | SUPB   | VCOM Buffer (Operational Transconductance Amplifier) Supply Voltage                                                                                                                                                                    |

| 7                  | 7                  | 7                  | 7       | BUFOUT | VCOM Buffer (Operational Transconductance Amplifier) Output                                                                                                                                                                            |

| 8                  | 8                  | 8                  | 8       | GND    | Analog Ground. Connect to power ground (PGND) underneath the IC.                                                                                                                                                                       |

| 9                  | 9                  | 9                  | 9       | REF    | Internal Reference Bypass Terminal. Connect a 0.22µF ceramic capacitor from REF to analog ground (GND). External load capability up to 50µA.                                                                                           |

| 10                 | 10                 | _                  | _       | FBP    | Positive Charge-Pump Regulator Feedback Input. Regulates to 1.25V nominal. Connect a resistive divider from the positive charge-pump output (V <sub>POS</sub> ) to FBP to analog ground (GND).                                         |

| 11                 | 11                 | _                  | _       | FBN    | Negative Charge-Pump Regulator Feedback Input. Regulates to 0V nominal. Connect a resistive divider from the negative charge-pump output (V <sub>NEG</sub> ) to FBN to the reference (REF).                                            |

| 12                 | 12                 | 10                 | 10      | SHDN   | Active-Low Shutdown Control Input. Pull SHDN low to force the controller into shutdown. If unused, connect SHDN to IN for normal operation. A rising edge on SHDN clears the fault latch.                                              |

| 13                 | _                  | 11                 | _       | SUPL   | Low-Dropout Linear Regulator Input Voltage. Can range from 4.5V to 15V. Bypass with a 1µF capacitor to GND (see <i>Capacitor Selection and Regulator Stability</i> ). Connect both input pins together externally.                     |

# **Pin Description (continued)**

| PIN                |                    |                    | PIN              |        |                                                                                                                                                                                                                                                                                                       |

|--------------------|--------------------|--------------------|------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1778<br>MAX1881 | MAX1880<br>MAX1882 | MAX1883<br>MAX1884 | MAX1885          | NAME   | FUNCTION                                                                                                                                                                                                                                                                                              |

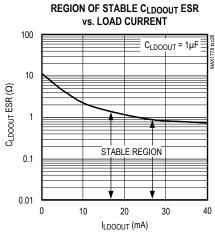

| 14                 | _                  | 12                 | _                | LDOOUT | Linear Regulator Output. Sources up to 40mA. Bypass to GND with a ceramic capacitor determined by: $C_{LDOOUT} \geq 0.5 ms \ X \left( \frac{I_{LDOOUT(MAX)}}{V_{LDOOUT}} \right)$                                                                                                                     |

| 15                 | _                  | 13                 | _                | FBL    | Voltage Setting Input. Connect a resistive divider from the linear regulator output (V <sub>LDOOUT</sub> ) to FBL to analog ground (GND).                                                                                                                                                             |

| 16                 | 16                 | 14                 | 14               | FLTSET | Fault Trip-Level Set Input. Connect to a resistive divider between REF and GND to set the main step-up converter's and positive charge pump's fault thresholds between 0.67 x V <sub>REF</sub> and 0.85 x V <sub>REF</sub> . Connect to GND for the preset fault threshold (0.9 x V <sub>REF</sub> ). |

| 17                 | 17                 | _                  | _                | SUPN   | Negative Charge-Pump Driver Supply Voltage. Bypass to power ground (PGND) with a 0.1µF capacitor.                                                                                                                                                                                                     |

| 18                 | 18                 | _                  | _                | DRVN   | Negative Charge-Pump Driver Output. Output high level is $V_{\mbox{SUPN}}$ and low level is PGND.                                                                                                                                                                                                     |

| 19                 | 19                 | _                  | _                | SUPP   | Positive Charge-Pump Driver Supply Voltage. Bypass to power ground (PGND) with a 0.1µF capacitor.                                                                                                                                                                                                     |

| 20                 | 20                 | _                  | _                | DRVP   | Positive Charge-Pump Driver Output. Output high level is V <sub>SUPP</sub> and low level is PGND                                                                                                                                                                                                      |

| 21                 | 21                 | 17                 | 17               | PGND   | Power Ground. Connect to analog ground (GND) underneath the IC.                                                                                                                                                                                                                                       |

| 22                 | 22                 | 18                 | 18               | LX     | Main Step-Up Regulator Power MOSFET N-Channel Drain. Place output diode and output capacitor as close as possible to PGND.                                                                                                                                                                            |

| 23                 | 23                 | 19                 | 19               | TGND   | Must be connected to ground.                                                                                                                                                                                                                                                                          |

| 24                 | 24                 | 20                 | 20               | RDY    | Active-Low, Open-Drain Output. Indicates all outputs are ready. On-resistance is $125\Omega$ (typ).                                                                                                                                                                                                   |

| _                  | 13–15              | 15, 16             | 11–13,<br>15, 16 | N.C.   | No Connection. Not internally connected.                                                                                                                                                                                                                                                              |

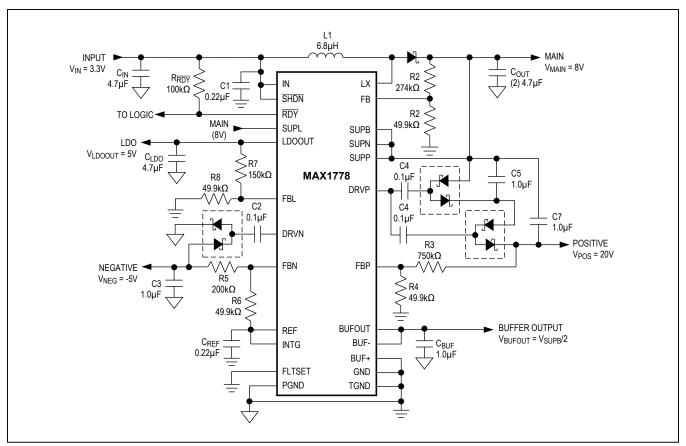

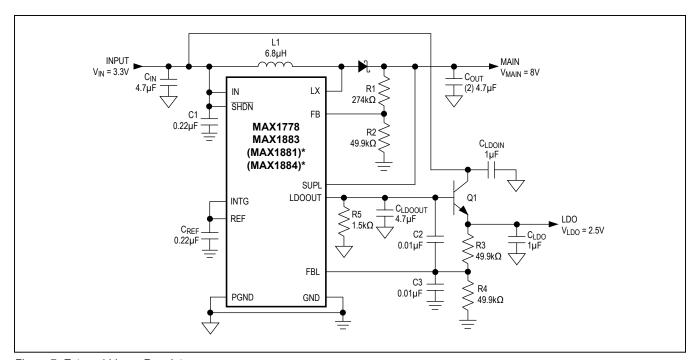

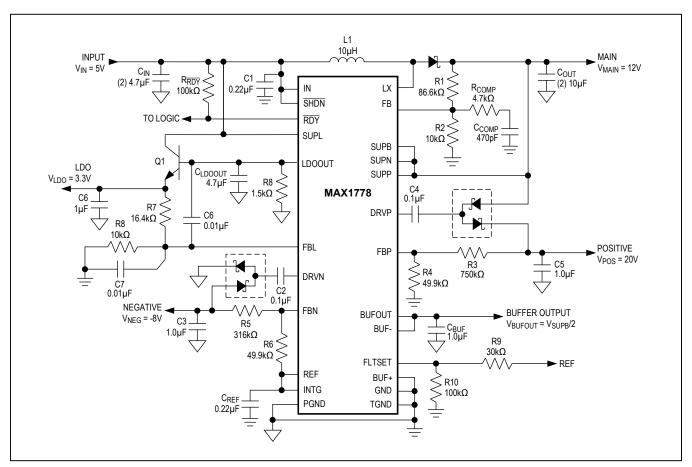

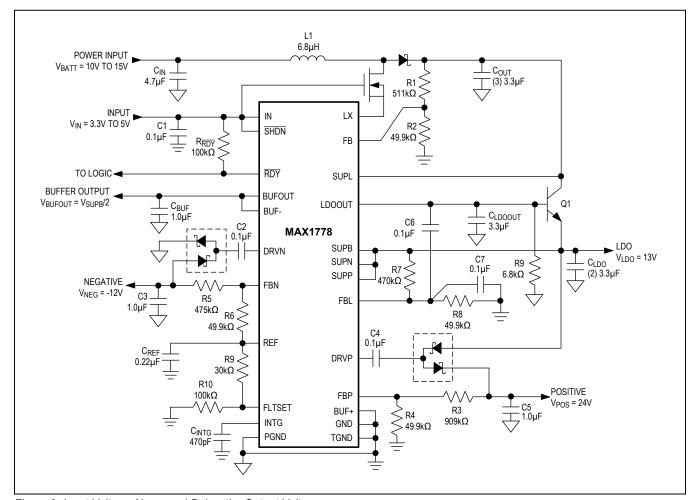

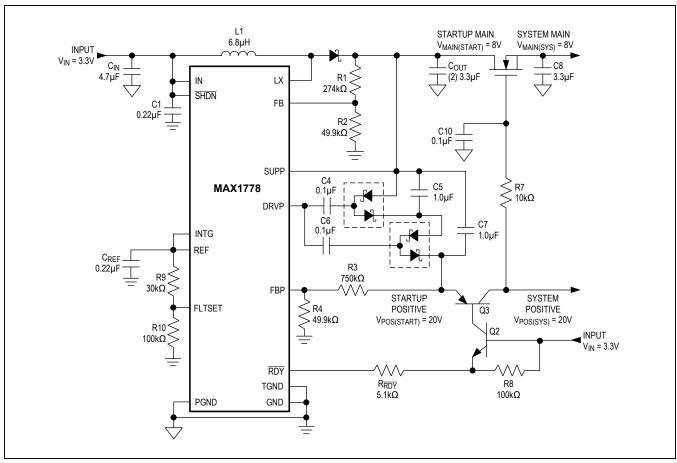

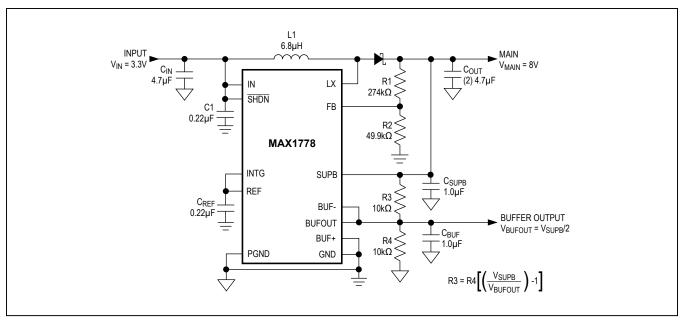

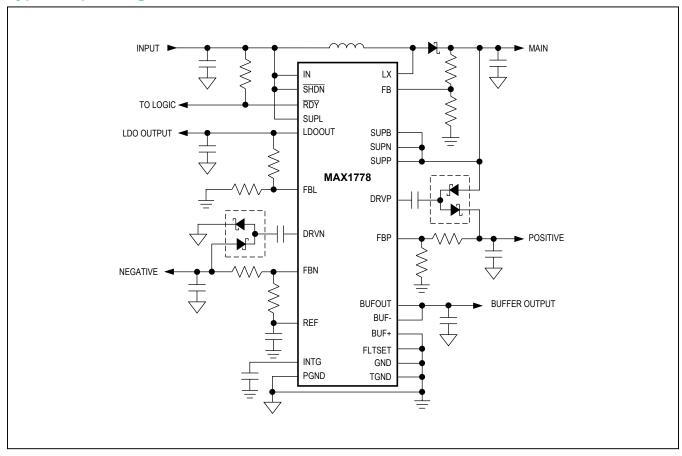

Figure 1. Typical Application Circuit

# **Detailed Description**

The MAX1778/MAX1880–MAX1885 are highly efficient multiple-output power supplies for thin-film transistor (TFT) liquid crystal display (LCD) applications. The devices contain one high-power step-up converter, two low-power charge pumps, an operational transconductance amplifier (VCOM buffer), and a low-dropout linear regulator. The primary step-up converter uses an internal N-channel MOSFET to provide maximum efficiency and to minimize the number of external components. The output voltage of the main step-up converter ( $V_{MAIN}$ ) can be set from  $V_{IN}$  to 13V with external resistors.

The dual charge pumps (MAX1778/MAX1880–MAX1882 only) independently regulate a positive output ( $V_{POS}$ ) and a negative output ( $V_{NEG}$ ). These low-power outputs use external diode and capacitor stages (as many stages as required) to regulate output voltages from - 40V to +40V. A unique control scheme minimizes output ripple as well as capacitor sizes for both charge pumps.

A resistor-programmable 40mA linear regulator (MAX1778/MAX1881/MAX1883/MAX1884 only) can provide preregulation or postregulation for any of the supplies. For higher current applications, an external transistor can be added.

Additionally, the VCOM buffer provides a high current output that is ideal for driving capacitive loads, such as the backplane of a TFT LCD panel. The positive feedback input features dual-mode operation, allowing this input to be connected to an internal 50% resistive-divider between the buffer's supply voltage and ground, or externally adjusted for other voltages.

Also included in the MAX1778/MAX1880–MAX1885 is a precision 1.25V reference that sources up to  $50\mu A$ , logic shutdown, soft-start, power-up sequencing, adjustable fault detection, thermal shutdown, and an active-low, open-drain ready output.

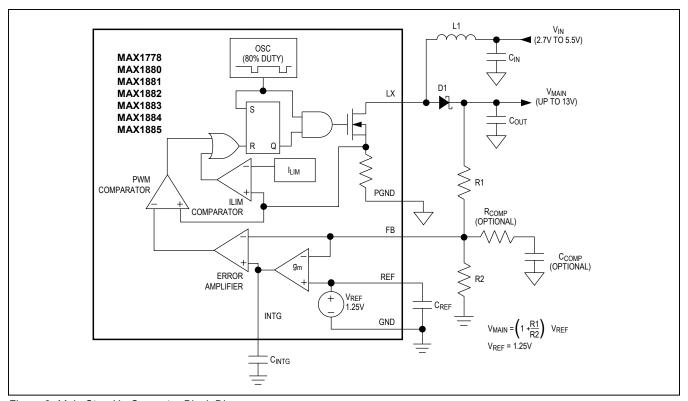

### Main Step-up Controller

During normal pulse-width modulation (PWM) operation, the MAX1778/MAX1880–MAX1885 main step-up controllers switch at a constant frequency of 500kHz or 1MHz (see the *Selector Guide*), allowing the use of low-profile inductors and output capacitors. Depending on the input-to-output voltage ratio, the controller regulates the output voltage and controls the power transfer by modulating the duty cycle (D) of each switching cycle:

$$D \approx \frac{V_{MAIN} - V_{IN}}{V_{MAIN}}$$

On the rising edge of the internal clock, the controller sets a flip-flop when the output voltage is too low, which turns on the n-channel MOSFET (Figure 2). The inductor current ramps up linearly, storing energy in a magnetic field. Once the sum of the feedback voltage error amplifier, slope-compensation, and current-feedback signals trip the multi-input comparator, the MOSFET turns off, the flip-flop resets, and the diode (D1) turns on. This forces the current through the inductor to ramp back down, transferring the energy stored in the magnetic field to the output capacitor and load. The MOSFET remains off for the rest of the clock cycle.

Changes in the feedback voltage-error signal shift the switch-current trip level, consequently modulating the MOSFET duty cycle.

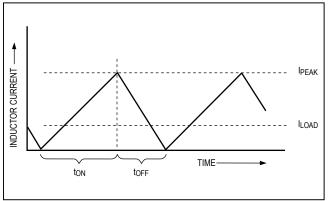

Under very light loads, an inherent switchover to pulse-skipping takes place (Figure 3). When this occurs, the controller skips most of the oscillator pulses in order to reduce the switching frequency and gate charge losses. When pulse-skipping, the step-up controller initiates a new switching cycle only when the output voltage drops too low. The n-channel MOSFET turns on, allowing the inductor current to ramp up until the multi-input comparator trips. Then, the MOSFET turns off and the diode turns on, forcing the inductor current to ramp down. When the inductor current reaches zero, the diode turns off, so the inductor stops conducting current. This forces the threshold between pulse-skipping and PWM operation to coincide with the boundary between continuous and discontinuous inductor-current operation:

$$I_{LOAD(CROSSOVER)} \approx \frac{1}{2} \left( \frac{V_{IN}}{V_{MAIN}} \right)^2 \left( \frac{V_{MAIN} - V_{IN}}{f_{OSC}L} \right)$$

Figure 2. Main Step-Up Converter Block Diagram

The switching waveforms appear noisy and asynchronous when light loading causes pulse-skipping operation; this is a normal operating condition that improves lightload efficiency.

Figure 3. Discontinuous-to-Continuous Conduction Crossover Point

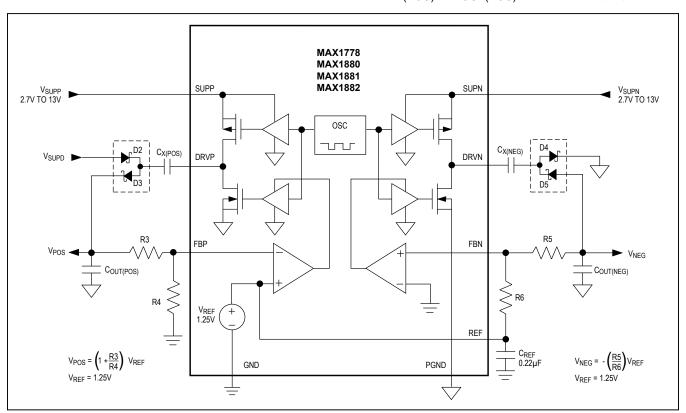

# Dual Charge-Pump Regulator (MAX1778/MAX1880-MAX1882 Only)

The MAX1778/MAX1880–MAX1882 controllers contain two independent low-power charge pumps (Figure 4). One charge pump inverts the input voltage and provides a regulated negative output voltage. The second charge pump doubles the input voltage and provides a regulated positive output voltage. The controllers contain internal p-channel and n-channel MOSFETs to control the power transfer. The internal MOSFETs switch at a constant frequency ( $f_{CHP} = f_{OSC}/2$ ).

### **Positive Charge Pump**

During the first half-cycle, the n-channel MOSFET turns on and charges flying capacitor  $C_{X(POS)}$  (Figure 4). This initial charge is controlled by the variable n-channel onresistance. During the second half-cycle, the n-channel MOSFET turns off and the p-channel MOSFET turns on, level shifting  $C_{X(POS)}$  by  $V_{SUPP}$  volts. This connects  $C_{X(POS)}$  in parallel with the reservoir capacitor  $C_{OUT(POS)}$ . If the voltage across  $C_{OUT(POS)}$  plus a diode drop  $(V_{POS} + V_{DIODE})$  is smaller than the level-shifted flying capacitor voltage  $(V_{CX(POS)} + V_{SUPP})$ , charge flows from  $C_{X(POS)}$  to  $C_{OUT(POS)}$  until the diode (D3) turns off.

Figure 4. Low-Power Charge Pump Block Diagram

#### **Negative Charge Pump**

During the first half-cycle, the p-channel MOSFET turns on, and flying capacitor  $C_{X(NEG)}$  charges to  $V_{SUPN}$  minus a diode drop (Figure 4). During the second half-cycle, the p-channel MOSFET turns off, and the n-channel MOSFET turns on, level shifting  $C_{X(NEG)}$ . This connects  $C_{X(NEG)}$  in parallel with reservoir capacitor  $C_{OUT(NEG)}$ . If the voltage across  $C_{OUT(NEG)}$  minus a diode drop is greater than the voltage across  $C_{X(NEG)}$ , charge flows from  $C_{OUT(NEG)}$  to  $C_{X(NEG)}$  until the diode (D5) turns off. The amount of charge transferred to the output is controlled by the variable n-channel on-resistance.

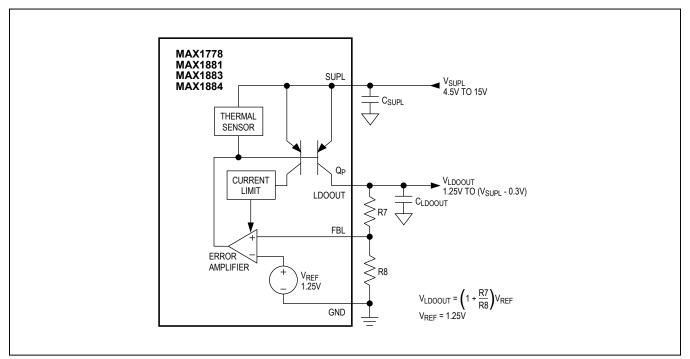

# Low-Dropout Linear Regulator (MAX1778/MAX1881/MAX1883/MAX1884 Only)

The MAX1778/MAX1881/MAX1883/MAX1884 contain a low-dropout linear regulator (Figure 5) that uses an internal pnp pass transistor (Qp) to supply loads up to 40mA. As illustrated in Figure 5, the 1.25V reference is connected to the error amplifier, which compares this reference with the feedback voltage and amplifies the difference. If the feedback voltage is higher than the reference voltage, the controller lowers the base current of Qp, which reduces the amount of current to the output. If the

feedback voltage is too low, the device increases the pass transistor base current, which allows more current to pass to the output and increases the output voltage. However, the linear regulator also includes an output current limit to protect the internal pass transistor against short circuits.

The low-dropout linear regulator monitors and controls the pass transistor's base current, limiting the output current to 130mA (typ). In conjunction with the thermal overload protection, this current limit protects the output, allowing it to be shorted to ground for an indefinite period of time without damaging the part.

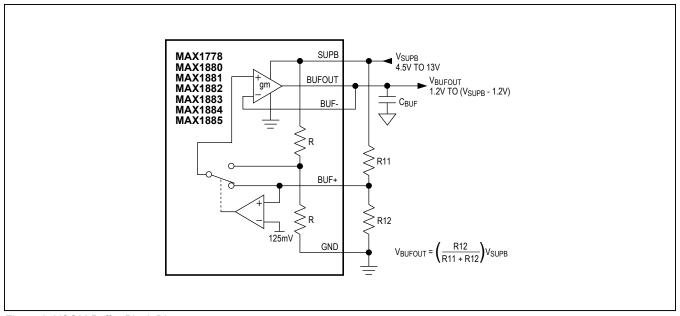

#### VCOM Buffer

The MAX1778/MAX1880–MAX1885 include a VCOM buffer, which uses an operational transconductance amplifier (OTA) to provide a current output that is ideal for driving capacitive loads, such as the backplane of a TFT LCD panel. The unity-gain bandwidth of this current-output buffer is:

$$GBW = gm/C_{OUT}$$

where gm is the amplifier's transconductance. The bandwidth is inversely proportional to the output capacitor, so large capacitive loads improve stability; however, lower bandwidth decreases the buffer's transient response time.

Figure 5. Low-Dropout Linear Regulator Block Diagram

Figure 6. VCOM Buffer Block Diagram

To improve the transient response times, the amplifier's transconductance increases as the output current increases (see the *Typical Operating Characteristics*).

The VCOM buffer's positive feedback input features dual mode operation. The buffer's output voltage can be internally set by a 50% resistive divider connected to the buffer's supply voltage (SUPB), or the output voltage can be externally adjusted for other voltages.

#### Shutdown (SHDN)

A logic-low level on \$\overline{SHDN}\$ shuts down all of the converters and the reference. When shut down, the supply current drops to 0.1\(\mu\)A to maximize battery life, and the reference is pulled to ground. The output capacitance, feedback resistors, and load current determine the rate at which each output voltage decays. A logic-level high on \$\overline{SHDN}\$ power activates the MAX1778/MAX1880–MAX1885 (see the *Power-Up Sequencing* section). Do not leave \$\overline{SHDN}\$ floating. If unused, connect \$\overline{SHDN}\$ to IN. A logic-level transition on \$\overline{SHDN}\$ clears the fault latch.

#### **Power-Up Sequencing**

Upon power-up or exiting shutdown, the MAX1778/MAX1880–MAX1885 start a power-up sequence. First, the reference powers up. Then, the main DC-DC step-up converter powers up with soft-start enabled. The linear regulator powers up at the same time as the main step-up converter; however, the power sequence and ready out-

put signal are not affected by the regulation of the linear regulator. While the main step-up converter powers up, the output of the PWM comparator remains low (Figure 2), and the step-up converter charges the output capacitors, limited only by the maximum duty cycle and currentlimit comparator. When the step-up converter approaches its nominal regulation value and the PWM comparator's output changes states for the first time, the negative charge pump turns on. When the negative output voltage reaches approximately 90% of its nominal value (V<sub>FBN</sub> < 110mV), the positive charge pump starts up. Finally, when the positive output voltage reaches 90% of its nominal value ( $V_{FBP} > 1.125V$ ), the active-low ready signal ( $\overline{RDY}$ ) goes low (see the Power Ready section), and the VCOM buffer powers up. The MAX1883-MAX1885 do not contain the charge pumps, but the power-up sequence still contains the charge pumps' startup logic, which appears as a delay (2 x 4096/f<sub>OSC</sub>) between the step-up converter reaching regulation and when the ready signal and VCOM buffer are activated.

#### Soft-Start

For the main step-up regulator, soft-start allows a gradual increase of the current-limit level during startup to reduce input surge currents. The MAX1778/MAX1880–MAX1885 divide the soft-start period into four phases. During the first phase, the controller limits the current limit to only 0.38A (see the *Electrical Characteristics*), approximately

a quarter of the maximum current limit (I<sub>LX(MAX)</sub>). If the output does not reach regulation within 1ms, soft-start enters phase II, and the current limit is increased by another 25%. This process is repeated for phase III. The maximum 1.5A (typ) current limit is reached within 3072 clock cycles or when the output reaches regulation, whichever occurs first (see the startup waveforms in the *Typical Operating Characteristics*).

For the charge pumps (MAX1778/MAX1880–MAX1882 only), soft-start is achieved by controlling the rate of rise of the output voltage. Both charge-pump output voltages are controlled to be in regulation within 4096 clock cycles, regardless of output capacitance and load, limited only by the charge pump's output impedance. Although the MAX1883–MAX1885 controllers do not include the charge pumps, the soft-start logic still contains the 4096 clock cycle startup periods for both charge pumps.

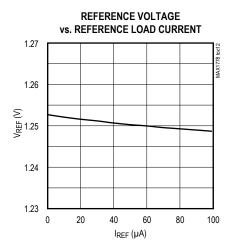

#### Fault Trip Level (FLTSET)

The MAX1778/MAX1880–MAX1885 feature dual-mode operation to allow operation with either a preset fault trip level or an adjustable trip level for the step-up converter and positive charge-pump outputs. Connect FLTSET to GND to select the preset 0.9 x V<sub>REF</sub> fault threshold. The fault trip level can also be adjusted by connecting a voltage-divider from REF to FLTSET (Figure 8). For greatest accuracy, the total load on the reference (including current through the negative charge-pump feedback resistors) should not exceed 50µA so that V<sub>REF</sub> is guaranteed to be in regulation (see the *Electrical Characteristics*). Therefore, select R10 in the 100k $\Omega$  to 1M $\Omega$  range, and calculate R9 with the following equation:

$$R9 = R10 [(V_{REF}/V_{FLTSET}) - 1]$$

where  $V_{REF}$  = 1.25V, and  $V_{FLTSET}$  can range from 0.67 x  $V_{REF}$  to 0.85 x  $V_{REF}$ . FLTSET's input bias current has a maximum value of 50nA. For 1% error, the current through R10 should be at least 100 times the FLTSET input bias current ( $I_{FLTSET}$ ).

#### **Fault Condition**

Once  $\overline{RDY}$  is low, if the output of the main regulator or either low-power charge pump falls below its fault detection threshold, or if the input drops below its undervoltage threshold, then  $\overline{RDY}$  goes high impedance and all outputs shut down; however, the reference remains active. After removing the fault condition, toggle shutdown (below 0.8V) or cycle the input voltage (below 0.2V) to clear the fault latch and reactivate the device.