# Intel Extended Temperature 82371EB PCI-TO-ISA/IDE Xcelerator (PIIX4E) Datasheet

- Supported Kits for both Pentium<sup>®</sup> and Pentium<sup>®</sup> II Microprocessors

- 82430TX ISA Kit

- 82440LX ISA/DP Kit

- Multifunction PCI to ISA Bridge

- Supports PCI at 30 MHz and 33 MHz

Supports PCI Rev 2.1 Specification

- Supports PCI Rev 2.1 Specification

Supports Full ISA or Extended I/O (EIO) Bus

- Supports Full Positive Decode or Subtractive Decode of PCI

- Supports ISA and EIO at 1/4 of PCI Frequency

- Supports both Mobile and Desktop Deep Green Environments

- 3.3V Operation with 5V Tolerant Buffers

- Ultra-low Power for Mobile Environments Support

- Power-On Suspend, Suspend to RAM, Suspend to Disk, and Soft-OFF System States

- All Registers Readable and Restorable for Proper Resume from 0.V Suspend

- Power Management Logic

- Global and Local Device Management

- Suspend and Resume Logic

- Supports Thermal Alarm

- Support for External Microcontroller

- Full Support for Advanced Configuration and Power Interface (ACPI) Revision 1.0 Specification and OS Directed Power Management

- Integrated IDE Controller

- Independent Timing of up to 4 Drives

- PIO Mode 4 and Bus Master IDE Transfers up to 14 Mbytes/sec

Supports "Ultra DMA/33"

- Supports "Ultra DMA/33" Synchronous DMA Mode Transfers

- up to 33 Mbytes/sec

© INTEL CORPORATION 1999

Integrated 16 x 32-bit Buffer for IDE PCI Burst Transfers

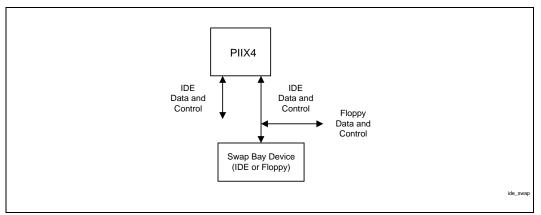

- Supports Glue-less "Swap-Bay" Option with Full Electrical Isolation

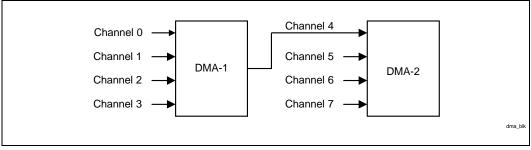

- Enhanced DMA Controller

- Two 82C37 DMA Controllers

- Supports PCI DMA with 3 PC/PCI Channels and Distributed DMA Protocols (Simultaneously)

- Fast Type-F DMA for Reduced PCI Bus Usage

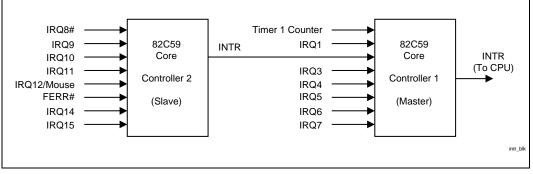

- Interrupt Controller Based on Two 82C59

- 15 Interrupt Support

- Independently Programmable for Edge/Level Sensitivity

- Supports Optional I/O APIC

- Serial Interrupt Input

- Timers Based on 82C54

- System Timer, Refresh Request, Speaker Tone Output

- Universal Serial Bus (USB) — Two USB 1.0 Ports for Serial

- Transfers at 12 or 1.5 Mbit/sec — Supports Legacy Keyboard and

- Mouse Software with USB-based Keyboard and Mouse

- Supports UHCI Design Guide

- SMBus

- Host Interface Allows CPU to Communicate Via SMBus

- Slave Interface Allows External SMBus Master to Control Resume Events

- Real-Time Clock

- 256-byte Battery-Back CMOS SRAM

- Includes Date Alarm

- Two 8-byte Lockout Ranges

- Microsoft Win95\* Compliant

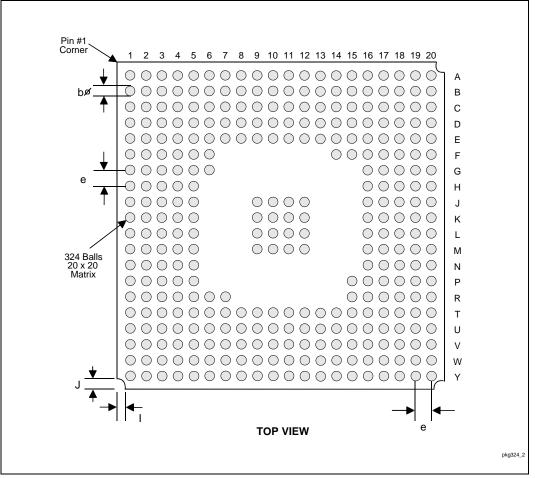

- 324 mBGA Package

ary 1999

Order Number: 273233-001

February 1999

in'

Information in this document is provided in conjunction with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by the sale of Intel products. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel retains the right to make changes to specifications and product descriptions at any time, without notice.

The 82371EB PIIX4E product may contain design defects or errors known as errata. Current characterized errata are available on request.

Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. Intel does not warrant or represent that such use will not infringe such rights.

I2C is a two-wire communication bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel. Implementation of the I2C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Third-party brands and names are the property of their respective owners.

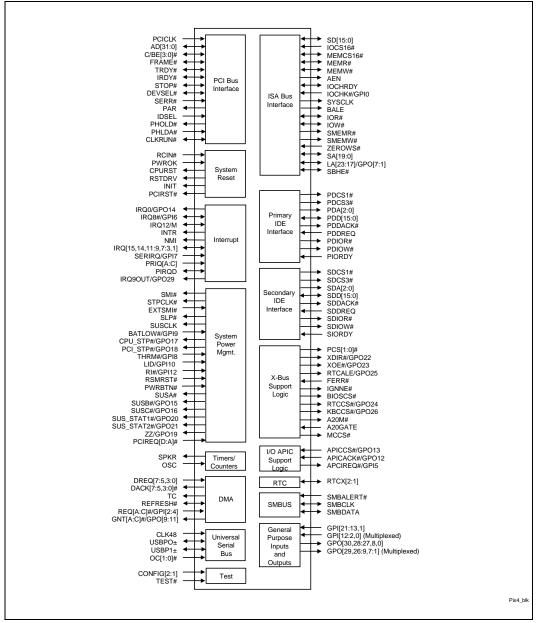

Simplified Block Diagram

# CONTENTS

### PAGE

| 1. 0.                                     | ARCHITECTURAL OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                                                          |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 2. 0.                                     | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                                          |

|                                           | 1. PIIX4E Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             |

|                                           | 2.1.1. PCI BUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18                                                                          |

|                                           | 2.1.2. ISA BUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                          |

|                                           | 2.1.3. X-BUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                                          |

|                                           | 2.1.4. DMA SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                             |

|                                           | 2.1.5. INTERRUPT CONTROLLER/APIC SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                                          |

|                                           | 2.1.6. CPU INTERFACE SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29                                                                          |

|                                           | 2.1.7. CLOCKING SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31                                                                          |

|                                           | 2.1.8. IDE SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31                                                                          |

|                                           | 2.1.9. UNIVERSAL SERIAL BUS SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                                                          |

|                                           | 2.1.10. POWER MANAGEMENT SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36                                                                          |

|                                           | 2.1.11. GENERAL PURPOSE INPUT AND OUTPUT SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39                                                                          |

|                                           | 2.1.12. OTHER SYSTEM AND TEST SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42                                                                          |

|                                           | 2.1.13. POWER AND GROUND PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42                                                                          |

|                                           | 2. Power Planes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                             |

| 2.3                                       | 3. Power Sequencing Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44                                                                          |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                             |

| 3. 0.                                     | REGISTER ADDRESS SPACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                          |

|                                           | REGISTER ADDRESS SPACE 1. PCI/ISA Bridge Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                           |

| 3.1                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                          |

| 3.1                                       | 1. PCI/ISA Bridge Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45<br>46                                                                    |

| 3.1                                       | 1. PCI/ISA Bridge Configuration<br>3.1.1. PCI CONFIGURATION REGISTERS (FUNCTION 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45<br>46<br>47                                                              |

| 3. <sup>-</sup><br>3.2                    | 1. PCI/ISA Bridge Configuration<br>3.1.1. PCI CONFIGURATION REGISTERS (FUNCTION 0)<br>3.1.2. IO SPACE REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45<br>46<br>47<br>50                                                        |

| 3. <sup>-</sup><br>3.2                    | PCI/ISA Bridge Configuration      PCI/ISA Bridge Configuration      1. PCI CONFIGURATION REGISTERS (FUNCTION 0)      IDE Configuration      IDE Configuration      2. IDE CONFIGURATION REGISTERS (FUNCTION 1)      3.2.2. IO SPACE REGISTERS                                                                                                                                                                                                                                                                                                              | 45<br>46<br>47<br>50<br>50<br>51                                            |

| 3. <sup>-</sup><br>3.2                    | PCI/ISA Bridge Configuration     3.1.1. PCI CONFIGURATION REGISTERS (FUNCTION 0)     3.1.2. IO SPACE REGISTERS     IDE Configuration     3.2.1. PCI CONFIGURATION REGISTERS (FUNCTION 1)                                                                                                                                                                                                                                                                                                                                                                   | 45<br>46<br>47<br>50<br>50<br>51                                            |

| 3.2<br>3.2<br>3.2                         | PCI/ISA Bridge Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45<br>46<br>47<br>50<br>51<br>51<br>51                                      |

| 3.7<br>3.2<br>3.3                         | PCI/ISA Bridge Configuration     1. PCI/ISA Bridge Configuration     3.1.1. PCI CONFIGURATION REGISTERS (FUNCTION 0)     3.1.2. IO SPACE REGISTERS     IDE Configuration     3.2.1. PCI CONFIGURATION REGISTERS (FUNCTION 1)     3.2.2. IO SPACE REGISTERS     Universal Serial Bus (USB) Configuration     3.3.1. PCI CONFIGURATION REGISTERS (FUNCTION 2)     3.3.2. IO SPACE REGISTERS                                                                                                                                                                  | 45<br>46<br>47<br>50<br>50<br>51<br>51<br>51<br>52                          |

| 3.7<br>3.2<br>3.3                         | PCI/ISA Bridge Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45<br>46<br>47<br>50<br>50<br>51<br>51<br>51<br>52                          |

| 3.4<br>3.2<br>3.4                         | PCI/ISA Bridge Configuration     1. PCI/ISA Bridge Configuration     3.1.1. PCI CONFIGURATION REGISTERS (FUNCTION 0)     3.1.2. IO SPACE REGISTERS     IDE Configuration     3.2.1. PCI CONFIGURATION REGISTERS (FUNCTION 1)     3.2.2. IO SPACE REGISTERS     Universal Serial Bus (USB) Configuration     3.3.1. PCI CONFIGURATION REGISTERS (FUNCTION 2)     3.3.2. IO SPACE REGISTERS                                                                                                                                                                  | 45<br>46<br>47<br>50<br>51<br>51<br>51<br>51<br>52<br>53                    |

| 3.4<br>3.2<br>3.4<br><b>4. 0.</b>         | PCI/ISA Bridge Configuration     1. PCI/ISA Bridge Configuration     3.1.1. PCI CONFIGURATION REGISTERS (FUNCTION 0)     3.1.2. IO SPACE REGISTERS     IDE Configuration     3.2.1. PCI CONFIGURATION REGISTERS (FUNCTION 1)     3.2.2. IO SPACE REGISTERS     Universal Serial Bus (USB) Configuration     3.3.1. PCI CONFIGURATION REGISTERS (FUNCTION 2)     3.3.2. IO SPACE REGISTERS     Power Management Configuration     3.4.1. IO SPACE REGISTERS  PCI TO ISA/EIO BRIDGE REGISTER DESCRIPTIONS                                                    | 45<br>46<br>50<br>51<br>51<br>51<br>52<br>53<br>54<br><b>56</b>             |

| 3.4<br>3.2<br>3.4<br>4. 0.<br>4.7         | PCI/ISA Bridge Configuration     1. PCI/ISA Bridge Configuration     3.1.1. PCI CONFIGURATION REGISTERS (FUNCTION 0)     3.1.2. IO SPACE REGISTERS     IDE Configuration     3.2.1. PCI CONFIGURATION REGISTERS (FUNCTION 1)     3.2.2. IO SPACE REGISTERS     Universal Serial Bus (USB) Configuration     3.3.1. PCI CONFIGURATION REGISTERS (FUNCTION 2)     3.3.2. IO SPACE REGISTERS     POwer Management Configuration     3.4.1. IO SPACE REGISTERS     PCI TO ISA/EIO BRIDGE REGISTER DESCRIPTIONS     PCI to ISA/EIO BRIDGE REGISTER DESCRIPTIONS | 45<br>46<br>47<br>50<br>51<br>51<br>51<br>52<br>53<br>54<br><b>56</b>       |

| 3.<br>3.<br>3.<br>3.<br>3.<br>4. 0.<br>4. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45<br>46<br>47<br>50<br>51<br>51<br>52<br>53<br>54<br><b>56</b><br>56       |

| 3.1<br>3.2<br>3.4<br>4. 0.<br>4. 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45<br>46<br>47<br>50<br>51<br>51<br>52<br>53<br>54<br><b>56</b><br>56<br>56 |

| 3.1<br>3.2<br>3.4<br>4. 0.<br>4. 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45<br>46<br>47<br>50<br>51<br>51<br>52<br>53<br>54<br><b>56</b><br>56<br>56 |

## Extended Temperature 82371EB (PIIX4E) Datasheet

|   | 4.1.4. PCISTS—PCI DEVICE STATUS REGISTER (FUNCTION 0)                    | 58 |

|---|--------------------------------------------------------------------------|----|

|   | 4.1.5. RID-REVISION IDENTIFICATION REGISTER (FUNCTION 0)                 | 58 |

|   | 4.1.6. CLASSC-CLASS CODE REGISTER (FUNCTION 0)                           | 59 |

|   | 4.1.7. HEDT-HEADER TYPE REGISTER (FUNCTION 0)                            | 59 |

|   | 4.1.8. IORT-ISA I/O RECOVERY TIMER REGISTER (FUNCTION 0)                 | 59 |

|   | 4.1.9. XBCS-XBUS CHIP SELECT REGISTER (FUNCTION 0)                       | 60 |

|   | 4.1.10. PIRQRC[A:D]-PIRQX ROUTE CONTROL REGISTERS (FUNCTION 0)           | 62 |

|   | 4.1.11. SERIRQC—SERIAL IRQ CONTROL REGISTER (FUNCTION 0)                 | 62 |

|   | 4.1.12. TOM-TOP OF MEMORY REGISTER (FUNCTION 0)                          | 63 |

|   | 4.1.13. MSTAT-MISCELLANEOUS STATUS REGISTER (FUNCTION 0)                 | 64 |

|   | 4.1.14. MBDMA[1:0]-MOTHERBOARD DEVICE DMA CONTROL REGISTERS (FUNCTION 0) | 64 |

|   | 4.1.15. APICBASE—APIC BASE ADDRESS RELOCATION REGISTER (FUNCTION 0)      | 65 |

|   | 4.1.16. DLC-DETERMINISTIC LATENCY CONTROL REGISTER (FUNCTION 0)          | 65 |

|   | 4.1.17. PDMACFG—PCI DMA CONFIGURATION REGISTER (FUNCTION 0)              | 66 |

|   | 4.1.18. DDMABP-DISTRIBUTED DMA SLAVE BASE POINTER REGISTERS (FUNCTION 0) | 67 |

|   | 4.1.19. GENCFG—GENERAL CONFIGURATION REGISTER (FUNCTION 0)               |    |

|   | 4.1.20. RTCCFG—REAL TIME CLOCK CONFIGURATION REGISTER (FUNCTION 0)       |    |

| 4 | 2. PCI to ISA/EIO Bridge IO Space Registers (IO)                         |    |

|   | 4.2.1. DMA REGISTERS                                                     |    |

|   | 4.2.1.1. DCOM—DMA Command Register (IO)                                  |    |

|   | 4.2.1.2. DCM—DMA Channel Mode Register (IO)                              |    |

|   | 4.2.1.3. DR—DMA Request Register (IO)                                    |    |

|   | 4.2.1.4. WSMB—Write Single Mask Bit (IO)                                 |    |

|   | 4.2.1.5. RWAMB—Read/Write All Mask Bits (IO)                             |    |

|   | 4.2.1.6. DS—DMA Status Register (IO)                                     |    |

|   | 4.2.1.7. DBADDR—DMA Base and Current Address Registers (IO)              |    |

|   | 4.2.1.8. DBCNT—DMA Base and Current Count Registers (IO)                 |    |

|   | 4.2.1.9. DLPAGE—DMA Low Page Registers (IO)                              |    |

|   | 4.2.1.10. DCBP—DMA Clear Byte Pointer Register (IO)                      |    |

|   | 4.2.1.11. DMC—DMA Master Clear Register (IO)                             |    |

|   | 4.2.1.12. DCLM—DMA Clear Mask Register (IO)                              |    |

|   | 4.2.2. INTERRUPT CONTROLLER REGISTERS                                    |    |

|   | 4.2.2.1. ICW1—Initialization Command Word 1 Register (IO)                |    |

|   | 4.2.2.2. ICW2—Initialization Command Word 2 Register (IO)                |    |

|   | 4.2.2.3. ICW3—Initialization Command Word 3 Register (IO)                |    |

|   | 4.2.2.4. ICW3—Initialization Command Word 3 Register (IO)                |    |

|   | 4.2.2.5. ICW4—Initialization Command Word 4 Register (IO)                |    |

|   | 4.2.2.6. OCW1—Operational Control Word 1 Register (IO)                   |    |

|   | 4.2.2.7. OCW2—Operational Control Word 2 Register (IO)                   |    |

|   | 4.2.2.8. OCW3—Operational Control Word 3 Register (IO)                   |    |

|   | 4.2.2.9. ELCR1—Edge/Level Control Register (IO)                          |    |

|   | 4.2.2.10. ELCR2—Edge/Level Control Register (IO)                         |    |

|   | 4.2.3. COUNTER/TIMER REGISTERS                                           | 84 |

# Extended Temperature 82371EB (PIIX4E) Datasheet

| 4.2.3.1. TCW—Timer Control Word Register (IO)                                                                                                                                                                                                                                 | 84                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 4.2.3.2. TMRSTS—Timer Status Registers (IO)                                                                                                                                                                                                                                   | 86                                     |

| 4.2.3.3. TMRCNT—Timer Count Registers (IO)                                                                                                                                                                                                                                    | 86                                     |

| 4.2.4. NMI REGISTERS                                                                                                                                                                                                                                                          | 87                                     |

| 4.2.4.1. NMISC-NMI Status and Control Register (IO)                                                                                                                                                                                                                           | 87                                     |

| 4.2.4.2. NMIEN—NMI Enable Register (Shared with Real-Time Clock Index Register) (IO)                                                                                                                                                                                          |                                        |

| 4.2.5. REAL TIME CLOCK REGISTERS                                                                                                                                                                                                                                              |                                        |

| 4.2.5.1. RTCI-Real-Time Clock Index Register (Shared with NMI Enable Register) (IO)                                                                                                                                                                                           |                                        |

| 4.2.5.2. RTCD—Real-Time Clock Data Register (IO)                                                                                                                                                                                                                              |                                        |

| 4.2.5.3. RTCEI—Real-Time Clock Extended Index Register (IO)                                                                                                                                                                                                                   | 89                                     |

| 4.2.5.4. RTCED—Real-Time Clock Extended Data Register (IO)                                                                                                                                                                                                                    | 89                                     |

| 4.2.6. ADVANCED POWER MANAGEMENT (APM) REGISTERS                                                                                                                                                                                                                              | 90                                     |

| 4.2.6.1. APMC—Advanced Power Management Control Port (IO)                                                                                                                                                                                                                     | 90                                     |

| 4.2.6.2. APMS—Advanced Power Management Status Port (IO)                                                                                                                                                                                                                      | 90                                     |

| 4.2.7. X-BUS, COPROCESSOR, AND RESET REGISTERS                                                                                                                                                                                                                                | 90                                     |

| 4.2.7.1. RIRQ—Reset X-Bus IRQ12/M and IRQ1 Register (IO)                                                                                                                                                                                                                      | 90                                     |

| 4.2.7.2. P92—Port 92 Register (IO)                                                                                                                                                                                                                                            | 91                                     |

| 4.2.7.3. CERR—Coprocessor Error Register (IO)                                                                                                                                                                                                                                 | 91                                     |

| 4.2.7.4. RC-Reset Control Register (IO)                                                                                                                                                                                                                                       | 92                                     |

|                                                                                                                                                                                                                                                                               |                                        |

| 5. 0. IDE CONTROLLER REGISTER DESCRIPTIONS (PCI FUNCTION 1)                                                                                                                                                                                                                   | 93                                     |

| 5. 0. IDE CONTROLLER REGISTER DESCRIPTIONS (PCI FUNCTION 1)<br>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)                                                                                                                                               |                                        |

|                                                                                                                                                                                                                                                                               | 93                                     |

| 5.1. IDE Controller PCI Configuration Registers (PCI Function 1)                                                                                                                                                                                                              | 93<br>93                               |

| 5.1. IDE Controller PCI Configuration Registers (PCI Function 1)<br>5.1.1. VID—VENDOR IDENTIFICATION REGISTER (FUNCTION 1)                                                                                                                                                    | 93<br>93<br>93                         |

| 5.1. IDE Controller PCI Configuration Registers (PCI Function 1)<br>5.1.1. VID—VENDOR IDENTIFICATION REGISTER (FUNCTION 1)<br>5.1.2. DID—DEVICE IDENTIFICATION REGISTER (FUNCTION 1)                                                                                          | 93<br>93<br>93<br>93                   |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li> <li>5.1.1. VID—VENDOR IDENTIFICATION REGISTER (FUNCTION 1)</li> <li>5.1.2. DID—DEVICE IDENTIFICATION REGISTER (FUNCTION 1)</li> <li>5.1.3. PCICMD—PCI COMMAND REGISTER (FUNCTION 1)</li> </ul> | 93<br>93<br>93<br>93<br>94             |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           | 93<br>93<br>93<br>93<br>93<br>94<br>95 |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

| <ul> <li>5.1. IDE Controller PCI Configuration Registers (PCI Function 1)</li></ul>                                                                                                                                                                                           |                                        |

## Extended Temperature 82371EB (PIIX4E) Datasheet

| 6. 0. | USB HOST CONTROLLER REGISTER DESCRIPTIONS (PCI FUNCTION 2)         | 105 |

|-------|--------------------------------------------------------------------|-----|

| 6.1   | . USB Host Controller PCI Configuration Registers (PCI Function 2) | 105 |

| (     | 6.1.1. VID—VENDOR IDENTIFICATION REGISTER (FUNCTION 2)             | 105 |

| (     | 6.1.2. DID—DEVICE IDENTIFICATION REGISTER (FUNCTION 2)             | 105 |

| (     | 6.1.3. PCICMD—PCI COMMAND REGISTER (FUNCTION 2)                    | 106 |

|       | 6.1.4. PCISTS—PCI DEVICE STATUS REGISTER (FUNCTION 2)              | 107 |

|       | 6.1.5. RID—REVISION IDENTIFICATION REGISTER (FUNCTION 2)           | 107 |

|       | 6.1.6. CLASSC—CLASS CODE REGISTER (FUNCTION 2)                     | 108 |

|       | 6.1.7. MLT—MASTER LATENCY TIMER REGISTER (FUNCTION 2)              | 108 |

|       | 6.1.8. HEDT—HEADER TYPE REGISTER (FUNCTION 2)                      | 109 |

|       | 6.1.9. INTLN—INTERRUPT LINE REGISTER (FUNCTION 2)                  | 109 |

|       | 6.1.10. INTPN—INTERRUPT PIN (FUNCTION 2)                           |     |

|       | 6.1.11. SBRNUM—SERIAL BUS RELEASE NUMBER (FUNCTION 2)              |     |

|       | 6.1.12. LEGSUP—LEGACY SUPPORT REGISTER (FUNCTION 2)                |     |

|       | 6.1.13. USBBA—USB I/O SPACE BASE ADDRESS Register (FUNCTION 2)     |     |

|       | 6.1.14. MISCSUP—Miscellaneous Support Register (FUNCTION 2)        |     |

|       | 2. USB Host Controller IO Space Registers                          |     |

|       | 6.2.1. USBCMD—USB COMMAND REGISTER (IO)                            |     |

|       | 6.2.2. USBSTS—USB STATUS REGISTER (IO)                             |     |

|       | 6.2.3. USBINTR—USB INTERRUPT ENABLE REGISTER (IO)                  |     |

|       | 6.2.4. FRNUM—FRAME NUMBER REGISTER (IO)                            |     |

|       | 6.2.5. FLBASEADD—FRAME LIST BASE ADDRESS REGISTER (IO)             |     |

|       | 6.2.6. SOFMOD—START OF FRAME (SOF) MODIFY REGISTER (IO)            |     |

|       | 6.2.7. PORTSC—PORT STATUS AND CONTROL REGISTER (IO)                | 119 |

| 7. 0. | POWER MANAGEMENT REGISTER DESCRIPTIONS                             | 120 |

|       | . Power Management PCI Configuration Registers (PCI Function 3)    |     |

|       | 7.1.1. VID—VENDOR IDENTIFICATION REGISTER (FUNCTION 3)             | 120 |

|       | 7.1.2. DID—DEVICE IDENTIFICATION REGISTER (FUNCTION 3)             | 121 |

|       | 7.1.3. PCICMD—PCI COMMAND REGISTER (FUNCTION 3)                    | 121 |

|       | 7.1.4. PCISTS—PCI DEVICE STATUS REGISTER (FUNCTION 3)              | 122 |

|       | 7.1.5. RID—REVISION IDENTIFICATION REGISTER (FUNCTION 3)           |     |

|       | 7.1.6. CLASSC—CLASS CODE REGISTER (FUNCTION 3)                     |     |

|       | 7.1.7. HEDT—HEADER TYPE REGISTER (FUNCTION 3)                      |     |

|       | 7.1.8. INTLN—INTERRUPT LINE REGISTER (FUNCTION 3)                  |     |

|       | 7.1.9. INTPN—INTERRUPT PIN (FUNCTION 3)                            |     |

|       | 7.1.10. PMBA—POWER MANAGEMENT BASE ADDRESS (FUNCTION 3)            |     |

|       | 7.1.11. CNTA—COUNT A (FUNCTION 3)                                  |     |

|       | 7.1.12. CNTB—COUNT B (FUNCTION 3)                                  |     |

|       | 7.1.13. GPICTL—GENERAL PURPOSE INPUT CONTROL (FUNCTION 3)          |     |

|       | 7.1.14. DEVRESD—DEVICE RESOURCE D (FUNCTION 3)                     |     |

|       | 7.1.15. DEVACTA—DEVICE ACTIVITY A (FUNCTION 3)                     |     |

|       | 7.1.16. DEVACTB—DEVICE ACTIVITY B (FUNCTION 3)                     | 130 |

| 7.1.17. DEVRESA—DEVICE RESOURCE A (FUNCTION 3)                | 131 |

|---------------------------------------------------------------|-----|

| 7.1.18. DEVRESB—DEVICE RESOURCE B (FUNCTION 3)                | 133 |

| 7.1.19. DEVRESC—DEVICE RESOURCE C (FUNCTION 3)                | 134 |

| 7.1.20. DEVRESE—DEVICE RESOURCE E (FUNCTION 3)                | 135 |

| 7.1.21. DEVRESF—DEVICE RESOURCE F (FUNCTION 3)                | 135 |

| 7.1.22. DEVRESG—DEVICE RESOURCE G (FUNCTION 3)                | 136 |

| 7.1.23. DEVRESH—DEVICE RESOURCE H (FUNCTION 3)                | 137 |

| 7.1.24. DEVRESI—DEVICE RESOURCE I (FUNCTION 3)                | 137 |

| 7.1.25. DEVRESJ—DEVICE RESOURCE J (FUNCTION 3)                | 138 |

| 7.1.26. PMREGMISC-MISCELLANEOUS POWER MANAGEMENT (FUNCTION 3) | 138 |

| 7.1.27. SMBBA—SMBUS BASE ADDRESS (FUNCTION 3)                 | 139 |

| 7.1.28. SMBHSTCFG—SMBUS HOST CONFIGURATION (FUNCTION 3)       | 139 |

| 7.1.29. SMBSLVC—SMBUS SLAVE COMMAND (FUNCTION 3)              | 139 |

| 7.1.30. SMBSHDW1—SMBUS SLAVE SHADOW PORT 1 (FUNCTION 3)       | 140 |

| 7.1.31. SMBSHDW2—SMBUS SLAVE SHADOW PORT 2 (FUNCTION 3)       | 140 |

| 7.1.32. SMBREV—SMBUS REVISION IDENTIFICATION (FUNCTION 3)     | 140 |

| 7.2. Power Management IO Space Registers                      | 141 |

| 7.2.1. PMSTS—POWER MANAGEMENT STATUS REGISTER (IO)            | 141 |

| 7.2.2. PMEN—POWER MANAGEMENT RESUME ENABLE REGISTER (IO)      | 142 |

| 7.2.3. PMCNTRL—POWER MANAGEMENT CONTROL REGISTER (IO)         | 142 |

| 7.2.4. PMTMR—POWER MANAGEMENT TIMER REGISTER (IO)             | 143 |

| 7.2.5. GPSTS—GENERAL PURPOSE STATUS REGISTER (IO)             | 143 |

| 7.2.6. GPEN—GENERAL PURPOSE ENABLE REGISTER (IO)              |     |

| 7.2.7. PCNTRL—PROCESSOR CONTROL REGISTER (IO)                 | 145 |

| 7.2.8. PLVL2—PROCESSOR LEVEL 2 REGISTER (IO)                  |     |

| 7.2.9. PLVL3—PROCESSOR LEVEL 3 REGISTER (IO)                  | 146 |

| 7.2.10. GLBSTS—GLOBAL STATUS REGISTER (IO)                    | 147 |

| 7.2.11. DEVSTS—DEVICE STATUS REGISTER (IO)                    | 148 |

| 7.2.12. GLBEN—GLOBAL ENABLE REGISTER (IO)                     | 148 |

| 7.2.13. GLBCTL—GLOBAL CONTROL REGISTER (IO)                   | 149 |

| 7.2.14. DEVCTL—DEVICE CONTROL REGISTER (IO)                   | 150 |

| 7.2.15. GPIREG—GENERAL PURPOSE INPUT REGISTER (IO)            | 151 |

| 7.2.16. GPOREG—GENERAL PURPOSE OUTPUT REGISTER (IO)           |     |

| 7.3. SMBus IO Space Registers                                 | 152 |

| 7.3.1. SMBHSTSTS—SMBUS HOST STATUS REGISTER (IO)              |     |

| 7.3.2. SMBSLVSTS—SMBUS SLAVE STATUS REGISTER (IO)             |     |

| 7.3.3. SMBHSTCNT—SMBUS HOST CONTROL REGISTER (IO)             |     |

| 7.3.4. SMBHSTCMD—SMBUS HOST COMMAND REGISTER (IO)             | 154 |

| 7.3.5. SMBHSTADD—SMBUS HOST ADDRESS REGISTER (IO)             | 155 |

| 7.3.6. SMBHSTDAT0—SMBUS HOST DATA 0 REGISTER (IO)             | 155 |

|                                                               |     |

# int<sub>el</sub>,

## Extended Temperature 82371EB (PIIX4E) Datasheet

| 7.3.7. SMBHSTDAT        | 1—SMBUS HOST DATA 1 REGISTER (IO)                      | 155 |

|-------------------------|--------------------------------------------------------|-----|

| 7.3.8. SMBBLKDAT-       | -SMBUS BLOCK DATA REGISTER (IO)                        | 156 |

| 7.3.9. SMBSLVCNT-       | -SMBUS SLAVE CONTROL REGISTER (IO)                     | 156 |

| 7.3.10. SMBSHDWC        | MD—SMBUS SHADOW COMMAND REGISTER (IO)                  | 157 |

| 7.3.11. SMBSLVEVT       |                                                        | 157 |

| 7.3.12. SMBSLVDAT       |                                                        | 157 |

| 8.0. PCI/ISA BRIDGE F   | UNCTIONAL DESCRIPTION                                  | 158 |

| 8.1. Memory and IO Ad   | ldress Map                                             | 158 |

|                         | S                                                      |     |

| 8.1.2. MEMORY ADI       | DRESS MAP                                              | 158 |

| 8.1.3. BIOS MEMOR       | ۲Y                                                     | 159 |

| 8.2. PCI Interface      |                                                        |     |

| 8.2.1. TRANSACTIO       | N TERMINATION                                          | 161 |

| 8.2.2. PARITY SUPF      | PORT                                                   | 161 |

| 8.2.3. PCI ARBITRA      | TION                                                   | 161 |

| 8.3. ISA/EIO Interface. |                                                        | 162 |

| 8.4. DMA Controller     |                                                        | 162 |

| 8.4.1. DMA TRANSF       | ER MODES                                               | 163 |

| 8.4.2. DMA TRANSF       | ER TYPES                                               | 164 |

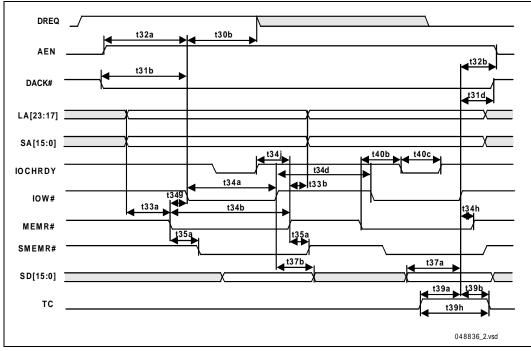

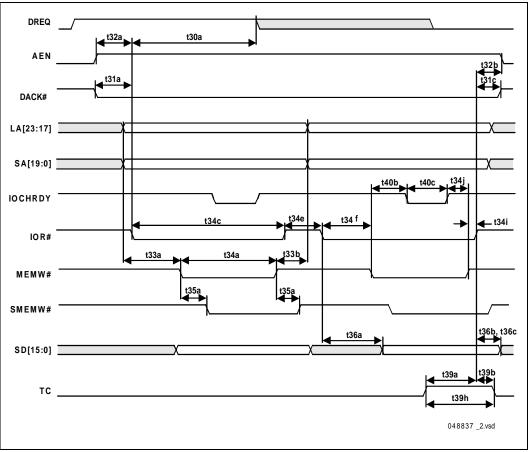

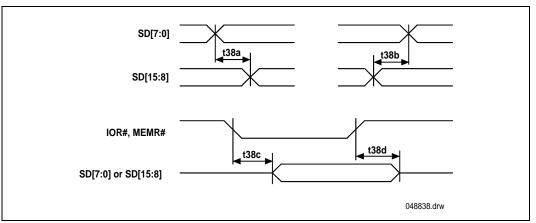

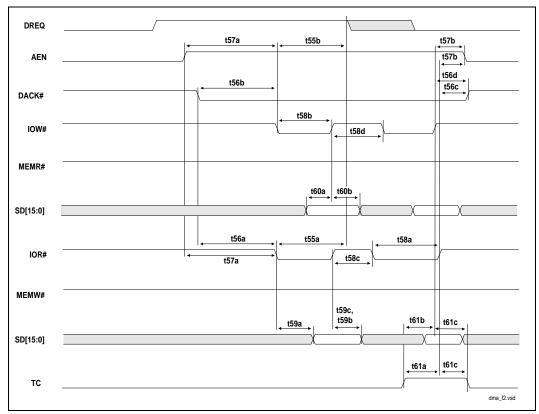

| 8.4.3. DMA TIMINGS      | 5                                                      | 165 |

| 8.4.4. DMA BUFFER       | R FOR TYPE F TRANSFERS                                 | 165 |

|                         | ACK# LATENCY CONTROL                                   |     |

| 8.4.6. CHANNEL PR       | IORITY                                                 | 166 |

| 8.4.7. REGISTER FL      | JNCTIONALITY                                           | 166 |

| 8.4.8. ADDRESS CC       | OMPATIBILITY MODE                                      | 166 |

| 8.4.9. SUMMARY OF       | F DMA TRANSFER SIZES                                   | 167 |

| 8.4.9.1. Address S      | Shifting When Programmed for 16-Bit I/O Count by Words | 167 |

| 8.4.10. AUTOINITIAI     | LIZE                                                   | 167 |

| 8.4.11. SOFTWARE        | COMMANDS                                               | 168 |

| 8.4.12. ISA REFRES      | SH CYCLES                                              | 168 |

| 8.5. PCI DMA            |                                                        | 169 |

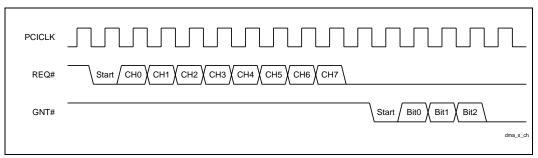

| 8.5.1. PC/PCI DMA.      |                                                        | 169 |

| 8.5.2. DISTRIBUTED      | D DMA                                                  | 172 |

|                         | ·                                                      |     |

| 8.6.1. PROGRAMMI        | NG THE INTERRUPT CONTROLLER                            | 176 |

|                         | RRUPT OPERATION                                        |     |

| 8.6.3. MODES OF O       | PERATION                                               | 177 |

|                         | DDE                                                    |     |

| 8.6.5. EDGE AND LE      | EVEL TRIGGERED MODE                                    | 179 |

| 8.6.6. INTERRUPT N      | MASKS                                                  |     |

| 8.6.7. READING THE      | E INTERRUPT CONTROLLER STATUS                          |     |

| 8.6.8. INTERRUPT S      | STEERING                                               |     |

# intط،

| 8.7. Serial Interrupts                                          |     |

|-----------------------------------------------------------------|-----|

| 8.7.1. PROTOCOL                                                 |     |

| 8.8. Timer/Counters                                             |     |

| 8.8.1. PROGRAMMING THE INTERVAL TIMER                           | 184 |

| 8.9. Real Time Clock                                            |     |

| 8.9.1. RTC REGISTERS AND RAM                                    |     |

| 8.9.1.1. Control Register A                                     |     |

| 8.9.1.2. Control Register B                                     | 190 |

| 8.9.1.3. Control Register C                                     | 191 |

| 8.9.1.4. Control Register D                                     | 191 |

| 8.9.2. RTC UPDATE CYCLE                                         | 192 |

| 8.9.3. RTC INTERRUPTS                                           |     |

| 8.9.4. LOCKABLE RAM RANGES                                      | 192 |

| 8.9.5. RTC EXTERNAL CONNECTIONS                                 |     |

| 8.10. Reset Support                                             |     |

| 8.11. Stand-Alone I/O APIC Support                              | 194 |

| 9.0. IDE CONTROLLER FUNCTIONAL DESCRIPTION                      |     |

| 9.1. IDE Signal Configuration                                   |     |

| 9.2. ATA Register Block Decode                                  |     |

| 9.3. PIO IDE Transactions                                       |     |

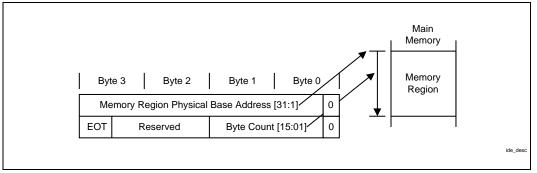

| 9.4. Bus Master Function                                        |     |

| 9.5. "Ultra DMA/33" Synchronous DMA Operation                   |     |

| 10. 0. USB HOST CONTROLLER FUNCTIONAL DESCRIPTION               | 203 |

|                                                                 |     |

| 11. 0. POWER MANAGEMENT FUNCTIONAL DESCRIPTION                  |     |

| 11.1. Power Management Overview                                 |     |

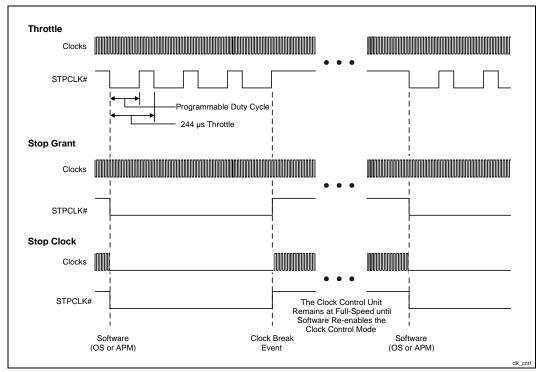

| 11.2. Clock Control                                             |     |

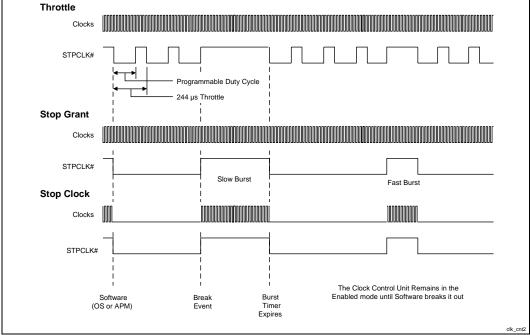

| 11.2.1. HOST CLOCK CONTROL MECHANISMS                           |     |

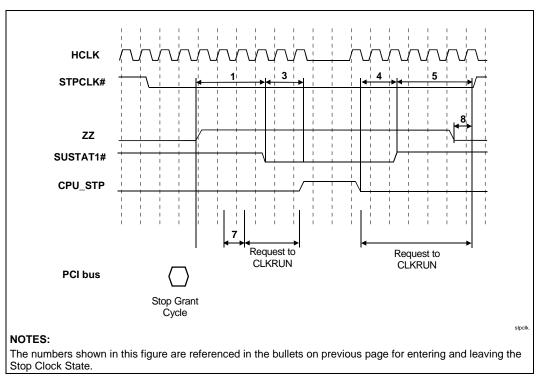

| 11.2.2. STOP CLOCK AND DEEP SLEEP STATE EXAMPLE SEQUENCE        |     |

| 11.2.3. PCI CLOCK CONTROL                                       |     |

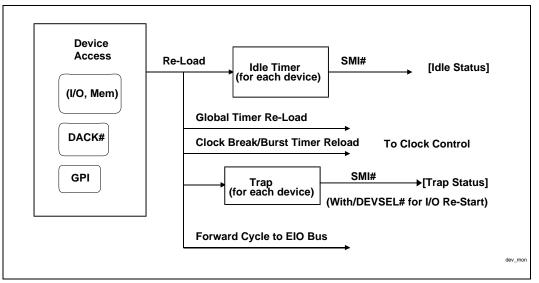

| 11.3. Peripheral Device Management<br>11.3.1. DEVICE IDLE TIMER |     |

|                                                                 |     |

|                                                                 |     |

| 11.3.3. PERIPHERAL DEVICE MANAGEMENT SEQUENCE                   |     |

| 11.3.4. DEVICE LOCATION ON PCI BUS OR ISA BUS                   |     |

| 11.3.5. DEVICE SPECIFIC DETAILS                                 |     |

| 11.3.5.1. Device 0: IDE Primary Drive 0                         |     |

| 11.3.5.2. Device 1: IDE Primary Drive 1                         |     |

| 11.3.5.3. Device 2: IDE Secondary Drive 0                       |     |

| 11.3.5.4. Device 3: IDE Secondary Drive 1                       |     |

## Extended Temperature 82371EB (PIIX4E) Datasheet

| 11.3.5.5. Device 4: Audio                                                            | 222 |

|--------------------------------------------------------------------------------------|-----|

| 11.3.5.6. Device 5: Floppy Disk Drive                                                | 223 |

| 11.3.5.7. Device 6: Serial Port A                                                    | 224 |

| 11.3.5.8. Device 7: Serial Port B                                                    | 225 |

| 11.3.5.9. Device 8: LPT (Parallel Port)                                              | 226 |

| 11.3.5.10. Device 9: Generic I/O Device 0                                            | 227 |

| 11.3.5.11. Device 10: Generic I/O Device 1                                           | 228 |

| 11.3.5.12. Device 11: User Interface (Keyboard, Mouse, Video)                        | 229 |

| 11.3.5.13. Device 12: Cardbus Slot (or Generic I/O and MEM Device)                   | 230 |

| 11.3.5.14. Device 13: Cardbus Slot (or Generic I/O and MEM Device)                   | 231 |

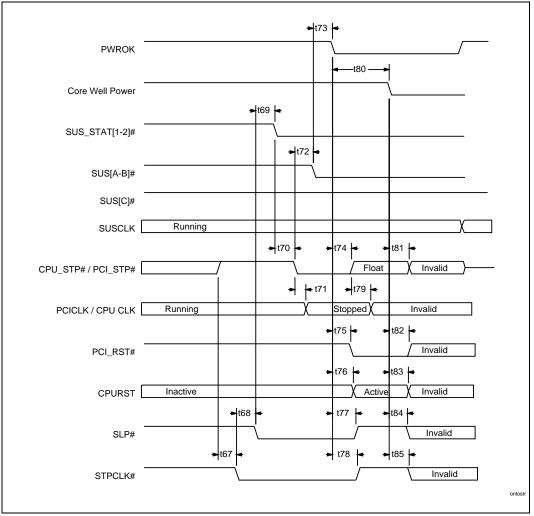

| 11.4. Suspend/Resume and Power Plane Control                                         | 232 |

| 11.4.1. SYSTEM SUSPEND                                                               | 232 |

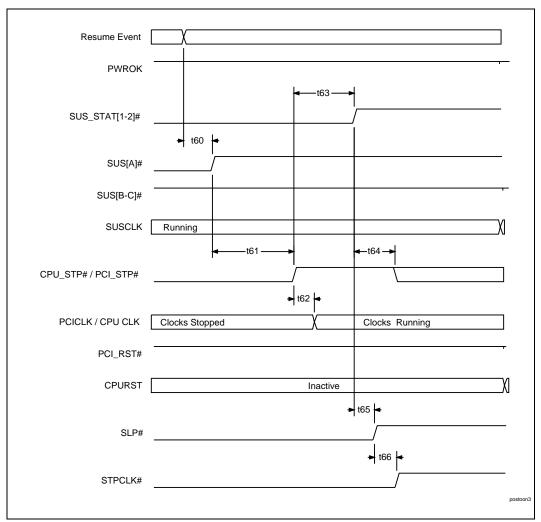

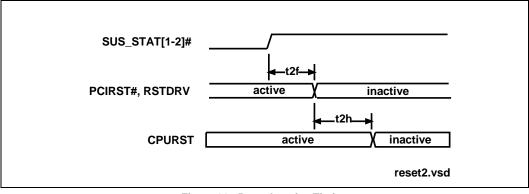

| 11.4.2. SYSTEM RESUME                                                                | 234 |

| 11.4.3. SYSTEM SUSPEND AND RESUME CONTROL SIGNALING                                  | 236 |

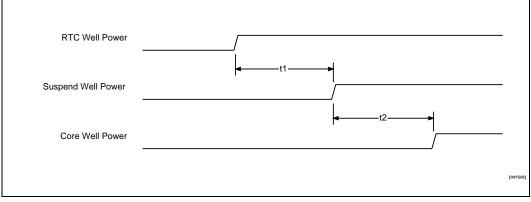

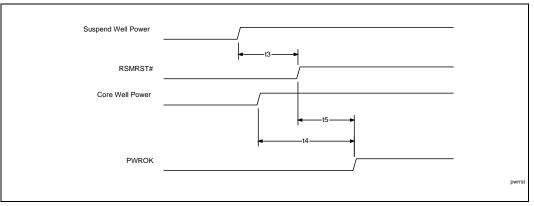

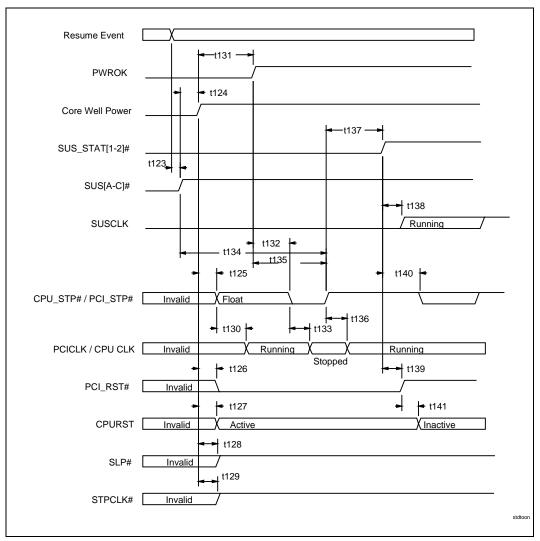

| 11.4.3.1. Power Supply Timings                                                       | 236 |

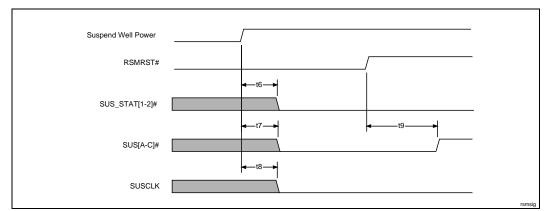

| 11.4.3.2. Power Level Active Status Signal Timings                                   | 237 |

| 11.4.3.3. Power Management Signal Timings (Powered From Suspend Power Well)          |     |

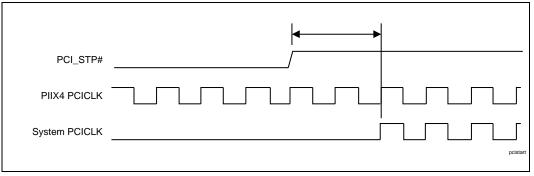

| 11.4.3.4. PCI Clock Stop and Start Timing Relationships                              | 239 |

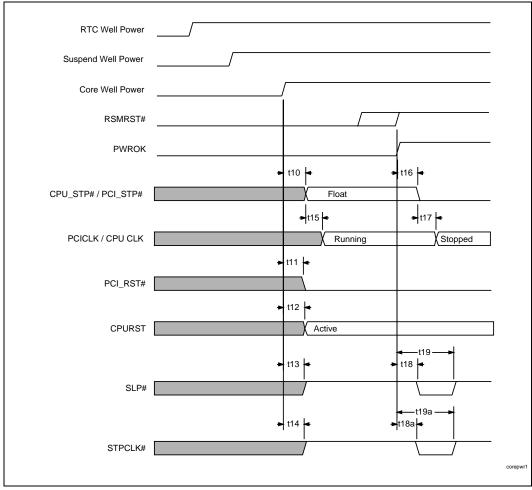

| 11.4.3.5. Power Management Signal Timings (Powered From PIIX4E Main Core Well)       | 240 |

| 11.4.3.6. Power Management Signal Timings (Powered From PIIX4E Main Core Well)       | 242 |

| 11.4.3.7. Mechanical Off to On Condition Timings                                     | 244 |

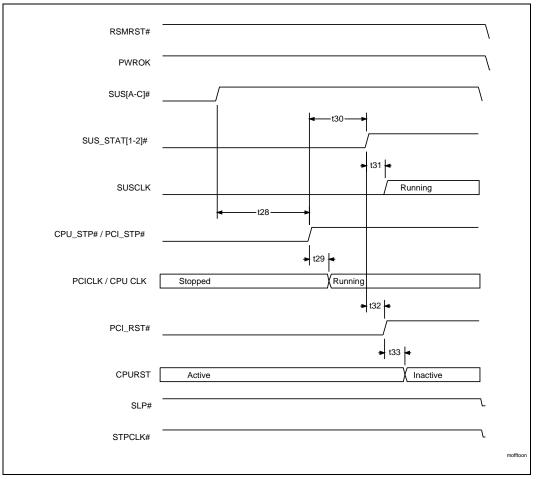

| 11.4.3.8. On State to Power On Suspend State Timing                                  | 246 |

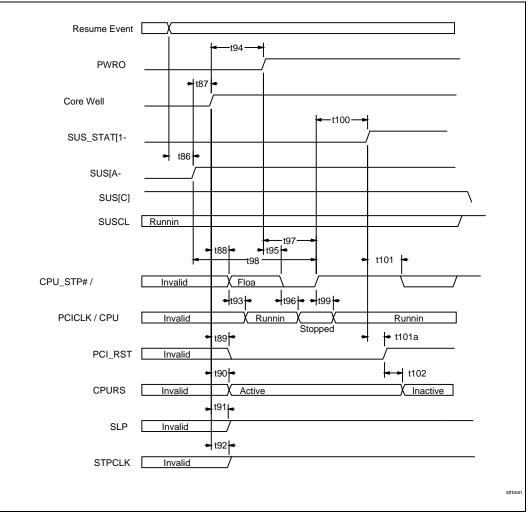

| 11.4.3.9. Power On Suspend to On Timing (With a Full System Reset)                   | 248 |

| 11.4.3.10. System Transition From Power On Suspend to On (With Only Processor Reset) | 250 |

| 11.4.3.11. Power On Suspend to On Timing (With No Resets)                            |     |

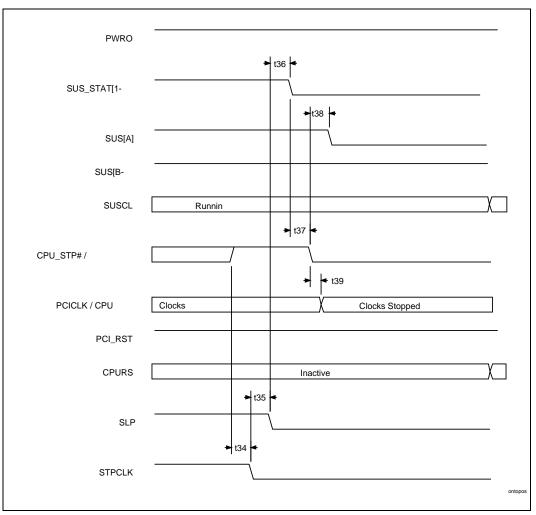

| 11.4.3.12. On State to Suspend to RAM State Timing                                   |     |

| 11.4.3.13. Suspend-To-RAM to On Timing (With Full System Reset)                      |     |

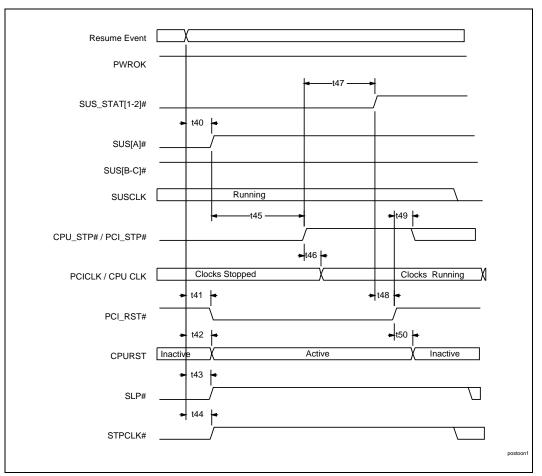

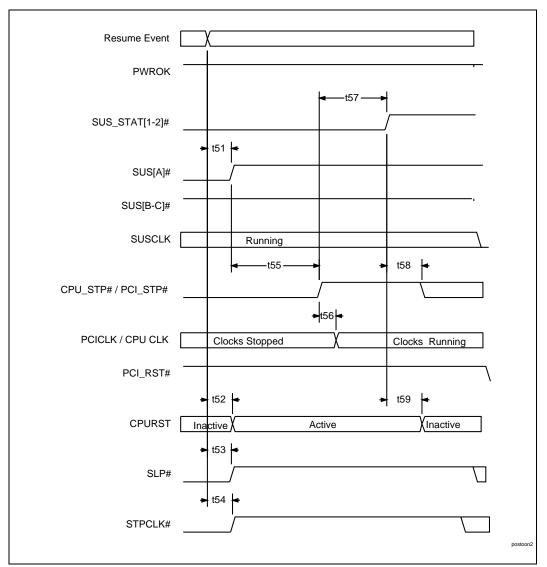

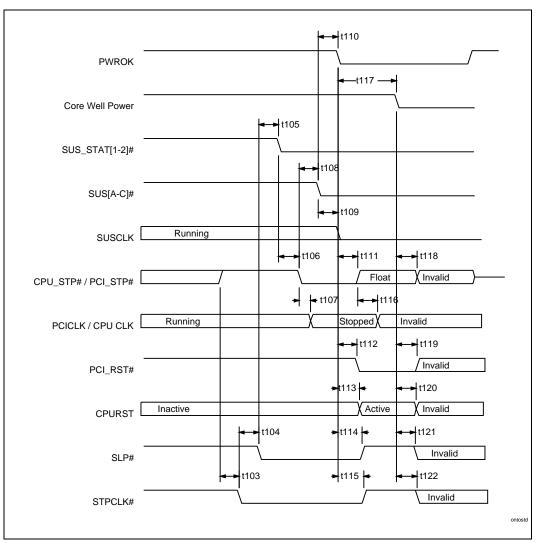

| 11.4.3.14. On State to Suspend to Disk/Soft Off State Timings                        |     |

| 11.4.3.15. Suspend-To-Disk to On (With Full System Reset)                            |     |

| 11.4.4. SHADOW REGISTERS                                                             | 262 |

| 11.5. System Management                                                              | 266 |

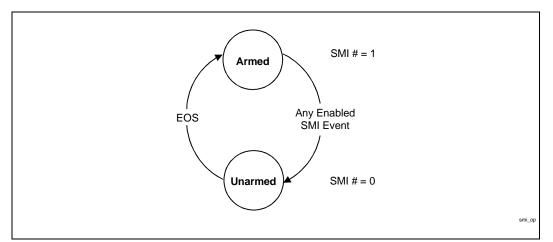

| 11.5.1. SMI OPERATION                                                                |     |

| 11.5.2. SMI# GENERATION EVENTS                                                       | -   |

| 11.5.3. GLOBAL STANDBY TIMER OPERATION                                               |     |

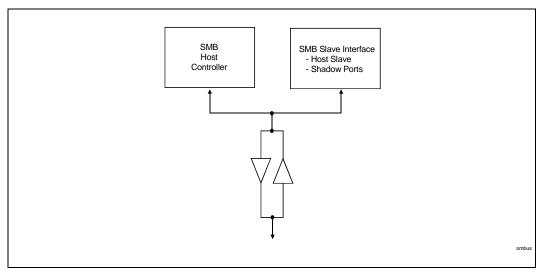

| 11.5.4. SMBUS FUNCTIONAL DESCRIPTION                                                 | -   |

| 11.5.4.1. SMBus Host Interface                                                       | -   |

| 11.5.4.2. SMBus Slave Interface                                                      |     |

| 11.6. ACPI Support                                                                   |     |

| 11.6.1. SCI GENERATION                                                               |     |

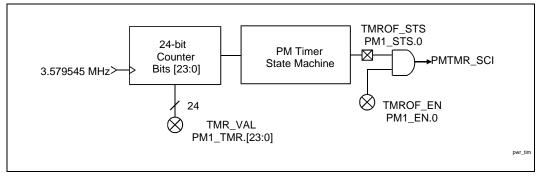

| 11.6.2. POWER MANAGEMENT TIMER                                                       |     |

| 11.6.3. GLOBAL LOCK                                                                  | 273 |

| 12. ELECTRICAL TIMING SPECIFICATIONS                                                 | 274 |

# intط،

## Extended Temperature 82371EB (PIIX4E) Datasheet

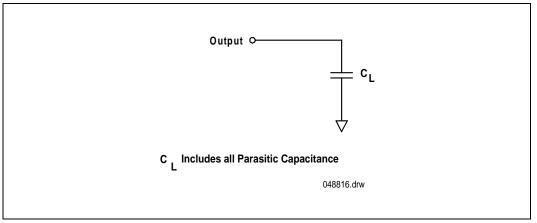

| 12.1. Electrical Characteristics                               | 274 |

|----------------------------------------------------------------|-----|

| 12.1.1. Absolute Maximum Ratings                               | 274 |

| 12.1.2. D.C. Characteristics                                   | 275 |

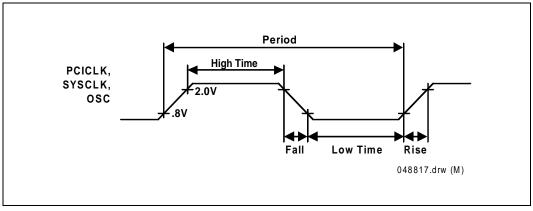

| 12.1.3. A.C. Characteristics                                   | 278 |

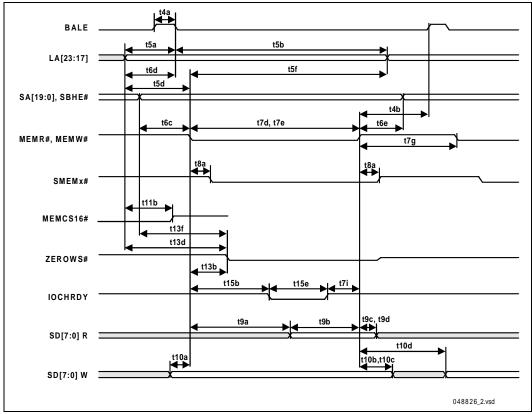

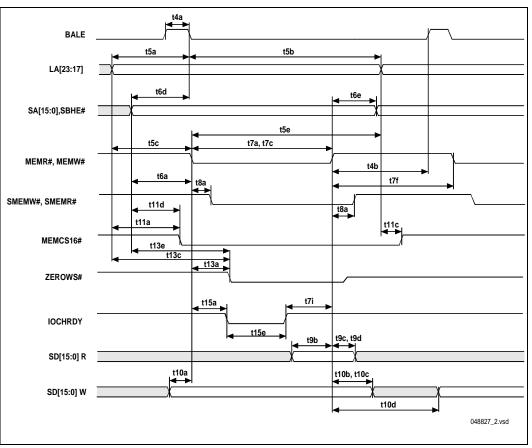

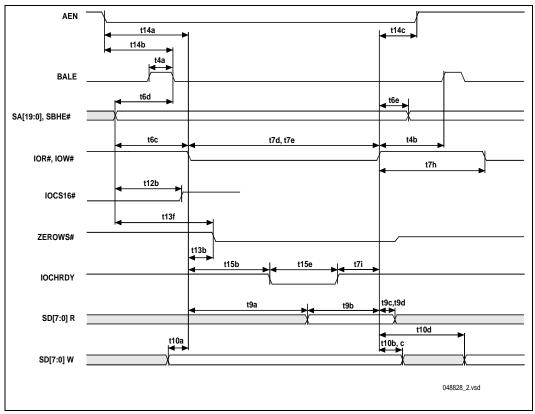

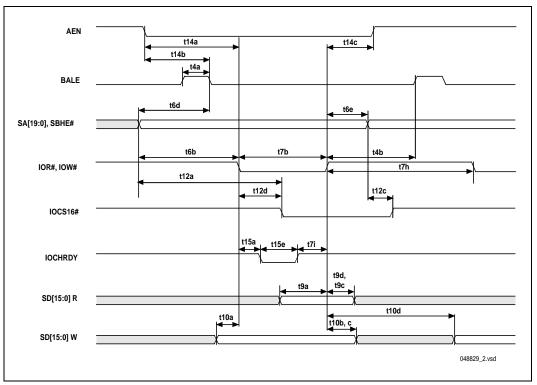

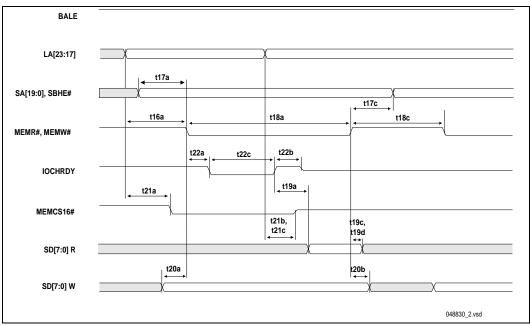

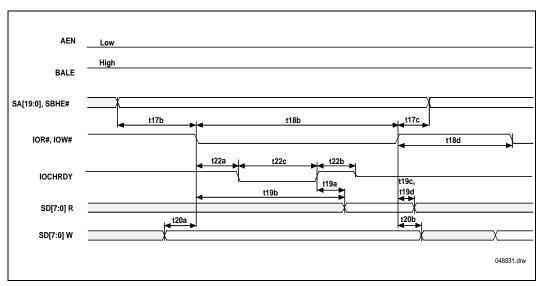

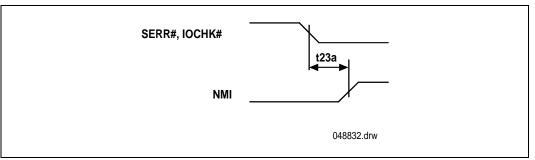

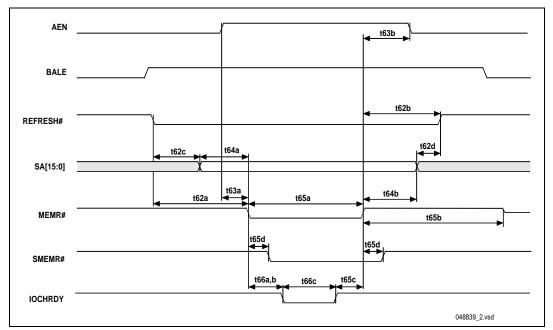

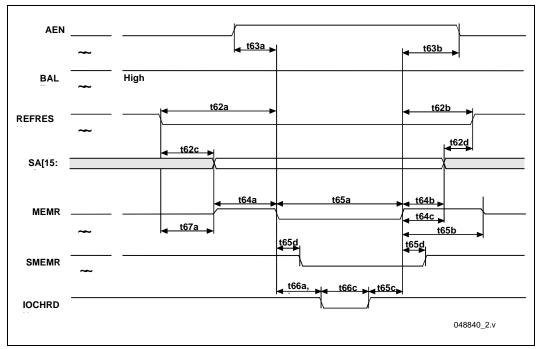

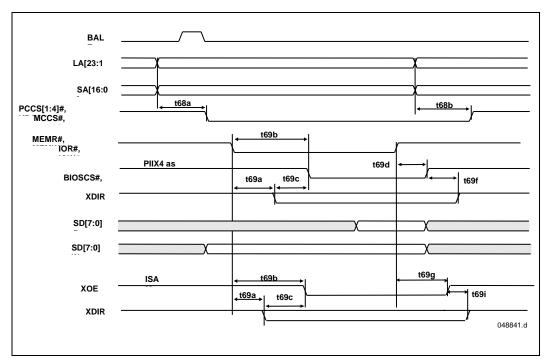

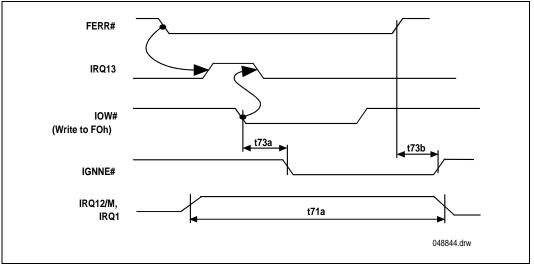

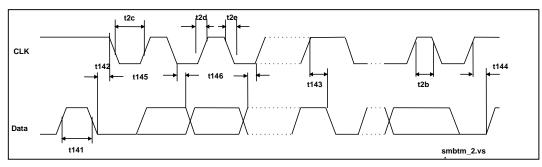

| 12.1.4. Clock, Reset, ISA Bus, X-Bus, and Host Timing Diagrams | 297 |

| 12.1.5. PCI Timing Diagrams                                    | 315 |

| 12.1.6. IDE Timing Diagrams                                    | 317 |

| 12.1.7. USB Timing Diagrams                                    | 318 |

| 12.1.8. IOAPIC Timing Diagrams                                 | 319 |

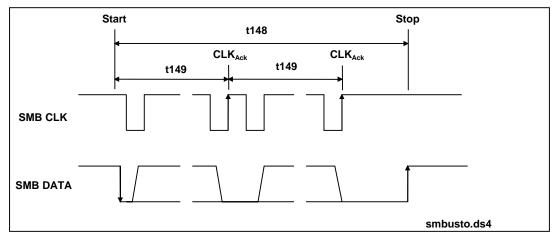

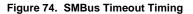

| 12.1.9.SMBus Timing Diagrams                                   | 320 |

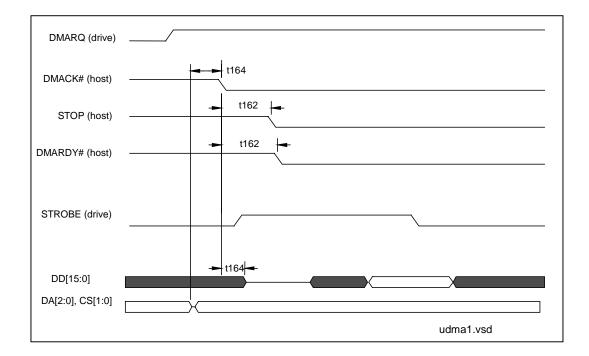

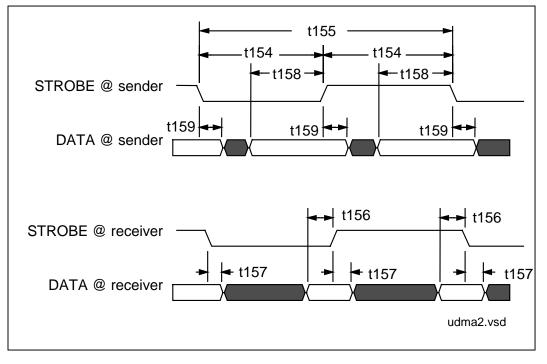

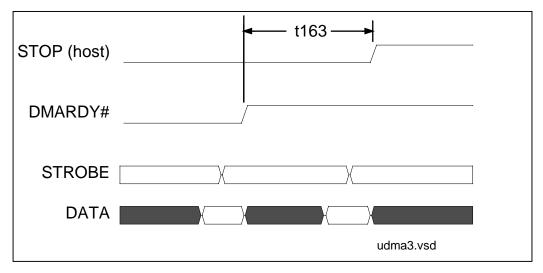

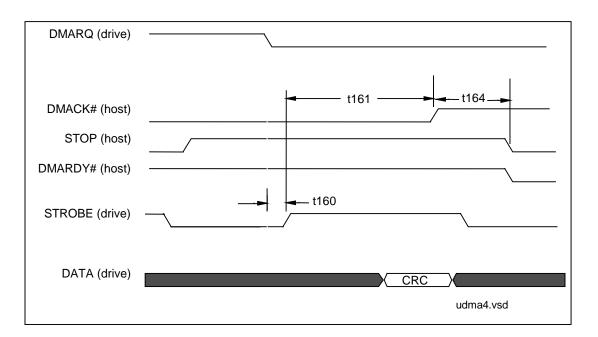

| 12.1.10. Ultra DMA/33 Timing Diagrams                          | 321 |

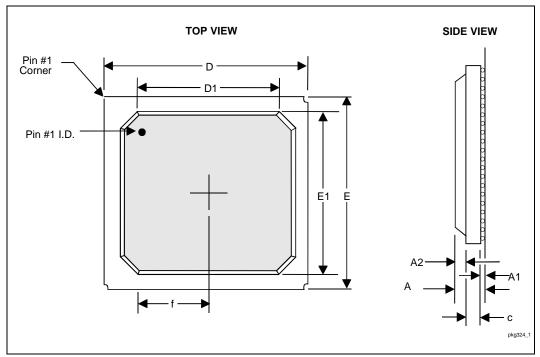

| 13. 0. PINOUT INFORMATION                                      | 324 |

| 14. 0. PIIX4E PACKAGE INFORMATION                              | 328 |

| 15. 0. TESTABILITY                                             |     |

| 15.1. Test Mode Description                                    |     |

| 15.2. Tri-state Mode                                           |     |

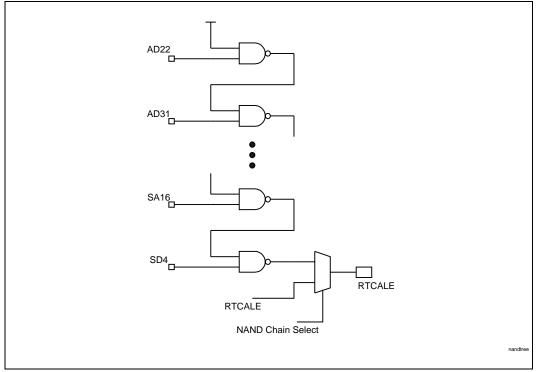

| 15.3. NAND Tree Mode                                           |     |

### **1.0. ARCHITECTURAL OVERVIEW**

The 82371EB PCI ISA IDE Xcelerator (PIIX4E) is a multi-function PCI device implementing a PCI-to-ISA bridge function, a PCI IDE function, a Universal Serial Bus host/hub function, and an Enhanced Power Management function. As a PCI-to-ISA bridge, PIIX4E integrates many common I/O functions found in ISA-based PC systems—two 82C37 DMA Controllers, two 82C59 Interrupt Controllers, an 82C54 Timer/Counter, and a Real Time Clock. In addition to compatible transfers, each DMA channel supports Type F transfers. PIIX4E also contains full support for both PC/PCI and Distributed DMA protocols implementing PCI-based DMA. The Interrupt Controller has Edge or Level sensitive programmable inputs and fully supports the use of an external I/O Advanced Programmable Interrupt Controller (APIC) and Serial Interrupts. Chip select decoding is provided for BIOS, Real Time Clock, Keyboard Controller, second external microcontroller, as well as two Programmable Chip Selects. PIIX4E provides full Plug and Play compatibility. PIIX4E can be configured as a Subtractive Decode bridge or as a Positive Decode bridge. This allows the use of a subtractive decode PCI-to-PCI bridge such as the Intel 380FB PCIset which implements a PCI/ISA docking station environment.

PIIX4E supports two IDE connectors for up to four IDE devices providing an interface for IDE hard disks and CD ROMs. Up to four IDE devices can be supported in Bus Master mode. PIIX4E contains support for "Ultra DMA/33" synchronous DMA compatible devices.

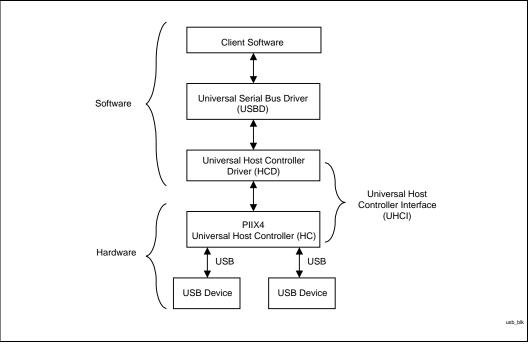

PIIX4E contains a Universal Serial Bus (USB) Host Controller that is Universal Host Controller Interface (UHCI) compatible. The Host Controller's root hub has two programmable USB ports.

PIIX4E supports Enhanced Power Management, including full Clock Control, Device Management for up to 14 devices, and Suspend and Resume logic with Power On Suspend, Suspend to RAM or Suspend to Disk. It fully supports Operating System Directed Power Management via the Advanced Configuration and Power Interface (ACPI) specification. PIIX4E integrates both a System Management Bus (SMBus) Host and Slave interface for serial communication with other devices.

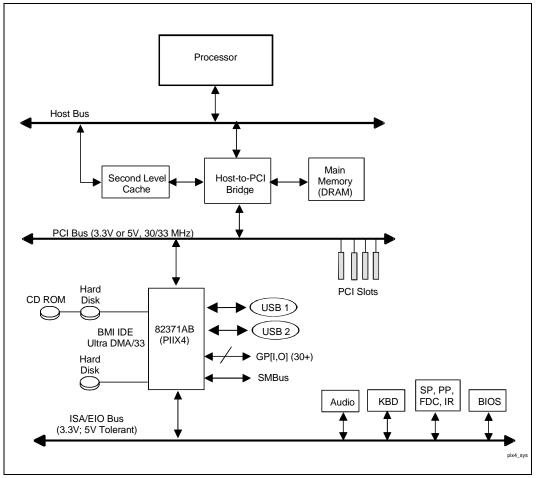

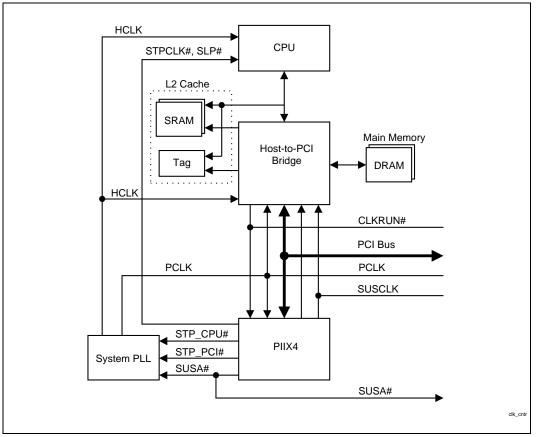

Figure 1 shows an example system block diagram using PIIX4E.

Figure 1. PIIX4E System Block Diagram

PRELIMINARY DRAFT

#### PCI to ISA/EIO Bridge

PIIX4E is compatible with the PCI Rev 2.1 specification, as well as the IEEE 996 specification for the ISA (AT) bus. On PCI, PIIX4E operates as a master for various internal modules, such as the USB controller, DMA controller, IDE bus master controller, distributed DMA masters, and on behalf of ISA masters. PIIX4E operates as a slave for its internal registers or for cycles that are passed to the ISA or EIO buses. All internal registers are positively decoded.

PIIX4E can be configured for a full ISA bus or a subset of the ISA bus called the Extended IO (EIO) bus. The use of the EIO bus allows unused signals to be configured as general purpose inputs and outputs. PIIX4E can directly drive up to five ISA slots without external data or address buffering. It also provides byte-swap logic, I/O recovery support, wait-state generation, and SYSCLK generation. X-Bus chip selects are provided for Keyboard Controller, BIOS, Real Time Clock, a second microcontroller, and two programmable chip selects.

PIIX4E can be configured as either a subtractive decode PCI to ISA bridge or as a positive decode bridge. This gives a system designer the option of placing another subtractive decode bridge in the system (e.g., an Intel 380FB Dock Set).

#### IDE Interface (Bus Master capability and synchronous DMA Mode)

The fast IDE interface supports up to four IDE devices providing an interface for IDE hard disks and CD ROMs. Each IDE device can have independent timings. The IDE interface supports PIO IDE transfers up to 14 Mbytes/sec and Bus Master IDE transfers up to 33 Mbytes/sec. It does not consume any ISA DMA resources. The IDE interface integrates 16x32-bit buffers for optimal transfers.

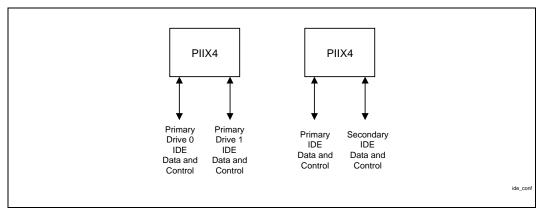

PIIX4E's IDE system contains two independent IDE signal channels. They can be electrically isolated independently, allowing for the implementation of a "glueless" Swap Bay. They can be configured to the standard primary and secondary channels (four devices) or primary drive 0 and primary drive 1 channels (two devices). This allows flexibility in system design and device power management.

#### Compatibility Modules (DMA Controller, Timer/Counters, Interrupt Controller)

The DMA controller incorporates the logic of two 82C37 DMA controllers, with seven independently programmable channels. Channels [0:3] are hardwired to 8-bit, count-by-byte transfers, and channels [5:7] are hardwired to 16-bit, count-by-word transfers. Any two of the seven DMA channels can be programmed to support fast Type-F transfers. The DMA controller also generates the ISA refresh cycles.

The DMA controller supports two separate methods for handling legacy DMA via the PCI bus. The PC/PCI protocol allows PCI-based peripherals to initiate DMA cycles by encoding requests and grants via three PC/PCI REQ#/GNT# pairs. The second method, Distributed DMA, allows reads and writes to 82C37 registers to be distributed to other PCI devices. The two methods can be enabled concurrently. The serial interrupt scheme typically associated with Distributed DMA is also supported.

The timer/counter block contains three counters that are equivalent in function to those found in one 82C54 programmable interval timer. These three counters are combined to provide the system timer function, refresh request, and speaker tone. The 14.31818-MHz oscillator input provides the clock source for these three counters.

PIIX4E provides an ISA-Compatible interrupt controller that incorporates the functionality of two 82C59 interrupt controllers. The two interrupt controllers are cascaded so that 14 external and two internal interrupts are possible. In addition, PIIX4E supports a serial interrupt scheme. PIIX4E provides full support for the use of an external IO APIC.

All registers in these modules can be read and restored. This is required to save and restore system state after power has been removed and restored to the circuit.

#### Enhanced Universal Serial Bus (USB) Controller

The PIIX4E USB controller provides enhanced support for the Universal Host Controller Interface (UHCI). This includes support that allows legacy software to use a USB-based keyboard and mouse.

#### RTC

PIIX4E contains a Motorola\* MC146818A-compatible real-time clock with 256 bytes of battery-backed RAM. The real-time clock performs two key functions: keeping track of the time of day and storing system data, even when the system is powered down. The RTC operates on a 32.768-kHz crystal and a separate 3V lithium battery that provides up to 7 years of protection.

The RTC also supports two lockable memory ranges. By setting bits in the configuration space, two 8-byte ranges can be locked to read and write accesses. This prevents unauthorized reading of passwords or other system security information.

The RTC also supports a date alarm that allows for scheduling a wake up event up to 30 days in advance, rather than just 24 hours in advance.

#### **GPIO and Chip Selects**

Various general purpose inputs and outputs are provided for custom system design. The number of inputs and outputs varies depending on PIIX4E configuration. Two programmable chip selects are provided which allow the designer to place devices on the X-Bus without the need for external decode logic.

#### Pentium® and Pentium® II Processor Interface

The PIIX4E CPU interface allows connection to all Pentium and Pentium II processors. The Sleep mode for the Pentium II processors is also supported.

#### **Enhanced Power Management**

PIIX4E's power management functions include enhanced clock control, local and global monitoring support for 14 individual devices, and various low-power (suspend) states, such as Power-On Suspend, Suspend-to-DRAM, and Suspend-to-Disk. A hardware-based thermal management circuit permits software-independent entrance to low-power states. PIIX4E has dedicated pins to monitor various external events (e.g., interfaces to a notebook lid, suspend/resume button, battery low indicators, etc.). PIIX4E contains full support for the Advanced Configuration and Power Interface (ACPI) Specification.

#### System Management Bus (SMBus)

PIIX4E contains a SMBus Host interface that allows the CPU to communicate with SMBus slaves and a SMBus Slave interface that allows external masters to activate power management events.

#### Configurability

PIIX4E provides a wide range of system configuration options. This includes full 16-bit I/O decode on internal modules, dynamic disable on all the internal modules, various peripheral decode options, and many options on system configuration.

PRELIMINARY DRAFT

### 2.0. SIGNAL DESCRIPTION

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signal. The term assert, or assertion indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.

Certain signals have different functions, depending on the configuration programmed in the PCI configuration space. The signal whose function is being described is in **bold** font. Some of the signals are multiplexed with General Purpose Inputs and Outputs. The default configuration and control bits for each are described in Table 1 and Table 2.

Each output signal description includes the value of the signal **During Reset**, **After Reset**, and **During POS**. **During Reset** refers to when the PCIRST# signal is asserted. **After Reset** is immediately after negation of PCIRST# and the signal may change value anytime thereafter. The term **High-Z** means tri-stated. The term **Undefined** means the signal could be high, low, tri-stated, or in some in-between level. Some of the power management signals are reset with the RSMRST# input signal. The functionality of these signals during RSMRST# assertion is described in the *Suspend/Resume and Power Plane Control* section.

The I/O buffer types are shown below:

| Buffer Type | Description                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------|

| I           | input only signal                                                                                                    |

| 0           | totem pole output                                                                                                    |

| I/O         | bi-direction, tri-state input/output pin                                                                             |

| s/t/s       | sustained tri-state                                                                                                  |

| OD          | open drain                                                                                                           |

| I/OD        | input/open drain output is a standard input buffer with an open drain output                                         |

| V           | This is not a standard signal. It is a power supply pin.                                                             |

| 3.3V/2.5V   | Indicates the buffer is $3.3V$ or $2.5V$ only, depending on the voltage ( $3.3V$ or $2.5V$ ) connected to VccX pins. |

| 3.3V/5V     | Indicates that the output is 3.3V and input is 3.3V receiver with 5V tolerance.                                      |

| 5V          | Indicates 3.3V receiver with 5V tolerance.                                                                           |

All 3V output signals can drive 5V TTL inputs. Most of the 3V input signals are 5V tolerant. The 3V input signals which are powered via the RTC or Suspend power planes should not exceed their power supply voltage (see *Power Planes* chapter for additional information). The open drain (OD) CPU interface signals should be pulled up to the CPU interface signal voltage.

## 2.1. PIIX4E Signals

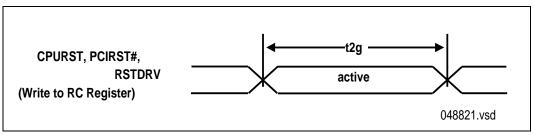

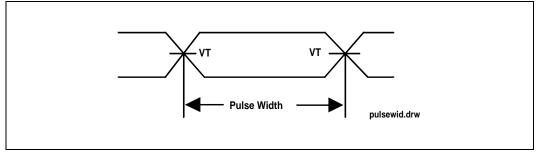

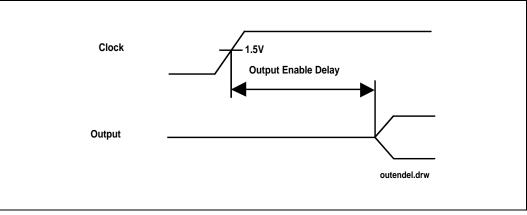

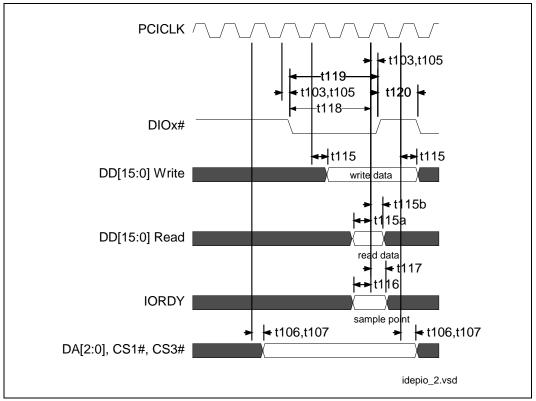

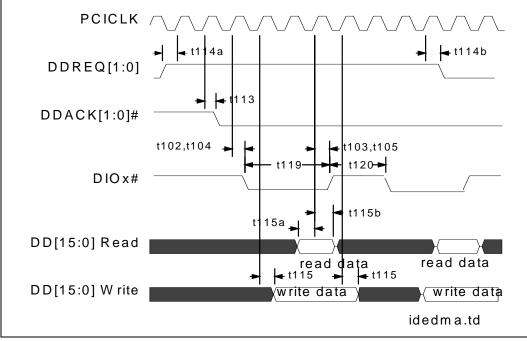

### 2.1.1. PCI BUS INTERFACE