**DGD0506**

HIGH FREQUENCY HALF-BRIDGE GATE DRIVER WITH PROGRAMMABLE DEADTIME IN DFN3030-10

## Description

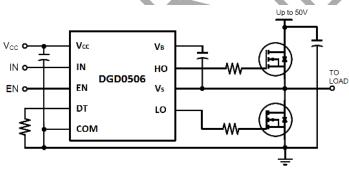

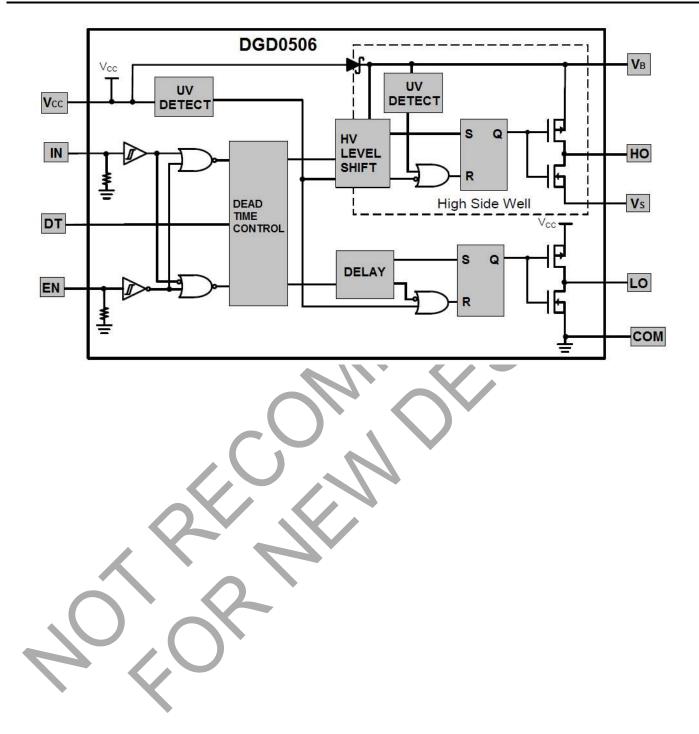

The DGD0506 is a high-frequency half-bridge gate driver capable of driving N-channel MOSFETs in a half-bridge configuration. The floating high-side driver is rated up to 50V.

The DGD0506 logic inputs are compatible with standard TTL and CMOS levels (down to 3.3V) to interface easily with MCUs. UVLO for high-side and low-side will protect a MOSFET with loss of supply. To protect MOSFETs, cross conduction prevention logic prevents the HO and LO outputs being on at the same time.

Fast and well-matched propagation delays allow a higher switching frequency, enabling a smaller, more compact power switching design using smaller associated components. The DGD0506 is offered in the V-DFN3030-10 package and operates over an extended -40°C to +125°C temperature range.

# Applications

- **DC-DC Converters**

- Motor Controls

- Battery Powered Hand Tools

- eCig Devices

- **Class-D Power Amplifiers**

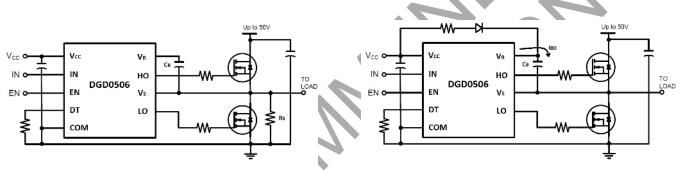

**Typical Configuration**

### Features

- 50V Floating High-Side Driver

- Drives Two N-Channel MOSFETs in a Half-Bridge Configuration

- 1.25A Source / 2.0A Sink Output Current Capability

- Internal Bootstrap Schottky Diode Included

- Undervoltage Lockout for High-Side and Low-Side Drivers

- Programmable Deadtime to Protect MOSFETs

- Logic Input (IN and EN) 3.3V Capability

- Ultra Low Standby Currents (<1µA)

- Extended Temperature Range: -40°C to +125°C

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

https://www.diodes.com/guality/product-definitions/

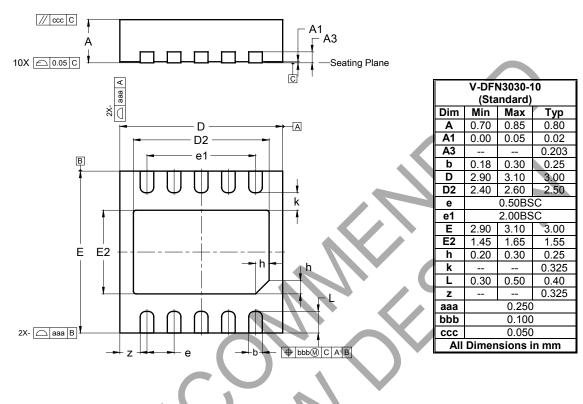

# **Mechanical Data**

- Case: V-DFN3030-10 (Standard)

- Case material: Molded Plastic. "Green" Molding Compound. UL Flammability Classification Rating 94V-0 Moisture Sensitivity: Level 3 per J-STD-020

- Terminals: Finish Matte Tin Finish

- Solderable per MIL-STD-202, Method 208 @3 Weight: 0.017 grams (Approximate)

Bottom View

V-DFN3030-10

### Ordering Information (Note 4)

| Product     | Marking | Reel Size (inches) | Tape Width (mm) | Quantity per Reel |

|-------------|---------|--------------------|-----------------|-------------------|

| DGD0506FN-7 | DGD0506 | 7                  | 8               | 3,000             |

1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant. Notes:

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free

3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

4. For packaging details, go to our website at https://www.diodes.com/design/support/packaging/diodes-packaging/.

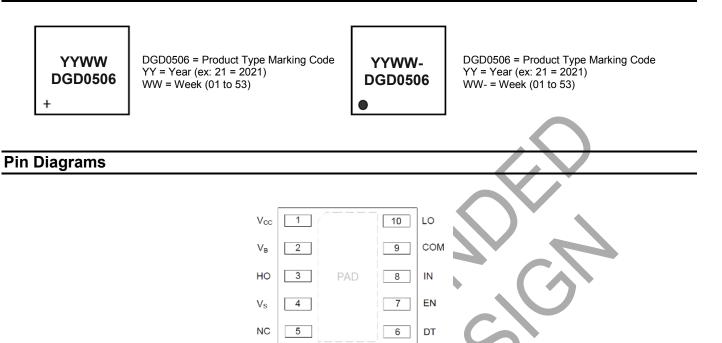

# **Marking Information**

# **Pin Descriptions**

| Pin Number | Pin Name        | Function                                                                                 |

|------------|-----------------|------------------------------------------------------------------------------------------|

| 1          | V <sub>cc</sub> | Low-Side and Logic Supply                                                                |

| 2          | VB              | High-Side Floating Supply                                                                |

| 3          | НО              | High-Side Gate Drive Output                                                              |

| 4          | Vs              | High-Side Floating Supply Return                                                         |

| 5          | NC              | No Connect (No Internal Connection)                                                      |

| 6          | DT              | Deadtime Control                                                                         |

| 7          | EN              | Logic Input Enable, a Logic Low turns off Gate Driver                                    |

| 8          | IN              | Logic Input for High-Side and Low-Side Gate Driver Outputs (HO and LO), in Phase with HO |

| 9          | СОМ             | Low-Side and Logic Return                                                                |

| 10         | LO              | Low-Side Gate Drive Output                                                               |

| PAD        | Substrate       | Connect to COM on PCB                                                                    |

# **Functional Block Diagram**

## Absolute Maximum Ratings (@ T<sub>A</sub> = +25°C, unless otherwise specified.)

| Characteristic                             | Symbol               | Value                                      | Unit |  |

|--------------------------------------------|----------------------|--------------------------------------------|------|--|

| High-Side Floating Positive Supply Voltage | V <sub>B</sub>       | -0.3 to +50                                | V    |  |

| High-Side Floating Negative Supply Voltage | Vs                   | V <sub>B</sub> -14 to V <sub>B</sub> +0.3  | V    |  |

| High-Side Floating Output Voltage          | V <sub>HO</sub>      | V <sub>S</sub> -0.3 to V <sub>B</sub> +0.3 | V    |  |

| Offset Supply Voltage Transient            | dV <sub>S</sub> / dt | 50                                         | V/ns |  |

| Logic and Low-Side Fixed Supply Voltage    | V <sub>CC</sub>      | -0.3 to +15                                | V    |  |

| Low-Side Output Voltage                    | V <sub>LO</sub>      | -0.3 to V <sub>CC</sub> +0.3               | V    |  |

| Logic Input Voltage (IN and EN)            | V <sub>IN</sub>      | -0.3 to +15                                | V    |  |

| Bootstrap Diode Current (Pulsed <10µs)     | I <sub>BD</sub>      | 500                                        | mA   |  |

## **Thermal Characteristics** (@ T<sub>A</sub> = +25°C, unless otherwise specified.)

| Characteristic                                    | Symbol           | Value       | Unit |

|---------------------------------------------------|------------------|-------------|------|

| Power Dissipation Linear Derating Factor (Note 5) | PD               | 0.4         | W    |

| Thermal Resistance, Junction to Ambient (Note 5)  | R <sub>0JA</sub> | 64          | °C/W |

| Thermal Resistance, Junction to Case (Note 5)     | Rejc             | 42          | °C/W |

| Operating Temperature                             | TJ               | +150        |      |

| Lead Temperature (Soldering, 10s)                 | TL               | +300        | °C   |

| Storage Temperature Range                         | Tstg             | -55 to +150 |      |

Note: 5. When mounted on a standard JEDEC 2-layer FR-4 board.

# **Recommended Operating Conditions**

| Parameter                                | Symbol          | Min                | Мах                 | Unit |

|------------------------------------------|-----------------|--------------------|---------------------|------|

| High-Side Floating Supply                | VB              | V <sub>S</sub> + 8 | V <sub>S</sub> + 14 | V    |

| High-Side Floating Supply Offset Voltage | Vs              | (Note 6)           | 50 (Note 7)         | V    |

| High-Side Floating Output Voltage        | V <sub>HO</sub> | Vs                 | VB                  | V    |

| Logic and Low Side Fixed Supply Voltage  | V <sub>CC</sub> | 8                  | 14                  | V    |

| Low-Side Output Voltage                  | V <sub>LO</sub> | 0                  | V <sub>CC</sub>     | V    |

| Logic Input Voltage (IN and EN)          | VIN             | 0                  | 5                   | V    |

| Bootstrap Diode Current (Pulsed <10µs)   | I <sub>BD</sub> | -                  | 400                 | mA   |

| Ambient Temperature                      | TA              | -40                | +125                | °C   |

Notes:

6. Logic operation for  $V_{\rm S}$  of -5V to +50V. 7. Provided  $V_{\rm B}$  doesn't exceed absolute maximum rating of 50V.

| Parameter                                                     | Symbol             | Min | Тур  | Мах  | Unit | Condition                                              |

|---------------------------------------------------------------|--------------------|-----|------|------|------|--------------------------------------------------------|

| Logic "1" Input Voltage                                       | VIH                | 2.4 | -    | _    | V    | -                                                      |

| Logic "0" Input Voltage                                       | VIL                | _   | _    | 0.8  | V    | -                                                      |

| Enable Logic "1" Input Voltage                                | V <sub>ENIH</sub>  | 1.5 | _    | _    | V    | -                                                      |

| Enable Logic "0" Input Voltage                                | VENIL              | -   | _    | 0.7  | V    | -                                                      |

| Input Voltage Hysteresis                                      | VINHYS             | -   | 0.6  | _    | V    | -                                                      |

| High Level Output Voltage, V <sub>BIAS</sub> - V <sub>O</sub> | V <sub>OH</sub>    | -   | 0.45 | 0.6  | V    | I <sub>O+</sub> = 100mA                                |

| Low Level Output Voltage, V <sub>O</sub>                      | Vol                | -   | 0.15 | 0.22 | V    | I <sub>O-</sub> = 100mA                                |

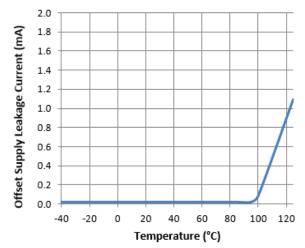

| Offset Supply Leakage Current                                 | I <sub>LK</sub>    | -   | 10   | 50   | μA   | $V_B = V_S = 50V$                                      |

| V <sub>CC</sub> Shutdown Supply Current                       | ICCSD              | -   | 0    | 1    | μA   | V <sub>IN</sub> = 0V or 5V, V <sub>EN</sub> = 0V       |

| V <sub>CC</sub> Quiescent Supply Current                      | ICCQ               | -   | 0.32 | 0.5  | mA   | V <sub>IN</sub> = 0V or 5V,<br>R <sub>DT</sub> = 100kΩ |

| V <sub>CC</sub> Operating Supply Current                      | ICCOP              | -   | 2.1  | -    | mA   | fs = 500kHz                                            |

| V <sub>BS</sub> Quiescent Supply Current                      | I <sub>BSQ</sub>   | -   | 62   | 100  | μA   | V <sub>IN</sub> = 0V or 5V                             |

| V <sub>BS</sub> Operating Supply Current                      | IBSOP              | -   | 1.1  |      | mA   | fs = 500kHz                                            |

| Logic "1" Input Bias Current                                  | I <sub>IN+</sub>   | -   | 25   | 60   | μA   | V <sub>IN</sub> = 5V                                   |

| Logic "0" Input Bias Current                                  | I <sub>IN-</sub>   | -   | 0    | 1    | μA   | V <sub>IN</sub> = 0V                                   |

| V <sub>BS</sub> Supply Undervoltage Positive Going Threshold  | V <sub>BSUV+</sub> | 5.9 | 6.9  | 7.9  | V    | -                                                      |

| V <sub>BS</sub> Supply Undervoltage Negative Going Threshold  | V <sub>BSUV-</sub> | 5.6 | 6.6  | 7.6  | v    | -                                                      |

| V <sub>CC</sub> Supply Undervoltage Positive Going Threshold  | V <sub>CCUV+</sub> | 5.9 | 6.9  | 7.9  | V    | -                                                      |

| V <sub>CC</sub> Supply Undervoltage Negative Going Threshold  | V <sub>CCUV-</sub> | 5.6 | 6.6  | 7.6  | V    | -                                                      |

| Output High Short-Circuit Pulsed Current                      | l <sub>O+</sub>    | 0.9 | 1.25 |      | А    | $V_0 = 0V$ , PW $\leq 10\mu s$                         |

| Output Low Short-Circuit Pulsed Current                       | lo-                | 1.5 | 2.0  | -    | А    | V <sub>O</sub> = 15V, PW ≤ 10µs                        |

| Forward Voltage of Bootstrap Diode                            | V <sub>F1</sub>    | -   | 0.27 | _    | V    | I <sub>F</sub> = 100μA                                 |

| Forward Voltage of Bootstrap Diode                            | V <sub>F2</sub>    | -   | 0.8  | _    | V    | I <sub>F</sub> = 100mA, PW ≤ 10ms                      |

# DC Electrical Characteristics (V<sub>CC</sub> = V<sub>BS</sub> = 12V, COM = V<sub>S</sub> = 0V, @ T<sub>A</sub> = +25°C, unless otherwise specified.) (Note 8)

Note: 8. The V<sub>IN</sub> and I<sub>IN</sub> parameters are applicable to the two logic pins: IN and EN. The V<sub>O</sub> and I<sub>O</sub> parameters are applicable to the respective output pins: HO and LO.

# AC Electrical Characteristics (V<sub>CC</sub> = V<sub>BS</sub> = 12V, COM = V<sub>S</sub> = 0V, C<sub>L</sub> = 1000pF, @ T<sub>A</sub> = +25°C, unless otherwise specified.)

| Parameter                                               | Symbol           | Min | Тур | Max | Unit | Condition               |

|---------------------------------------------------------|------------------|-----|-----|-----|------|-------------------------|

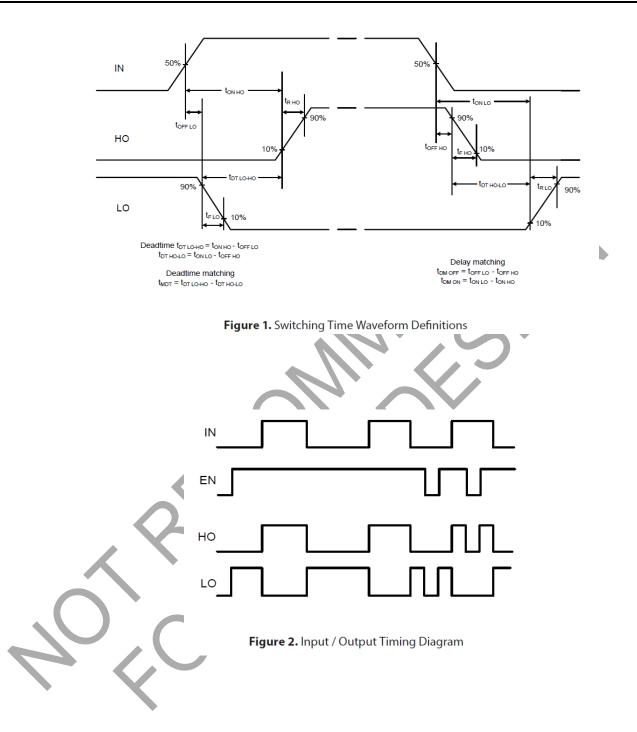

| Turn-on Propagation Delay, HO & LO                      | t <sub>ON</sub>  | 65  | 96  | 125 | ns   | $R_{DT} = 10k\Omega$    |

| Tum-on Propagation Delay, HO & LO                       |                  | 350 | 463 | 580 | ns   | R <sub>DT</sub> = 100kΩ |

| Turn-off Propagation Delay, HO & LO                     | t <sub>OFF</sub> | -   | 22  | 56  | ns   | -                       |

| Turn-on Rise Time                                       | t <sub>R</sub>   | -   | 17  | 35  | ns   | -                       |

| Turn-off Fall Time                                      | tF               | -   | 12  | 25  | ns   | -                       |

| Delay Matching                                          | t <sub>DM</sub>  | -   | -   | 50  | ns   | -                       |

|                                                         | t <sub>DT</sub>  | 40  | 70  | 100 | ns   | R <sub>DT</sub> = 10kΩ  |

| Deadtime: t <sub>DT LO-HO</sub> & t <sub>DT HO-LO</sub> |                  | 300 | 430 | 560 | ns   | R <sub>DT</sub> = 100kΩ |

| Deadtime Matching                                       | t <sub>MDT</sub> | -   | _   | 50  | ns   | R <sub>DT</sub> = 100kΩ |

# Timing Waveforms

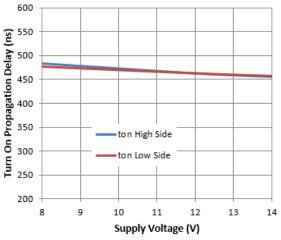

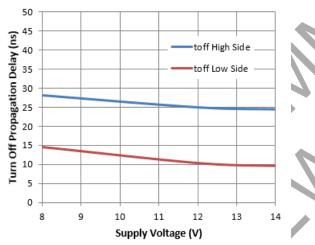

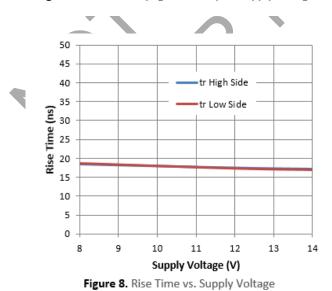

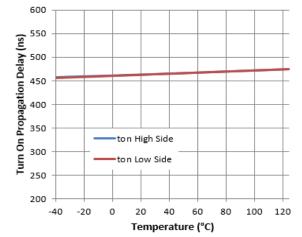

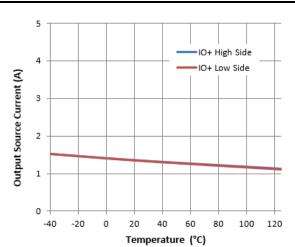

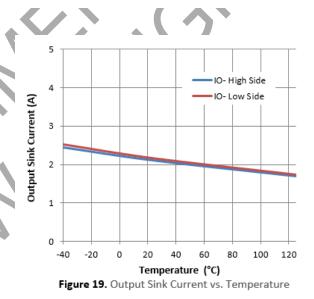

# Typical Performance Characteristics (V<sub>CC</sub> = 12V, @ T<sub>A</sub> = +25°C, unless otherwise specified.)

Figure 4. Turn-on Propagation Delay vs. Supply Voltage

Figure 6. Turn-off Propagation Delay vs. Supply Voltage

Figure 5. Turn-on Propagation Delay vs. Temperature

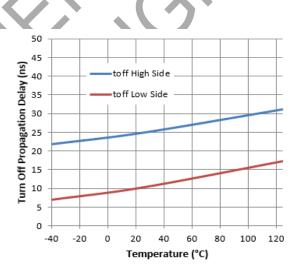

Figure 7. Turn-off Propagation Delay vs. Temperature

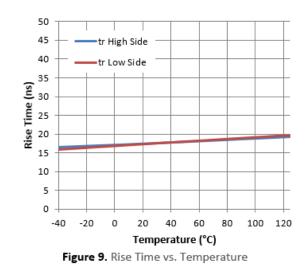

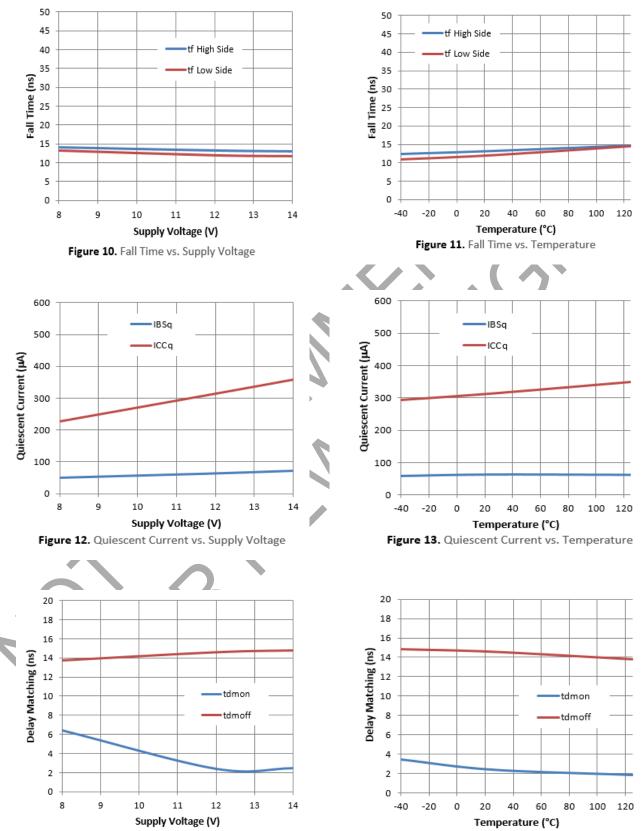

# Typical Performance Characteristics (continued)

Figure 14. Delay Matching vs. Supply Voltage

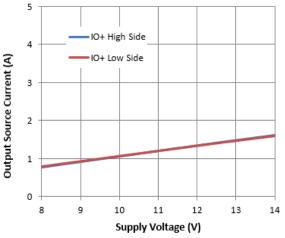

# Typical Performance Characteristics (continued)

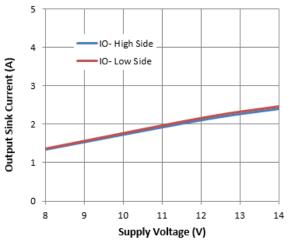

Figure 16. Output Source Current vs. Supply Voltage

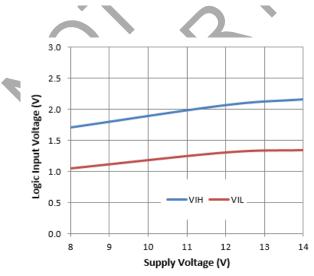

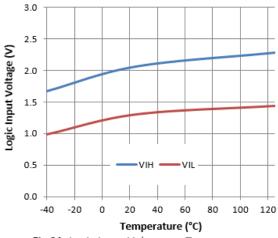

Fig 20. Logic Input Voltage vs. Supply Voltage

Fig 21. Logic Input Voltage vs. Temperature

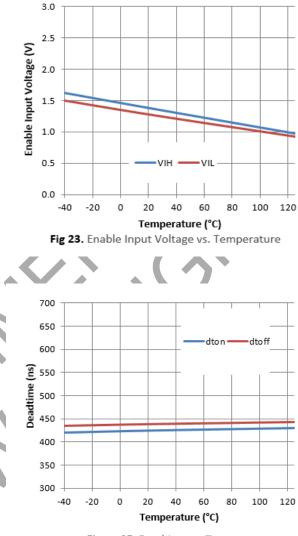

# Typical Performance Characteristics (continued)

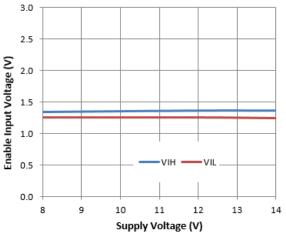

Fig 22. Enable Input Voltage vs. Supply Voltage

VCC UVLO (V) 7.5 7 6.5 6 5.5 5 -40 -20 0 20 40 60 80 100 120 Temperature (°C)

Figure 26. VCC UVLO vs. Temperature

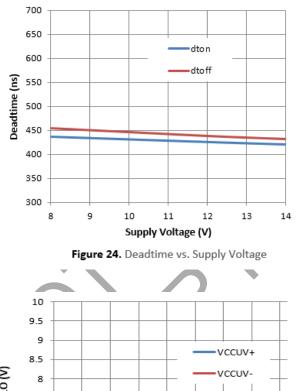

Figure 25. Deadtime vs. Temperature

Figure 27. Offset Supply Leakage Current vs. Temperature

## **Application Information**

#### **Bootstrap Capacitor Selection**

The capacitance of the bootstrap capacitor should be high enough to provide the charge required by the gate of the high side MOSFET with only a minimal loss of voltage across it. As a general guideline, it is recommended to make sure the charge stored by the bootstrap capacitor is about 50 times more than the required gate charge at operating  $V_{CC}$  (usually about 10V to 12V).

The formula to calculate the change in  $V_{BS}$  to provide a certain amount of gate charge is shown below; Q = C \* V where Q is the gate charge required by the external MOSFET to raise its gate voltage to 10V. C is the bootstrap capacitance and V is the voltage drop across the Vbs.

Example: To switch a high side MOSFET that requires 20nC of gate charge to raise its gate voltage to 10V, the capacitor size can be calculated as below;

$Q_{G(MOSFET)} = C_{(BOOTSTRAP)} * \Delta V_{BS};$

$\Delta V_{BS}$  = voltage drop acorss the bootstrap capacitor while providing the required gate charge

In this example, let's say the acceptable  $\Delta V_{BS}$  is 200mV.

The required bootstrap capacitor for the job is;

$C_{(BOOTSTRAP)} = Q_{G(MOSFET)} / \Delta V_{BS} = 20nC/200mV = 100nF$

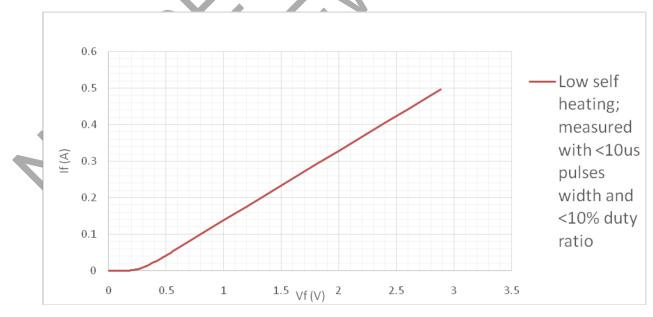

#### **Bootstrap Diode Current**

The DGD0506 comes with an integrated bootstrap Schottky diode. The forward characteristics of the diode is shown in the figure 28. The maximum recommended operating current is 400mA pulsed. Under steady state conditions the only current flowing through the internal diode is the charge current required by the high-side MOSFET's gate capacitance, however, it is important to cover applications where the inrush current exceeds this rating. In such applications to limit the current flowing through the internal diode to the recommended value, two techniques are suggested as shown in figures 29 and 30.

Figure 28. DGD0506 'Internal Diode + Internal Resistor' V<sub>F</sub> vs. I<sub>F</sub>

### Application Information (continued)

#### Pre-Bias Resistor between Vs and COM

This technique eliminates the inrush current, altogether, by pre-charging the capacitor to a value close to  $V_{CC}$  before the DGD0506 is enabled and an input signal is applied. By pre-charging the capacitor to  $V_{CC}$  only a small steady state current flows through the internal diode eliminating the need for any external diode. The recommended range for the Rs is  $10k\Omega$  to  $100k\Omega$ .

#### External Diode and Resistor

To enable appropriate current sharing and limit the internal bootstrap current to less than 400mA, a Schottky diode must be used as an external diode. The voltage drop across the external diode and resistor must be limited to 2.4V, to limit the internal diode's current share to <400mA. Hence it is important to choose an appropriate external diode and resistor combination. At any observed inrush current peak, it is important that the combined voltage drop of the external resistor and diode is less than 2.4V.

For internal diode current to be <400mA; (I<sub>INRUSH</sub> \* R<sub>EXT</sub>) + (Vf<sub>EXT</sub> @ I<sub>INRUSH</sub> < 2.4V.

Figure 29. Inrush current is greatly limited by precharging the boost-strap Capacitor through Rs Figure 30. Current into the boost-strap capacitance is shared between the external diode and the internal Diode

## **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

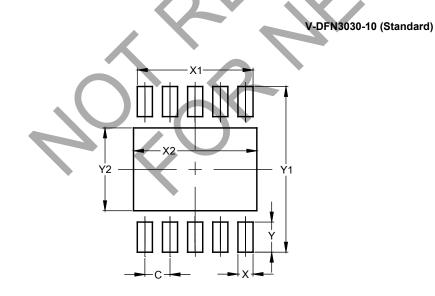

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| С          | 0.500            |

| Х          | 0.300            |

| X1         | 2.300            |

| X2         | 2.600            |

| Y          | 0.600            |

| Y1         | 3.300            |

| Y2         | 1.650            |

### V-DFN3030-10 (Standard)

#### IMPORTANT NOTICE

1. DIODES INCORPORATED AND ITS SUBSIDIARIES ("DIODES") MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes products. Diodes products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of the Diodes products for their intended applications, (c) ensuring their applications, which incorporate Diodes products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

5. Diodes products are provided subject to Diodes Standard Terms and Conditions of Sale (<u>https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/</u>) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

Copyright © 2021 Diodes Incorporated

www.diodes.com