## SG1524B/SG2524B/SG3524B

## Datasheet

# **Regulating Pulse Width Modulator**

July 2018

## Contents

| 1 | Revis       | sion History<br>Revision 2.0     | 1      |

|---|-------------|----------------------------------|--------|

|   | 1.1         | Revision 2.0                     | 1      |

|   | 1.2         | Revision 1.4                     | 1      |

|   | 1.3         | Revision 1.1                     | 1      |

| 2 | Prod        | uct Overview                     | 2      |

|   | 2.1         | Features                         | 2      |

|   | 2.2         | High Reliability Features        | 2      |

|   | 2.3         | Block Diagram                    | 3      |

| 3 | Elect       | rical Specifications             | 4      |

|   | 3.1         | Recommended Operating Conditions |        |

|   | 3.2         | Typical Performance Curves       | 7      |

|   | 3.3         | Absolute Maximum Ratings         | 8      |

| 4 | Pack<br>4.1 | age Information<br>Thermal Data  | 9<br>3 |

| 5 | Orde        | ring Information1                | 4      |

## 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

### 1.1 Revision 2.0

Revision 2.0 was published in July 2018. In revision 2.0 of this document, the format was updated to the latest template. The following is the summary of changes in revision 2.0 of this document

- Corrected a typo in the title of the document.

- Formatting edits were done.

### 1.2 Revision 1.4

Revision 1.4 was published in December 2014. The following is the summary of changes in revision 1.4 of this document.

- Corrected a typo in the Features (see page 2) section.

- Corrected a typo in the Ordering Information (see page 14) section.

### 1.3 Revision 1.1

Revision 1.1 was published in February 1994. It was the first publication of this document.

## 2 Product Overview

The SG1524B is a pulse width modulator for switching power supplies, that gives improved performance over industry standards, like the SG1524. This is a direct pin-for-pin replacement for the earlier device, and combines advanced processing techniques and circuit design to provide improved reference accuracy, and extended common mode range at the error amplifier and current limit inputs. A DC-coupled flip-flop eliminates triggering and glitch problems, and a pulse width modulator data latch prevents edge oscillations. The circuit incorporates true digital shutdown for high speed response, while an under voltage lockout circuit prevents spurious outputs when the supply voltage is too low for stable operation. Full double-pulse suppression logic insures alternating output pulses when the shutdown pin is used for pulse-by-pulse current limiting. SG1524B is specified for operation over the full military ambient temperature range of -55 °C to 125 °C. It is characterized for the industrial range of -25 °C to 85 °C, and is designed for the commercial range of 0 °C to 70 °C.

### 2.1 Features

The main features of SG1524B are as follows.

- 7 V to 40 V operation

- 5 V reference trimmed to ±1%

- 100 Hz to 400 kHz oscillator range

- Excellent external sync capability

- Dual 100 mA output transistors

- Wide current limit common mode range

- DC-coupled toggle flip-flop

- PWM data latch

- Undervoltage lockout

- Full double pulse suppression logic

- 60 V output collectors

### 2.2 High Reliability Features

The high reliability features of SG1524B are as follows.

- Available to MIL-STD-883

- MSC-AMS level "S" processing available

- Available to DSCC-standard microcircuit drawing (SMD)

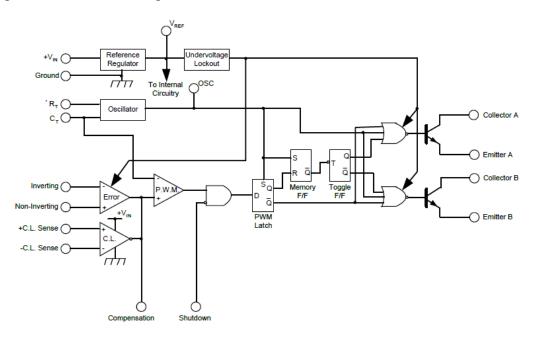

## 2.3 Block Diagram

The following figure shows the block diagram of SG1524B.

### Figure 1 • SG1524B Block Diagram

## **3** Electrical Specifications

This section shows the electrical characteristics of SG1524B/SG2524B/SG3524B. If not specified, these specifications apply over the operating ambient temperatures for SG1524B with  $-55 \degree C \le T_A \le 125 \degree C$ , SG2524B with  $-25 \degree C \le T_A \le 85 \degree C$ , SG3524B with  $0 \degree C \le T_A \le 70 \degree C$ , and  $V_{IN} = 20 V$ . Low duty cycle pulse testing techniques are used, that maintain junction and case temperatures equal to the ambient temperature.

The following table shows the parameters and test conditions of SG1524B/SG2524B/SG3524B.

### **Table 1 • Electrical Characteristics**

| Parameter              | Test Conditions                                | SG1524B/2524B |         |      | SG352 | 4B      |      | Units |

|------------------------|------------------------------------------------|---------------|---------|------|-------|---------|------|-------|

|                        |                                                | Min           | Typical | Max  | Min   | Typical | Max  |       |

| Reference Section      | (I∟ = 0 mA)                                    |               |         |      |       |         |      |       |

| Output voltage         | T <sub>J</sub> = 25 °C                         | 4.95          | 5.00    | 5.05 | 4.90  | 5.00    | 5.10 | V     |

| Line regulation        | V <sub>IN</sub> = 7 V to 40 V                  |               | 3       | 20   |       | 3       | 30   | mV    |

| Load regulation        | IL = 0 mA to 20 mA                             |               | 5       | 30   |       | 5       | 50   | mV    |

| Temperature            | Over operating temperature                     |               | 15      | 50   |       | 15      | 50   | mV    |

| stability <sup>1</sup> | range                                          |               |         |      |       |         |      |       |

| Total output           | Over line, load and                            | 4.90          |         | 5.10 | 4.80  |         | 5.20 | V     |

| voltage range          | temperature                                    |               |         |      |       |         |      |       |

| Short circuit          | Vref-0 V                                       | 25            | 50      | 120  | 25    | 50      | 120  | mA    |

| current                |                                                |               |         |      |       |         |      |       |

| Undervoltage Lock      | out Section                                    |               |         |      |       |         |      |       |

| Threshold              |                                                | 4.3           | 4.5     | 4.7  | 4.2   | 4.5     | 4.9  | V     |

| voltage                |                                                |               |         |      |       |         |      |       |

| Oscillator Section (   | Fosc = 45 kHz, Rτ = 2700 Ω, Cτ = 0.01          | μF)           |         |      |       |         |      |       |

| Initial accuracy       | TJ = 25 °C                                     | 42            | 45      | 48   | 40    | 45      | 50   | kHz   |

| Voltage stability      | V <sub>IN</sub> = 7 V to 40 V                  |               | 0.1     | 1    |       | 0.1     | 1    | %     |

| Temperature            | Over operating range                           |               | 1       | 2    |       | 1       | 2    | %     |

| stability <sup>1</sup> |                                                |               |         |      |       |         |      |       |

| Minimum                | Rτ = 150 kΩ, Cτ = 0.1 μF                       |               | 50      | 140  | 400   | 50      | 120  | Hz    |

| frequency <sup>1</sup> |                                                |               |         |      |       |         |      |       |

| Maximum                | R <sub>T</sub> = 2 kΩ, C <sub>T</sub> = 470 pF | 400           | 600     |      | 400   | 600     |      | kHz   |

| frequency              |                                                |               |         |      |       |         |      |       |

| Sawtooth peak          | V <sub>IN</sub> = 40 V                         |               | 3.5     | 3.9  |       | 3.5     | 3.9  | V     |

| voltage                |                                                |               |         |      |       |         |      |       |

| Sawtooth valley        | V <sub>IN</sub> = 7 V                          | 0.6           | 1       |      | 0.6   | 1       |      | V     |

| voltage                |                                                |               |         |      |       |         |      |       |

| Clock amplitude        |                                                | 3.0           | 4.0     |      | 3.0   | 4.0     |      | V     |

| Clock pulse            |                                                | 0.2           | 0.5     | 1.2  | 0.2   | 0.5     | 1.2  | μs    |

| width                  |                                                |               |         |      |       |         |      |       |

| Error Amplifier Sec    | tion (Vcm = 2.3 V to Vref)                     |               |         |      |       |         |      |       |

| Input offset           | Rs ≤ 2 kΩ                                      |               | 0.5     | 5    |       | 2       | 10   | mV    |

| voltage                |                                                |               |         |      |       |         |      |       |

| Input bias             |                                                |               | 1       | 5    |       | 1       | 10   | μA    |

| current                |                                                |               |         |      |       |         |      |       |

|                                           |                                                          |          |          |     |       | a 🔨    | MICROCHIP | company |

|-------------------------------------------|----------------------------------------------------------|----------|----------|-----|-------|--------|-----------|---------|

| Parameter                                 | Test Conditions                                          | SG152    | 4B/2524B |     | SG352 | 4B     |           | Units   |

| Input offset<br>current                   |                                                          |          |          | 1   |       |        | 1         | μΑ      |

| DC open loop<br>gain                      | $R_L \geq 10 \ M\Omega$                                  | 60       | 78       |     | 60    | 78     |           | dB      |

| Output low level                          | I <sub>SINK</sub> = 100 μA                               |          | 0.2      | 0.5 |       | 0.2    | 0.5       | V       |

|                                           | Vpin 1 - Vpin 2 ≥ 150 mV                                 |          |          |     |       |        |           |         |

| Output high level                         | I <sub>source</sub> = 100 μA<br>Vpin 2 - Vpin 1 ≥ 150 mV | 3.8      | 4.2      |     | 3.8   | 4.2    |           | V       |

| Common mode<br>rejection                  | V <sub>CM</sub> = 2.3 V to V <sub>REF</sub>              | 70       | 90       |     | 70    | 90     |           | dB      |

| Supply voltage rejection                  | $V_{IN}$ = 7 V to 40 V                                   | 76       | 100      |     | 76    | 100    |           | dB      |

| Gain-bandwidth<br>product <sup>1</sup>    | T <sub>J</sub> = 25 °C                                   | 1        | 2        |     | 1     | 2      |           | MHz     |

| P.W.M. Comparator                         | · ( Fosc = 45 kHz, Rτ = 2700 Ω, Cτ =                     | 0.01 μF) |          |     |       |        |           |         |

| Minimum duty<br>cycle                     | V <sub>COMP</sub> = 0.5 V                                |          |          | 0   |       |        | 0         | %       |

| Maximum duty<br>cycle                     | V <sub>COMP</sub> = 3.9 V                                | 45       | 49       |     | 45    | 49     |           | %       |

| Current Limit Ampli                       | fier Section (Vcm = 0 V to 17.5 V)                       |          |          |     |       |        |           |         |

| Sense voltage                             |                                                          | 180      | 200      | 220 | 170   | 200    | 230       | mV      |

| Input bias<br>current                     |                                                          |          | -3       | -10 |       | -3     | -10       | μΑ      |

| Shutdown Input Sec                        | tion                                                     |          |          |     |       |        |           |         |

| High input<br>voltage                     |                                                          | 2.0      |          |     | 2.0   |        |           | V       |

| High input<br>current                     | Vshutdown = 5 V                                          |          | 0.10.1   | 11  |       | 0.10.1 | 11        | mA      |

| Low input<br>voltage                      |                                                          |          |          | 0.6 |       |        | 0.6       |         |

| Output Section for e                      | each Transistor                                          |          |          |     |       |        |           |         |

| Collector leakage<br>current              | V <sub>CE</sub> = 60 V                                   |          |          | 50  |       |        | 50        | μΑ      |

| Collector                                 | Ic = 10 mA                                               |          | 0.2      | 0.4 |       | 0.2    | 0.4       | V       |

| saturation<br>voltage                     | Ic = 100 mA                                              |          | 1.0      | 2.0 |       | 1.0    | 2.0       | V       |

| Emitter output                            | $I_{\rm E} = 10  \rm mA$                                 | 17.5     | 19       |     | 17.5  | 19     |           | V       |

| voltage                                   | I <sub>E</sub> = 100 mA                                  | 17       | 18       |     | 17    | 18     |           | V       |

| Emitter voltage<br>rise time <sup>1</sup> | R <sub>E</sub> = 2 kΩ, T <sub>A</sub> = 25 °C            |          | 0.2      | 0.5 |       | 0.2    | 0.5       | μs      |

| Collector voltage                         | Rc = 2 kΩ, T <sub>A</sub> = 25 °C                        |          | 0.1      | 0.2 |       | 0.1    | 0.2       | μs      |

fall time **Power Consumption** VIN = 40 V, VSHUTDOWN = 2.0 V 5 12 5 Standby current 12 mΑ

#### Note:

1. These parameters, although guaranteed over the recommended operating conditions, are not tested in production.

### 3.1 Recommended Operating Conditions

The following table shows recommended operating conditions of SG1524B/SG2524B/SG3524B. Here, the operating conditions refer to ranges over which the device is functional.

### Table 2 • Recommended Operating Conditions

| Parameter                                     | Value                         | Unit   |  |

|-----------------------------------------------|-------------------------------|--------|--|

| Input voltage (V <sub>IN</sub> )              | 7 to 40                       | V      |  |

| Collector voltage                             | 0 to 60                       | V      |  |

| Error A common mode range                     | 2.3 to VREF                   | V      |  |

| Current limit sense common mode range         | 0 to $V_{\text{IN}}$ to 2.5 V | V      |  |

| Output current (each transistor)              | 0 to 100                      | mA     |  |

| Reference load current                        | 0 to 20                       | mA     |  |

| Oscillator charging current                   | 25 to 1.8                     | μA/mA  |  |

| Oscillator frequency range                    | 100 to 400                    | Hz/kHz |  |

| Oscillator timing resistor (R <sub>T</sub> )  | 2 to 150                      | kΩ     |  |

| Oscillator timing capacitor (C <sub>T</sub> ) | 1 to 0.1                      | nF/μF  |  |

| Operating Ambient Temperature Range           |                               |        |  |

| SG1524B                                       | –55 to 125                    | °C     |  |

| SG2524B                                       | –25 to 85                     | °C     |  |

| SG3524B                                       | 0 to 70                       | °C     |  |

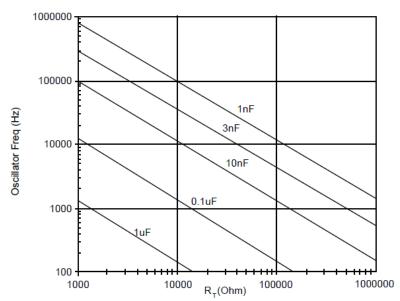

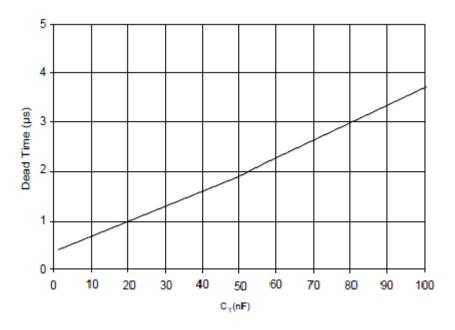

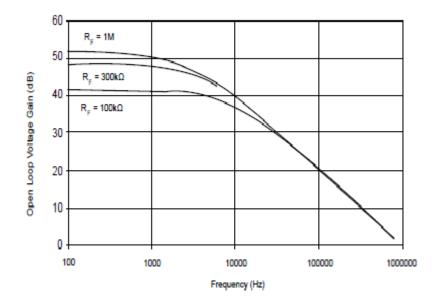

### 3.2 Typical Performance Curves

The following figures show characteristic curves of SG1524B. The conditions are, VIN = 20 V, TA = 25 °C.

### Figure 2 • Oscillator Frequency vs. Timing Resistor and Capacitor

Figure 3 • SG1524B Dead Times vs. Timing Capacitance (RT = 2.7 kΩ)

#### Figure 4 • SG1524B Error Amplitude Voltage Gain vs. Frequency over Rf

### 3.3 Absolute Maximum Ratings

The following table shows the absolute maximum ratings of SG1524B/SG2524B/SG3524B. The absolute maximum ratings refer to values beyond which damage may occur.

| Table 3 • | Absolute | Maximum | Ratings |

|-----------|----------|---------|---------|

|-----------|----------|---------|---------|

| Parameter                                                                 | Value                   | Units |

|---------------------------------------------------------------------------|-------------------------|-------|

| Input voltage (+V <sub>IN</sub> )                                         | 42                      | V     |

| Collector voltage                                                         | 60                      | V     |

| Logic inputs                                                              | –0.3 to 5.5             | V     |

| Current limit sense inputs                                                | -0.3 to V <sub>IN</sub> | V     |

| Output current (each transistor)                                          | 200                     | mA    |

| Reference load current                                                    | 50                      | mA    |

| Oscillator charging current                                               | 5                       | mA    |

| Operating Junction Temperature                                            |                         |       |

| Hermetic (J, and L Packages)                                              | 150                     | °C    |

| Plastic (N, and DW Packages)                                              | 150                     | °C    |

| Storage temperature range                                                 | -65 to 150              | °C    |

| Lead temperature (soldering, 10 seconds)                                  | 300                     | °C    |

| RoHS peak package solder reflow temperature (40 seconds maximum exposure) | 260 (0, –5)             | °C    |

## 4 Package Information

This section shows the package outline dimensions and thermal specifications of SG1524B/SG2524B/SG3524B. Controlling dimensions are in inches, and metric equivalents are shown for general information.

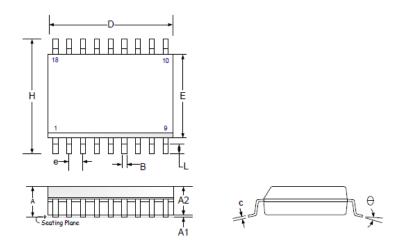

The following figure and table show DW 16-pin SOWB package and its dimensions. Dimensions do not include protrusions and should not exceed 0.155 mm (0.006 in.) on any side. Lead dimension should not include solder coverage.

#### Figure 5 • DW 16-Pin SOWB Package

#### Table 4 • DW 16-Pin SOWB Package Dimensions

| Dimensions       | Millimeters |         | Inches    |         |

|------------------|-------------|---------|-----------|---------|

|                  | Minimum     | Maximum | Minimum   | Maximum |

| А                | 1.35        | 1.75    | 0.053     | 0.069   |

| A1               | 0.10        | 0.25    | 0.004     | 0.010   |

| A2               | 1.25        | 1.52    | 0.049     | 0.060   |

| b                | 0.33        | 0.51    | 0.013     | 0.020   |

| с                | 0.19        | 0.25    | 0.007     | 0.010   |

| D                | 9.78        | 10.01   | 0.385     | 0.394   |

| E                | 5.79        | 6.20    | 0.228     | 0.244   |

| e                | 1.27 BSC    |         | 0.050 BSC |         |

| Н                | 3.81        | 4.01    | 0.150     | 0.158   |

| L                | 0.40        | 1.27    | 0.016     | 0.050   |

| Θ                | 0           | 8       | 0         | 8       |

| Lead coplanarity | -           | 0.10    | -         | 0.004   |

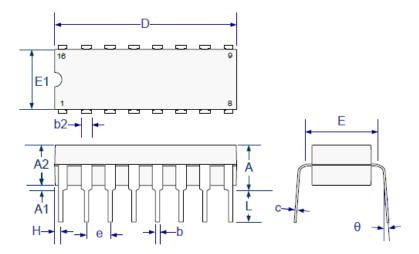

The following figure and table show N 16-pin plastic dual inline package and its dimensions. Dimensions do not include protrusions and should not exceed 0.155 mm (0.006 in.) on any side. Lead dimension should not include solder coverage.

### Figure 6 • N 16-Pin Plastic Dual Inline Package

### Table 5 • N 16-Pin Plastic Dual Inline Package Dimensions

| Dimensions | Millimeters  |         | Inches        |         |

|------------|--------------|---------|---------------|---------|

|            | Minimum      | Maximum | Minimum       | Maximum |

| Α          | -            | 5/08    | -             | 0.200   |

| A1         | 0.38         | 0.51    | 0.015         | 0.040   |

| A2         | 3.30 typical |         | 0.130 typical |         |

| b          | 0.38         | 0.51    | 0.015         | 0.020   |

| b2         | 0.76         | 1.52    | 0.030         | 0.060   |

| с          | 0.20         | 0.38    | 0.008         | 0.015   |

| D          | 18.54        | 20.57   | 0.730         | 0.810   |

| е          | 2.54 BSC     |         | 0.100 BSC     |         |

| E1         | 6.10         | 6.60    | 0.240         | 0.260   |

| E          | 7.62 BSC     |         | 0.300 BSC     |         |

| L          | 3.05         | -       | 0.120         | -       |

| θ          | -            | 15°     | -             | 15°     |

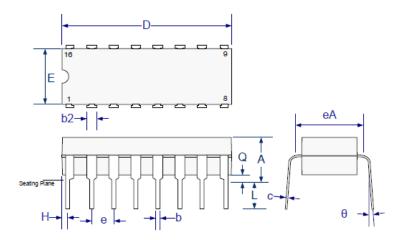

The following figure and table show J 16-pin ceramic dual inline package and its dimensions. Dimensions do not include protrusions and should not exceed 0.155 mm (0.006 in.) on any side. Lead dimension should not include solder coverage.

### Figure 7 • J 16-Pin Ceramic Dual Inline Package

### Table 6 • J 16-Pin Ceramic Dual Inline Package Dimensions

| Dimensions | Millimeters |         | Inches    |         |

|------------|-------------|---------|-----------|---------|

|            | Minimum     | Maximum | Minimum   | Maximum |

|            | -           | 5.08    | -         | 0.200   |

|            | 0.38        | 0.51    | 0.015     | 0.020   |

|            | 1.04        | 1.65    | 0.045     | 0.065   |

|            | 0.20        | 0.38    | 0.008     | 0.015   |

|            | 19.30       | 19.94   | 0.760     | 0.785   |

|            | 5.59        | 7.11    | 0.220     | 0.280   |

|            | 2.54 BSC    |         | 0.100 BSC |         |

| ١          | 7.37        | 7.87    | 0.290     | 0.310   |

|            | 0.63        | 1.78    | 0.025     | 0.070   |

|            | 3.18        | 5.08    | 0.125     | 0.200   |

|            | -           | 15°     | -         | 15°     |

|            | 0.51        | 1.02    | 0.020     | 0.040   |

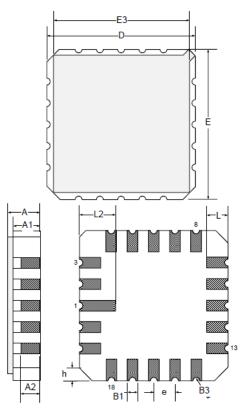

The following figure and table show L 20-pin ceramic leadless chip carrier (LCC) package and its outline dimensions. All exposed metalized area should be gold plated, 60 micro-inch minimum thickness over nickel plated base, if not specified in purchase order.

Table 7 • L 20-Pin Ceramic Leadless Chip Carrier (LCC) Package Outline Dimensions

| DIM | Millimeters   |         | Inches        | Inches  |  |  |

|-----|---------------|---------|---------------|---------|--|--|

|     | Minimum       | Maximum | Minimum       | Maximum |  |  |

| D/E | 8.64          | 9.14    | 0.340         | 0.360   |  |  |

| E3  | -             | 8.128   | -             | 0.320   |  |  |

| e   | 1.270 BSC     |         | 0.050 BSC     |         |  |  |

| B1  | 0.635 typical |         | 0.025 typical |         |  |  |

| L   | 1.02          | 1.52    | 0.040         | 0.060   |  |  |

| A   | 1.626         | 2.286   | 0.064         | 0.090   |  |  |

| ı   | 1.016 typical |         | 0.040 typical |         |  |  |

| 41  | 1.372         | 1.68    | 0.054         | 0.066   |  |  |

| 42  | -             | 1.168   | -             | 0.046   |  |  |

| L2  | 1.91          | 2.41    | 0.075         | 0.95    |  |  |

| 33  | 0.203 R       |         | 0.008 R       |         |  |  |

### 4.1 Thermal Data

The following table shows the thermal data specifications of SG1524B/SG2524B/SG3524B.

| Parameter                                                    | Value | Units |  |

|--------------------------------------------------------------|-------|-------|--|

| J Package                                                    |       |       |  |

| Thermal resistance-junction to case, $\theta_{\text{JC}}$    | 30    | °C/W  |  |

| Thermal resistance-junction to ambient, $\theta_{\text{JA}}$ | 80    | °C/W  |  |

| N Package                                                    |       |       |  |

| Thermal resistance-junction to case, $\theta_{\text{JC}}$    | 40    | °C/W  |  |

| Thermal resistance-junction to ambient, $\theta_{\text{JA}}$ | 65    | °C/W  |  |

| DW Package                                                   |       |       |  |

| Thermal resistance-junction to case, $\theta_{\text{JC}}$    | 40    | °C/W  |  |

| Thermal resistance-junction to ambient, $\theta_{\text{JA}}$ | 95    | °C/W  |  |

| L Package                                                    |       |       |  |

| Thermal resistance-junction to case, $\theta_{\text{JC}}$    | 35    | °C/W  |  |

| Thermal resistance-junction to ambient, $\theta_{\text{JA}}$ | 120   | °C/W  |  |

#### Notes:

- Junction temperature calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ .

- The above numbers for  $\theta_{Jc}$  are maximum for the limiting thermal resistance of the package in a standard mounting configuration. The  $\theta_{JA}$  numbers are meant to be guidelines for the thermal performance of the device or pc-board system. All of the them assume no ambient airflow.

## 5 Ordering Information

The following figures and tables show the connection diagrams and ordering information of SG1524B.

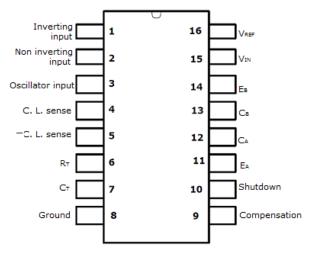

### Figure 9 • 16-Pin Dual Inline Package

- N Package: RoHS complaint/Pb-free transition DC: 0503

- N Package: RoHS/Pb-free 100% matte tin lead finish

#### Table 9 • Ordering Information of 16-Pin Dual Inline Package

| Ambient<br>Temperature | Туре | Package                               | Part Number   | Packaging Type                    |  |

|------------------------|------|---------------------------------------|---------------|-----------------------------------|--|

| 55 °C to 125 °C        | J    | 16-pin ceramic dual<br>inline package | SG1524BJ      | CERDIP                            |  |

|                        |      |                                       | SG1524BJ-883B | (ceramic dual in-line<br>package) |  |

|                        |      |                                       | SG2524BJ-DESC | package)                          |  |

| –25 °C to 85 °C        | Ν    | 16-pin dual inline plastic            | SG2524BN      | PDIP                              |  |

| 0 °C to 70 °C          | _    | package                               | SG3524BN      | (plastic dual in-line<br>package) |  |

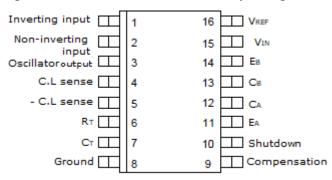

### Figure 10 • 16-Pin Small Outline Wide Body Package

- DW Package: RoHS complaint/Pb-free transition DC: 0516

- DW Package: RoHS/Pb-free 100% matte tin lead finish

#### Table 10 • Ordering Information of 16-Pin Small Outline Wide Body Package

| Ambient Temperature | Туре | Package                                 | Part Number   | Packaging Type                  |

|---------------------|------|-----------------------------------------|---------------|---------------------------------|

| –25 °C to 85 °C     | DW   | 16-pin dual inline<br>plastic package   | SG2524BDW     | SOWB                            |

| 0 °C to 70 °C       | -    |                                         | SG3524BDW     |                                 |

| –55 °C to 125 °C    | L    | 20-pin ceramic<br>leadless chip carrier | SG1524BL-883B | CLCC                            |

|                     |      |                                         | SG1524BL      | (Ceramic leadless chip carrier) |

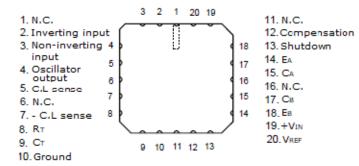

#### Figure 11 • 20-Pin Ceramic Leadless Chip Carrier

### Table 11 • Ordering Information of 20-Pin Ceramic Leadless Chip Carrier

| Ambient Temperature | Туре | Package                 | Part Number   | Packaging Type |

|---------------------|------|-------------------------|---------------|----------------|

| –55 °C to 125 °C    | L    | 20-pin ceramic leadless | SG1524BL-883B | CLCC           |

|                     |      | chip carrier            | SG1524BL      |                |

#### Notes:

- Contact your Microsemi representative for DESC product availability.

- All packages are viewed from the top.

- Hermetic packages, J and L use Sn63/Pb37 hot solder lead finish. Contact your Microsemi representative for availability of RoHS versions.

- Available in tape and reel. Append the letters "TR" to the part number: SG3524BDW-TR.

Microsemi Headquarters

One Enterprise, Aliso Viejo, C4 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2018 Microsemi. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mision-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is provident y to Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAS, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions; security technologies and scalable anti-tamper products; thermet solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; thermet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www microsemi.com.

SG1524B-2.00-0718