SLUSD12A - OCTOBER 2017-REVISED FEBRUARY 2018

UCC28780

# **UCC28780 High Frequency Active Clamp Flyback Controller**

#### **Features**

- Full and Partial Zero Voltage Switching (ZVS) of Primary FET with Adaptive Control

- Programmable Timing for External Si or GaN

- High Switching Frequency up to 1 MHz

- Programmable Adaptive Burst Control and Standby Mode for Light-Load Efficiency with Low Output Ripple and Audible Noise Mitigation

- Brownout Detection without Direct Line Sensing

- Accurate Programmable Over-Power Protection (OPP) to Support Peak Power Mode

- Fault Protections: Over-Temperature, Output Over-Voltage, Output Short-Circuit, Over-Current, and Pin Fault

- Direct Interface with Optocoupler Based Feedback Allows for Dynamically Scalable Output Voltage

- Internal Soft Start

- NTC Thermistor Interface with External Enable

# **Applications**

- High-Density AC-to-DC Adapters for Notebook, Tablet, TV, Set-Top Box and Printer

- USB Power Delivery, Direct and Fast Mobile Chargers

- AC-to-DC or DC-to-DC Auxiliary Power Supply

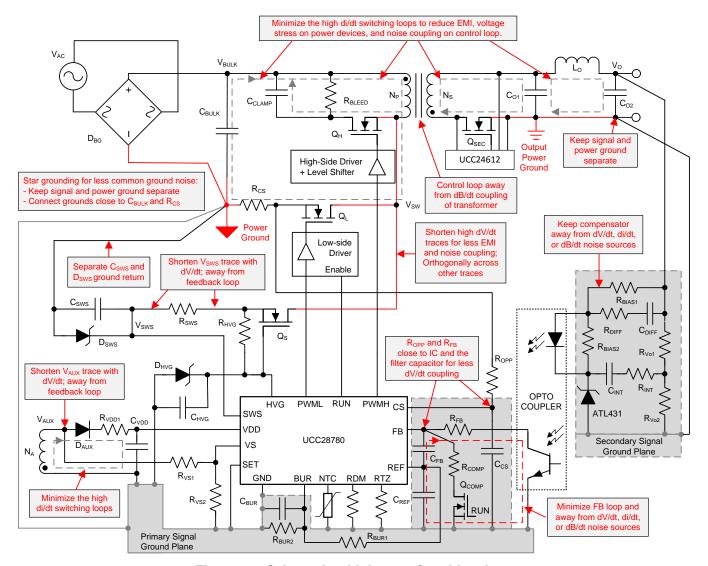

# 3 Description

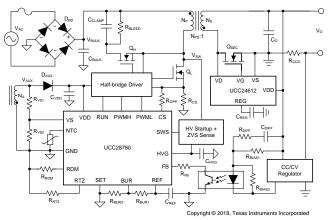

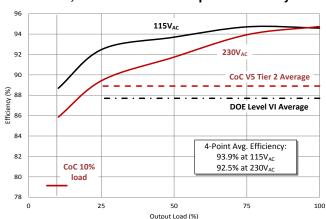

UCC28780 is a high-frequency active-clamp flyback controller that enables high-density AC-to-DC power supplies that comply with stringent global efficiency standards such as DoE Level VI and EU CoC V5 Tier-2. User programmable advanced control law features allow performance to be optimized for both Silicon (Si) and Gallium Nitride (GaN) power FETs. Direct operation with switching devices that combine driver and GaN FETs is further enhanced with logiclevel gate signals and enable outputs.

Zero voltage switching (ZVS) is achieved over a wide operating range with advanced auto-tuning techniques, adaptive dead-time optimization, and variable switching frequency control law. Using adaptive multimode control that changes the operation based on input and output conditions, UCC28780 enables high efficiency while mitigating audible noise. With a variable switching frequency of up to 1 MHz and accurate programmable over-power protection, which provides consistent power for thermal design across wide line range, the size of passive components can be further reduced and enable high power density.

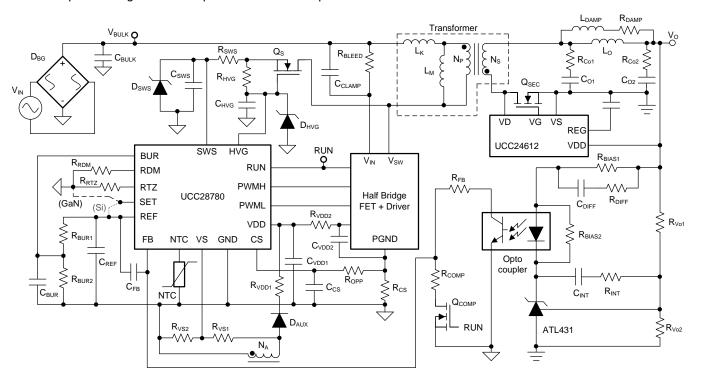

UCC28780 works with VDS-sensing synchronous rectifier controllers, such as UCC24612, to achieve higher conversion efficiency and very compact designs.

# Device Information(1)

| ORDERABLE PART NUMBER | PACKAGE | BODY SIZE (NOM)    |

|-----------------------|---------|--------------------|

| UCC28780RTE           | WQFN-16 | 3.00 mm × 3.00 mm  |

| UCC28780D             | SOIC-16 | 10.33 mm × 7.50 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

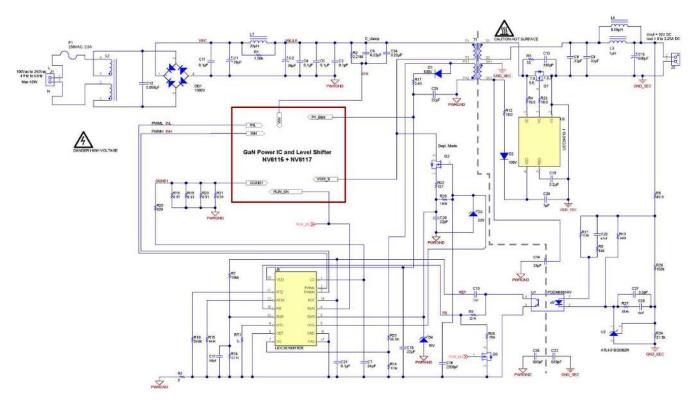

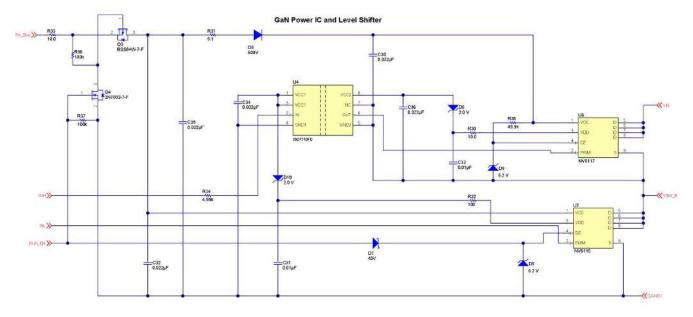

# Simplified Schematic

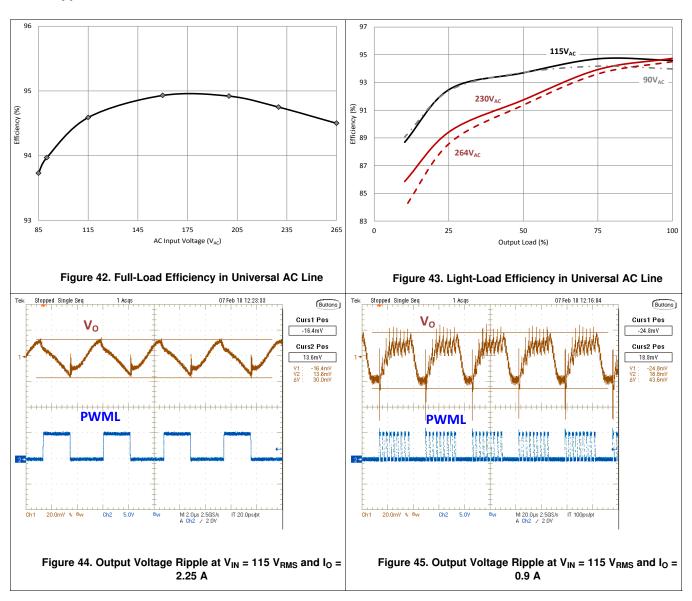

#### 45-W, 20-V GaN-ACF Adapter Efficiency

# **Table of Contents**

| 1 | Features 1                           |    | 7.4 Device Functional Modes                         | 21                |

|---|--------------------------------------|----|-----------------------------------------------------|-------------------|

| 2 | Applications 1                       | 8  | Application and Implementation                      | . 37              |

| 3 | Description 1                        |    | 8.1 Application Information                         | 37                |

| 4 | Revision History2                    |    | 8.2 Typical Application Circuit                     | 37                |

| 5 | Pin Configuration and Functions      | 9  | Power Supply Recommendations                        | 51                |

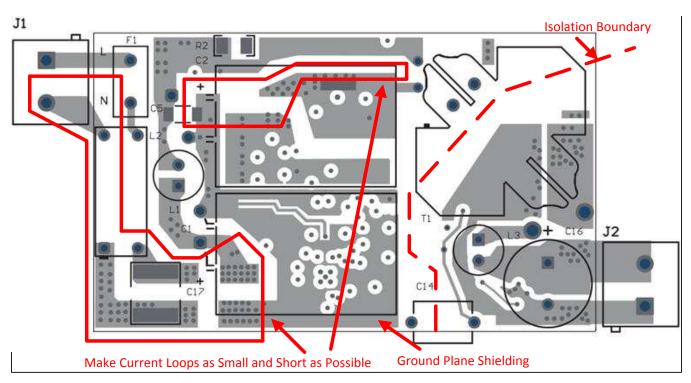

| 6 | Specifications5                      | 10 | Layout                                              | . 52              |

| • | 6.1 Absolute Maximum Ratings 5       |    | 10.1 Layout Guidelines                              | 52                |

|   | 6.2 ESD Ratings                      |    | 10.2 Layout Example                                 | 54                |

|   | 6.3 Recommended Operating Conditions | 11 | Device and Documentation Support                    | 58                |

|   | 6.4 Thermal Information of SOIC      |    | 11.1 Documentation Support                          | 58                |

|   | 6.5 Thermal Information of WQFN6     |    | 11.2 Receiving Notification of Documentation Update | s <mark>58</mark> |

|   | 6.6 Electrical Characteristics       |    | 11.3 Community Resources                            | 58                |

|   | 6.7 Typical Characteristics          |    | 11.4 Trademarks                                     | 58                |

| 7 | Detailed Description 12              |    | 11.5 Electrostatic Discharge Caution                | 58                |

|   | 7.1 Overview                         |    | 11.6 Glossary                                       | 58                |

|   | 7.2 Functional Block Diagram         | 12 | Mechanical, Packaging, and Orderable                |                   |

|   | 7.3 Detailed Pin Description         |    | Information                                         | . 59              |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE           | REVISION | NOTES            |

|----------------|----------|------------------|

| February, 2018 | A        | Initial release. |

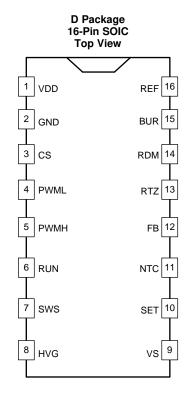

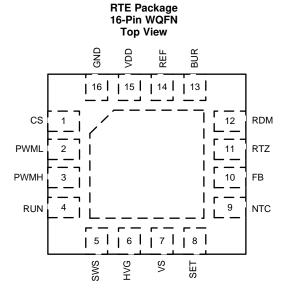

# 5 Pin Configuration and Functions

Copyright © 2017–2018, Texas Instruments Incorporated

Submit Documentation Feedback

#### Pin Functions

| Pin Functions |      |      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------------|------|------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|               | PIN  | 1    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| NAME          | SOIC | WQFN |                     | 22001III 11011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| BUR           | 15   | 13   | I                   | This pin is used to program the burst level of the converter at light load. A resistive divider between REF and GND is used to set a voltage at this pin to determine the peak current level when the converter enters the adaptive burst mode. In addition, the Thevenin resistance on BUR pin (equivalent resistance of the divider resistors in parallel) is used to set an offset voltage for smooth mode transition which increases the peak current level when the converter enters the low power mode. |  |

| CS            | 3    | 1    | I                   | This is the current sense input pin. This pin couples through a line-compensation resistor to a current-sense resistor to sense and control the peak primary current in each switching cycle. A current sourced from this pin, which magnitude is proportional to the converter's input voltage derived from the VS-pin input signal, creates an offset voltage across the line-compensation resistor to program an OPP level at high line.                                                                   |  |

| FB            | 12   | 10   | I                   | The feedback current signal to close the converter's regulation loop is coupled to this pin. This pin presents a 4-V output that is designed to have 0-µA to 75-µA current pulled out of the pin corresponding to the converter operating from full-power to zero-power conditions.                                                                                                                                                                                                                           |  |

| GND           | 2    | 16   | G                   | Ground reference and return for all controller signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| HVG           | 8    | 9    | 0                   | The high-voltage gate pin is used to control the gate of an external depletion-mode MOSFET for start-up and switch-node voltage sensing. A 2.2-nF ceramic bypass capacitor to ground is required.                                                                                                                                                                                                                                                                                                             |  |

| NTC           | 11   | O    | I                   | This is an interface to an external NTC (negative temperature coefficient) thermistor for remote temperature sensing. Pulling this pin low shuts down PWM action and initiates a fault response.                                                                                                                                                                                                                                                                                                              |  |

| PWMH          | 5    | 3    | 0                   | The PWMH pin is a logic-level output signal used to control the gate of the high-side clamp switch through an external gate driver.                                                                                                                                                                                                                                                                                                                                                                           |  |

| PWML          | 4    | 2    | 0                   | The PWML pin is a logic-level output signal used to control the gate of the low-side primary switch through an external gate driver.                                                                                                                                                                                                                                                                                                                                                                          |  |

| RDM           | 14   | 12   | I                   | A resistor to ground on this pin programs a synthesized demagnetization time used to control the on-time of the high-side switch to achieve zero voltage switching on the low-side switch. The controller applies a voltage on this pin that varies with the output voltage derived from the VS pin signal.                                                                                                                                                                                                   |  |

| REF           | 16   | 14   | 0                   | 5V reference output that requires a 0.1-μF ceramic bypass capacitor to ground. This reference is used to power internal circuits and can supply a limited external load current.                                                                                                                                                                                                                                                                                                                              |  |

| RTZ           | 13   | 11   | I                   | A resistor to ground on this pin programs an adaptive transition-to-zero delay from the turn-off edge of the high-side clamp switch to the turn-on edge of the low-side switch.                                                                                                                                                                                                                                                                                                                               |  |

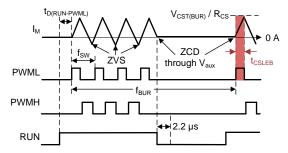

| RUN           | 6    | 4    | 0                   | This output pin is high when the controller is in a run state. During start-up and wait states this output is low. It can be used to enable and disable the external gate drivers to reduce the static power consumption. There is a preset delay, $t_{D(RUN-PWML)}$ , of about 2.2 $\mu$ s that delays the initiation of PWML switching after this pin has gone high.                                                                                                                                        |  |

| SET           | 10   | 8    | I                   | This pin is used to configure the controller to be optimized for Gallium Nitride (GaN) power FETs or silicon (Si) power FETs on the primary side. Depending on setting, it will optimize parameters of the ZVS control loop, dead-time adjustment, and protection features. When pulled high to REF pin, it is optimized for Si FETs. When pulled low to GND, it is optimized for GaN FETs.                                                                                                                   |  |

| SWS           | 7    | 5    | I                   | This sensing input is used to monitor the switch-node voltage as it nears zero volts in normal operation. During start-up, this pin is connected to the VDD pin internally to allow the high-voltage sensing network to provide start-up current.                                                                                                                                                                                                                                                             |  |

| VDD           | 1    | 15   | Р                   | Bias power input to the controller. A hold-up capacitor to ground is required for the bias power supplied from the transformer auxiliary winding to this pin.                                                                                                                                                                                                                                                                                                                                                 |  |

| VS            | 9    | 7    | I                   | This voltage sensing input pin is coupled to the auxiliary winding of the converter's transformer via a resistor divider. The pin and the associated external resistors are used to monitor the output and input voltages of the converter.                                                                                                                                                                                                                                                                   |  |

<sup>(1)</sup> I = Input, O = Output, P = Power, G = Ground

# 6 Specifications

# 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |                            | MIN         | MAX                                                                                                      | UNIT |

|------------------------------------------------|----------------------------|-------------|----------------------------------------------------------------------------------------------------------|------|

| Input Voltage                                  | VDD                        |             | 38                                                                                                       | V    |

|                                                | sws                        | -6          | 38                                                                                                       |      |

|                                                | VDD-SWS (Run state)        | -20         | 38                                                                                                       |      |

|                                                | CS                         | -0.3        | 3.6                                                                                                      |      |

|                                                | NTC                        | -0.3        | 7                                                                                                        |      |

|                                                | FB                         | -0.3        | 7                                                                                                        |      |

|                                                | VS (Continuous)            | -0.75       | 7                                                                                                        |      |

|                                                | VS (Transient, 100ns Max.) | -1          | 7                                                                                                        |      |

|                                                | RTZ                        | -0.3        | 7                                                                                                        |      |

|                                                | BUR                        | -0.3        | 7                                                                                                        |      |

|                                                | SET                        | -0.3        | 7                                                                                                        |      |

|                                                | RDM                        | -0.3        | 7                                                                                                        |      |

| Output Voltage                                 | REF                        | -0.3        | 7                                                                                                        | V    |

|                                                | HVG                        | -0.3        | 25                                                                                                       |      |

|                                                | PWML, PWMH, RUN            | -0.3        | 7                                                                                                        |      |

| Source Current                                 | REF                        |             | 5                                                                                                        | mA   |

|                                                | HVG                        |             | Self-limiting                                                                                            |      |

|                                                | VS (Continuous)            |             | 2                                                                                                        |      |

|                                                | VS (Transient, 100ns Max.) |             | 2.5                                                                                                      |      |

|                                                | FB                         |             | -0.3 7 -0.3 7 -0.3 7 -0.3 7 -0.3 7 -0.3 25 -0.3 7  5 Self-limiting 2 2.5 1 1 Self-limiting Self-limiting |      |

|                                                | PWML, PWMH, RUN            |             | 1                                                                                                        |      |

|                                                | RTZ                        |             | Self-limiting                                                                                            |      |

|                                                | RDM                        |             | Self-limiting                                                                                            |      |

| Sink Current                                   | PWML, PWMH, RUN            |             | 1                                                                                                        | mA   |

|                                                | SWS                        |             | 5                                                                                                        | mA   |

| Operating junction temperature, T <sub>J</sub> |                            | <b>–</b> 55 | 150                                                                                                      | °C   |

| Storage temperature, T <sub>stg</sub>          |                            | -55         | 150                                                                                                      | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                  |                                | MIN | NOM MAX | UNIT |

|------------------|--------------------------------|-----|---------|------|

| $V_{VDD}$        | Bias-supply operating voltage  | 12  | 34      | V    |

| $C_{VDD}$        | VDD capacitor                  | 0.3 |         | μF   |

| C <sub>REF</sub> | REF bypass capacitor           | 0.1 |         | μF   |

| C <sub>HVG</sub> | HVG bypass capacitor           | 2.2 |         | nF   |

| T <sub>J</sub>   | Operating Junction temperature | -40 | 125     | °C   |

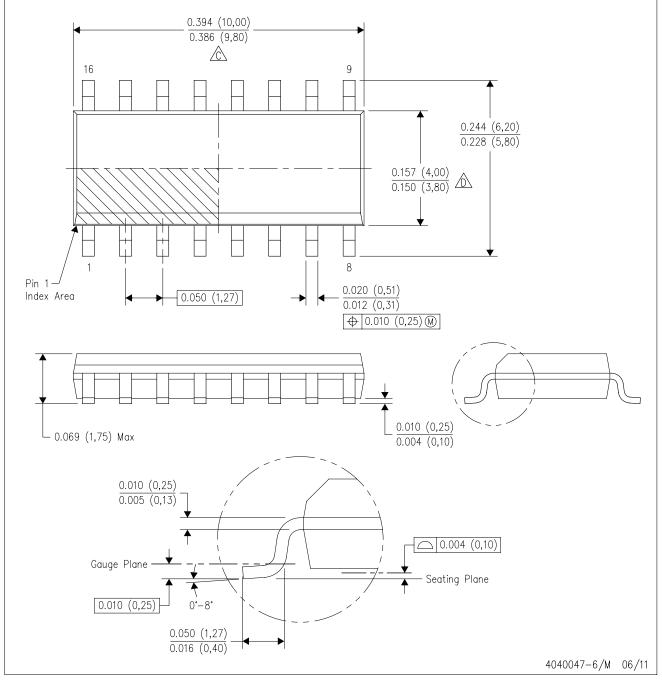

## 6.4 Thermal Information of SOIC

|                      |                                              | D       |      |

|----------------------|----------------------------------------------|---------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | SOIC    | UNIT |

|                      |                                              | 16 PINS |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 83.9    | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 43.0    | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 42.6    | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 10.9    | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 42.2    | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | n/a     | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

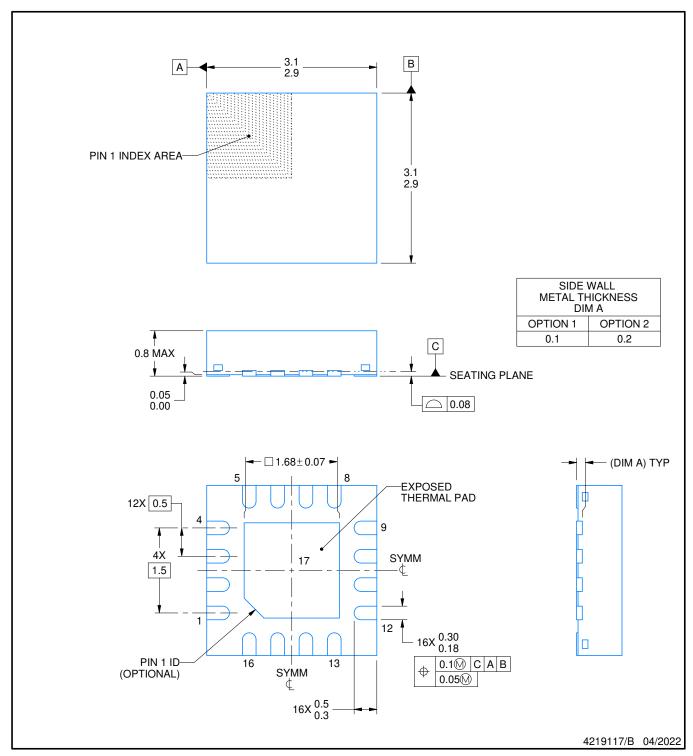

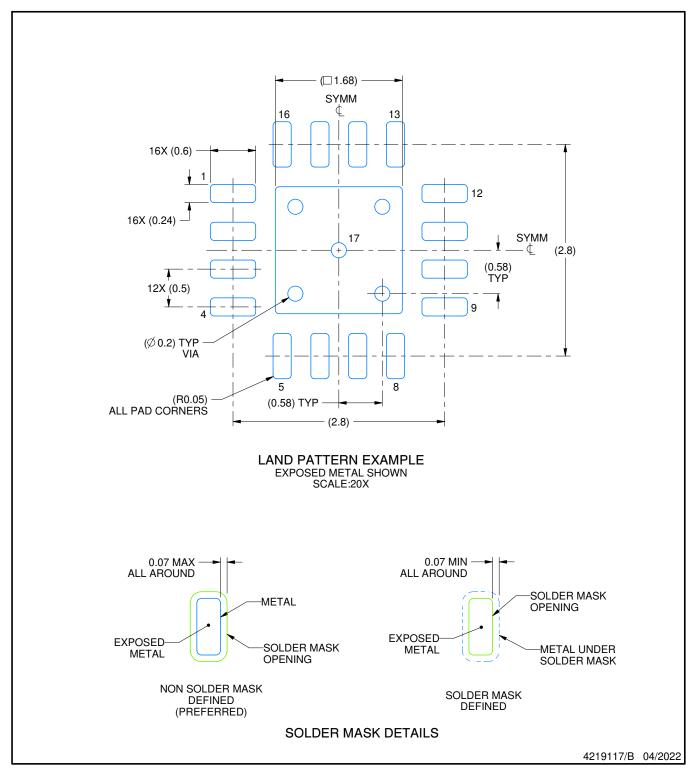

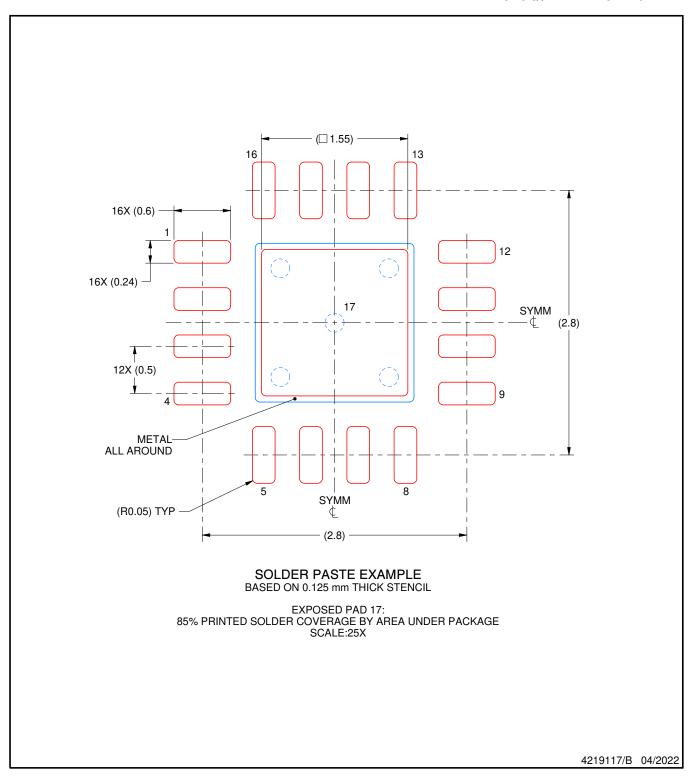

## 6.5 Thermal Information of WQFN

|                      |                                              | RTE + PAD |      |

|----------------------|----------------------------------------------|-----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | WQFN      | UNIT |

|                      |                                              | 16 PINS   |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 47.2      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 48.9      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 22.0      | °C/W |

| ΨЈΤ                  | Junction-to-top characterization parameter   | 1.0       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 22.0      | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 6.7       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.6 Electrical Characteristics

Over operating free-air temperature range,  $V_{VDD}$  = 15V,  $R_{RDM}$  = 115 k $\Omega$ ,  $R_{RTZ}$  = 140 k $\Omega$ ,  $V_{BUR}$ = 1.2 V,  $V_{SET}$  = 0 V,  $R_{NTC}$  = 50 k $\Omega$ ,  $V_{VS}$  = 4 V,  $V_{SWS}$  = 0 V,  $V_{SWS}$  = 0  $V_{SET}$  = 0  $V_{$

|                         | PARAMETER                                               | TEST CONDITION                                                          | MIN   | TYP  | MAX      | UNIT |

|-------------------------|---------------------------------------------------------|-------------------------------------------------------------------------|-------|------|----------|------|

| BIAS SUPF               | PLY INPUT CURRENT                                       |                                                                         |       |      |          |      |

| I <sub>RUN(STOP)</sub>  | Supply current, run                                     | No switching                                                            |       | 2.3  | 3        | mA   |

| I <sub>RUN(SW)</sub>    | Supply current, run                                     | Switching, $I_{VSL} = 0 \mu A$                                          |       | 2.5  | 3.3      | mA   |

| I <sub>WAIT</sub>       | Supply current, wait                                    | I <sub>FB</sub> = -85 μA                                                |       | 400  | 550      | μΑ   |

| I <sub>START</sub>      | Supply current, start                                   | $V_{VDD} = V_{VDD(ON)} - 100 \text{ mV}, V_{VS} = 0$                    |       | 70   | 140      | μΑ   |

| I <sub>FAULT</sub>      | Supply current, fault                                   | Fault state                                                             |       | 265  | 350      | μΑ   |

|                         | LTAGE LOCKOUT (UVLO)                                    |                                                                         |       |      | <u>I</u> |      |

| V <sub>VDD(ON)</sub>    | VDD turn-on threshold                                   | V <sub>VDD</sub> increasing                                             | 16.7  | 17.5 | 18.2     | V    |

| V <sub>VDD(OFF)</sub>   | VDD turn-off threshold                                  | V <sub>VDD</sub> decreasing                                             | 9.35  | 9.8  | 10.4     | V    |

| V <sub>VDD(PCT)</sub>   | Offset to power cycle for long output voltage overshoot | Offset above $V_{VDD(OFF)}$ , $I_{FB} = -85 \mu A$                      | 0.3   | 1    | 1.5      | V    |

| VS INPUT                |                                                         | <del>-</del>                                                            |       |      | ļ        |      |

| V <sub>VSNC</sub>       | Negative clamp level                                    | I <sub>VSL</sub> = -1.25 mA, voltage below ground                       | 170   | 250  | 325      | mV   |

| V <sub>ZCD</sub>        | Zero-crossing detection (ZCD) level                     | V <sub>VS</sub> decreasing                                              | 10    | 30   | 55       | mV   |

| t <sub>ZC</sub>         | Zero-crossing timeout delay                             |                                                                         | 1.8   | 2.2  | 2.7      | μs   |

| t <sub>D(ZCD)</sub>     | Propagation delay from ZCD high to PWML high            | V <sub>VS</sub> step from 4 V to -0.1 V                                 |       | 20   | 45       | ns   |

| I <sub>VSB</sub>        | Input bias current                                      | V <sub>VS</sub> = 4 V                                                   | -0.25 | 0    | 0.25     | μΑ   |

| CS INPUT                |                                                         |                                                                         |       |      |          |      |

| V <sub>CST(MAX)</sub>   | Maximum CS threshold voltage                            | V <sub>CS</sub> increasing                                              | 765   | 800  | 825      | mV   |

| V <sub>CST(MIN)</sub>   | Minimum CS threshold voltage                            | V <sub>CS</sub> decreasing, I <sub>FB</sub> = -85 μA                    | 123   | 150  | 170      | mV   |

| t <sub>CSLEB</sub>      | Leading-edge blanking time                              | V <sub>SET</sub> = 5 V, V <sub>CS</sub> = 1 V                           | 175   | 200  | 225      | ns   |

|                         |                                                         | V <sub>SET</sub> = 0 V, V <sub>CS</sub> = 1 V                           | 115   | 130  | 145      |      |

| t <sub>D(CS)</sub>      | Propagation delay of CS comparator high to PWML low     | V <sub>CS</sub> step from 0 V to 1 V                                    |       | 15   | 25       | ns   |

| K <sub>LC</sub>         | Line-compensation current ratio                         | $I_{VSL}$ = -1.25 mA, $I_{VSL}$ / current out of CS pin                 | 22.5  | 25   | 27       | A/A  |

| RUN, PWM                | L, PWMH                                                 |                                                                         |       |      |          |      |

| V <sub>PWMLH</sub>      | High level of PWML, PWMH, and                           | I <sub>PWML(H)</sub> = -1 mA, I <sub>RUN</sub> = -1 mA                  | 4.4   | 5    |          | V    |

| V <sub>PWMHH</sub>      | RUN pins                                                |                                                                         |       |      |          |      |

| V <sub>RUNH</sub>       |                                                         |                                                                         |       |      |          |      |

| $V_{PWMLL}$             | Low level of PWML, PWMH, and                            | $I_{PWML(H)} = +1 \text{ mA}, I_{RUN} = +1 \text{ mA}$                  |       |      | 0.5      | V    |

| $V_{PWMHL}$             | RUN pins                                                |                                                                         |       |      |          |      |

| V <sub>RUNL</sub>       |                                                         |                                                                         |       |      |          |      |

| t <sub>RISE</sub>       | Turn-on rise time, 10% to 90% <sup>(1)</sup>            | C <sub>LOAD</sub> = 10 pF                                               |       |      | 10       | ns   |

| t <sub>FALL</sub>       | Turn-off fall time, 90% to 10% <sup>(1)</sup>           | C <sub>LOAD</sub> = 10 pF                                               |       |      | 10       | ns   |

| t <sub>D(RUN-</sub>     | Delay from RUN high to PWML high                        |                                                                         | 1.8   |      | 5.4      | μs   |

| t <sub>D(VS-PWMH)</sub> | Dead-time between VS high and PWMH high                 | V <sub>SET</sub> = 5 V                                                  | 44    | 55   | 70       | ns   |

| t <sub>D(PWML-H)</sub>  | Dead-time between PWML low and PWMH high                | V <sub>SET</sub> = 0 V                                                  | 34    | 42   | 51       | ns   |

| t <sub>ON(MIN)</sub>    | Minimum on-time of PWML in low                          | $V_{SET} = 5 \text{ V}, I_{FB} = -85 \mu\text{A}, V_{CS} = 1 \text{ V}$ | 70    | 90   | 115      | ns   |

|                         | power mode                                              | $V_{SET} = 0 \text{ V}, I_{FB} = -85 \mu\text{A}, V_{CS} = 1 \text{ V}$ | 48    | 65   | 80       | ns   |

<sup>(1)</sup> Not tested in protection, and limits guaranteed by design.

# **Electrical Characteristics (continued)**

Over operating free-air temperature range,  $V_{VDD}$  = 15V,  $R_{RDM}$  = 115 k $\Omega$ ,  $R_{RTZ}$  = 140 k $\Omega$ ,  $V_{BUR}$ = 1.2 V,  $V_{SET}$  = 0 V,  $R_{NTC}$  = 50 k $\Omega$ ,  $V_{VS}$  = 4 V,  $V_{SWS}$  = 0 V,  $V_{SWS}$  = 0  $V_{$

|                       | PARAMETER                                                                     | TEST CONDITION                                                              | MIN  | TYP   | MAX  | UNIT |

|-----------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|-------|------|------|

| PROTECT               | ION                                                                           |                                                                             |      |       | I    |      |

| V <sub>OVP</sub>      | Over-voltage threshold                                                        | V <sub>VS</sub> increasing                                                  | 4.4  | 4.5   | 4.6  | V    |

| V <sub>OCP</sub>      | Over-current threshold                                                        | V <sub>CS</sub> increasing                                                  | 0.97 | 1.2   | 1.35 |      |

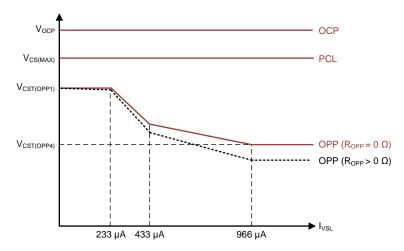

| V <sub>CST(OPP)</sub> | Over-power threshold on CS pin                                                | I <sub>VSL</sub> = 0 μA                                                     | 574  | 600   | 627  | mV   |

| 00.(0)                |                                                                               | I <sub>VSL</sub> = -333 μA                                                  | 492  | 545   | 595  |      |

|                       |                                                                               | I <sub>VSL</sub> = -666 μA                                                  | 426  | 460   | 492  |      |

|                       |                                                                               | I <sub>VSL</sub> = -1.25 mA                                                 | 405  | 425   | 452  |      |

| K <sub>OPP</sub>      | OPP threshold voltage ratio                                                   | $V_{CST(OPP)}$ ratio between $I_{VSL}$ = 0 $\mu A$ and $I_{VSL}$ = -1.25 mA | 1.36 | 1.4   | 1.44 | V/V  |

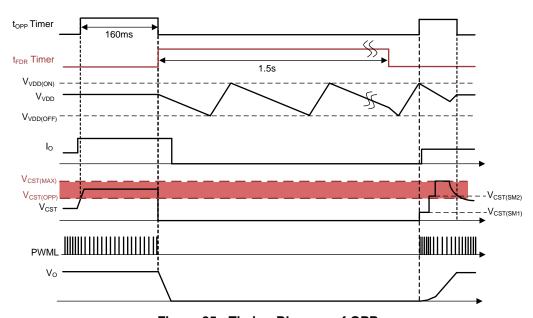

| OPP                   | OPP fault timer                                                               | I <sub>FB</sub> = 0 A                                                       | 115  | 160   | 200  | ms   |

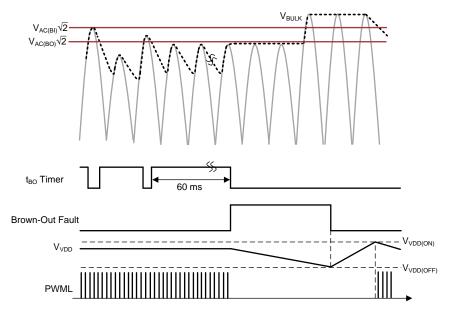

| VSL(RUN)              | VS line-sense run current                                                     | Current out of VS pin increasing                                            | 330  | 365   | 400  | μΑ   |

| VSL(STOP)             | VS line-sense stop current                                                    | Current out of VS pin decreasing                                            | 275  | 305   | 335  |      |

| < <sub>VSL</sub>      | VS line-sense ratio                                                           | I <sub>VSL(STOP)</sub> / I <sub>VSL(RUN)</sub>                              | 0.81 | 0.836 | 0.85 | A/A  |

| ВО                    | Brown-out detection delay time                                                | I <sub>VSL</sub> < I <sub>VSL(STOP)</sub>                                   | 35   | 60    | 75   | ms   |

| R <sub>RDM(TH)</sub>  | R <sub>RDM</sub> threshold for CS pin fault                                   |                                                                             | 41   | 50    | 59   | kΩ   |

| CSF1                  | Max. PWML on time for detecting CS pin fault                                  | V <sub>SET</sub> = 5 V                                                      | 1.6  | 2     | 2.3  | μs   |

| CSF0                  | Max. PWML on time for detecting CS pin fault                                  | $R_{RDM} < R_{RDM(TH)}$ for $V_{SET} = 0 V$                                 | 0.8  | 1     | 1.15 | μs   |

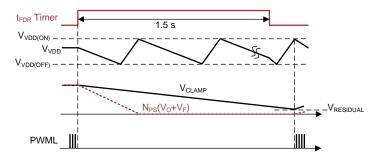

| FDR                   | Fault-reset delay timer                                                       | OCP, OPP, OVP, SCP, or CS pin fault                                         | 1    | 1.5   | 1.9  | S    |

| $\Gamma_{J(STOP)}$    | Thermal shut-down temperature                                                 | Internal junction temperature                                               | 125  |       |      | °C   |

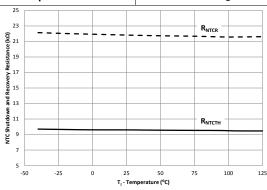

| NTC INPU              | Т                                                                             |                                                                             |      |       | ·    |      |

| / <sub>NTCTH</sub>    | NTC shut-down voltage                                                         | Voltage decreasing                                                          | 0.9  | 1.0   | 1.1  | ٧    |

| R <sub>NTСТН</sub>    | NTC shut-down resistance                                                      | R <sub>NTC</sub> decreasing                                                 | 8.7  | 9.5   | 10.3 | kΩ   |

| R <sub>NTCR</sub>     | NTC recovery resistance                                                       | R <sub>NTC</sub> increasing                                                 | 19.5 | 21.7  | 24   | kΩ   |

| NTC                   | NTC pull-up current, out of pin                                               | $R_{NTC} = 12 \text{ k}\Omega$                                              | 85   | 105   | 120  | μΑ   |

| BUR INPU              | T AND LOW POWER MODE                                                          |                                                                             |      |       |      |      |

| K <sub>BUR-CST</sub>  | Ratio from V <sub>BUR</sub> to V <sub>CST</sub>                               | V <sub>CST</sub> between V <sub>CST(OPP1)</sub> and 0.7 V                   | 3.9  | 4     | 4.13 | V/V  |

| BR(UP)                | Upper threshold of burst rate frequency in adaptive burst mode <sup>(1)</sup> |                                                                             | 29   | 34    | 39   | kHz  |

| BR(LR)                | Lower threshold of burst rate frequency in adaptive burst mode (1)            |                                                                             | 21   | 25    | 29   | kHz  |

| LPM                   | Burst rate frequency in low power mode                                        |                                                                             | 22   | 25    | 28   | kHz  |

| BUR                   | Bias current of V <sub>BUR</sub> offset in LPM                                |                                                                             | 2.1  | 2.7   | 3.4  | μΑ   |

| RTZ INPU              | Г                                                                             |                                                                             |      |       |      |      |

| Z(MAX)                | Maximum programmable dead-time from PWMH low to PWML high                     | $R_{RTZ}$ = 280 k $\Omega$ , $I_{VSL}$ = -1 mA, $V_{SET}$ = 5 $V$           | 380  | 480   | 565  | ns   |

| Z(MIN)                | Minimum programmable dead-time from PWMH low to PWML high                     | $R_{RTZ}$ = 78.4 k $\Omega$ , $I_{VSL}$ = -1 mA, $V_{SET}$ = 0 V            | 66   | 72    | 86   | ns   |

| Z                     | Dead-time from PWMH low to                                                    | I <sub>VSL</sub> = -150 μA                                                  | 144  | 172   | 205  | ns   |

|                       | PWML high                                                                     | I <sub>VSL</sub> = -450 μA                                                  | 123  | 150   | 177  | ns   |

|                       |                                                                               | I <sub>VSL</sub> = -733 μA                                                  | 110  | 125   | 145  | ns   |

| < <sub>TZ</sub>       | T <sub>Z</sub> compensation ratio                                             | $T_Z$ ratio between $I_{VSL}$ = -200 μA and $I_{VSL}$ = -733 μA             | 1.26 | 1.4   | 1.57 | s/s  |

# **Electrical Characteristics (continued)**

Over operating free-air temperature range,  $V_{VDD}$  = 15V,  $R_{RDM}$  = 115 k $\Omega$ ,  $R_{RTZ}$  = 140 k $\Omega$ ,  $V_{BUR}$ = 1.2 V,  $V_{SET}$  = 0 V,  $R_{NTC}$  = 50 k $\Omega$ ,  $V_{VS}$  = 4 V,  $V_{SWS}$  = 0 V,  $I_{FB}$  = 0  $\mu$ A,  $I_{HVG}$  = 25  $\mu$ A, and -40 °C <  $I_{J}$  =  $I_{A}$  < 125 °C (unless otherwise noted)

|                       | PARAMETER                                    | TEST CONDITION                                              | MIN  | TYP  | MAX  | UNIT |

|-----------------------|----------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| SWS INPL              | JT                                           |                                                             |      |      |      |      |

| V <sub>TH(SWS)</sub>  | SWS zero voltage threshold                   | V <sub>SET</sub> = 5 V                                      | 8.8  | 9    | 9.6  | V    |

|                       |                                              | V <sub>SET</sub> = 0 V                                      | 3.7  | 4    | 4.3  | V    |

| t <sub>D(SWS-</sub>   | Time between SWS low to PWML high            | V <sub>SWS</sub> step from 5 V to 0 V                       |      | 12   | 28   | ns   |

| FB INPUT              |                                              |                                                             |      |      |      |      |

| I <sub>FB(SBP)</sub>  | Maximum control FB current                   | I <sub>FB</sub> increasing                                  |      | 75   | 95   | μΑ   |

| $V_{FB(REG)}$         | Regulated FB voltage level                   |                                                             | 4    | 4.3  | 4.65 | V    |

| R <sub>FBI</sub>      | FB input resistance                          |                                                             | 7    | 8    | 9.5  | kΩ   |

| REF OUT               | PUT                                          |                                                             |      |      | ·    |      |

| V <sub>REF</sub>      | REF voltage level                            | I <sub>REF</sub> = 0 A                                      | 4.9  | 5    | 5.1  | V    |

| I <sub>S(REF)</sub>   | Short current of REF pin                     | Short REF pin                                               | 8    | 14   | 18   | mA   |

| $V_{R(LINE)}$         | Line regulation of V <sub>REF</sub>          | V <sub>VDD</sub> = 12 V to 35 V                             | -5   |      | 7    | mV   |

| $V_{R(LOAD)}$         | Load regulation of V <sub>REF</sub>          | I <sub>REF</sub> = 0 mA to 1 mA, change in V <sub>REF</sub> | -10  |      | 10   | mV   |

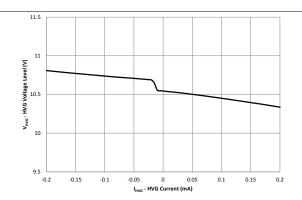

| HVG OUT               | PUT                                          |                                                             |      |      | ·    |      |

| $V_{HVG}$             | HVG voltage level                            | $I_{HVG} = +/-200 \mu A$ , run state                        | 9.7  | 10.5 | 11.4 | V    |

| I <sub>SE(HVG)</sub>  | HVG max sink current during startup          | V <sub>HVG</sub> = 13 V, start state                        | 55   | 90   | 140  | μΑ   |

| I <sub>S(HVG)</sub>   | Short current of HVG pin                     | Short HVG pin                                               | 0.4  | 1    | 1.6  | mA   |

| V <sub>HR(LINE)</sub> | Line regulation of V <sub>HVG</sub>          | V <sub>VDD</sub> = 12 V to 35 V                             | -25  |      | 25   | mV   |

| V <sub>HVG(OV)</sub>  | HVG over voltage threshold                   |                                                             | 13.0 | 13.8 | 14.6 | V    |

| RDM INPL              | JT                                           |                                                             |      |      |      |      |

| t <sub>DM(MAX)</sub>  | Maximum PWMH pulse width with maximum tuning | V <sub>SWS</sub> = 12 V                                     | 6.08 | 6.76 | 7.6  | μs   |

| t <sub>DM(MIN)</sub>  | Minimum PWMH pulse width with minimum tuning | V <sub>SWS</sub> = 0 V                                      | 3.05 | 3.4  | 3.8  | μs   |

# TEXAS INSTRUMENTS

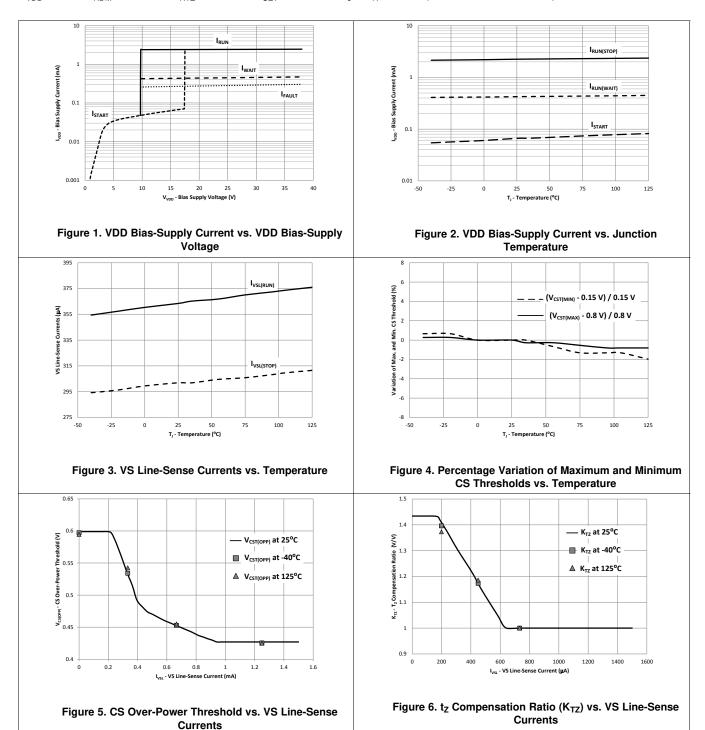

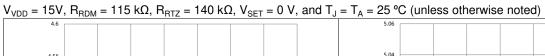

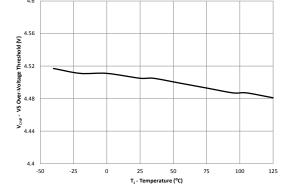

# 6.7 Typical Characteristics

$V_{VDD}$  = 15V,  $R_{RDM}$  = 115 k $\Omega$ ,  $R_{RTZ}$  = 140 k $\Omega$ ,  $V_{SET}$  = 0 V, and  $T_J$  =  $T_A$  = 25 °C (unless otherwise noted)

Product Folder Links: UCC28780

Submit Documentation Feedback

Copyright © 2017–2018, Texas Instruments Incorporated

) 10.4

-50

-25

# **Typical Characteristics (continued)**

Figure 7. VS Over-Voltage Threshold vs. Temperature

Figure 8. REF Voltage vs. Temperature

Figure 9. HVG Voltage vs. Temperature

75

100

125

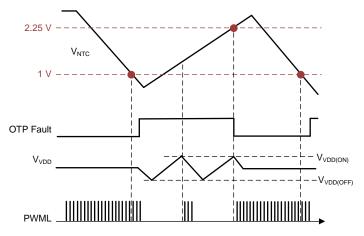

Figure 11. NTC Thresholds vs. Junction Temperature

# 7 Detailed Description

#### 7.1 Overview

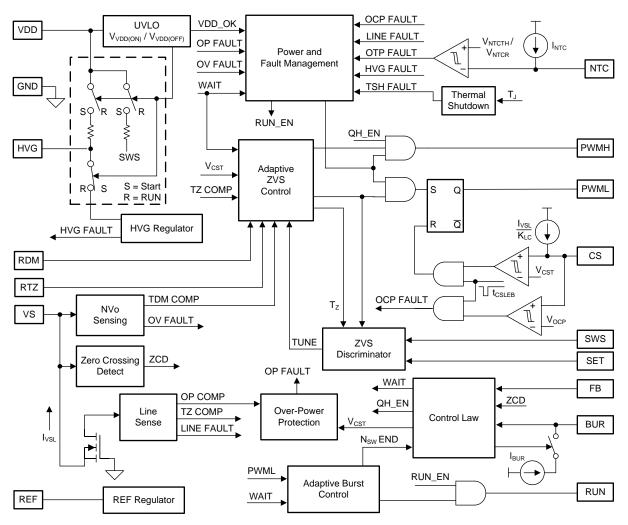

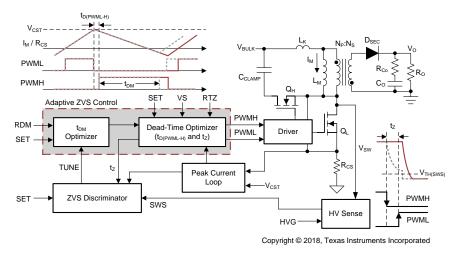

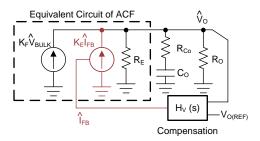

The UCC28780 is a transition-mode (TM) active clamp flyback (ACF) controller, equipped with advanced control schemes to enable significant size reduction of passive components for higher power density and higher average efficiency. The control law is optimized for Silicon (Si) and Gallium Nitride (GaN) power FETs in a half-bridge configuration and is capable of driving high-frequency AC/DC converters up to 1 MHz. The zero voltage switching (ZVS) control of the UCC28780 is capable of auto-tuning the on-time of a high-side clamp switch (Q<sub>H</sub>) by using a unique lossless ZVS sensing network connected between the switch-node voltage (V<sub>SW</sub>) and SWS pin. The ACF controller is designed to adaptively achieve targeted full-ZVS or partial-ZVS conditions for the low-side main switch (Q<sub>L</sub>) with minimum circulating energy over wide operating conditions. Auto-tuning eliminates the risk of losing ZVS due to component tolerance, input/output voltage changes, and temperature variations, since the Q<sub>H</sub> on-time is corrected cycle-by-cycle.

Dead-times between PWML (controls  $Q_L$ ) and PWMH (controls  $Q_H$ ) are optimally adjusted to help minimize the circulating energy required for ZVS. Therefore, the overall system efficiency can be significantly improved and more consistent efficiency can be obtained in mass production of the soft-switching topology. The programming features of the RTZ, RDM, BUR, and SET pins provide rich flexibility to optimize the power stage efficiency across a range of output power and operating frequency levels.

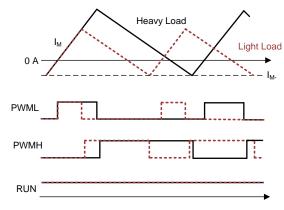

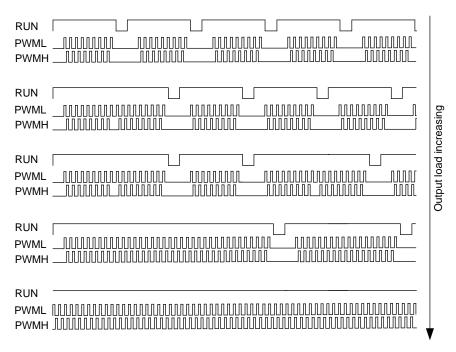

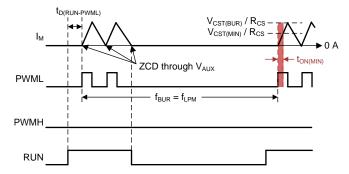

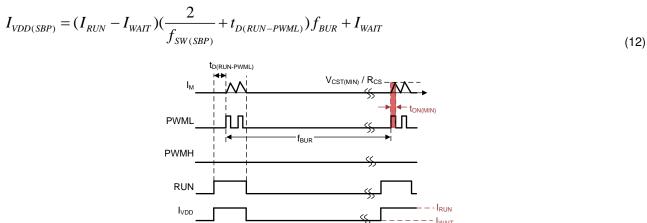

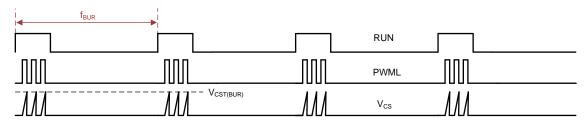

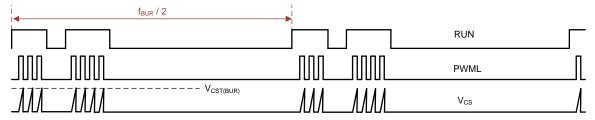

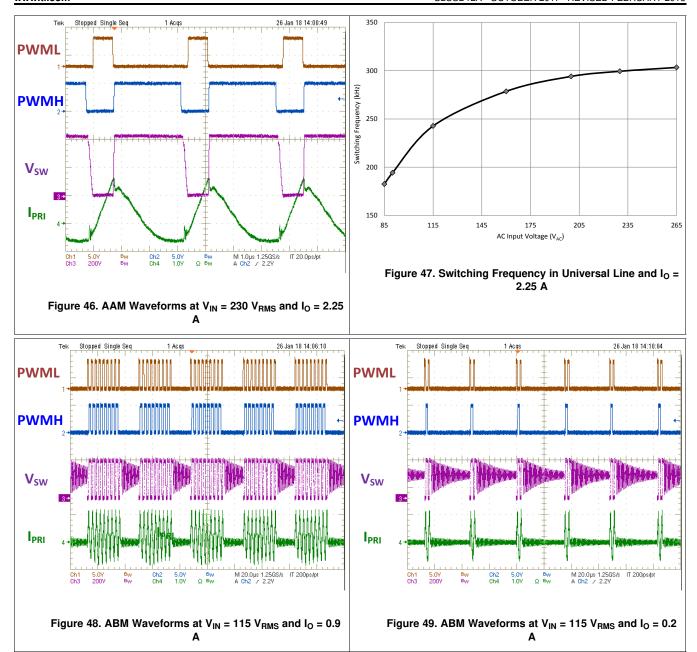

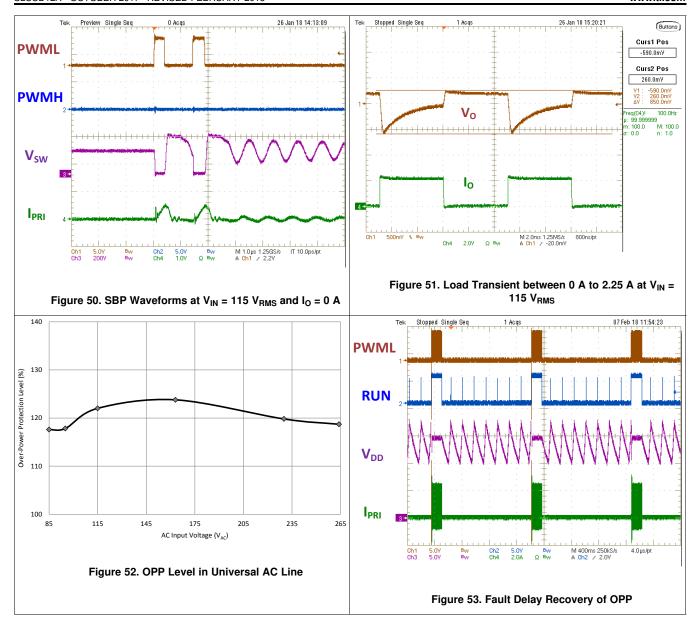

The UCC28780 uses four different operating modes to maximize efficiency over wide load and line ranges. Adaptive amplitude modulation (AAM) adjusts the peak primary current at the higher load levels. Adaptive burst mode (ABM) modulates the pulse count of each burst packet in the medium to light load range. Low power mode (LPM) reduces the peak primary current of each two-pulse burst packet in the very light load range. Standby power (SBP) mode minimizes the loss during no load conditions.

The unique burst mode control of the UCC28780 maximizes the light load efficiency of the ACF power stage, while avoiding the concerns of conventional burst operation - such as output ripple and audible noise. The burst control provides an enable signal through the RUN pin to dynamically manage the static current of the half-bridge driver and also adaptively disables the on-time of Q<sub>H</sub>. These functions can be used to manage the quiescent power consumed by the half-bridge driver, further improving the converter's light-load efficiency and reducing its standby power.

Instead of using a conventional high-voltage resistor, the UCC28780 starts up the VDD supply voltage with an external high-voltage depletion-mode MOSFET between the SWS pin and the switch node. Fast startup is achieved with low standby power overhead. Moreover, the HVG pin controls the gate of the depletion-mode FET to also allow this MOSFET to be used in a lossless ZVS sensing. This arrangement avoids additional sensing devices.

The UCC28780 also integrates a robust set of protection features tailored to maximize the reliability. These features include internal soft start, brown in/out, output over-voltage, output over-power, system over-temperature, switch over-current, output short-circuit protection, and pin open/short.

# 7.2 Functional Block Diagram

Copyright © 2018, Texas Instruments Incorporated

Copyright © 2017–2018, Texas Instruments Incorporated

# 7.3 Detailed Pin Description

#### 7.3.1 BUR Pin (Programmable Burst Mode)

The voltage at the BUR pin ( $V_{BUR}$ ) sets a target peak current threshold ( $V_{CST(BUR)}$ ) which programs the onset of adaptive burst mode (ABM) and determines the clamped peak current level of switching cycles in each burst packet. When  $V_{BUR}$  is designed higher, ABM will start at heavier output load conditions with higher peak current, so the benefit is the higher light-load efficiency but the side effect is a larger burst output voltage ripple. Therefore, 50% to 60% of output load at high line is the recommended highest load condition entering into ABM ( $I_{O(BUR)}$ ) for both Si and GaN-based ACF designs. The gain between  $V_{BUR}$  and  $V_{CST(BUR)}$  is a constant gain of  $K_{BUR-CST}$ , so setting  $V_{CST(BUR)}$  just requires properly selecting the resistor divider on the BUR pin formed by  $R_{BUR1}$  and  $R_{BUR2}$ .  $V_{BUR}$  should be set between 0.7 V and 2.4 V. If  $V_{BUR}$  is less than 0.7 V,  $V_{CST(BUR)}$  holds at 0.7 V /  $K_{BUR-CST}$ .

$$R_{BUR2} = \frac{R_{BUR1}K_{BUR-CST}V_{CST(BUR)}}{V_{REF} - K_{BUR-CST}V_{CST(BUR)}} = \frac{4 \times R_{BUR1}V_{CST(BUR)}}{5V - 4 \times V_{CST(BUR)}}$$

$$(1)$$

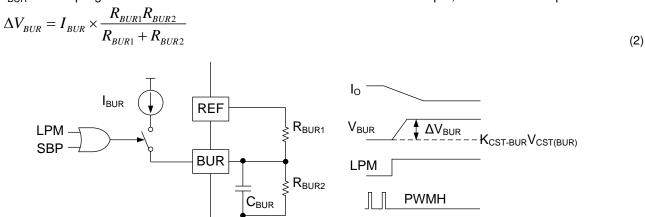

In order to enhance the mode transition between ABM and Low Power Mode (LPM), a programmable offset voltage ( $\Delta V_{BUR}$ ) is generated on top of the  $V_{BUR}$  setting in ABM through an internal 2.7- $\mu$ A current source ( $I_{BUR}$ ), as shown in Figure 12. In ABM mode,  $V_{BUR}$  is set through the resistor voltage divider to fulfill the target average efficiency. After transition from ABM to LPM, the current source is enabled in LPM and flows out of the BUR pin, so  $\Delta V_{BUR}$  can be programmed based on the Thevenin resistance on the BUR pin, which can be expressed as

Copyright © 2018, Texas Instruments Incorporated

Figure 12. Hysteresis Voltage Generation on BUR Pin

When  $V_{BUR}$  becomes higher after transition to LPM, the initial peak magnetizing current in LPM is increased with larger energy per switching cycle in a burst packet, which forces UCC28780 to stay in LPM with a higher feedback current than ABM. If  $\Delta V_{BUR}$  is designed too small, it is possible that mode toggling between LPM and ABM can occur resulting in audible noise. For that situation,  $\Delta V_{BUR}$  greater than 100 mV is recommended. To minimize the noise coupling effect on  $V_{BUR}$ , a filter capacitor on the BUR pin ( $C_{BUR}$ ) may be needed.  $C_{BUR}$  needs to be properly designed to minimize the delay of generating  $\Delta V_{BUR}$  in time during mode transition. It is recommended that  $C_{BUR}$  should be sized small enough to ensure  $\Delta V_{BUR}$  settles within 40  $\mu$ s, corresponding to the burst frequency of 25 kHz in LPM ( $f_{LPM}$ ). Based on three RC time constants representing 95% of a settled steady state value from a step response, the design guide of  $C_{BUR}$  is expressed as

$$C_{BUR} \le 40 \,\mu s \times \frac{R_{BUR1} + R_{BUR2}}{3R_{BUR1}R_{BUR2}} \tag{3}$$

#### 7.3.2 FB Pin (Feedback Pin)

The FB pin connects to the collector of an optocoupler output transistor through an external current-limiting resistor (R<sub>FB</sub>). Depending on the operating mode, the controller uses different content of the collector current flowing out of the FB pin (IFB) to regulate the output voltage. For the operating modes based on peak current control,  $I_{FB}$  is converted into an internal peak current threshold ( $V_{CST}$ ) to modulate the amplitude of the current sense signal on the CS pin. For example, when the output voltage ( $V_O$ ) is lower than the regulation level set by the shunt regulator, the "current level" of IFB moves to lower value, so V<sub>CST</sub> goes up to deliver more power to the output load.

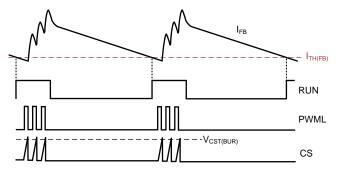

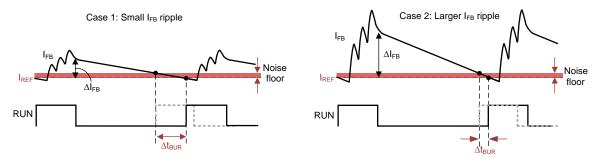

As the burst control takes over the  $V_O$  regulation, where  $V_{CST}$  is clamped to  $V_{CST(BUR)}$ , the "current ripple" of  $I_{FB}$  is used to modulate burst off time, as shown in Figure 13. Specifically, after a group of pulses stop bursting, the output load current starts to discharge the output capacitor, which makes Vo start to decay. A proper type-III compensation on the secondary side of VO feedback loop minimizes the phase-delay between IFB current ripple and output voltage ripple. For a detailed design guide on each passive component of the type-III compensator, please refer to Application and Implementation. When the decaying I<sub>FB</sub> intersects with an internal reference current (I<sub>TH(FB)</sub>), the ripple regulator generates a new set of grouped burst pulses to deliver more power, which makes V<sub>O</sub> and I<sub>FB</sub> ripples move upward.

Figure 13. Concept of Burst Control

The nature of ripple-based control in burst mode requires additional care on the noise level of I<sub>FB</sub> to improve the consistency of burst off-time between burst cycles. Firstly, a high-quality ceramic-bypass capacitor between FB pin and REF pin (CFB) is required for decoupling IFB noise. A minimum of 100 pF is recommended. There is an internal 8-kΩ resistor (R<sub>FBI</sub>) connected to the FB pin that in conjunction with an external C<sub>FB</sub> forms an effective low-pass filter. On the other hand, too strong low-pass filtering with too large CFB can attenuate the IFB ripple creating slope distortion of the intersection point between IFB and ITH(FB), which can cause inconsistent burst offtimes, even though V<sub>O</sub> stays in regulation and the I<sub>FB</sub> noise is low. Secondly, since ABM utilizes the falling-edge burst-ripple content of I<sub>FB</sub> to determine the beginning of every burst packet, the operation is affected if the burstripple content of the output voltage is too small due to using a low-ESR output capacitor, or if there is an additional low-frequency ringing on the output ripple due to using a second-order output filter.

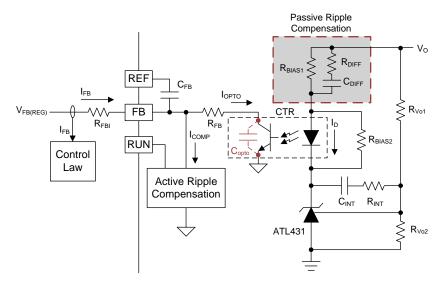

Compared with an electrolytic-type of output capacitor, the advantage of ACF using a low-ESR output capacitor such as a polymer capacitor is to minimize the switching-ripple content of the output voltage to meet the ripple specification, but the burst-ripple content is also reduced. Therefore, the switching ripple and noise on IFB may be very close to I<sub>TH(FB)</sub>, which triggers the next burst event prematurely. For a converter using a second-order output filter, a  $\pi$  filter design as example, even though both switching-ripple and burst-ripple contents are further attenuated, additional low-frequency ringing caused by the resonance between the output filter inductor and one of the output filter capacitors is generated, which may trigger the next burst event too early as well. Therefore, applying an active ripple compensation (ARC) technique is recommended to generate a noise-free burst ripple artificially to stabilize the ABM operation of ACF using either a low-ESR output capacitor or a second-order output filter.

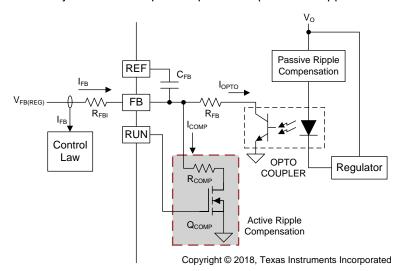

Figure 14 illustrates the implementation of ARC formed by a high-impedance resistor (R<sub>COMP</sub>) in series with a small-signal enhancement MOSFET (Q<sub>COMP</sub>) where its gate is controlled by the RUN pin of UCC28780. When RUN pin is in a high state which turns on  $Q_{COMP}$ ,  $R_{COMP}$  connected to FB pin creates a compensation current ( $I_{COMP}$ ), with a magnitude around  $V_{FB}$  /  $R_{COMP}$ . When RUN pin changes to a low state which turns off  $Q_{COMP}$ , R<sub>COMP</sub> and the drain-source junction capacitor of Q<sub>COMP</sub> creates a slow falling edge of I<sub>COMP</sub>, with a ramp slope

Copyright © 2017-2018, Texas Instruments Incorporated

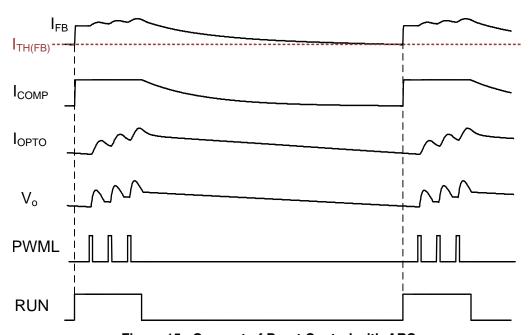

dependent on the RC time constant. Then, the summation of the current from the optocoupler ( $I_{OPTO}$ ) and  $I_{COMP}$  becomes the total feedback current out of FB pin ( $I_{FB}$ ) to compare with  $I_{TH(FB)}$ . As the ARC operation in Figure 15 explains, the magnitude of  $I_{COMP}$  helps to push any switching and noise content of  $I_{FB}$  away from  $I_{TH(FB)}$ , and the slow falling edge of  $I_{COMP}$  further pushes the undesirable ripple content away from  $I_{TH(FB)}$ , especially the low-frequency ringing of the  $\pi$  output filter. The magnitude of  $I_{COMP}$  can be adjusted by  $R_{COMP}$ , and 1 M $\Omega$  to 2 M $\Omega$  is the recommended value which injects around 2  $\mu A$  to 4  $\mu A$  of compensation ripple current into the loop.

Figure 14. Implementation of Active Ripple Compensation (ARC)

Figure 15. Concept of Burst Control with ARC

# 7.3.3 VDD Pin (Device Bias Supply)

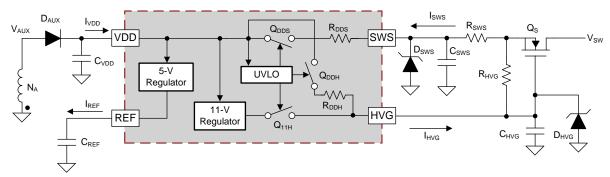

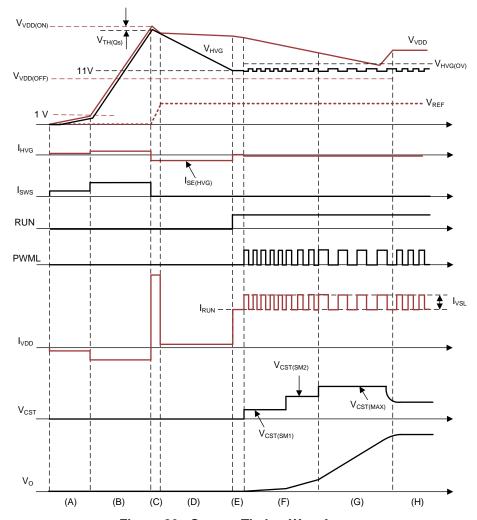

The VDD pin is the primary bias for the internal 5-V REF regulator, internal 11-V HVG regulator, other internal references, and the undervoltage lock-out (UVLO) circuit. As shown in Functional Block Diagram, the UVLO circuit connected to the VDD pin controls three power-path switches among VDD, HVG, and SWS pins, in order to allow  $Q_S$  to be able to perform both  $V_{VDD}$  startup and  $V_{SW}$  sensing for ZVS control after startup. During startup, SWS and HVG pins are connected to VDD pin allowing an external depletion-mode MOSFET ( $Q_S$ ) to charge the

VDD capacitor ( $C_{VDD}$ ) from the switch-node voltage ( $V_{SW}$ ). After VDD startup competes, the ZVS discriminator block is enabled, so as switching logics. Then, the transformer starts delivering energy to the output capacitor ( $C_O$ ) every switching cycle, so both output voltage ( $V_O$ ) and auxiliary winding voltage ( $V_{AUX}$ ) increase. As  $V_{AUX}$  is high enough, the auxiliary winding will take over to power  $V_{VDD}$ . The UVLO circuit provides a turn-on threshold of  $V_{VDD(ON)}$  at 17.5 V and turn-off threshold of  $V_{VDD(OFF)}$  at 9.8 V. The range can accommodate lower values of VDD capacitor ( $C_{VDD}$ ) and support shorter power-on delays. 38-V maximum operating level on  $V_{VDD}$  alleviates concerns with leakage energy charging of  $C_{VDD}$  and gives added flexibility when a varying output voltage must be supported.

As  $V_{VDD}$  reaches  $V_{VDD(ON)}$ , SWS pin is disconnected from the VDD pin, so the  $C_{VDD}$  size has to be sufficient to hold  $V_{VDD}$  higher than  $V_{VDD(OFF)}$  until the positive auxiliary winding voltage is high enough to take over bias power delivery during  $V_O$  soft start. Therefore, the calculation of minimum capacitance  $(C_{VDD(MIN)})$  needs to consider the discharging effect from the sink current of the UCC28780 during switching in its run state  $(I_{RUN(SW)})$ , the average operating current of driver  $(I_{DR})$ , and the average gate charge current of half-bridge FETs  $(I_{Qg})$  throughout the longest time of  $V_O$  soft start  $(t_{SS(MAX)})$ .

$$C_{VDD(MIN)} = \frac{(I_{RUN(SW)} + I_{DR} + I_{Qg})t_{SS(MAX)}}{V_{VDD(ON)} - V_{VDD(OFF)}}$$

$$(4)$$

$t_{SS(MAX)}$  estimation should consider the averaged soft-start current ( $I_{SEC(SS)}$ ) on the secondary side of ACF, the constant-current output load ( $I_{O(SS)}$ ) (if any), maximum output capacitance ( $C_{O(MAX)}$ ), and a 1-ms time-out potentially being triggered in the startup sequence.

$$t_{SS(MAX)} = \frac{C_{O(MAX)}V_{O}}{I_{SEC(SS)} - I_{O(SS)}} + 1ms$$

(5)

During  $V_O$  soft start,  $V_{CST}$  reaches the maximum current threshold on the CS pin  $(V_{CST(MAX)})$ , so  $I_{SEC(SS)}$  at the minimum voltage of the input bulk capacitor  $(V_{BULK(MIN)})$  can be approximated as:

$$I_{SEC(SS)} = \frac{N_{PS}V_{CST(MAX)}}{2R_{CS}} \frac{V_{BULK(MIN)}}{V_{BULK(MIN)} + N_{PS}(V_O + V_F)}$$

(6)

where  $R_{CS}$  is the current sense resistor,  $N_{PS}$  is primary-to-secondary turns ratio, and  $V_F$  is the forward voltage drop of the secondary rectifier.

For details of the startup sequencing, one can refer to the Device Functional Modes of this datasheet.

## 7.3.4 REF Pin (Internal 5-V Bias)

The output of the internal 5-V regulator of the controller is connected to this pin. It requires a high-quality ceramic-bypass capacitor ( $C_{REF}$ ) to GND for decoupling switching noise and lowering the voltage droop as the controller transitions from wait state to run state. The minimum  $C_{REF}$  value is 0.1  $\mu$ F, and a high quality dielectric material should be used, such as a X7R. The output short current ( $I_{S(REF)}$ ) of the REF regulator is self-limited to approximately 14 mA. 5-V bias is only available after the under-voltage lock-out (UVLO) circuit enables the operation of UCC28780 after  $V_{VDD}$  reaches  $V_{VDD(ON)}$ .

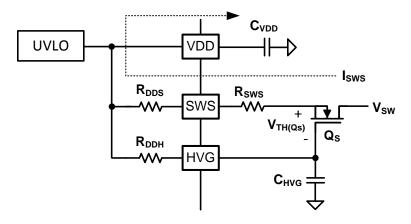

#### 7.3.5 HVG and SWS Pins

The HVG pin provides a controlled voltage to the gate of the depletion-mode MOSFET ( $Q_S$ ), enabling  $Q_S$  to serve both  $V_{VDD}$  startup and lossless ZVS sensing from the high-voltage switch node ( $V_{SW}$ ). During  $V_{VDD}$  startup, the UVLO circuit commands two power-path switches connecting SWS and HVG pins to VDD pin with two internal current-limit resistors ( $R_{DDS}$  and  $R_{DDH}$ ) separately, as shown in Figure 16. In this configuration,  $Q_S$  behaves as a current source to charge the VDD capacitor ( $C_{VDD}$ ).  $R_{DDS}$  is set at 12 k $\Omega$  when  $V_{VDD}$  is below 1 V to limit the maximum fault current under VDD pin short events.  $R_{DDS}$  is reduced to 1 k $\Omega$  when  $V_{VDD}$  rises above 1 V to allow  $V_{VDD}$  to charge faster. The maximum charge current ( $I_{SWS}$ ) is affected by  $I_{DDS}$ , the external series resistance ( $I_{SWS}$ ) from SWS pin to  $I_{SWS}$  and the threshold voltage of  $I_{SWS}$ 0 is  $I_{SWS}$ 1 can be calculated as

$$I_{SWS} = \frac{V_{TH(Qs)}}{R_{DDS} + R_{SWS}} \tag{7}$$

# TEXAS INSTRUMENTS

# **Detailed Pin Description (continued)**

Copyright © 2018, Texas Instruments Incorporated

Figure 16. Operation of the VDD Startup Circuit

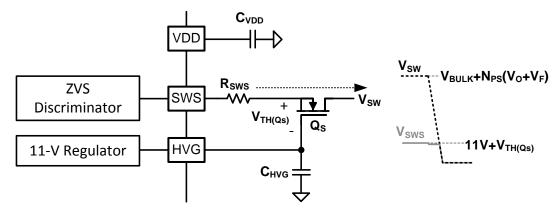

After  $V_{VDD}$  reaches  $V_{VDD(ON)}$ , the two power-path switches open the connections among SWS, HVG, and VDD pins. At this point, a third power-path switch connects an internal 11-V regulator to the HVG pin for configuring  $Q_S$  to perform lossless ZVS sensing. As  $Q_S$  gate is fixed at 11 V and the drain pin voltage of  $Q_S$  becomes higher than the sum of  $Q_S$  threshold voltage  $(V_{TH(Q_S)})$  and the 11-V gate voltage,  $Q_S$  turns off and the source pin voltage of  $Q_S$  can no longer follow the drain pin voltage change, so this gate control method makes  $Q_S$  act as a high-voltage blocking device with the drain pin connected to  $V_{SW}$ . When the controller is switching,  $V_{SW}$  can be lower than 11 V, so  $Q_S$  turns on and forces the source pin voltage to follow  $V_{SW}$ , becoming a replica of the  $V_{SW}$  waveform at the lower voltage level, as illustrated in Figure 17.

The limited window for monitoring the  $V_{SW}$  waveform suffices for ZVS control of the UCC28780, since the ZVS tuning threshold ( $V_{TH(SWS)}$ ) is lower than that, which is at 9 V for  $V_{SET}$  = 5 V and at 4 V for  $V_{SET}$  = 0 V. The 9-V threshold is the auto-tuning target of the internal adaptive ZVS control loop for realizing a partial ZVS condition on the ACF using Si primary switches. On the other hand, performing full ZVS operation is more suitable for the ACF with GaN primary switches. The 4-V threshold can help to better compensate sensing delay between  $V_{SW}$  and the SWS pin more than using a 0-V threshold. The internal 11-V regulator requires a high quality ceramic bypass capacitor ( $C_{HVG}$ ) between the HVG pin and GND for noise filtering and providing compensation to the regulator circuitry. The minimum  $C_{HVG}$  value is 2.2 nF and an X7R-type dielectric capacitor is recommended. The controller enters a fault state if the HVG pin is open or shorted to GND during  $V_{VDD}$  start-up, or if  $V_{HVG}$  overshoot is higher than  $V_{HVG(OV)}$  of 13.8 V in run state. The output short current of HVG regulator ( $I_{S(HVG)}$ ) is self-limited to around 1mA.

Copyright © 2018, Texas Instruments Incorporated

Figure 17. ZVS Sensing by Reusing the VDD Startup Circuit

#### 7.3.6 RTZ Pin (Sets Delay for Transition Time to Zero)

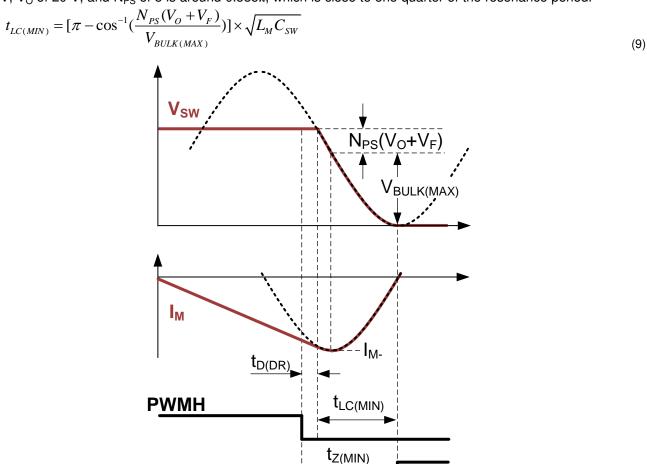

The dead-time between PWMH falling edge and PWML rising edge ( $t_Z$ ) serves as the wait time for  $V_{SW}$  transition from its high level down to the target ZVS point. Since the optimal  $t_Z$  varies with  $V_{BULK}$ , the internal dead-time optimizer automatically extends  $t_Z$  as  $V_{BULK}$  is less than the highest voltage of the input bulk capacitor ( $V_{BULK(MAX)}$ ). The circulating energy for ZVS can be further reduced, obtaining higher efficiency at low line versus a fixed dead-time over a wide line voltage range. A resistor on RTZ pin ( $R_{RTZ}$ ) programs the minimum  $t_Z$  ( $t_{Z(MIN)}$ ) at  $V_{BULK(MAX)}$ , which is the sum of the propagation delay of the high-side driver ( $t_{D(DR)}$ ) and the minimum resonant transition time of  $V_{SW}$  falling edge ( $t_{LC(MIN)}$ ).

$$R_{RTZ} = K_{TZ} \times t_{Z(MIN)} = K_{TZ} \times (t_{D(DR)} + t_{LC(MIN)})$$

(8)

where  $K_{TZ}$  is equal to  $11.2 \times 10^{11}$  (unit:  $F^{-1}$ ) for  $V_{SET} = 0$  V, and  $5.6 \times 10^{11}$  (unit:  $F^{-1}$ ) for  $V_{SET} = 5$  V. As illustrated in Figure 18, after PWMH turns off  $Q_H$  after  $t_{D(DR)}$  delay, the negative magnetizing current ( $i_{M^-}$ ) becomes an initial condition of the resonant tank formed by magnetizing inductance ( $L_M$ ) and the switch-node capacitance ( $C_{SW}$ ).  $C_{SW}$  is the total capacitive loading on the switch-node, including all junction capacitance ( $C_{OSS}$ ) of switching devices, stray capacitance of the boot-strap diode, intra-winding capacitance of the transformer, the snubber capacitor, and parasitic capacitance of the PCB traces between switch-node and ground. Unlike a conventional valley-switching flyback converter, the resonance of an active clamp flyback converter at high line does not begin at the peak of the sinusoidal trajectory. The transition time of  $V_{SW}$  takes less than half of the resonance period. The following  $t_{LC(MIN)}$  expression quantifies the transition time for  $R_{RTZ}$  calculation, where an arccosine term represents the initial angle at the resonance beginning. The value of  $\pi$  minus the arccosine term at  $V_{BULK(MAX)}$  of 375 V,  $V_{O}$  of 20 V, and  $N_{PS}$  of 5 is around 0.585 $\pi$ , which is close to one quarter of the resonance period.

Figure 18. RTZ Setting for the Falling-edge Transition of V<sub>SW</sub>

Product Folder Links: UCC28780

**PWML**

#### 7.3.7 RDM Pin (Sets Synthesized Demagnetization Time for ZVS Tuning)

The  $R_{RDM}$  resistor provides the power stage information to the  $t_{DM}$  optimizer for auto-tuning the on-time of PWMH to achieve ZVS within a given  $t_Z$  discharge time. The following equation calculates the resistance, based on the knowledge of the primary magnetizing inductance ( $L_M$ ), auxiliary-to-primary turns ratio ( $N_A/N_P$ ), the values of the resistor divider ( $R_{VS1}$  and  $R_{VS2}$ ) from the auxiliary winding to VS pin, and the current sense resistor ( $R_{CS}$ ). Among those parameters,  $L_M$  contributes the most variation due to its typically wider tolerance. The optimizer is equipped with wide enough on-time tuning range of PWMH to cover tolerance errors. Therefore, just typical values are enough for the calculation.

$$R_{RDM} = \frac{N_A R_{VS2}}{N_P (R_{VS1} + R_{VS2})} \frac{K_{DM} L_M}{R_{CS}}$$

(10)

where  $K_{DM}$  is equal to  $5 \times 10^9$  (unit:  $F^{-1}$ ) for both  $V_{SET} = 5$  V and 0 V.

# 7.3.8 RUN Pin (Driver Enable Pin)

The RUN pin is a logic-level output signal to enable the gate driver. It generates a 5-V logic output when the driver should be active, and pulls down to less than 0.5 V when the driver should be disabled. During burst mode operation, the RUN pin serves as a power management function to dynamically reduce the static current of the driver, so light-load efficiency can be further improved and standby power can be minimized. In addition, there are two delays between RUN going high to first PWML pulse going high in each burst packet. The first delay is a fixed 2.2- $\mu$ s delay time, intended to provide an appropriate wake-up time for UCC28780 and the gate driver to transition from a wait state to a run state. The second delay is another 2.2- $\mu$ s timeout,  $t_{ZC}$  in the electrical table, intended to turn on the low-side switch of the first switching cycle per burst packet around the valley point of DCM ringing by waiting for the zero crossing detection (ZCD) on the auxiliary winding voltage ( $V_{AUX}$ ). Therefore, the minimum total delay time is 2.2  $\mu$ s typically if ZCD is detected immediately after the first 2.2- $\mu$ s wake-up time, while the maximum total delay time is 4.4  $\mu$ s if ZCD is not triggered after the timeout. The total delay time with tolerance over temperature are listed as  $t_{D(RUN-PWML)}$  in the electrical table. RUN pin can also be used to control the external active ripple compensation network to enhance the stability of the burst regulation loop.

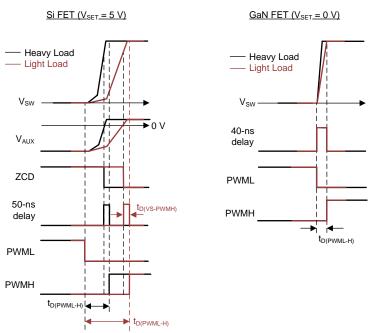

#### 7.3.9 SET Pin

Due to different capacitance non-linearity between Si and GaN power FETs as well as different propagation delays of their drivers, SET pin is provided to program critical parameters of UCC28780 for the two distinctive power stages. Firstly, this pin sets the zero voltage threshold  $(V_{TH(SWS)})$  at the SWS input pin to be two different auto-tuning targets for ZVS control. When SET pin is tied to GND,  $V_{TH(SWS)}$  is set at its low level of 4 V for realizing full ZVS, which allows the low-side switch  $(Q_L)$  to be turned on when the switch-node voltage drops close to 0 V. When SET pin is tied to REF pin,  $V_{TH(SWS)}$  is set at 9 V for implementing partial ZVS, which makes  $Q_L$  turn on at around 9V. Secondly, this pin generates different PWML-to-PWMH dead-time  $(t_{D(PWML-H)})$  to achieve ZVS on the high-side clamp switch  $(Q_H)$ . A fixed 40ns for  $V_{SET} = 0$  V and an adaptive adjustment for  $V_{SET} = 5$  V. Thirdly, this setting also selects the current sense leading edge blanking time  $(t_{CSLEB})$  to accommodate different delays of the gate drivers; 130 ns for  $V_{SET} = 0$  V and 200 ns for  $V_{SET} = 5$  V. Fourthly, the minimum PWML ontime  $(t_{ON(MIN)})$  in low-power mode and standby-power mode varies based on the driver capability; 65 ns for  $V_{SET} = 0$  V and 90 ns for  $V_{SET} = 5$  V. Finally, the maximum PWML on-time for detecting CS pin fault  $(t_{CSF})$ .  $t_{CSF}$  for  $V_{SET} = 5$  V  $t_{CSF}$  for  $t_{CSF}$  and  $t_{CSF}$  and  $t_{CSF}$  for  $t_{CSF}$  for  $t_{CSF}$  for  $t_{CSF}$  and  $t_{CSF}$  for  $t_{CSF}$  for  $t_{CSF}$  and  $t_{CSF}$  for  $t_{CSF}$  for  $t_{CSF}$  for  $t_{CSF}$  and  $t_{CSF}$  for  $t_{CS$

#### 7.4 Device Functional Modes

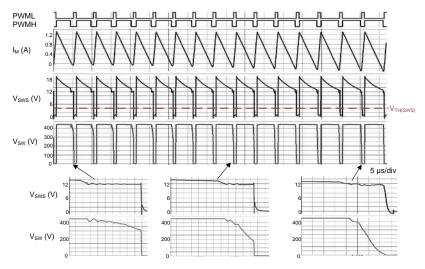

#### 7.4.1 Adaptive ZVS Control with Auto-Tuning

Figure 19 shows the simplified block diagram explaining the ZVS control of UCC28780. A high-voltage sensing network provides the replica of the switch node voltage waveform ( $V_{SW}$ ) with a limited "visible" voltage range that the SWS pin can handle. The ZVS discriminator identifies the ZVS condition and determines the adjustment direction for the on-time of PWMH ( $t_{DM}$ ) by detecting if  $V_{SW}$  reaches a predetermined ZVS threshold,  $V_{TH(SWS)}$ , within  $t_Z$ , where  $t_Z$  is the targeted zero voltage transition time of  $V_{SW}$  controlled by the PWMH-to-PWML dead-time optimizer.

In Figure 19,  $V_{SW}$  of the current switching cycle in the dashed line has not reached  $V_{TH(SWS)}$  after  $t_Z$  expires. The ZVS discriminator sends a TUNE signal to increase  $t_{DM}$  for the next switching cycle in the solid line, such that the negative magnetizing current ( $I_{M-}$ ) can be increased to bring  $V_{SW}$  down to a lower level in the same  $t_Z$ . After a few switching cycles, the  $t_{DM}$  optimizer settles and locks into ZVS operation of the low-side switch ( $Q_L$ ). In steady-state, there is a fine adjustment on  $t_{DM}$ , which is the least significant bit (LSB) of the ZVS tuning loop. This small change of  $t_{DM}$  in each switching cycle is too small to significantly move the ZVS condition away from the desired operating point. Figure 20 demonstrates how fast the ZVS control can lock into ZVS operation. Before the ZVS loop is settled, UCC28780 starts in a valley-switching mode as  $t_{DM}$  is not long enough to create sufficient  $I_{M-}$ . Within 15 switching cycles, the ZVS tuning loop settles and begins toggling  $t_{DM}$  with an LSB.

Figure 19. Block Diagram of Adaptive ZVS Control

Figure 20. Auto-Tuning Process of Adaptive ZVS Control

# **Device Functional Modes (continued)**

#### 7.4.2 Dead-Time Optimization

The dead-time optimizer in Figure 19 controls the two dead-times: the dead-time between PWMH falling edge and PWML rising edge ( $t_z$ ), as well as the dead-time between PWML falling edge and PWMH rising edge ( $t_{D(PWML-H)}$ ).

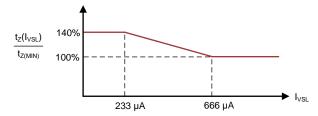

The adaptive control law for  $t_Z$  of UCC28780 utilizes the line feed-forward signal to extend  $t_Z$  as  $V_{BULK}$  reduces, as shown in Figure 21. The VS pin senses  $V_{BULK}$  through the auxiliary winding voltage  $(V_{AUX})$  when the low-side switch  $(Q_L)$  is on. The auxiliary winding creates a line-sensing current  $(I_{VSL})$  out of the VS pin flowing through the upper resistor of the voltage divider on VS pin  $(R_{VS1})$ . Minimum  $t_Z$   $(t_{Z(MIN)})$  is set at  $V_{BULK(MAX)}$  through the RTZ pin. When  $I_{VSL}$  is lower than 666  $\mu$ A,  $t_Z$  linearly increases and the maximum  $t_Z$  extension is 140% of  $t_{Z(MIN)}$ .

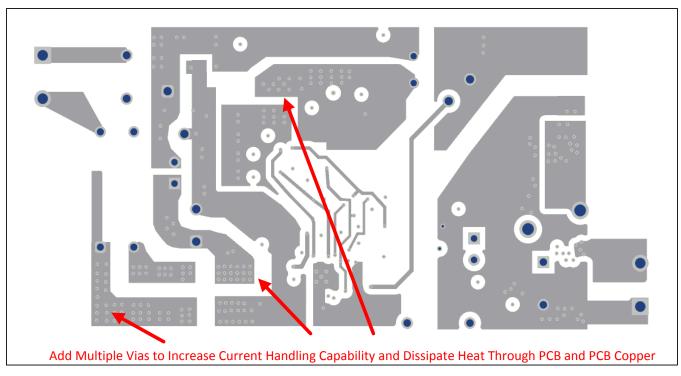

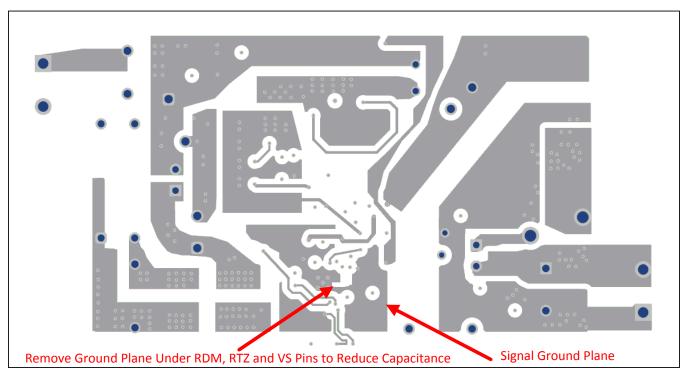

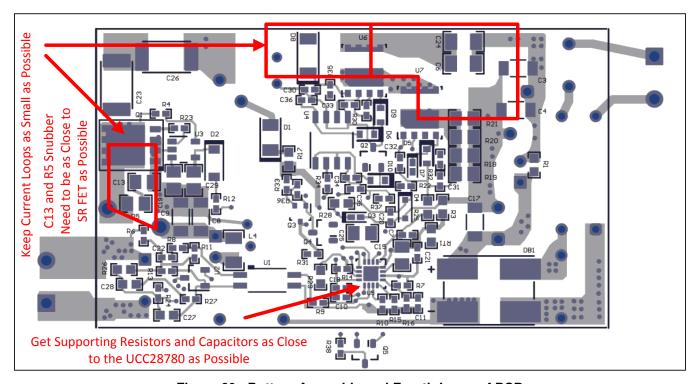

Figure 21. t<sub>Z</sub> Control Optimized for Wide Input Voltage Range