- PnP Card Autoconfiguration Sequence Compliant

- Supports Two Logical Devices

- Decodes 10-Bit I/O Address Location With Programmable 1-, 2-, 4-, 8-, 16-Byte Block Size

- Maps Interrupts to Six Interrupt Outputs IRQ3-IRQ7 and IRQ9

- Provides Simple 3-Terminal Interface to SGS-Thomson EEPROM 2K/4K ST93C56/66 or Equivalent

- 3-State Output EEPROM Interface Allows the EEPROM to be Accessed by Another Controller

- Provides Direct Connection to ISA/AT Bus

- Data and Interrupt Signals Require No Buffer

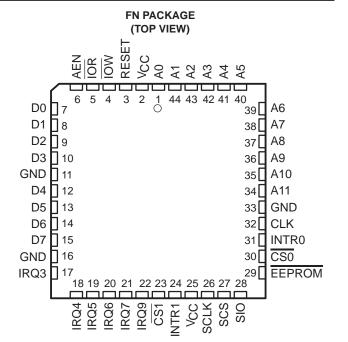

- Available in 44-Pin Plastic Leaded Chip Carrier (PLCC) and 48-Pin TQFP Package

#### description

The TL16PNP100A responds to the plug-andplay (PnP) autoconfiguration process. The process puts all PnP cards in a configuration mode, isolates one PnP card at a time, assigns a card-select number (CSN), and reads the card resource-data structure from the ST93C56/66 EEPROM. After the resource requirements and capabilities are determined for all cards, the process uses the CSN to configure the card by writing to the configuration registers. The TL16PNP100A implements configuration registers only for I/O applications with two logical devices, and DMA application support is not provided. Finally, the process activates the TL16PNP100A card and removes it from configuration mode. After the configuration process, the logic function can then start responding to industry standard architecture (ISA) bus cycles. The controller disables the EEPROM interface after the configuration is complete to allow another on-board controller to access the EEPROM.

NC – No internal connection

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

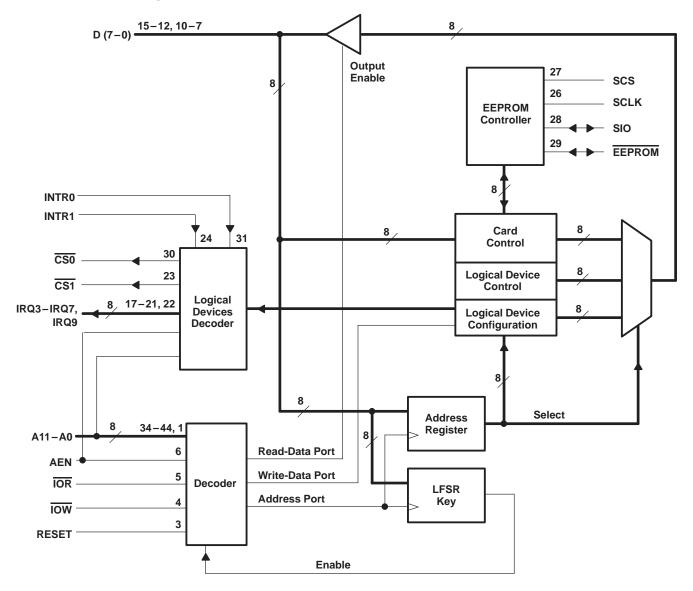

#### functional block diagram

NOTE A: Terminal numbers shown are for the FN package.

#### **Terminal Functions**

| TERMINAL         |               |                        |     |                                                                                                                                                                                                                                                                                          |

|------------------|---------------|------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | FN<br>NO.     | PT<br>NO.              | I/O | DESCRIPTION                                                                                                                                                                                                                                                                              |

| A0<br>A11-A1     | 1<br>44-34    | 42<br>41-33,<br>31, 30 | I   | 12-bit ISA address terminals. A0 and A1-A11 are used during the PnP autoconfiguration sequence.                                                                                                                                                                                          |

| AEN              | 6             | 48                     | ı   | ISA address enable. AEN is active during DMA operation and causes the controller to ignore the ISA transaction.                                                                                                                                                                          |

| CLK              | 32            | 28                     | I   | 22-MHz external clock input. CLK synchronizes PnP logic and generates a 0.68-MHz SCLK.                                                                                                                                                                                                   |

| CS0              | 30            | 26                     | 0   | Chip select. $\overline{CSO}$ is used for logical device number 0. The address decoder only decodes a 10-bit address for one I/O location with programmable block size.                                                                                                                  |

| CS1              | 23            | 18                     | 0   | Chip select. CS1 is used for logical device number 1. The address decoder only decodes a 10-bit address for one I/O location with programmable block size.                                                                                                                               |

| D0-D3<br>D4-D7   | 7–10<br>12–15 | 1-4<br>6,8-10          | I/O | Data bus. D0–D3 and D4–D7 with 3-state outputs provide a bidirectional path for data, control, and status information between the TL16PNP100A and the CPU. Output drive sinks 24 mA at 0.4 V and sources 12 mA at 2.4 V.                                                                 |

| EEPROM           | 29            | 25                     | I/O | EEPROM interface access enable. A 3-state bidirectional signal. When $\overline{\text{EEPROM}}$ is pulled low, the EEPROM interface is being accessed. A release state indicates the EEPROM interface is idle. A 100 $\mu$ A pullup transistor is connected internally to this terminal. |

| GND              | 11, 16,<br>33 | 5, 11,<br>29           |     | Ground (0 V). All terminals must be tied to GND for proper operation.                                                                                                                                                                                                                    |

| INTR0            | 31            | 27                     | Т   | Interrupt request from logical device number 0. INTR0 is an active-high signal.                                                                                                                                                                                                          |

| INTR1            | 24            | 19                     | I   | Interrupt request from logical device number 1. INTR1 is an active-high signal.                                                                                                                                                                                                          |

| IOR              | 5             | 47                     | I   | ISA read input                                                                                                                                                                                                                                                                           |

| ĪOW              | 4             | 46                     | I   | ISA write input                                                                                                                                                                                                                                                                          |

| IRQ3-IRQ<br>IRQ9 | 7 17-21<br>22 | 12–16<br>17            | 0   | Interrupt request. INTRn request is mapped to one of the IRQs based on the value of the content of the interrupt request level (0×70) register. Output drive sinks 24 mA at 0.4 V and sources 12 mA at 2.4 V. These terminals are 3-state outputs.                                       |

| RESET            | 3             | 45                     | I   | Reset. When active (high), RESET clears most logical device registers and puts the TL16PNP100A in the wait-for-key state. The CSN is reset to 0×0. All configuration registers are set to their power-up values.                                                                         |

| SCLK             | 26            | 22                     | I/O | Serial clock (3-state output path). SCLK controls the serial bus timing for address data. A 100- $\mu$ A pulldown transistor is connected internally to this terminal.                                                                                                                   |

| SCS              | 27            | 23                     | I/O | EEPROM chip select (3-state output). SCS controls the activity of the EEPROM. A 100-μA pulldown transistor is connected internally to this terminal.                                                                                                                                     |

| SIO              | 28            | 24                     | I/O | Serial input/output. A 3-state bidirectional EEPROM I/O data path. A 100 $\mu$ A pulldown transistor is connected internally to this terminal.                                                                                                                                           |

| Vcc              | 2, 25         | 21, 43                 |     | 5-V supply voltage                                                                                                                                                                                                                                                                       |

100

111

SLLS200C - MARCH 1995 - REVISED SEPTEMBER 1997

#### detailed description

#### block size

This device generates read instructions for the EEPROM. Read transactions consist of read opcode, address and data cycles. Data cycles are comprised of 2-byte DATA. After power up resets, this device reads the programmable block size value from address zero in the EEPROM. Data [15:13] carries the block size information for logical device 0. Data [11–9] carries the block size information for the logical device 1 (see Table 1).

**BLOCK SIZE** DATA [15:13]/[11:9] ADDRESS BITS DECODED (Bytes) 000 A9-A0 1 001 2 A9-A1 010 4 A9-A2

8

16 (default)

Table 1. Block Size

#### **EEPROM** signal description

This device interfaces to SGS-Thomson's compatible EEPROM 2-Kbit ST93C56 or 4-Kbit ST93C66. After completion of the configuration sequence, it allows an optional on-board controller to access the EEPROM. During and after reset, TL16PNP100A gains access to the EEPROM by asserting EEPROM low, informing the optional on-board controller that it is accessing the EEPROM. After the configuration is complete, the device leaves the configuration mode, is activated, and is in the wait-for-key state. The EEPROM signal is then released and pulled high, SIO is released and pulled down, and SCS and SCLK are placed in the high-impedance state and pulled down.

A9-A3

A9-A4

#### NOTE

When the device enters the configuration mode again and leaves the wait-for-key state, it gains direct access to the EEPROM after the EEPROM signal is released. The wake command generates a read transaction from address 0×1, which is the beginning of the resource data of the card.

When the EEPROM signal is released, the interface of the EEPROM is idle. The TL16PNP100A drives the EEPROM signal low when the device enters the configuration mode again.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub>                | 0.5 V to 7 V  |

|------------------------------------------------------|---------------|

| Input voltage range at any input, V <sub>1</sub>     | 0.5 V to 7 V  |

| Output voltage range, V <sub>O</sub>                 | 0.5 V to 7 V  |

| Operating free-air temperature range, T <sub>A</sub> | 0°C to 70°C   |

| Storage temperature range, T <sub>stg</sub>          | 65°C to 150°C |

| Case temperature for 10 seconds: FN package          |               |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## TL16PNP100A STANDALONE PLUG-AND-PLAY (PnP) CONTROLLER

SLLS200C - MARCH 1995 - REVISED SEPTEMBER 1997

#### recommended operating conditions

|                                                | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------|------|-----|------|------|

| Supply voltage, V <sub>CC</sub>                | 4.75 | 5   | 5.25 | V    |

| High-level input voltage, VIH                  | 2    |     | VCC  | V    |

| Low-level input voltage, V <sub>I</sub> L      | -0.5 |     | 0.8  | V    |

| Operating free-air temperature, T <sub>A</sub> | 0    |     | 70   | °C   |

## electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                     | PARAMETER                           | TEST CON                                                                                              | DITIONS                                                 | MIN                  | TYP† | MAX | UNIT |

|---------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------|------|-----|------|

| \/a                 | High-level output voltage           | $I_{OH} = -4 \text{ mA (see Note 1)}$                                                                 |                                                         | V <sub>CC</sub> -0.8 |      |     | V    |

| VOH                 | r ligh-level output voltage         | $I_{OH} = -12 \text{ mA}$ (see Note 2                                                                 | 2)                                                      | VCC-0.8              |      |     | V    |

| \/a:                | Low level output voltage            | I <sub>OL</sub> = 4 mA (see Note 1)                                                                   |                                                         |                      |      | 0.5 | ٧    |

| VOL                 | Low-level output voltage            | I <sub>OL</sub> = 24 mA (see Note 2)                                                                  |                                                         |                      |      | 0.5 | V    |

| l <sub>l</sub>      | Input current                       | V <sub>CC</sub> = 5.25 V,<br>V <sub>I</sub> = 0 to 5.25 V,                                            | V <sub>SS</sub> = 0,<br>All other terminals<br>floating |                      |      | ±1  | μΑ   |

| loz                 | High-impedance-state output current | $V_{CC} = 5.25 \text{ V},$<br>$V_{O} = 0 \text{ to } 5.25 \text{ V},$<br>Pullup transistors and pullo | $V_{SS} = 0$ , down transistors are off                 |                      |      | ±10 | μΑ   |

| ICC                 | Supply current                      | V <sub>CC</sub> = 5.25 V,<br>All inputs at 0.8 V,<br>No load on outputs                               | $T_A = 25$ °C,<br>CLK at 4 MHz,                         |                      |      | 0.7 | mA   |

| C <sub>i(CLK)</sub> | Clock input capacitance             |                                                                                                       |                                                         |                      | 15   | 20  | pF   |

| fCLK                | Clock frequency                     |                                                                                                       |                                                         | 10                   |      | 22  | MHz  |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

NOTES: 1. These parameters apply for all outputs except D7–D0, IRQ3–IRQ7 and IRQ9.

# clock timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                                                                      | PARAMETER                                     | ALTERNATE<br>SYMBOL | TEST CONDITIONS | MIN | MAX  | UNIT |

|----------------------------------------------------------------------|-----------------------------------------------|---------------------|-----------------|-----|------|------|

| tw(SCLKH)                                                            | Pulse duration, SCLK high to low (see Note 3) | <sup>t</sup> CHCL   |                 | 250 |      | ns   |

| t <sub>W</sub> (SCLKL) Pulse duration, SCLK low to high (see Note 3) |                                               | <sup>t</sup> CLCH   | See Figure 8    | 250 |      | ns   |

| fCLK                                                                 | SCLK clock frequency (see Note 4)             |                     |                 | 0.3 | 0.68 | MHz  |

NOTES: 3. The ST93C56 chip select, S, must be brought low for a minimum of 250 ns (t<sub>SLSH</sub>) between consecutive instruction cycles according to the ST93C56 specification.

4. The SCLK signal is attained by internally dividing the frequency of the XIN signal by 32.

<sup>2.</sup> These parameters only apply for D7–D0 and IRQ3–IRQ7 and IRQ9 outputs.

## TL16PNP100A STANDALONE PLUG-AND-PLAY (PnP) CONTROLLER

SLLS200C - MARCH 1995 - REVISED SEPTEMBER 1997

## switching characteristics

|                                                                    | PARAMETER                                                 | ALTERNATE<br>SYMBOL | TEST CONDITIONS       | MIN | MAX | UNIT            |

|--------------------------------------------------------------------|-----------------------------------------------------------|---------------------|-----------------------|-----|-----|-----------------|

| t <sub>d1</sub>                                                    | Delay time, CS high to SCLK high                          | tSHCH               | See Figure 8          | 50  |     | ns              |

| t <sub>d2</sub>                                                    | Delay time, SIO input valid to SCLK high                  | <sup>t</sup> DVCH   | See Figure 8 and Fig- | 100 |     | ns              |

| <sup>t</sup> pd1                                                   | Propagation delay time, SCLK high to SIO level transition | <sup>†</sup> CHDX   | ure 9                 | 100 |     | ns              |

| t <sub>pd2</sub>                                                   | Propagation delay time, SCLK high to output valid         | <sup>t</sup> CHQV   |                       |     | 500 | ns              |

| t <sub>pd3</sub> Propagation delay time, SCLK low to CS transition |                                                           | tCLSL               | See Figure 9          |     | 2   | clock<br>period |

| t <sub>d3</sub>                                                    | Delay time, CS low to D/Q output Hi-Z                     | <sup>t</sup> SLQZ   |                       |     | 100 | ns              |

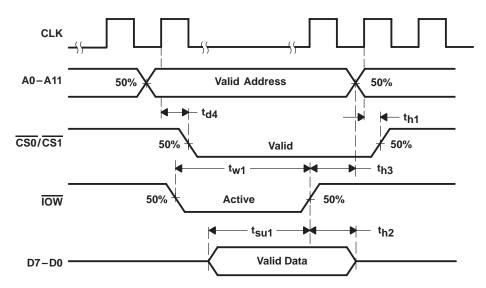

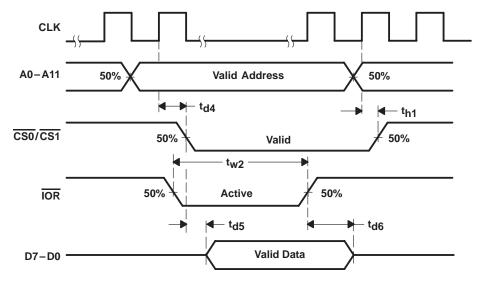

# system timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                  | PARAMETER                                                                                                                          | ALTERNATE<br>SYMBOL | TEST CONDITIONS                                                                            | MIN | MAX | UNIT             |

|------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------|-----|-----|------------------|

| t <sub>w1</sub>  | Pulse duration, write strobe, $\overline{IOW}$ low                                                                                 | tWR                 | See Figure 5                                                                               | 2   |     | clock<br>periods |

| t <sub>w2</sub>  | Pulse duration, read strobe, $\overline{IOR}$ low                                                                                  | t <sub>RD</sub>     | See Figure 6                                                                               | 3   |     | clock<br>periods |

| t <sub>w3</sub>  | Pulse duration, master reset                                                                                                       | t <sub>MR</sub>     |                                                                                            | 1   |     | μs               |

| t <sub>su1</sub> | Setup time, data D7–D0 valid before IOW↑                                                                                           | t <sub>DS</sub>     | See Figure 5                                                                               | 15  |     | ns               |

| th1              | Hold time, chip select $\overline{\text{CSx}}$ valid after address A0–A11 becomes invalid                                          | <sup>t</sup> CH     | From the first rising edge of XIN after address becomes invalid, See Figure 5 and Figure 6 |     | 20  | ns               |

| t <sub>h2</sub>  | Hold time, data valid D7–D0 after IOW↑                                                                                             | <sup>t</sup> DH     | See Figure 5                                                                               | 5   |     | ns               |

| t <sub>d4</sub>  | Delay time, CSx valid after address A0–A11 valid                                                                                   | <sup>t</sup> CSRW   | From the first rising edge of XIN after address valid,<br>See Figure 5 and Figure 6        |     | 30  | ns               |

| t <sub>h</sub> 3 | Hold time, address A0–A11 valid after IOW↑                                                                                         | tAW                 | See Figure 5                                                                               | 5   |     | ns               |

| <sup>t</sup> d5  | Delay time, IOR valid to data D0-D7 valid                                                                                          | tCSVD               | C <sub>L</sub> = 45 pF after 2 clock periods,<br>See Figure 6                              |     | 30  | ns               |

| <sup>t</sup> d6  | Delay time, IOR↑ to floating data D0–D7                                                                                            | <sup>t</sup> HZ     | C <sub>L</sub> = 45 pF,<br>See Figure 6                                                    |     | 20  | ns               |

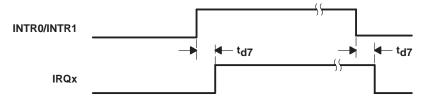

| <sup>t</sup> d7  | Delay time, INTR0 $\uparrow$ , INTR1 $\uparrow$ , INTR0 $\downarrow$ , or INTR1 $\downarrow$ to IRQ $\uparrow$ or IRQ $\downarrow$ |                     | See Figure 7                                                                               |     | 15  | ns               |

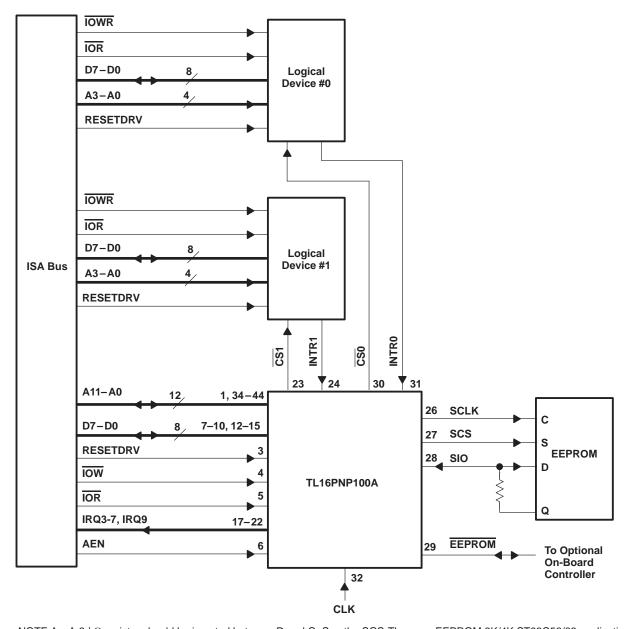

#### **APPLICATION INFORMATION**

NOTE A: A  $2-k\Omega$  resistor should be inserted between D and Q. See the SGS-Thomson EEPROM 2K/4K ST93C56/66 application report.

Figure 1. Basic TL16PNP100A Configuration

#### APPLICATION INFORMATION

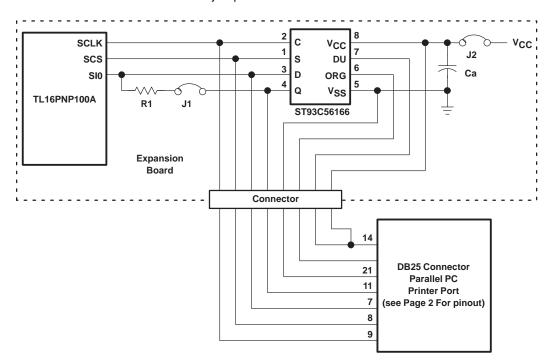

#### on-board EEPROM programming

This section describes a simple approach to programming the resource EEPROM in an expansion board that uses the TL16PNP100A. This approach involves utilizing a readily available standard EEPROM programmer and a ribbon cable in addition to minor additions to the expansion board.

#### hardware required for programming an expansion board EEPROM

The hardware required for programming an expansion board EEPROM is listed in the following bulleted list and shown in Figure 2.

- Ribbon cable with DB25 connector

- On-board ribbon connector and two jumper wires

Figure 2. Programming an Expansion Board EEPROM

#### APPLICATION INFORMATION

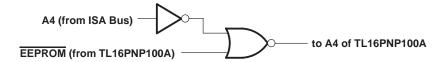

#### 32-byte I/O block size

The TL16PNP100A supports I/O block sizes ranging from 1 to 16 bytes. The following is one method to enable this device to support 32-byte I/O block size.

- Use only one logical device, and consequently one CS, either CS0 or CS1.

- In the first 2 bytes of the EEPROM select an I/O block size of 16 bytes for the selected logical device.

- In the EEPROM I/O descriptor resources, set the number of ports to 32 and the base address increment to 32.

- Use a NOR gate and an inverter to qualify address line A4 with the signal EEPROM as shown in Figure 3:

Figure 3. 32-Byte I/O Support

This operation forces A4 to 0 after completing the confirguration process (EEPROM signal is pulled up internally and goes high after the configuration process is complete.) When the address on the ISA bus is in the next 16 I/O addresses, only A4 changes from 0 to 1. Since A4 is being forced to 0, the TL16PNP100A thinks that the address is still in the 16-byte range and it asserts CS.

#### Example:

Using logical device 0:

- Connect CS0 directly to the CS input of the device.

- Insert the NOR gate as described above.

- In the EEPROM, set the I/O block size to 0x00E0 (Blk\_size = 16 bytes)

- The I/O descriptor in the EEPROM resources should be as follows:

| I/O Port | Descripto | or 1                                   |

|----------|-----------|----------------------------------------|

| db       | 047h      | ; Small item, type I/O port descriptor |

| db       | 000h      | ; Information, [0] = 0, 10 bit decode  |

| db       | 020h      | ; Minimum base address [7:0]           |

| db       | 002h      | ; Minimum base address [15:8]          |

| db       | 0e0h      | ; Maximum base address [7:0]           |

| db       | 003h      | ; Maximum base address [15:8]          |

| db       | 020h      | ; Base address increment = 32          |

| db       | 020h      | : Number of ports required = 32        |

#### APPLICATION INFORMATION

During configuration, assuming the system assigned the device address range 0x220 to 0x23F, <u>EEPROM</u> is low and A4 from the ISA bus passes to A4 on the TL16PNP100A. When configuration is complete <u>EEPROM</u> goes high, and A4 at the input of TL16PNP100A is reset to 0. Since the block size is 16, the TL16PNP100A looks at address bits A9 to A4. When the address on the A9 to A0 is in the range of 0x220 to 0x22F, A9 to A4 is as follows:

| A9 | A8 | A7 | A6 | A5 | A4 | A3 | A1 | A1 | A0 |

|----|----|----|----|----|----|----|----|----|----|

| 1  | 0  | 0  | 0  | 1  | 0  | Χ  | Χ  | Χ  | X  |

and  $\overline{CS0}$  is asserted low.

When the address is in the range of 0x230 to 0x23F, A9 to A4 is as follows:

| A9 | A8 | A7 | A6 | A5 | A4 | А3 | A1 | A1 | A0 |

|----|----|----|----|----|----|----|----|----|----|

| 1  | 0  | 0  | 0  | 1  | 1  | Χ  | Χ  | Χ  | Х  |

However, since A4 at the input of PNP100A is forced to 0, A9 to A4 is the same as in the range of 0x220 to 0x22F and TL16PNP100A asserts CS0 low.

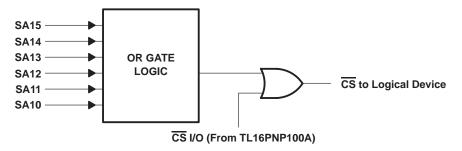

#### obtaining Windows 95™ logo

To obtain the Windows 95<sup>™</sup> logo, the card should be able to decode 16-bit I/O address. Since the TL15PNP100A uses 10-bit address decoding, an OR gate is needed on-board to decode the upper 6 address bits (SA15-SA10). The customer can use this gate by changing the I/O port descriptors in the EEPROM to reflect the 16-BIT ISA address. However, the customer must make sure that the upper 6 BITS in the I/O port descriptors have the same minimum and maximum base in the address registers.

For example, a logical device requires a base address between 0200h and 0300h with an 8-byte as a base alignment and one I/O port requested. (Notice that the requested base address is such that the upper six bits in the minimum and maximum base address ranges are the same as in this example all are considered to be zeros). To meet the requested resources, the following steps must be done:

1. Modify the gate logic on the board as shown in Figure 4.

Figure 4. Gate Logic Modification

All the signals on the left side of the OR gate are ISA signals.

Window 95 is a trademark of Microsoft Corporation.

### TL16PNP100A STANDALONE PLUG-AND-PLAY (PnP) CONTROLLER

SLLS200C - MARCH 1995 - REVISED SEPTEMBER 1997

#### **APPLICATION INFORMATION**

- 2. Program the I/O ports descriptors in the EEPROM as follows:

- 47h I/O port descriptors with 7 bytes

- 01h Information, bit 0 is set. The logical device is decoding full 16-bit ISA addresses

- 00h Address bits 7–0 for minimum configuration base I/O address

- 02h Address bits 15–8 for minimum configuration base I/O address

- 00h Address bits 7–0 for maximum configuration base I/O address

- 03h Address bits 15–8 for maximum configuration base I/O address

- 08h Base alignment, which has a block size of 8 bytes

- 01h One I/O port is needed

Using the above setup, the PnP BIOS maps the logical device to an address so that the upper six bits are always zeros. The 0 output from the OR gate occurs when SA15-SA10 and SAEN are low. This forces the logical device to check SA09-SA0 for a possible valid address.

#### PARAMETER MEASUREMENT INFORMATION

Figure 5. Write-Cycle Timing

Figure 6. Read-Cycle Timing

Figure 7. External Interrupt (EXINTR) Timing

#### PRINCIPLES OF OPERATION

#### PnP card configuration sequence

The PnP logic is quiescent on power up and must be enabled by software.

- 1. The initiation key places the PnP logic into configuration mode through a series of predefined writes to the ADDRESS port (see PnP Autoconfiguration Ports section).

- 2. A serial identifier is accessed in bit-sequence and used to isolate the ISA cards. Seventy-two READ\_DATA port reads are required to isolate each card.

- 3. Once isolated, a card is assigned a CSN that is later used to select the card. This assignment is accomplished by programming the CSN.

- 4. The PnP software then reads the resource-data structure on each card. When all resource capabilities and demands are known, a process of resource arbitration is invoked to determine resource allocation for each card.

- 5. All PnP cards are then activated and removed from the configuration mode. This activation is accomplished by programming the ACTIVE register.

#### PnP autoconfiguration ports

Three 8-bit ports (see Table 2) are used by the software to access the configuration space on each ISA PnP card. These registers are used by the PnP software to issue commands, check status, access the resource data information, and configure the PnP hardware.

The ports have been chosen so as to avoid conflicts in the installed base of ISA functions, while at the same time minimizing the number of ports needed in the ISA I/O space.

PORT NAME

LOCATION

TYPE

ADDRESS

0×0279 (printer status port)

Write only

WRITE\_DATA

0×0A79 (printer status port + 0×0800)

Write only

READ\_DATA

Relocatable in range 0×0203 to 0×03FF

Read only

**Table 2. Autoconfiguration Ports**

The PnP registers are accessed by first writing the address of the desired register to the ADDRESS port, followed by a read of data from the READ\_DATA port or a write of data to the WRITE\_DATA port. Once addressed, the desired register may be accessed through the WRITE\_DATA or READ\_DATA ports.

The ADDRESS port is also the destination of the initiation key writes (see PnP ISA specification).

The address of the READ\_DATA port is set by programming the SET RD\_DATA PORT register. When a card cannot be isolated for a given READ\_DATA port address, the READ\_DATA port address is in conflict. The READ\_DATA port address must then be relocated and the isolation process begun again. The entire range between 0×0203 and 0×3FF is available; however, in practice it is expected that only a few address locations are necessary before the software determines that PnP cards are not present.

#### PRINCIPLES OF OPERATION

#### PnP registers

PnP card standard registers are divided into three parts: card control, logical device control, and logical device configuration. There is exactly one of each card control register on each ISA card. Card control registers are used for global functions that control the entire card. Logical device control registers and logical device configuration registers are repeated for each logical device. Since the TL16PNP100A has two logical devices and they are intended only for I/O applications, not all the configuration registers are implemented.

#### PnP card control registers

The PnP card device control registers are listed in Table 3.

**Table 3. PnP Card Control Registers**

| ADDRESS PORT<br>VALUE | REGISTER NAME VALUE                                                                                                                                                                                                                                                                                                                             | READ/WRITE<br>CAPABILITY                                                                       | POWER UP                                   |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------|

| 0×00                  | SET RD_DATA PORT                                                                                                                                                                                                                                                                                                                                | Write only                                                                                     | 00 00 00 00                                |

|                       | Writing to this register modifies the address port used for rea allowed when the card is in the isolation state.  Bits 7–0 These bits become I/O port address bits 9                                                                                                                                                                            |                                                                                                | iting to this register is only             |

| 0×01                  | SERIAL ISOLATION                                                                                                                                                                                                                                                                                                                                | Read only                                                                                      | 00 00 00 00                                |

|                       | Reading from this register causes a card in the isolation state                                                                                                                                                                                                                                                                                 | e to compare one bit of the boar                                                               | d ID.                                      |

| 0×02                  | CONFIGURATION CONTROL                                                                                                                                                                                                                                                                                                                           | Write only                                                                                     | 0 00                                       |

|                       | This 3-bit register consists of three independent commands, register bits. These bits are automatically reset to 0 by the hat Bit 2 Writing a 1 to bit 1 causes the card to reset Bit 1 Writing a 1 to bit 2 causes the card preserved and the logical device is unaffect Bit 0 Writing a 1 to bit 0 resets the configuration CSN is preserved. | ardware after the commands exect its CSN and RD-DATA port to to enter the wait-for-key stated. | ecute.<br>zero.<br>ee, but the card CSN is |

| 0×03                  | WAKE[CSN]                                                                                                                                                                                                                                                                                                                                       | Write only                                                                                     | 00 00 00 00                                |

|                       | Writing to this register, when the write data bits 7–0 matches the to the isolation state when the write data for this command is z zero. The pointer to the SERIAL IDENTIFIER is reset. This re                                                                                                                                                | zero, or to the configuration state                                                            |                                            |

| 0×04                  | RESOURCE DATA                                                                                                                                                                                                                                                                                                                                   | Read only                                                                                      | 00 00 00 00                                |

|                       | Reading from this register reads the next byte of resource info polled until its bit 0 is reset before this register may be read.                                                                                                                                                                                                               | ormation from the EEPROM. The                                                                  | e STATUS register must be                  |

| 0×05                  | STATUS                                                                                                                                                                                                                                                                                                                                          | Read only                                                                                      | 0                                          |

|                       | Bit 0 A one-bit register that, when set, indic RESOURCE DATA register.                                                                                                                                                                                                                                                                          | cates it is okay to read the                                                                   | next data byte from the                    |

| 0×06                  | CARD-SELECT NUMBER                                                                                                                                                                                                                                                                                                                              | Read/write                                                                                     | 00 00 00 00                                |

|                       | Writing to this register sets a card CSN, which is uniquely assignant to be individually selected during a Wake[CSN] comman                                                                                                                                                                                                                     | 5                                                                                              | process. This allows each                  |

|                       | card to be individually selected during a wake[Con] comman                                                                                                                                                                                                                                                                                      | iu.                                                                                            |                                            |

| 0×07                  | LOGICAL DEVICE NUMBER                                                                                                                                                                                                                                                                                                                           | Read/write                                                                                     | 00 00 00 00                                |

#### PRINCIPLES OF OPERATION

#### PnP logical device control registers

The registers in Table 4 are repeated for each logical device. These registers control device functions, such as enabling the device onto the ISA bus.

**Table 4. PnP Logical Device Control Registers**

| ADDRESS PORT<br>VALUE |                                                  | REGISTER NAME VALUE                                                                                                                                                                                                                                                                                                              | READ/WRITE<br>CAPABILITY                                             | POWER UP                                              |

|-----------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|

| 0×30                  | ACTIVE                                           |                                                                                                                                                                                                                                                                                                                                  | Read/write                                                           | 00 00 00 00                                           |

|                       | Bits 7–1<br>Bit 0                                | trols whether the logical device is active on the These bits are reserved and must be set to ze If set, bit 0 activates the logical device. e does not respond to nor drive any ISA bus sign I.                                                                                                                                  | ero.                                                                 | activated, I/O range check                            |

| 0×31                  | I/O RANGE CHE                                    | CK                                                                                                                                                                                                                                                                                                                               | Read/write                                                           | 00 00 00 00                                           |

|                       | This register is u<br>Bits 7–2<br>Bit 1<br>Bit 0 | sed to perform a conflict check on the I/O port re.  These bits are reserved and must be set to ze If set to 1, bit 1 I/O range check is enabled. I/O inactive.  If set to 1, the logical device responds to I/O real I/O range check is in operation. If clear, the logical device responds to I/O range check is in operation. | ero.<br>O range check is only valid wad operations to its assigned I | when the logical device is 1/O range with a 0×55 when |

## PnP logical device configuration registers

The registers in Table 5 are repeated for each logical device and are used to program the ISA bus resource use of the device.

**Table 5. PnP Logical Device Configuration Registers**

| ADDRESS PORT<br>VALUE |                                                                                                                                                                                                                                                                                                                                                                                                                             | REGISTER NAME VALUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | READ/WRITE<br>CAPABILITY | POWER UP    |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|--|--|

| 0×60                  | I/O PORT BASE                                                                                                                                                                                                                                                                                                                                                                                                               | ADDRESS [15–8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Read/write               | 00          |  |  |

|                       | This register indicates the selected I/O lower limit address bits [15–8] for I/O descriptor 0. When the device is activated, if there is an address match to register 0×61 and an address match to this register, a chip select is generated to the logical device.  Bits 7–2  Bits 15–10 are not supported, since the logical device uses 10-bit address decoding.  Bits 1–0 have address bits 9 and 8 are indicated here. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |             |  |  |

| 0×61                  | I/O PORT BASE                                                                                                                                                                                                                                                                                                                                                                                                               | ADDRESS [7-0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Read/write               | 00 00 00 00 |  |  |

|                       | •                                                                                                                                                                                                                                                                                                                                                                                                                           | licates the selected I/O lower limit address<br>ess match to register 0×60 and an address<br>Address bits 7–0 are indicated here.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |             |  |  |

| 0×70                  | INTERRUPT RE                                                                                                                                                                                                                                                                                                                                                                                                                | EQUEST LEVEL SELECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Read/write               | 00 00       |  |  |

|                       | This register indicates the selected interrupt level.  Bits 3–0 These bits select the interrupt level. This device uses 6 interrupts from IRQ3 to IRQ7 and IRQ9.                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |             |  |  |

| 0×71                  | INTERRUPT RE                                                                                                                                                                                                                                                                                                                                                                                                                | EQUEST TYPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Read/write               | 00 00       |  |  |

|                       | This register ind<br>Bit 7–2<br>Bit 1<br>Bit 0                                                                                                                                                                                                                                                                                                                                                                              | licates which type of interrupt is used for the These bits are reserved.  This bit is level, where 1 = high, 0 = low This bit is type, where 1 = level, 0 = edgen to the type is the type in the type is the type |                          |             |  |  |

#### PRINCIPLES OF OPERATION

Table 6. PnP Logical Device Configuration Registers (continued)

| ADDRESS PORT<br>VALUE | REGISTER NAME VALUE                                                   | READ/WRITE<br>CAPABILITY | POWER UP    |

|-----------------------|-----------------------------------------------------------------------|--------------------------|-------------|

| 0×74                  | DMA CHANNEL SELECT 0                                                  | Read only                | 00 00 01 00 |

|                       | This register has a value of 4 to indicate that DMA is not supported. |                          |             |

| 0×75                  | DMA CHANNEL SELECT 1                                                  | Read only                | 00 00 01 00 |

|                       | This register has a value of 4 to indicate that DMA is not supported. |                          |             |

#### **EEPROM**

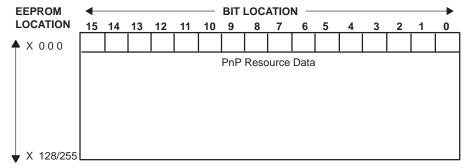

The TL16PNP100A has been designed to interface with the ST93C56/66 EEPROM (SGS-Thomson) or an equivalent. The EEPROM provides the block size for each device and the PnP resource data.

#### memory organization

The EEPROM should be organized as 128/255 words times 16 bits, so its ORG terminal should be connected to  $V_{CC}$  or left unconnected. The EEPROM memory organization is shown in Table 7.

Table 7. EEPROM Memory Organization

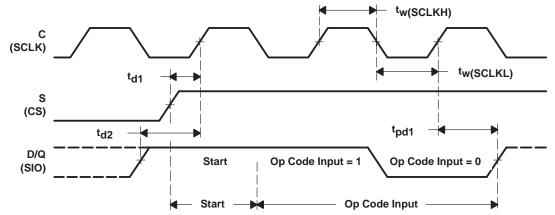

#### **EEPROM READ (see Figure 8 and Figure 9)**

This device only supports read transactions. The READ op code instruction (10) must be sent to the EEPROM. The op code is then followed by an 8-bit-long address for the 16-bit word. The READ op code with accompanying address directs the EEPROM to output serial data on the EEPROM data terminals D and Q, which is connected to the TL16PNP100A bidirectional serial data bus (SIO). Specifically, when a READ op code and address are received, the instruction and address are decoded and the addressed EEPROM data is transferred into an output shift register in the EEPROM. Each read transaction consists of a start bit, 2-bit op code (10), 8-bit address, and 16-bit data. The TL16PNP100A does not accommodate the EEPROM autoaddress next-word feature.

#### **READ op code transfer (see Figure 8)**

Initially, the EEPROM chip select signal (S) which connects to the TL16PNP100A EEPROM chip select (CS), is raised. The EEPROM data, D and Q, then sample the TL16PNP100A SIO line on the following rising edges of the TL16PNP100A serial clock, SCLK, until a 1 is sampled and decoded by the EEPROM as a start bit. The TL16PNP100A SCLK signal connects to the EEPROM clock C. The READ op code (10) is then sampled on the next two rising edges of SCLK. TL16PNP100A sources the op code at the falling edges of SCLK.

#### PRINCIPLES OF OPERATION

#### **READ op code transfer (continued)**

NOTE A: The corresponding TL16PNP100A terminal names are provided in parentheses. D/Q indicates that D and Q terminals in the EEPROMs are tied together through  $2-k\Omega$  resistor.

Figure 8. READ Op Code Transfer

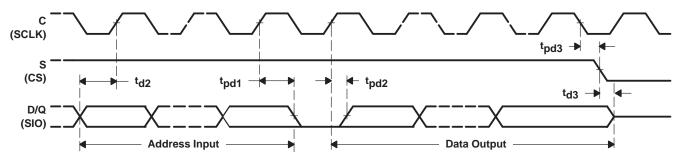

#### READ address and data transfer (see Figure 9)

After receiving the READ op code, the EEPROM samples the READ address on the next eight rising edges of SCLK. The device sources the address at the falling edge of SCLK. The EEPROM then sends out a dummy 0 bit on the D/Q line, which is followed by the 16-bit data word with the MSB first. Output data changes are triggered by the rising edges of SCLK. The data is also read by the TL16PNP100A on the rising edges of SCLK.

NOTE A: The corresponding terminal names are provided in parentheses. D/Q indicates that D and Q terminals in the EEPROMs are tied together through  $2-k\Omega$  resistor.

Figure 9. READ Address and Data Transfer

#### **MECHANICAL DATA**

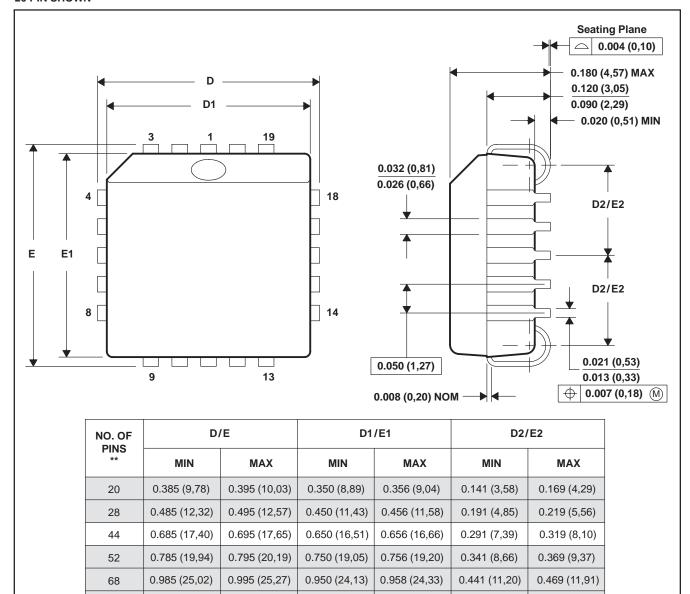

#### FN (S-PQCC-J\*\*)

#### **20 PIN SHOWN**

#### PLASTIC J-LEADED CHIP CARRIER

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

1.185 (30,10)

1.195 (30,35)

C. Falls within JEDEC MS-018

84

1.150 (29,21)

1.158 (29,41)

0.541 (13,74)

0.569 (14,45)

4040005/B 03/95

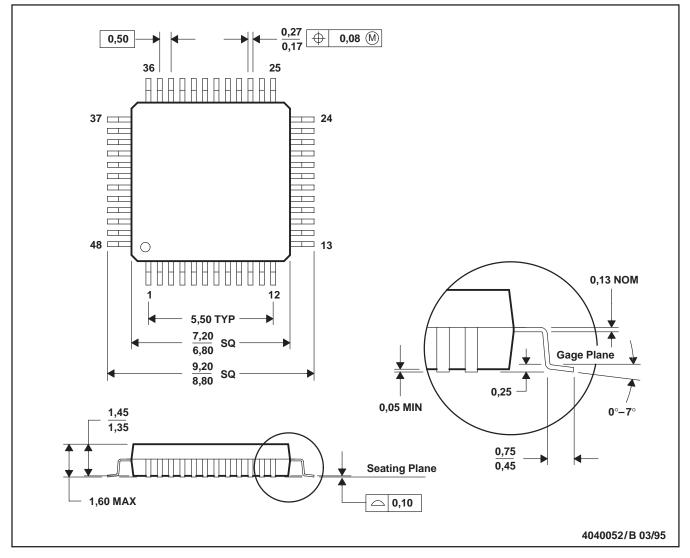

#### **MECHANICAL DATA**

#### PT (S-PQFP-G48)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MO-136

- D. This may also be a thermally-enhanced plastic package with leads connected to the die pads.

i.com 24-Jun-2005

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| TL16PNP100AFN    | OBSOLETE              | PLCC            | FN                 | 44                  | TBD                     | Call TI          | Call TI                      |

| TL16PNP100AFNR   | OBSOLETE              | PLCC            | FN                 | 44                  | TBD                     | Call TI          | Call TI                      |

| TL16PNP100APT    | OBSOLETE              | LQFP            | PT                 | 48                  | TBD                     | Call TI          | Call TI                      |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.