# **DSP** Microcomputer

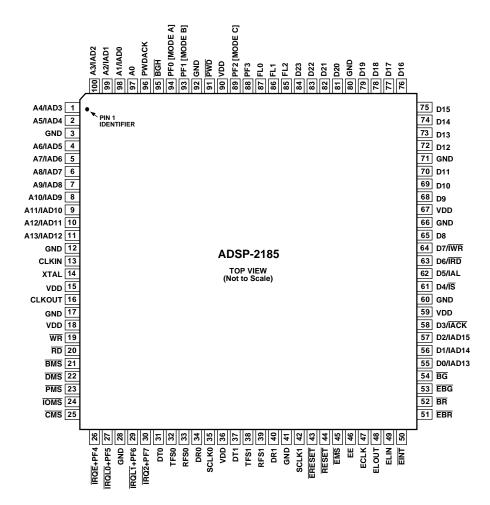

ADSP-2185

### **FEATURES**

### **PERFORM ANCE**

30 ns Instruction Cycle Time 33 MIPS Sustained Performance

Single-Cycle Instruction Execution

Single-Cycle Context Switch

3-Bus Architecture Allows Dual Operand Fetches in Every Instruction Cycle

**Multifunction Instructions**

Power-Down Mode Featuring Low CMOS Standby Power Dissipation with 100 Cycle Recovery from Power-Down Condition

Low Power Dissipation in Idle Mode

### **INTEGRATION**

ADSP-2100 Family Code Compatible, with Instruction Set Extensions

80K Bytes of On-Chip RAM, Configured as 16K Words On-Chip Program Memory RAM and 16K Words On-Chip Data Memory RAM

Dual Purpose Program Memory for Both Instruction and Data Storage

Independent ALU, Multiplier/ Accumulator and Barrel Shifter Computational Units

Two Independent Data Address Generators Powerful Program Sequencer Provides

Zero Overhead Looping Conditional Instruction Execution

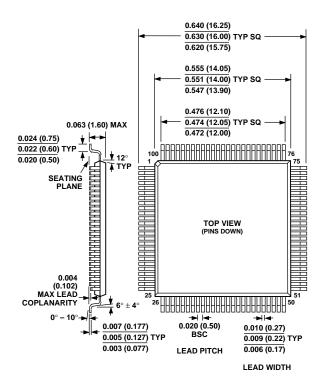

Programmable 16-Bit Interval Timer with Prescaler 100-Lead TQFP

### SYSTEM INTERFACE

- 16-Bit Internal DMA Port for High Speed Access to On-Chip Memory (Mode Selectable)

- 4 MByte Byte Memory Interface for Storage of Data Tables & Program Overlays

- 8-Bit DMA to Byte Memory for Transparent Program and Data Memory Transfers (Mode Selectable)

- I/O Memory Interface with 2048 Locations Supports Parallel Peripherals (Mode Selectable)

- Programmable Memory Strobe & Separate I/O Memory Space Permits "Glueless" System Design (Mode Selectable)

**Programmable Wait State Generation**

Two Double-Buffered Serial Ports with Companding Hardware and Automatic Data Buffering

Automatic Booting of On-Chip Program Memory from Byte-Wide External Memory, e.g., EPROM, or Through Internal DMA Port

\*ICE-Port is a trademark of Analog Devices, Inc.

# REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

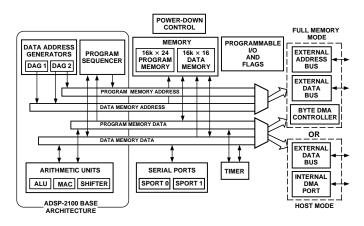

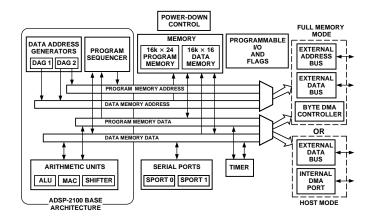

#### FUNCTIONAL BLOCK DIAGRAM

# Six External Interrupts

13 Programmable Flag Pins Provide Flexible System Signaling

UART Emulation through Software SPORT Reconfiguration ICE-Port™\* Emulator Interface Supports Debugging in Final Systems

### GENERAL NOTE

This data sheet represents production grade specifications for the ADSP-2185 (5 V).

# GENERAL DESCRIPTION

The ADSP-2185 is a single-chip microcomputer optimized for digital signal processing (DSP) and other high speed numeric processing applications.

The ADSP-2185 combines the ADSP-2100 family base architecture (three computational units, data address generators and a program sequencer) with two serial ports, a 16-bit internal DMA port, a byte DMA port, a programmable timer, Flag I/O, extensive interrupt capabilities and on-chip program and data memory.

The ADSP-2185 integrates 80K bytes of on-chip memory configured as 16K words (24-bit) of program RAM and 16K words (16-bit) of data RAM. Power-down circuitry is also provided to meet the low power needs of battery operated portable equipment. The ADSP-2185 is available in 100-pin TQFP package.

In addition, the ADSP-2185 supports new instructions, which include bit manipulations—bit set, bit clear, bit toggle, bit test—new ALU constants, new multiplication instruction (x squared), biased rounding, result free ALU operations, I/O memory transfers and global interrupt masking, for increased flexibility.

Fabricated in a high speed, double metal, low power, 0.5  $\mu m$  CMOS process, the ADSP-2185 operates with a 30 ns instruction cycle time. Every instruction can execute in a single processor cycle.

The ADSP-2185's flexible architecture and comprehensive instruction set allow the processor to perform multiple operations in parallel. In one processor cycle the ADSP-2185 can:

- generate the next program address

- fetch the next instruction

- perform one or two data moves

- update one or two data address pointers

- perform a computational operation

This takes place while the processor continues to:

- receive and transmit data through the two serial ports

- receive and/or transmit data through the internal DMA port

- receive and/or transmit data through the byte DMA port

- decrement timer

# Development System

The ADSP-2100 Family Development Software, a complete set of tools for software and hardware system development, supports the ADSP-2185. The System Builder provides a high level method for defining the architecture of systems under development. The Assembler has an algebraic syntax that is easy to program and debug. The Linker combines object files into an executable file. The Simulator provides an interactive instruction-level simulation with a reconfigurable user interface to display different portions of the hardware environment. A PROM Splitter generates PROM programmer compatible files. The C Compiler, based on the Free Software Foundation's GNU C Compiler, generates ADSP-2185 assembly source code. The source code debugger allows programs to be corrected in the C environment. The Runtime Library includes over 100 ANSI-standard mathematical and DSP-specific functions.

The EZ-KIT Lite is a hardware/software kit offering a complete development environment for the entire ADSP-21xx family: an ADSP-218x based evaluation board with PC monitor software plus Assembler, Linker, Simulator and PROM Splitter software. The ADSP-21xx EZ-KIT Lite is a low cost, easy to use hardware platform on which you can quickly get started with your DSP software design. The EZ-KIT Lite includes the following features:

- 33 MHz ADSP-2181

- Full 16-bit Stereo Audio I/O with AD1847 SoundPort®\* Codec

- RS-232 Interface to PC with Windows® 3.1 Control Software

- Stand-Alone Operation with Socketed EPROM

- EZ-ICE®\* Connector for Emulator Control

- DSP Demo Programs

The ADSP-218x EZ-ICE®\* Emulator aids in the hardware debugging of an ADSP-2185 system. The emulator consists of hardware, host computer resident software, and the target board connector. The ADSP-2185 integrates on-chip emulation support with a 14-pin ICE-PORT™\* interface. This interface provides a simpler target board connection that requires fewer mechanical clearance considerations than other ADSP-2100 Family EZ-ICE®\*s. The ADSP-2185 device need not be removed from the target system when using the EZ-ICE®\*, nor are any adapters needed. Due to the small footprint of the EZ-ICE®\* connector, emulation can be supported in final board designs.

The EZ-ICE®\* performs a full range of functions, including:

- In-target operation

- Up to 20 breakpoints

- Single-step or full-speed operation

- Registers and memory values can be examined and altered

- PC upload and download functions

- Instruction-level emulation of program booting and execution

- Complete assembly and disassembly of instructions

- · C source-level debugging

See Designing An EZ-ICE<sup>®</sup>\*-Compatible Target System in the *ADSP-2100 Family EZ-Tools Manual* (ADSP-2181 sections) as well as the Target Board Connector for EZ-ICE<sup>®</sup>\* Probe section of this data sheet for the exact specifications of the EZ-ICE<sup>®</sup>\* target board connector.

# **Additional Information**

This data sheet provides a general overview of ADSP-2185 functionality. For additional information on the architecture and instruction set of the processor, refer to the ADSP-2100 Family User's Manual. For more information about the development tools, refer to the ADSP-2100 Family Development Tools Data Sheet.

### ARCHITECTURE OVERVIEW

The ADSP-2185 instruction set provides flexible data moves and multifunction (one or two data moves with a computation) instructions. Every instruction can be executed in a single processor cycle. The ADSP-2185 assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports program development.

Figure 1. Block Diagram

Figure 1 is an overall block diagram of the ADSP-2185. The processor contains three independent computational units: the ALU, the multiplier/accumulator (MAC) and the shifter. The computational units process 16-bit data directly and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add and multiply/subtract operations with 40 bits of accumulation. The shifter performs logical and arithmetic shifts, normalization, denormalization and derive exponent operations.

The shifter can be used to efficiently implement numeric format control including multiword and block floating-point representations.

-2-

<sup>\*</sup>All trademarks are the property of their respective holders.

<sup>\*</sup>EZ-ICE and SoundPORT are registered trademarks of Analog Devices, Inc.

The internal result (R) bus connects the computational units so the output of any unit may be the input of any unit on the next cycle.

A powerful program sequencer and two dedicated data address generators ensure efficient delivery of operands to these computational units. The sequencer supports conditional jumps, subroutine calls and returns in a single cycle. With internal loop counters and loop stacks, the ADSP-2185 executes looped code with zero overhead; no explicit jump instructions are required to maintain loops.

Two data address generators (DAGs) provide addresses for simultaneous dual operand fetches from data memory and program memory. Each DAG maintains and updates four address pointers. Whenever the pointer is used to access data (indirect addressing), it is post-modified by the value of one of four possible modify registers. A length value may be associated with each pointer to implement automatic modulo addressing for circular buffers.

Efficient data transfer is achieved with the use of five internal buses:

- Program Memory Address (PMA) Bus

- Program Memory Data (PMD) Bus

- Data Memory Address (DMA) Bus

- Data Memory Data (DMD) Bus

- Result (R) Bus

The two address buses (PMA and DMA) share a single external address bus, allowing memory to be expanded off-chip, and the two data buses (PMD and DMD) share a single external data bus. Byte memory space and I/O memory space also share the external buses.

Program memory can store both instructions and data, permitting the ADSP-2185 to fetch two operands in a single cycle, one from program memory and one from data memory. The ADSP-2185 can fetch an operand from program memory and the next instruction in the same cycle.

When configured in host mode, the ADSP-2185 has a 16-bit Internal DMA port (IDMA port) for connection to external systems. The IDMA port is made up of 16 data/address pins and five control pins. The IDMA port provides transparent, direct access to the DSPs on-chip program and data RAM.

An interface to low cost byte-wide memory is provided by the Byte DMA port (BDMA port). The BDMA port is bidirectional and can directly address up to four megabytes of external RAM or ROM for off-chip storage of program overlays or data tables.

The byte memory and I/O memory space interface supports slow memories and I/O memory-mapped peripherals with programmable wait state generation. External devices can gain control of external buses with bus request/grant signals  $(\overline{BR}, \overline{BGH} \text{ and } \overline{BG})$ . One execution mode (Go Mode) allows the ADSP-2185 to continue running from on-chip memory. Normal execution mode requires the processor to halt while buses are granted.

The ADSP-2185 can respond to eleven interrupts. There can be up to six external interrupts (one edge-sensitive, two level-sensitive and three configurable) and seven internal interrupts generated by the timer, the serial ports (SPORTs), the Byte DMA port and the power-down circuitry. There is also a master RESET signal. The two serial ports provide a complete synchronous serial interface with optional companding in hardware and a

wide variety of framed or frameless data transmit and receive modes of operation.

Each port can generate an internal programmable serial clock or accept an external serial clock.

The ADSP-2185 provides up to 13 general-purpose flag pins. The data input and output pins on SPORT1 can be alternatively configured as an input flag and an output flag. In addition, eight flags are programmable as inputs or outputs, and three flags are always outputs.

A programmable interval timer generates periodic interrupts. A 16-bit count register (TCOUNT) decrements every *n* processor cycle, where *n* is a scaling value stored in an 8-bit register (TSCALE). When the value of the count register reaches zero, an interrupt is generated and the count register is reloaded from a 16-bit period register (TPERIOD).

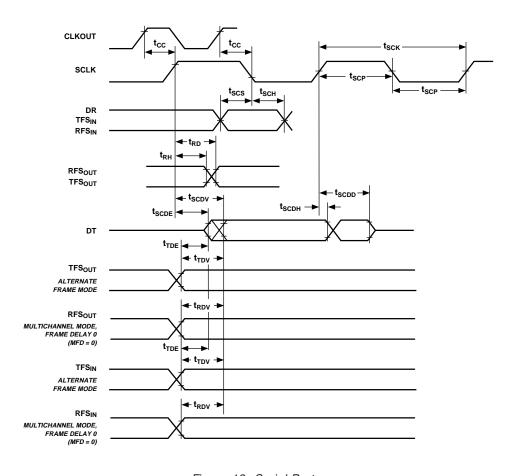

#### Serial Ports

The ADSP-2185 incorporates two complete synchronous serial ports (SPORT0 and SPORT1) for serial communications and multiprocessor communication.

Here is a brief list of the capabilities of the ADSP-2185 SPORTs. For additional information on Serial Ports, refer to the ADSP-2100 Family User's Manual.

- SPORTs are bidirectional and have a separate, double-buffered transmit and receive section.

- SPORTs can use an external serial clock or generate their own serial clock internally.

- SPORTs have independent framing for the receive and transmit sections. Sections run in a frameless mode or with frame synchronization signals internally or externally generated.

Frame sync signals are active high or inverted, with either of two pulse widths and timings.

- SPORTs support serial data word lengths from 3 to 16 bits and provide optional A-law and μ-law companding according to CCITT recommendation G.711.

- SPORT receive and transmit sections can generate unique interrupts on completing a data word transfer.

- SPORTs can receive and transmit an entire circular buffer of data with only one overhead cycle per data word. An interrupt is generated after a data buffer transfer.

- SPORT0 has a multichannel interface to selectively receive and transmit a 24 or 32 word, time-division multiplexed, serial bitstream.

- SPORT 1 can be configured to have two external interrupts (IRQ0 and IRQ1) and the Flag In and Flag Out signals. The internally generated serial clock may still be used in this configuration.

# PIN DESCRIPTIONS

The ADSP-2185 will be available in a 100-lead TQFP package. In order to maintain maximum functionality and reduce package size and pin count, some serial port, programmable flag, interrupt and external bus pins have dual, multiplexed functionality. The external bus pins are configured during RESET only, while serial port pins are software configurable during program execution. Flag and interrupt functionality is retained concurrently on multiplexed pins. In cases where pin functionality is reconfigurable, the default state is shown in plain text; alternate functionality is shown in italics.

### Common-Mode Pins

| Common-Mou                | #    | Input/ |                                                                        |

|---------------------------|------|--------|------------------------------------------------------------------------|

| Pin                       | of   | Out-   |                                                                        |

| Name(s)                   | Pins | put    | Function                                                               |

| RESET                     | 1    | I      | Processor Reset Input                                                  |

| $\overline{BR}$           | 1    | I      | Bus Request Input                                                      |

| $\overline{\mathrm{BG}}$  | 1    | 0      | Bus Grant Output                                                       |

| $\overline{\text{BGH}}$   | 1    | 0      | Bus Grant Hung Output                                                  |

| $\overline{\mathrm{DMS}}$ | 1    | 0      | Data Memory Select Output                                              |

| <u>PMS</u>                | 1    | 0      | Program Memory Select Output                                           |

| <b>IOMS</b>               | 1    | 0      | Memory Select Output                                                   |

| $\overline{\mathrm{BMS}}$ | 1    | 0      | Byte Memory Select Output                                              |

| <b>CMS</b>                | 1    | 0      | Combined Memory Select Output                                          |

| $\overline{\text{RD}}$    | 1    | 0      | Memory Read Enable Output                                              |

| $\overline{WR}$           | 1    | 0      | Memory Write Enable Output                                             |

| TRQ2/                     | 1    | I      | Edge- or Level-Sensitive                                               |

|                           |      |        | Interrupt Request <sup>1</sup>                                         |

| PF7                       |      | I/O    | Programmable I/O Pin                                                   |

| IRQL0/                    | 1    | I      | Level-Sensitive Interrupt Requests <sup>1</sup>                        |

| PF5                       |      | I/O    | Programmable I/O Pin                                                   |

| IRQL1/                    | 1    | I      | Level-Sensitive Interrupt Requests <sup>1</sup>                        |

| PF6                       | 1    | I/O    | Programmable I/O Pin                                                   |

| IRQE/<br>PF4              | 1    | I/O    | Edge-Sensitive Interrupt Requests <sup>1</sup><br>Programmable I/O Pin |

| PF3                       | 1    | I/O    | Programmable I/O Pin                                                   |

| Mode C/                   | 1    | I      | Mode Select Input—Checked                                              |

| Wode C/                   | 1    | 1      | only During RESET                                                      |

| PF2                       |      | I/O    | Programmable I/O Pin During                                            |

|                           |      |        | Normal Operation                                                       |

| Mode B/                   | 1    | I      | Mode Select Input—Checked                                              |

|                           |      |        | only During RESET                                                      |

| PF1                       |      | I/O    | Programmable I/O Pin During                                            |

| M - 1 - A/                | 1    | т      | Normal Operation                                                       |

| Mode A/                   | 1    | I      | Mode Select Input—Checked only During RESET                            |

| PF0                       |      | I/O    | Programmable I/O Pin During                                            |

|                           |      | 1, 0   | Normal Operation                                                       |

| CLKIN, XTAL               | 2    | I      | Clock or Quartz Crystal Input                                          |

| CLKOUT                    | 1    | 0      | Processor Clock Output                                                 |

| SPORT0                    | 5    | I/O    | Serial Port I/O Pins                                                   |

| SPORT 1/                  | 5    | I/O    | Serial Port I/O Pins                                                   |

| ĪRQ1:0                    |      |        | Edge- or Level-Sensitive Interrupts,                                   |

| FI, FO                    |      |        | Flag In, Flag Out <sup>2</sup>                                         |

| $\overline{	ext{PWD}}$    | 1    | I      | Power-Down Control Input                                               |

| PWDACK                    | 1    | 0      | Power-Down Control Output                                              |

| FL0, FL1, FL2             | 3    | 0      | Output Flags                                                           |

| VDD and GND               | 16   | I      | Power and Ground                                                       |

| EZ-Port                   | 9    | I/O    | For Emulation Use                                                      |

| -                         |      |        | •                                                                      |

#### NOTES

# **Memory Interface Pins**

The ADSP-2185 processor can be used in one of two modes, Full Memory Mode, which allows BDMA operation with full external overlay memory and I/O capability, or Host Mode, which allows IDMA operation with limited external addressing capabilities. The operating mode is determined by the state of the Mode C pin during RESET and cannot be changed while the processor is running.

Full Memory Mode Pins (Mode C = 0)

| Pin Name | #<br>of<br>Pins | Input/<br>Output | Function                                                                                                      |

|----------|-----------------|------------------|---------------------------------------------------------------------------------------------------------------|

| A13:0    | 14              | О                | Address Output Pins for Program, Data, Byte and I/O Spaces                                                    |

| D23:0    | 24              | I/O              | Data I/O Pins for Program,<br>Data, Byte and I/O Spaces<br>(8 MSBs Are Also Used as<br>Byte Memory Addresses) |

# $Host\ Mode\ Pins\ (Mode\ C=1)$

| Pin Name    | #<br>of<br>Pins | Input/<br>Output | Function                      |

|-------------|-----------------|------------------|-------------------------------|

| IAD 15:0    | 16              | I/O              | IDMA Port Address/Data Bus    |

| A0          | 1               | 0                | Address Pin for External I/O, |

|             |                 |                  | Program, Data, or Byte Access |

| D23:8       | 16              | I/O              | Data I/O Pins for Program,    |

|             |                 |                  | Data Byte and I/O Spaces      |

| ĪWR         | 1               | I                | IDMA Write Enable             |

| ĪRD         | 1               | I                | IDMA Read Enable              |

| IAL         | 1               | I                | IDMA Address Latch Pin        |

| ĪS          | 1               | I                | IDMA Select                   |

| <b>IACK</b> | 1               | 0                | IDMA Port Acknowledge         |

In Host Mode, external peripheral addresses can be decoded using the A0,  $\overline{CMS}$ ,  $\overline{PMS}$ ,  $\overline{DMS}$ , and  $\overline{IOMS}$  signals

# Setting Memory Mode

-4-

Memory Mode selection for the ADSP-2185 is made during chip reset through the use of the Mode C pin. This pin is multiplexed with the DSP's PF2 pin, so care must be taken in how the mode selection is made. The two methods for selecting the value of Mode C are active and passive.

Passive configuration involves the use a pull-up or pull-down resistor connected to the Mode C pin. To minimize power consumption, or if the PF2 pin is to be used as an output in the DSP application, a weak pull-up or pull-down, on the order of  $100~k\Omega$ , can be used. This value should be sufficient to pull the pin to the desired level and still allow the pin to operate as a programmable flag output without undue strain on the processor's output driver. For minimum power consumption during power-down, reconfigure PF2 to be an input as the pull-up or pull-down will hold the pin in a known state and will not switch.

Active configuration involves the use of a three-stateable external driver connected to the Mode C pin. A driver's output enable should be connected to the DSP's RESET signal such that it only drives the PF2 pin when RESET is active (low). After

<sup>&</sup>lt;sup>1</sup>Interrupt/Flag pins retain both functions concurrently. If IMASK is set to enable the corresponding interrupts, the DSP will vector to the appropriate interrupt vector address when the pin is asserted, either by external devices or set as a programmable flag.

<sup>&</sup>lt;sup>2</sup>SPORT configuration determined by the DSP System Control Register. Software configurable.

RESET is deasserted, the driver should three-state, thus allowing full use of the PF2 pin as either an input or output.

To minimize power consumption during power-down, configure the programmable flag as an output when connected to a three-stated buffer. This ensures that the pin will be held at a constant level and not oscillate should the three-state driver's level hover around the logic switching point.

#### Interrupts

The interrupt controller allows the processor to respond to the eleven possible interrupts and reset with minimum overhead. The ADSP-2185 provides four dedicated external interrupt input pins,  $\overline{IRQ2}$ ,  $\overline{IRQL0}$ ,  $\overline{IRQL1}$  and  $\overline{IRQE}$  (shared with the PF7:4 pins). In addition, SPORT1 may be reconfigured for  $\overline{IRQ0}$ ,  $\overline{IRQ1}$ , FLAG\_IN and FLAG\_OUT, for a total of six external interrupts. The ADSP-2185 also supports internal interrupts from the timer, the byte DMA port, the two serial ports, software and the power-down control circuit. The interrupt levels are internally prioritized and individually maskable (except power-down and reset). The  $\overline{IRQ2}$ ,  $\overline{IRQ0}$  and  $\overline{IRQ1}$  input pins can be programmed to be either level- or edge-sensitive.  $\overline{IRQL0}$  and  $\overline{IRQL1}$  are level-sensitive and  $\overline{IRQE}$  is edge-sensitive. The priorities and vector addresses of all interrupts are shown in Table I.

Table I. Interrupt Priority & Interrupt Vector Addresses

| Source Of Interrupt      | Interrupt Vector Address (Hex) |

|--------------------------|--------------------------------|

| Reset (or Power-Up with  |                                |

| PUCR = 1)                | 0000 (Highest Priority)        |

| Power-down (Nonmaskable) | 002C                           |

| ĪRQ2                     | 0004                           |

| ĪRQL1                    | 0008                           |

| ĪRQL0                    | 000C                           |

| SPORT0 Transmit          | 0010                           |

| SPORT0 Receive           | 0014                           |

| ĪRQE                     | 0018                           |

| BDMA Interrupt           | 001C                           |

| SPORT1 Transmit or IRQ1  | 0020                           |

| SPORT 1 Receive or IRQ0  | 0024                           |

| Timer                    | 0028 (Lowest Priority)         |

Interrupt routines can either be nested, with higher priority interrupts taking precedence, or processed sequentially. Interrupts can be masked or unmasked with the IMASK register. Individual interrupt requests are logically ANDed with the bits in IMASK; the highest priority unmasked interrupt is then selected. The power-down interrupt is nonmaskable.

The ADSP-2185 masks all interrupts for one instruction cycle following the execution of an instruction that modifies the IMASK register. This does not affect serial port autobuffering or DMA transfers.

The interrupt control register, ICNTL, controls interrupt nesting and defines the  $\overline{IRQ0}$ ,  $\overline{IRQ1}$  and  $\overline{IRQ2}$  external interrupts to be either edge- or level-sensitive. The  $\overline{IRQE}$  pin is an external edge-sensitive interrupt and can be forced and cleared. The  $\overline{IRQL0}$  and  $\overline{IRQL1}$  pins are external level-sensitive interrupts.

The IFC register is a write-only register used to force and clear interrupts.

On-chip stacks preserve the processor status and are automatically maintained during interrupt handling. The stacks are twelve levels deep to allow interrupt, loop and subroutine nesting.

The following instructions allow global enable or disable servicing of the interrupts (including power-down), regardless of the state of IMASK. Disabling the interrupts does not affect serial port autobuffering or DMA.

ENA INTS;

DIS INTS;

When the processor is reset, interrupt servicing is enabled.

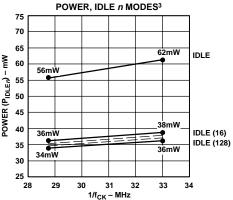

#### LOW POWER OPERATION

The ADSP-2185 has three low power modes that significantly reduce the power dissipation when the device operates under standby conditions. These modes are:

- Power-Down

- Idle

- · Slow Idle

The CLKOUT pin may also be disabled to reduce external power dissipation.

#### Power-Down

The ADSP-2185 processor has a low power feature that lets the processor enter a very low power dormant state through hardware or software control. Here is a brief list of power-down features. Refer to the ADSP-2100 Family User's Manual, "System Interface" chapter, for detailed information about the power-down feature.

- Quick recovery from power-down. The processor begins executing instructions in as few as 100 CLKIN cycles.

- Support for an externally generated TTL or CMOS processor clock. The external clock can continue running during power-down without affecting the lowest power rating and 100 CLKIN cycle recovery.

- Support for crystal operation includes disabling the oscillator to save power (the processor automatically waits approximately 4096 CLKIN cycles for the crystal oscillator to start or stabilize), and letting the oscillator run to allow 100 CLKIN cycle start-up.

- Power-down is initiated by either the power-down pin (PWD) or the software power-down force bit.

- Interrupt support allows an unlimited number of instructions to be executed before optionally powering down. The powerdown interrupt also can be used as a nonmaskable, edgesensitive interrupt.

- Context clear/save control allows the processor to continue where it left off or start with a clean context when leaving the power-down state.

- The  $\overline{RESET}$  pin also can be used to terminate power-down.

- Power-down acknowledge pin indicates when the processor has entered power-down.

REV. 0 \_5\_

#### Idle

When the ADSP-2185 is in the Idle Mode, the processor waits indefinitely in a low power state until an interrupt occurs. When an unmasked interrupt occurs, it is serviced; execution then continues with the instruction following the IDLE instruction. In Idle mode IDMA, BDMA and autobuffer cycle steals still occur.

#### Slow Idle

The IDLE instruction is enhanced on the ADSP-2185 to let the processor's internal clock signal be slowed, further reducing power consumption. The reduced clock frequency, a programmable fraction of the normal clock rate, is specified by a selectable divisor given in the IDLE instruction. The format of the instruction is

# IDLE(n);

where n = 16, 32, 64 or 128. This instruction keeps the processor fully functional, but operating at the slower clock rate. While it is in this state, the processor's other internal clock signals, such as SCLK, CLKOUT and timer clock, are reduced by the same ratio. The default form of the instruction, when no clock divisor is given, is the standard IDLE instruction.

When the *IDLE* (n) instruction is used, it effectively slows down the processor's internal clock and thus its response time to incoming interrupts. The one-cycle response time of the standard idle state is increased by n, the clock divisor. When an enabled interrupt is received, the ADSP-2185 will remain in the idle state for up to a maximum of n processor cycles (n = 16, 32, 64 or 128) before resuming normal operation.

When the IDLE (n) instruction is used in systems that have an externally generated serial clock (SCLK), the serial clock rate may be faster than the processor's reduced internal clock rate. Under these conditions, interrupts must not be generated at a faster rate than can be serviced, due to the additional time the processor takes to come out of the idle state (a maximum of n processor cycles).

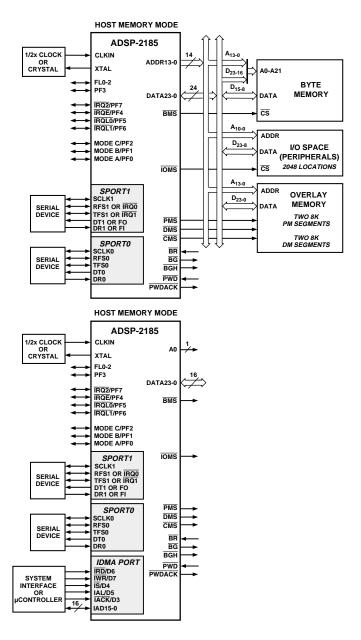

# SYSTEM INTERFACE

Figure 2 shows typical basic system configurations with the ADSP-2185, two serial devices, a byte-wide EPROM and optional external program and data overlay memories (mode selectable). Programmable wait state generation allows the processor to easily connect to slow peripheral devices. The ADSP-2185 also provides four external interrupts and two serial ports or six external interrupts and one serial port.

Host Memory mode allows access to the full external data bus, but limits addressing to a single address bit (A0). Additional system peripherals can be added in this mode through the use of external hardware to generate and latch address signals.

Figure 2. Basic System Configuration

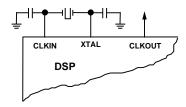

## **Clock Signals**

The ADSP-2185 can be clocked by either a crystal or a TTL-compatible clock signal.

The CLKIN input cannot be halted, changed during operation or operated below the specified frequency during normal operation. The only exception is while the processor is in the powerdown state. For additional information, refer to Chapter 9, ADSP-2100 Family User's Manual, for detailed information on this power-down feature.

If an external clock is used, it should be a TTL-compatible signal running at half the instruction rate. The signal is connected to the processor's CLKIN input. When an external clock is used, the XTAL input must be left unconnected.

The ADSP-2185 uses an input clock with a frequency equal to half the instruction rate; a 16.67 MHz input clock yields a 30 ns processor cycle (which is equivalent to 33 MHz). Normally, instructions are executed in a single processor cycle. All device timing is relative to the internal instruction clock rate, which is indicated by the CLKOUT signal when enabled.

Because the ADSP-2185 includes an on-chip oscillator circuit, an external crystal may be used. The crystal should be connected across the CLKIN and XTAL pins, with two capacitors connected as shown in Figure 3. Capacitor values are dependent on crystal type and should be specified by the crystal manufacturer. A parallel-resonant, fundamental frequency, microprocessor-grade crystal should be used.

A clock output (CLKOUT) signal is generated by the processor at the processor's cycle rate. This can be enabled and disabled by the CLKODIS bit in the SPORTO Autobuffer Control Register.

Figure 3. External Crystal Connections

#### Reset

The RESET signal initiates a master reset of the ADSP-2185. The RESET signal must be asserted during the power-up sequence to assure proper initialization. RESET during initial power-up must be held long enough to allow the internal clock to stabilize. If RESET is activated any time after power-up, the clock continues to run and does not require stabilization time.

The power-up sequence is defined as the total time required for the crystal oscillator circuit to stabilize after a valid  $V_{\rm DD}$  is applied to the processor, and for the internal phase-locked loop (PLL) to lock onto the specific crystal frequency. A minimum of 2000 CLKIN cycles ensures that the PLL has locked, but does not include the crystal oscillator start-up time. During this power-up sequence the  $\overline{RESET}$  signal should be held low. On any subsequent resets, the  $\overline{RESET}$  signal must meet the minimum pulse width specification,  $t_{RSP}$ .

The RESET input contains some hysteresis; however, if you use an RC circuit to generate your RESET signal, the use of an external Schmidt trigger is recommended.

The master reset sets all internal stack pointers to the empty stack condition, masks all interrupts and clears the MSTAT register. When  $\overline{RESET}$  is released, if there is no pending bus request and the chip is configured for booting, the boot-loading sequence is performed. The first instruction is fetched from on-chip program memory location 0x0000 once boot loading completes.

### MEMORY ARCHITECTURE

The ADSP-2185 provides a variety of memory and peripheral interface options. The key functional groups are Program Memory, Data Memory, Byte Memory and I/O.

**Program Memory** is a 24-bit-wide space for storing both instruction opcodes and data. The ADSP-2185 has 16K words of Program Memory RAM on chip, and the capability of accessing up to two 8K external memory overlay spaces using the external data bus. Both an instruction opcode and a data value can be read from on-chip program memory in a single cycle.

**Data Memory** is a 16-bit-wide space used for the storage of data variables and for memory-mapped control registers. The ADSP-2185 has 16K words on Data Memory RAM on chip, consisting of 16,352 user-accessible locations and 32 memory-mapped registers. Support also exists for up to two 8K external memory overlay spaces through the external data bus.

**Byte Memory (Full Memory Mode)** provides access to an 8-bit wide memory space through the Byte DMA (BDMA) port. The Byte Memory interface provides access to 4 MBytes of memory by utilizing eight data lines as additional address lines. This gives the BDMA Port an effective 22-bit address range. On power-up, the DSP can automatically load bootstrap code from byte memory.

I/O Space (Full Memory Mode) allows access to 2048 locations of 16-bit-wide data. It is intended to be used to communicate with parallel peripheral devices such as data converters and external registers or latches.

#### **Program Memory**

The ADSP-2185 contains a  $16K \times 24$  on-chip program RAM. The on-chip program memory is designed to allow up to two accesses each cycle so that all operations can complete in a single cycle. In addition, the ADSP-2185 allows the use of 8K external memory overlays.

The program memory space organization is controlled by the Mode B pin and the PMOVLAY register. Normally, the ADSP-2185 is configured with Mode B=0 and program memory organized as shown in Figure 4.

| PROGRAM MEMORY                                                                                        | ADDRESS |

|-------------------------------------------------------------------------------------------------------|---------|

| 8K INTERNAL<br>(PMOVLAY = 0,<br>MODE B = 0)<br>OR<br>EXTERNAL 8K<br>(PMOVLAY = 1 or 2,<br>MODE B = 0) | 0x3FFF  |

|                                                                                                       | 0x2000  |

| 8K INTERNAL                                                                                           | 0x1FFF  |

|                                                                                                       | 0x0000  |

Figure 4. Program Memory (Mode B = 0)

There are 16K words of memory accessible internally when the PMOVLAY register is set to 0. When PMOVLAY is set to something other than 0, external accesses occur at addresses 0x2000 through 0x3FFF. The external address is generated as shown in Table II.

REV. 0 -7-

Table II.

| PMOVLAY | Memory                | A13            | A12:0                                              |

|---------|-----------------------|----------------|----------------------------------------------------|

| 0       | Internal              | Not Applicable | Not Applicable                                     |

| 1       | External<br>Overlay 1 | 0              | 13 LSBs of Address<br>Between 0x2000<br>and 0x3FFF |

| 2       | External<br>Overlay 2 | 1              | 13 LSBs of Address<br>Between 0x2000<br>and 0x3FFF |

This organization provides for two external 8K overlay segments using only the normal 14 address bits. This allows for simple program overlays using one of the two external segments in place of the on-chip memory. Care must be taken in using this overlay space in that the processor core (i.e., the sequencer) does not take into account the PMOVLAY register value. For example, if a loop operation was occurring on one of the external overlays and the program changes to another external overlay or internal memory, an incorrect loop operation could occur. In addition, care must be taken in interrupt service routines as the overlay registers are not automatically saved and restored on the processor mode stack.

When Mode B = 1, booting is disabled and overlay memory is disabled (PMOVLAY must be 0). Figure 5 shows the memory map in this configuration.

| PROGRAM MEMORY                              | ADDRESS |

|---------------------------------------------|---------|

|                                             | 0x3FFF  |

| INTERNAL 8K<br>(PMOVLAY = 0,<br>MODE B = 1) |         |

|                                             | 0x2000  |

|                                             | 0x1FFF  |

| 8K EXTERNAL                                 |         |

|                                             | 0x0000  |

Figure 5. Program Memory (Mode B = 1)

# Data Memory

The ADSP-2185 has 16,352 16-bit words of internal data memory. In addition, the ADSP-2185 allows the use of 8K external memory overlays. Figure 6 shows the organization of the data memory.

| DATA MEMORY                                                           | ADDRESS          |

|-----------------------------------------------------------------------|------------------|

| 32 MEMORY-<br>MAPPED REGISTERS                                        | 0x3FFF           |

|                                                                       | 0x3FEO           |

|                                                                       | 0x3FDF           |

| INTERNAL<br>8160 WORDS                                                |                  |

|                                                                       | 0x2000           |

| 8K INTERNAL<br>(DMOVLAY = 0)<br>OR<br>EXTERNAL 8K<br>(DMOVLAY = 1, 2) | 0x1FFF<br>0x0000 |

Figure 6. Data Memory

There are 16,352 words of memory accessible internally when the DMOVLAY register is set to 0. When DMOVLAY is set to something other than 0, external accesses occur at addresses 0x0000 through 0x1FFF. The external address is generated as shown in Table III.

Table III.

| DMOVLAY | Memory                            | A13            | A12:0                                                            |

|---------|-----------------------------------|----------------|------------------------------------------------------------------|

| 0       | Internal<br>External<br>Overlay 1 | Not Applicable | Not Applicable<br>13 LSBs of Address<br>Between 0x2000           |

| 2       | External<br>Overlay 2             | 1              | and 0x3FFF<br>13 LSBs of Address<br>Between 0x2000<br>and 0x3FFF |

This organization allows for two external 8K overlays using only the normal 14 address bits. All internal accesses complete in one cycle. Accesses to external memory are timed using the wait states specified by the DWAIT register.

# I/O Space (Full Memory Mode)

The ADSP-2185 supports an additional external memory space called I/O space. This space is designed to support simple connections to peripherals or to bus interface ASIC data registers. I/O space supports 2048 locations. The lower eleven bits of the external address bus are used; the upper three bits are undefined. Two instructions were added to the core ADSP-2100 Family instruction set to read from and write to I/O memory space. The I/O space also has four dedicated 3-bit wait state registers, IOWAIT0-3, which specify up to seven wait states to be automatically generated for each of four regions. The wait states act on address ranges as shown in Table IV.

Table IV.

| Address Range | Wait State Register |

|---------------|---------------------|

| 0x000–0x1FF   | IOWAIT0             |

| 0x200-0x3FF   | IOWAIT1             |

| 0x400-0x5FF   | IOWAIT2             |

| 0x600-0x7FF   | IOWAIT3             |

# Composite Memory Select (CMS)

The ADSP-2185 has a programmable memory select signal that is useful for generating memory select signals for memories mapped to more than one space. The  $\overline{CMS}$  signal is generated to have the same timing as each of the individual memory select signals ( $\overline{PMS}$ ,  $\overline{DMS}$ ,  $\overline{DMS}$ ,  $\overline{IOMS}$ ), but can combine their functionality.

When set, each bit in the CMSSEL register causes the  $\overline{\text{CMS}}$  signal to be asserted when the selected memory select is asserted. For example, to use a 32K word memory to act as both program and data memory, set the  $\overline{\text{PMS}}$  and  $\overline{\text{DMS}}$  bits in the CMSSEL register and use the  $\overline{\text{CMS}}$  pin to drive the chip select of the memory and use either  $\overline{\text{DMS}}$  or  $\overline{\text{PMS}}$  as the additional address bit.

The CMS pin functions as the other memory select signals, with the same timing and bus request logic. A 1 in the enable bit causes the assertion of the CMS signal at the same time as the

selected memory select signal. All enable bits, except the BMS bit, default to 1 at reset,

# Byte Memory

The byte memory space is a bidirectional, 8-bit-wide, external memory space used to store programs and data. Byte memory is accessed using the BDMA feature. The byte memory space consists of 256 pages, each of which is  $16K \times 8$ .

The byte memory space on the ADSP-2185 supports read and write operations as well as four different data formats. The byte memory uses data bits 15:8 for data. The byte memory uses data bits 23:16 and address bits 13:0 to create a 22-bit address. This allows up to a 4 meg  $\times$  8 (32 megabit) ROM or RAM to be used without glue logic. All byte memory accesses are timed by the BMWAIT register.

# Byte Memory DMA (BDMA, Full Memory Mode)

The Byte memory DMA controller allows loading and storing of program instructions and data using the byte memory space. The BDMA circuit is able to access the byte memory space while the processor is operating normally and steals only one DSP cycle per 8-, 16- or 24-bit word transferred.

The BDMA circuit supports four different data formats, which are selected by the BTYPE register field. The appropriate number of 8-bit accesses are done from the byte memory space to build the word size selected. Table V shows the data formats supported by the BDMA circuit.

Table V.

| ВТҮРЕ | Internal<br>Memory Space | Word Size | Alignment |

|-------|--------------------------|-----------|-----------|

| 00    | Program Memory           | 24        | Full Word |

| 01    | Data Memory              | 16        | Full Word |

| 10    | Data Memory              | 8         | MSBs      |

| 11    | Data Memory              | 8         | LSBs      |

Unused bits in the 8-bit data memory formats are filled with 0s. The BIAD register field is used to specify the starting address for the on-chip memory involved with the transfer. The 14-bit BEAD register specifies the starting address for the external byte memory space. The 8-bit BMPAGE register specifies the starting page for the external byte memory space. The BDIR register field selects the direction of the transfer. Finally the 14-bit BWCOUNT register specifies the number of DSP words to transfer and initiates the BDMA circuit transfers.

BDMA accesses can cross page boundaries during sequential addressing. A BDMA interrupt is generated on the completion of the number of transfers specified by the BWCOUNT register. The BWCOUNT register is updated after each transfer so it can be used to check the status of the transfers. When it reaches zero, the transfers have finished and a BDMA interrupt is generated. The BMPAGE and BEAD registers must not be accessed by the DSP during BDMA operations.

The source or destination of a BDMA transfer will always be on-chip program or data memory, regardless of the values of Mode B, PMOVLAY or DMOVLAY.

When the BWCOUNT register is written with a nonzero value, the BDMA circuit starts executing byte memory accesses with wait states set by BMWAIT. These accesses continue until the count reaches zero. When enough accesses have occurred to

create a destination word, it is transferred to or from on-chip memory. The transfer takes one DSP cycle. DSP accesses to external memory have priority over BDMA byte memory accesses.

The BDMA Context Reset bit (BCR) controls whether the processor is held off while the BDMA accesses are occurring. Setting the BCR bit to 0 allows the processor to continue operations. Setting the BCR bit to 1 causes the processor to stop execution while the BDMA accesses are occurring, to clear the context of the processor and to start execution at address 0 when the BDMA accesses have completed.

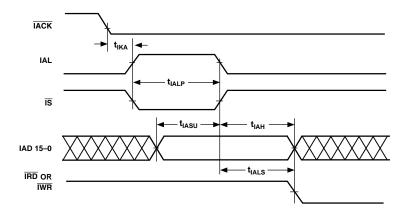

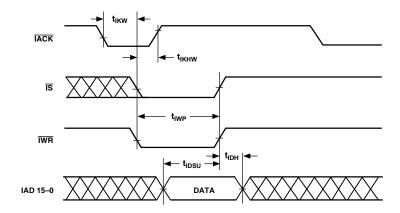

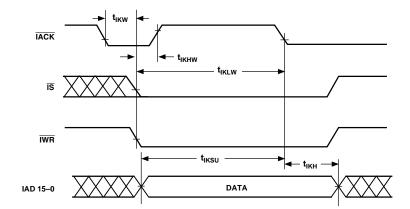

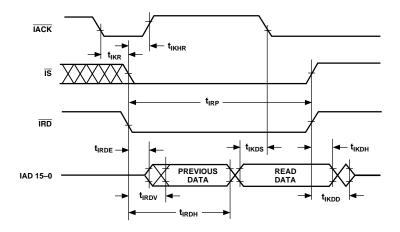

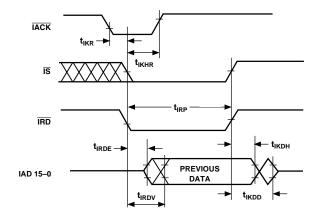

# Internal Memory DMA Port (IDMA Port; Host Memory Mode)

The IDMA Port provides an efficient means of communication between a host system and the ADSP-2185. The port is used to access the on-chip program memory and data memory of the DSP with only one DSP cycle per word overhead. The IDMA port cannot, however, be used to write to the DSP's memory-mapped control registers.

The IDMA port has a 16-bit multiplexed address and data bus and supports 24-bit program memory. The IDMA port is completely asynchronous and can be written to while the ADSP-2185 is operating at full speed.

The DSP memory address is latched and then automatically incremented after each IDMA transaction. An external device can therefore access a block of sequentially addressed memory by specifying only the starting address of the block. This increases throughput as the address does not have to be sent for each memory access.

IDMA Port access occurs in two phases. The first is the IDMA Address Latch cycle. When the acknowledge is asserted, a 14-bit address and 1-bit destination type can be driven onto the bus by an external device. The address specifies an on-chip memory location, the destination type specifies whether it is a DM or PM access. The falling edge of the address latch signal latches this value into the IDMAA register.

Once the address is stored, data can then be either read from or written to the ADSP-2185's on-chip memory. Asserting the select line ( $\overline{\text{IS}}$ ) and the appropriate read or write line ( $\overline{\text{IRD}}$  and  $\overline{\text{IWR}}$  respectively) signals the ADSP-2185 that a particular transaction is required. In either case, there is a one-processor-cycle delay for synchronization. The memory access consumes one additional processor cycle.

Once an access has occurred, the latched address is automatically incremented and another access can occur.

Through the IDMAA register, the DSP can also specify the starting address and data format for DMA operation.

# $Bootstrap\ Loading\ (Booting)$

The ADSP-2185 has two mechanisms to allow automatic loading of the internal program memory after reset. The method for booting is controlled by the Mode A, B and C configuration bits as shown in Table VI. These four states can be compressed into two-state bits by allowing an IDMA boot with Mode C = 1. However, three bits are used to ensure future compatibility with parts containing internal program memory ROM.

### **BDMA Booting**

When the MODE pins specify BDMA booting, the ADSP-2185 initiates a BDMA boot sequence when RESET is released.

Table VI. Boot Summary Table

| MODE C | MODE B | MODE A | <b>Booting Method</b>                                                                                                                                                                                                                     |

|--------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | 0      | BDMA feature is used to load the first 32 program memory words from the byte memory space. Program execution is held off until all 32 words have been loaded. Chip is configured in Full Memory Mode.                                     |

| 0      | 1      | 0      | No Automatic boot operations occur. Program execution starts at external memory location 0. Chip is configured in Full Memory Mode. BDMA can still be used but the processor does not automatically use or wait for these operations.     |

| 1      | 0      | 0      | BDMA feature is used to load the first 32 program memory words from the byte memory space. Program execution is held off until all 32 words have been loaded. Chip is configured in Host Mode. Additional interface hardware is required. |

| 1      | 0      | 1      | IDMA feature is used to load any internal memory as desired. Program execution is held off until internal program memory location 0 is written to. Chip is configured in Host Mode.                                                       |

The BDMA interface is set up during reset to the following defaults when BDMA booting is specified: the BDIR, BMPAGE, BIAD and BEAD registers are set to 0; the BTYPE register is set to 0 to specify program memory 24 bit words; and the BWCOUNT register is set to 32. This causes 32 words of onchip program memory to be loaded from byte memory. These 32 words are used to set up the BDMA to load in the remaining program code. The BCR bit is also set to 1, which causes program execution to be held off until all 32 words are loaded into on-chip program memory. Execution then begins at address 0.

The ADSP-2100 Family development software (Revision 5.02 and later) fully supports the BDMA booting feature and can generate byte memory space compatible boot code.

The IDLE instruction can also be used to allow the processor to hold off execution while booting continues through the BDMA interface. For BDMA accesses while in Host Mode, the addresses to boot memory must be constructed externally to the ADSP-2185. The only memory address bit provided by the processor is A0.

## **IDMA Port Booting**

The ADSP-2185 can also boot programs through its Internal DMA port. If Mode C = 1, Mode B = 0 and Mode A = 1, the ADSP-2185 boots from the IDMA port. IDMA feature can load as much on-chip memory as desired. Program execution is held off until on-chip program memory location 0 is written to.

The ADSP-2100 Family development software (Revision 5.02 and later) can generate IDMA compatible boot code.

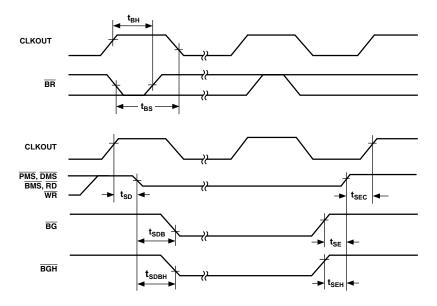

#### **Bus Request & Bus Grant**

The ADSP-2185 can relinquish control of the data and address buses to an external device. When the external device requires access to memory, it asserts the bus request (BR) signal. If the ADSP-2185 is not performing an external memory access, it responds to the active BR input in the following processor cycle by:

- Three-stating the data and address buses and the PMS, DMS, BMS, CMS, IOMS, RD, WR output drivers,

- Asserting the bus grant (BG) signal and

- Halting program execution.

If Go Mode is enabled, the ADSP-2185 will not halt program execution until it encounters an instruction that requires an external memory access.

If the ADSP-2185 is performing an external memory access when the external device asserts the  $\overline{BR}$  signal, then it will not three-state the memory interfaces or assert the  $\overline{BG}$  signal until the processor cycle after the access completes. The instruction does not need to be completed when the bus is granted. If a single instruction requires two external memory accesses, the bus will be granted between the two accesses.

When the  $\overline{BR}$  signal is released, the processor releases the  $\overline{BG}$  signal, reenables the output drivers and continues program execution from the point where it stopped.

The bus request feature operates at all times, including when the processor is booting and when RESET is active.

The  $\overline{BGH}$  pin is asserted when the ADSP-2185 is ready to execute an instruction but is stopped because the external bus is already granted to another device. The other device can release the bus by deasserting bus request. Once the bus is released, the ADSP-2185 deasserts  $\overline{BG}$  and  $\overline{BGH}$  and executes the external memory access.

## Flag I/O Pins

The ADSP-2185 has eight general purpose programmable input/output flag pins. They are controlled by two memory mapped registers. The PFT YPE register determines the direction, 1 = output and 0 = input. The PFDATA register is used to read and write the values on the pins. Data being read from a pin configured as an input is synchronized to the ADSP-2185's clock. Bits that are programmed as outputs will read the value being output. The PF pins default to input during reset.

In addition to the programmable flags, the ADSP-2185 has five fixed-mode flags, FLAG\_IN, FLAG\_OUT, FL0, FL1 and FL2. FL0-FL2 are dedicated output flags. FLAG\_IN and FLAG\_OUT are available as an alternate configuration of SPORT 1

Note: Pins PF0, PF1 and PF2 are also used for device configuration during reset.

-10- REV. 0

### **BIASED ROUNDING**

A mode is available on the ADSP-2185 to allow biased rounding in addition to the normal unbiased rounding. When the BIASRND bit is set to 0, the normal unbiased rounding operations occur. When the BIASRND bit is set to 1, biased rounding occurs instead of the normal unbiased rounding. When operating in biased rounding mode all rounding operations with MR0 set to 0x8000 will round up, rather than only rounding up odd MR1 values.

For example:

Table VII.

| MR Value<br>Before RND | Biased<br>RND Result | Unbiased<br>RND Result |  |

|------------------------|----------------------|------------------------|--|

| 00-0000-8000           | 00-0001-8000         | 00-0000-8000           |  |

| 00-0001-8000           | 00-0002-8000         | 00-0002-8000           |  |

| 00-0000-8001           | 00-0001-8001         | 00-0001-8001           |  |

| 00-0001-8001           | 00-0002-8001         | 00-0002-8001           |  |

| 00-0000-7FFF           | 00-0000-7FFF         | 00-0000-7FFF           |  |

| 00-0001-7FFF           | 00-0001-7FFF         | 00-0001-7FFF           |  |

This mode only has an effect when the MR0 register contains 0x8000; all other rounding operations work normally. This mode allows more efficient implementation of bit-specified algorithms that use biased rounding, for example the GSM speech compression routines. Unbiased rounding is preferred for most algorithms.

Note: BIASRND bit is Bit 12 of the SPORT 0 Autobuffer Control register.

# **Instruction Set Description**

The ADSP-2185 assembly language instruction set has an algebraic syntax that was designed for ease of coding and readability. The assembly language, which takes full advantage of the processor's unique architecture, offers the following benefits:

- The algebraic syntax eliminates the need to remember cryptic assembler mnemonics. For example, a typical arithmetic add instruction, such as AR = AX0 + AY0, resembles a simple equation.

- Every instruction assembles into a single, 24-bit word that can execute in a single instruction cycle.

- The syntax is a superset ADSP-2100 Family assembly language and is completely source and object code compatible with other family members. Programs may need to be relocated to use on-chip memory and conform to the ADSP-2185's interrupt vector and reset vector map.

- Sixteen condition codes are available. For conditional jump, call, return or arithmetic instructions, the condition can be checked and the operation executed in the same instruction cycle.

- Multifunction instructions allow parallel execution of an arithmetic instruction with up to two fetches or one write to processor memory space during a single instruction cycle.

# I/O Space Instructions

The instructions used to access the ADSP-2185's I/O memory space are as follows:

**Syntax:** IO(addr) = dregdreg = IO(addr);

where addr is an address value between 0 and 2047 and dreg is any of the 16 data registers.

Examples: IO(23) = AR0; AR1 = IO(17);

**Description:** The I/O space read and write instructions move

data between the data registers and the I/O

memory space.

# DESIGNING AN EZ-ICE®\*-COMPATIBLE SYSTEM

The ADSP-2185 has on-chip emulation support and an ICE-Port<sup>™</sup>\*, a special set of pins that interface to the EZ-ICE<sup>®</sup>\*. These features allow in-circuit emulation without replacing the target system processor by using only a 14-pin connection from the target system to the EZ-ICE®\*. Target systems must have a 14-pin connector to accept the EZ-ICE®\*'s in-circuit probe, a 14-pin plug. See the ADSP-2100 Family EZ-Tools data sheet for complete information on ICE products.

The ICE-Port<sup>TM\*</sup> interface consists of the following ADSP-2185 pins:

$\overline{\text{EBR}}$

**EBG**

**ERESET**

**EMS**

**EINT**

**ECLK**

ELIN

**ELOUT**

EE

These ADSP-2185 pins must be connected only to the EZ-ICE®\* connector in the target system. These pins have no function except during emulation, and do not require pull-up or pull-down resistors. The traces for these signals between the ADSP-2185 and the connector must be kept as short as possible, no longer than three inches.

The following pins are also used by the EZ-ICE®\*:

$\overline{BR}$

$\overline{BG}$

**RESET**

GND

The EZ-ICE®\* uses the EE (emulator enable) signal to take control of the ADSP-2185 in the target system. This causes the processor to use its ERESET, EBR and EBG pins instead of the  $\overline{RESET}$ ,  $\overline{BR}$  and  $\overline{BG}$  pins. The  $\overline{BG}$  output is three-stated. These signals do not need to be jumper-isolated in your system.

The EZ-ICE®\* connects to your target system via a ribbon cable and a 14-pin female plug. The female plug is plugged onto the 14-pin connector (a pin strip header) on the target board.

REV. 0 -11-

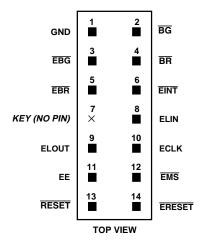

# Target Board Connector for EZ-ICE®\* Probe

The EZ-ICE®\* connector (a standard pin strip header) is shown in Figure 7. You must add this connector to your target board design if you intend to use the EZ-ICE®\*. Be sure to allow enough room in your system to fit the EZ-ICE®\* probe onto the 14-pin connector.

Figure 7. Target Board Connector for EZ-ICE®\*

The 14-pin, 2-row pin strip header is keyed at the Pin 7 location—you must remove Pin 7 from the header. The pins must be 0.025 inch square and at least 0.20 inch in length. Pin spacing should be  $0.1 \times 0.1$  inches. The pin strip header must have at least 0.15 inch clearance on all sides to accept the EZ-ICE®\* probe plug. Pin strip headers are available from vendors such as 3M, McKenzie and Samtec.

## Target Memory Interface

For your target system to be compatible with the EZ-ICE $^{\otimes}*$  emulator, it must comply with the memory interface guidelines listed below.

# PM, DM, BM, IOM and CM

Design your Program Memory (PM), Data Memory (DM), Byte Memory (BM), I/O Memory (IOM) and Composite Memory (CM) external interfaces to comply with worst case device timing requirements and switching characteristics as specified in this DSP's data sheet. The performance of the EZ-ICE®\* may approach published worst case specification for some memory access timing requirements and switching characteristics.

Note: If your target does not meet the worst case chip specification for memory access parameters, you may not be able to emulate your circuitry at the desired CLKIN frequency. Depending on the severity of the specification violation, you may have trouble manufacturing your system as DSP components statistically vary in switching characteristic and timing requirements within published limits.

Restriction: All memory strobe signals on the ADSP-2185  $(\overline{RD},\overline{WR},\overline{PMS},\overline{DMS},\overline{BMS},\overline{CMS}$  and  $\overline{IOMS})$  used in your target system must have  $10~\text{k}\Omega$  pull-up resistors connected when the EZ-ICE\*\* is being used. The pull-up resistors are necessary because there are no internal pull-ups to guarantee their state during prolonged three-state conditions resulting from typical EZ-ICE\*\* debugging sessions. These resistors may be removed at your option when the EZ-ICE\*\* is not being used.

# **Target System Interface Signals**

When the EZ-ICE<sup>®</sup>\* board is installed, the performance on some system signals change. Design your system to be compatible with the following system interface signal changes introduced by the EZ-ICE<sup>®</sup>\* board:

- EZ-ICE<sup>®</sup>\* emulation introduces an 8 ns propagation delay between your target circuitry and the DSP on the RESET signal.

- EZ-ICE  $^{\otimes}*$  emulation introduces an 8 ns propagation delay between your target circuitry and the DSP on the  $\overline{BR}$  signal.

- EZ-ICE®\* emulation ignores  $\overline{RESET}$  and  $\overline{BR}$  when single-stepping.

- EZ-ICE<sup>®</sup>\* emulation ignores RESET and BR when in Emulator Space (DSP halted).

- EZ-ICE<sup>®</sup>\* emulation ignores the state of target  $\overline{BR}$  in certain modes. As a result, the target system may take control of the DSP's external memory bus only if bus grant ( $\overline{BG}$ ) is asserted by the EZ-ICE<sup>®</sup>\* board's DSP.

-12- REV. 0

# RECOMMENDED OPERATING CONDITIONS

|                              | K Grade |     | ВС  |     |      |

|------------------------------|---------|-----|-----|-----|------|

| Parameter                    | Min     | Max | Min | Max | Unit |

| $\overline{V_{\mathrm{DD}}}$ | 4.5     | 5.5 | 4.5 | 5.5 | V    |

| $T_{AMB}$                    | 0       | +70 | -40 | +85 | °C   |

# ELECTRICAL CHARACTERISTICS

|           |                                                |                               | ]            | K/B Grade | es  |      |

|-----------|------------------------------------------------|-------------------------------|--------------|-----------|-----|------|

| Parameter |                                                | <b>Test Conditions</b>        | Min          | Typ       | Max | Unit |

| $V_{IH}$  | Hi-Level Input Voltage <sup>1, 2</sup>         | $@V_{DD} = max$               | 2.0          |           |     | V    |

| $V_{IH}$  | Hi-Level CLKIN Voltage                         | $@V_{DD} = max$               | 2.2          |           |     | V    |

| $V_{IL}$  | Lo-Level Input Voltage <sup>I, 3</sup>         | $@V_{DD} = min$               |              |           | 0.8 | V    |

| $V_{OH}$  | Hi-Level Output Voltage <sup>1, 4, 5</sup>     | $@V_{DD} = min$               |              |           |     |      |

|           |                                                | $I_{OH} = -0.5 \text{ mA}$    | 2.4          |           |     | V    |

|           |                                                | $@V_{DD} = min$               |              |           |     |      |

|           |                                                | $I_{OH} = -100 \ \mu A^6$     | $V_{DD} = 0$ | ).3       |     | V    |

| $V_{OL}$  | Lo-Level Output Voltage <sup>1, 4, 5</sup>     | $@V_{DD} = min$               |              |           |     |      |

|           |                                                | $I_{OL} = 2 \text{ mA}$       |              |           | 0.4 | V    |

| $I_{IH}$  | Hi-Level Input Current <sup>3</sup>            | $@V_{DD} = max$               |              |           |     |      |

|           |                                                | $V_{IN} = V_{DD} max$         |              |           | 10  | μΑ   |

| $I_{IL}$  | Lo-Level Input Current <sup>3</sup>            | $@V_{DD} = max$               |              |           |     |      |

|           | _                                              | $V_{IN} = 0 V$                |              |           | 10  | μΑ   |

| $I_{OZH}$ | Three-State Leakage Current <sup>7</sup>       | $@V_{DD} = max$               |              |           |     |      |

|           | _                                              | $V_{IN} = V_{DD} max^8$       |              |           | 10  | μΑ   |

| $I_{OZL}$ | Three-State Leakage Current <sup>7</sup>       | $@V_{DD} = \max_{\alpha}$     |              |           |     |      |

|           |                                                | $V_{IN} = 0 V^8$              |              |           | 10  | μA   |

| $I_{DD}$  | Supply Current (Idle) <sup>9</sup>             | $@V_{DD} = 5.0$               |              | 12.4      |     | m A  |

| $I_{DD}$  | Supply Current (Dynamic) <sup>10</sup>         | $@V_{DD} = 5.0$               |              |           |     |      |

|           |                                                | $T_{AMB} = +25^{\circ}C$      |              |           |     |      |

|           | 2 6 12                                         | $t_{CK} = 30 \text{ ns}^{11}$ |              | 63        |     | m A  |

| $C_{I}$   | Input Pin Capacitance <sup>3, 6, 12</sup>      | $@V_{IN} = 2.5 V,$            |              |           |     |      |

|           |                                                | $f_{IN} = 1.0 MHz,$           |              |           | 8   | pF   |

| _         |                                                | $T_{AMB} = +25^{\circ}C$      |              |           |     |      |

| $C_{0}$   | Output Pin Capacitance <sup>6, 7, 12, 13</sup> | $@V_{IN} = 2.5 \text{ V},$    |              |           |     |      |

|           |                                                | $f_{IN} = 1.0 MHz,$           |              |           | _   |      |

|           |                                                | $T_{AMB} = +25^{\circ}C$      |              |           | 8   | pF   |

# NOTES

REV. 0 -13-

<sup>&</sup>lt;sup>1</sup> Bidirectional pins: D0-D23, RFS0, RFS1, SCLK0, SCLK1, TFS0, TFS1, A1-A13, PF0-PF7.

<sup>&</sup>lt;sup>2</sup> Input only pins: RESET, BR, DR0, DR1, PWD.

<sup>3</sup> Input only pins: CLKIN, RESET, BR, DR0, DR1, PWD.

<sup>4</sup> Output pins: BG, PMS, DMS, BMS, IOMS, CMS, RD, WR, PWDACK, A0, DT0, DT1, CLKOUT, FL2-0, BGH.

<sup>&</sup>lt;sup>5</sup> Although specified for TTL outputs, all ADSP-2185 outputs are CMOS-compatible and will drive to V<sub>DD</sub> and GND, assuming no dc loads.

<sup>&</sup>lt;sup>6</sup>Guaranteed but not tested.

<sup>&</sup>lt;sup>7</sup> Three-statable pins: A0-A13, D0-D23, PMS, DMS, BMS, TOMS, CMS, RD, WR, DT0, DT1, SCLK0, SCLK1, TFS0, TFS1, RFS0, RSF1, PF0-PF7.

$<sup>^{8}</sup>$  0 V on  $\overline{BR}$ , CLKIN Inactive.

$<sup>^{9}</sup>$  Idle refers to ADSP-2185 state of operation during execution of IDLE instruction. Deasserted pins are driven to either  $V_{DD}$  or GND.

<sup>&</sup>lt;sup>10</sup>IDD measurement taken with all instructions executing from internal memory. 50% of the instructions are multifunction (types 1, 4, 5, 12, 13, 14), 30% are type 2 and type 6, and 20% are idle instructions.

$<sup>^{11}</sup>V_{IN} = 0$  V and 3 V. For typical figures for supply currents, refer to Power Dissipation section.

<sup>&</sup>lt;sup>12</sup>Applies to TQFP package type.

<sup>&</sup>lt;sup>13</sup>Output pin capacitance is the capacitive load for any three-stated output pin.

Specifications subject to change without notice.

### ABSOLUTE MAXIMUM RATINGS\*

| Supply Voltage                                                      |

|---------------------------------------------------------------------|

| Input Voltage0.3 V to $V_{DD}$ + 0.3 V                              |

| Output Voltage Swing $-0.3 \text{ V}$ to $V_{DD}$ + $0.3 \text{ V}$ |

| Operating Temperature Range (Ambient)40°C to +85°C                  |

| Storage Temperature Range65°C to +150°C                             |

| Lead Temperature (5 sec) TQFP +280°C                                |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD SENSITIVITY**.

The ADSP-2185 is an ESD (electrostatic discharge) sensitive device. Electrostatic charges readily accumulate on the human body and equipment and can discharge without detection. Permanent damage may occur to devices subjected to high energy electrostatic discharges.

The ADSP-2185 features proprietary ESD protection circuitry to dissipate high energy discharges (Human Body Model) per method 3015 of MIL-STD-883. Proper ESD precautions are recommended to avoid performance degradation or loss of functionality. Unused devices must be stored in conductive foam or shunts, and the foam should be discharged to the destination before devices are removed.

# ADSP-2185 TIMING PARAMETERS

# **GENERAL NOTES**

Use the exact timing information given. Do not attempt to derive parameters from the addition or subtraction of others. While addition or subtraction would yield meaningful results for an individual device, the values given in this data sheet reflect statistical variations and worst cases. Consequently, you cannot meaningfully add up parameters to derive longer times.

# TIMING NOTES

Switching characteristics specify how the processor changes its signals. You have no control over this timing—circuitry external to the processor must be designed for compatibility with these signal characteristics. Switching characteristics tell you what the processor will do in a given circumstance. You can also use switching characteristics to ensure that any timing requirement of a device connected to the processor (such as memory) is satisfied.

Timing requirements apply to signals that are controlled by circuitry external to the processor, such as the data input for a read operation. Timing requirements guarantee that the processor operates correctly with other devices.

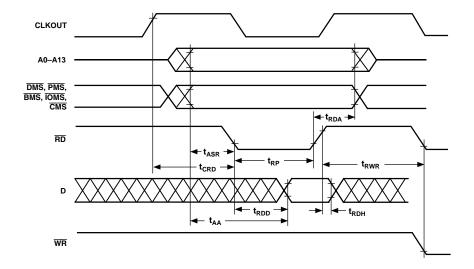

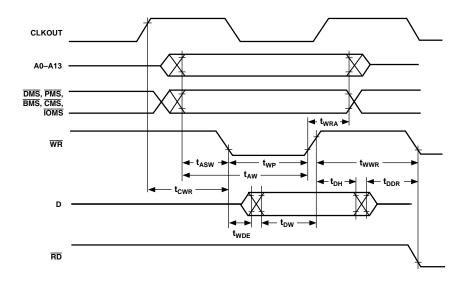

### MEMORY TIMING SPECIFICATIONS

The table below shows common memory device specifications and the corresponding ADSP-2185 timing parameters, for your convenience.

| Memory<br>Device<br>Specification | ADSP-2185<br>Timing<br>Parameter | Timing<br>Parameter<br>Definition                                                             |

|-----------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------|

| Address Setup to<br>Write Start   | t <sub>ASW</sub>                 | A0-A13, $\overline{x}\overline{M}\overline{S}$ Setup<br>before $\overline{W}\overline{R}$ Low |

| Address Setup to<br>Write End     | $t_{ m AW}$                      | A0-A13, xMS Setup<br>before WR Deasserted                                                     |

| Address Hold Time                 | $t_{WRA}$                        | $\frac{\text{A0-A13}}{\text{WR}}$ Low                                                         |

| Data Setup Time                   | $t_{\mathrm{DW}}$                | Data Setup before WR<br>High                                                                  |

| Data Hold Time                    | $t_{\rm DH}$                     | Data Hold after WR High                                                                       |

| $\overline{OE}$ to Data Valid     | $t_{RDD}$                        | RD Low to Data Valid                                                                          |

| Address Access Time               | $t_{AA}$                         | A0-A13, xMS to Data<br>Valid                                                                  |

$\overline{xMS} = \overline{PMS}, \overline{DMS}, \overline{BMS}, \overline{CMS}, \overline{IOMS}.$

# FREQUENCY DEPENDENCY FOR TIMING SPECIFICATIONS

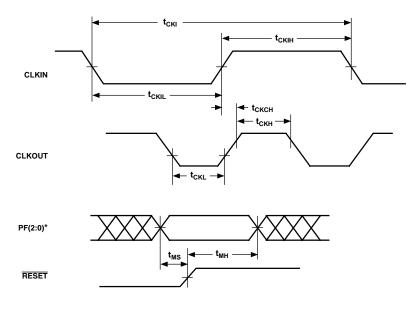

$t_{CK}$  is defined as  $0.5t_{CKI}.$  The ADSP-2185 uses an input clock with a frequency equal to half the instruction rate: a 16.67 MHz input clock (which is equivalent to 60 ns) yields a 30 ns processor cycle (equivalent to 33 MHz).  $t_{CK}$  values within the range of  $0.5t_{CKI}$  period should be substituted for all relevant timing parameters to obtain the specification value.

Example:  $t_{CKH} = 0.5t_{CK} - 7 \text{ ns} = 0.5 (30 \text{ ns}) - 7 \text{ ns} = 8 \text{ ns}$

-14- REV. 0

### **ENVIRONMENTAL CONDITIONS**

Ambient Temperature Rating:

$$\begin{split} T_{AMB} &= T_{CASE} - (PD \ x \ \theta_{CA}) \\ T_{CASE} &= Case \ Temperature \ in \ ^{\circ}C \end{split}$$

PD = Power Dissipation in W

$\theta_{CA}$  = Thermal Resistance (Case-to-Ambient)

$\theta_{JA}$  = Thermal Resistance (Junction-to-Ambient)

$\theta_{JC}$  = Thermal Resistance (Junction-to-Case)

| Package | $	heta_{ m JA}$ | $\theta_{ m JC}$ | $\theta_{\mathrm{CA}}$ |

|---------|-----------------|------------------|------------------------|