# Femtoampere Input Bias Current Electrometer Amplifier

### **Data Sheet**

#### FEATURES

Low input bias current

$\pm 20$  fA maximum at T<sub>A</sub> = 25°C (guaranteed at production test)  $\pm 20$  fA maximum at -40°C < T<sub>A</sub> < +85°C  $\pm 250$  fA maximum at -40°C < T<sub>A</sub> < +125°C (guaranteed at production test) Low offset voltage: 50 μV maximum over specified CMRR range Offset voltage drift:  $\pm 0.13$ μV/°C typical,  $\pm 0.5$ μV/°C maximum Integrated guard buffer with 100 μV maximum offset

Low voltage noise density: 14 nV/√Hz at 10 kHz Wide bandwidth: 2 MHz unity-gain crossover Supply voltage: 4.5 V to 16 V (±2.25 V to ±8 V)

Operating temperature:  $-40^{\circ}$ C to  $+125^{\circ}$ C

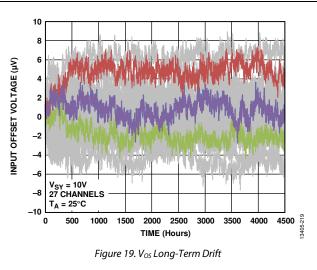

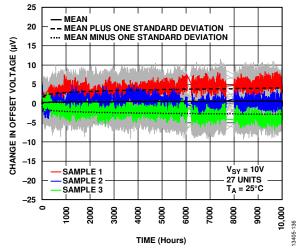

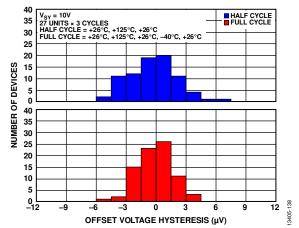

Long-term offset voltage drift (10,000 hours): 0.5 μV typical Temperature hysteresis: 1.5 μV typical

#### APPLICATIONS

- Laboratory and analytical instrumentation: spectrophotometers, chromatographs, mass spectrometers, and potentiostatic and amperostatic coulometry Instrumentation: picoammeters and coulombmeters

- Transimpedance amplifier (TIA) for photodiodes, ion

- chambers, and working electrode measurements High impedance buffering for chemical sensors and capacitive sensors

#### **GENERAL DESCRIPTION**

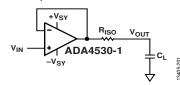

The ADA4530-1 is a femtoampere ( $10^{-15}$  A) level input bias current operational amplifier suitable for use as an electrometer that also includes an integrated guard buffer. It has an operating voltage range of 4.5 V to 16 V, enabling it to operate in conventional 5 V and 10 V single supply systems as well as ±2.5 V and ±5 V dual supply systems.

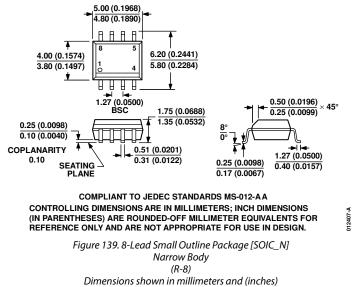

It provides ultralow input bias currents that are production tested at 25°C and at 125°C to ensure the device meets its performance goals in user systems. The integrated guard buffer isolates the input pins from leakage in the printed circuit board (PCB), minimizes board component count, and enables easy system design. The ADA4530-1 is available in an industrystandard surface-mount 8-lead SOIC package with a unique pinout optimized to prevent signals from coupling between the sensitive input pins, the power supplies, and the output pin while enabling easy routing of the guard ring traces.

The ADA4530-1 also offers low offset voltage, low offset drift, and low voltage and current noise needed for the types of applications that require such low leakages.

Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

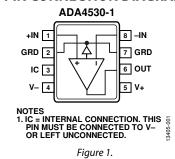

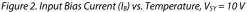

#### PIN CONNECTION DIAGRAM

ADA4530-1

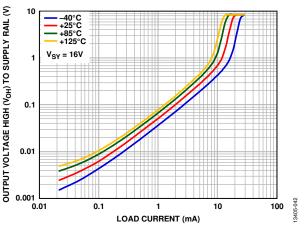

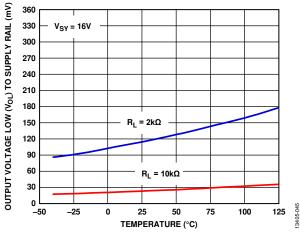

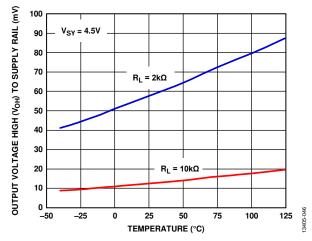

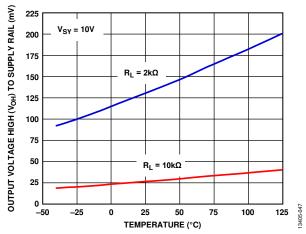

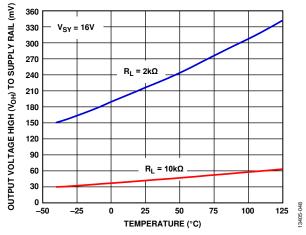

To maximize the dynamic range of the system, the ADA4530-1 has a rail-to-rail output stage that can typically drive to within 30 mV of the supply rails under a 10 k $\Omega$  load.

The ADA4530-1 operates over the  $-40^{\circ}$ C to  $+125^{\circ}$ C industrial temperature range and is available in an 8-lead SOIC package.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2015–2017 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

| Features                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications                                                                                                                                                                                                                                                           |

| Pin Connection Diagram 1                                                                                                                                                                                                                                               |

| General Description                                                                                                                                                                                                                                                    |

| Revision History                                                                                                                                                                                                                                                       |

| Specifications                                                                                                                                                                                                                                                         |

| 5 V Nominal Electrical Characteristics                                                                                                                                                                                                                                 |

| 10 V Nominal Electrical Characteristics                                                                                                                                                                                                                                |

| 15 V Nominal Electrical Characteristics                                                                                                                                                                                                                                |

| Absolute Maximum Ratings10                                                                                                                                                                                                                                             |

| Thermal Resistance10                                                                                                                                                                                                                                                   |

| ESD Caution10                                                                                                                                                                                                                                                          |

| Pin Configuration and Function Descriptions11                                                                                                                                                                                                                          |

| Typical Performance Characteristics12                                                                                                                                                                                                                                  |

| Main Amplifier, DC Performance12                                                                                                                                                                                                                                       |

| 1                                                                                                                                                                                                                                                                      |

| Main Amplifier, AC Performance                                                                                                                                                                                                                                         |

| -                                                                                                                                                                                                                                                                      |

| Main Amplifier, AC Performance                                                                                                                                                                                                                                         |

| Main Amplifier, AC Performance                                                                                                                                                                                                                                         |

| Main Amplifier, AC Performance                                                                                                                                                                                                                                         |

| Main Amplifier, AC Performance21Guard Amplifier27Theory of Operation29ESD Structure29                                                                                                                                                                                  |

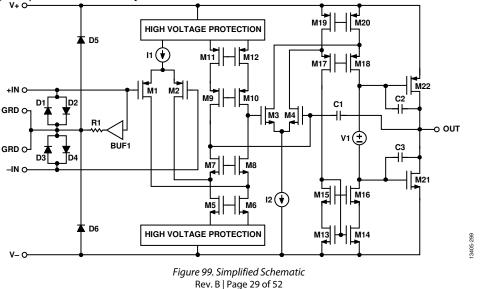

| Main Amplifier, AC Performance21Guard Amplifier27Theory of Operation29ESD Structure29Input Stage29                                                                                                                                                                     |

| Main Amplifier, AC Performance21Guard Amplifier27Theory of Operation29ESD Structure29Input Stage29Gain Stage30                                                                                                                                                         |

| Main Amplifier, AC Performance21Guard Amplifier27Theory of Operation29ESD Structure29Input Stage29Gain Stage30Output Stage30                                                                                                                                           |

| Main Amplifier, AC Performance21Guard Amplifier27Theory of Operation29ESD Structure29Input Stage29Gain Stage30Output Stage30Guard Buffer30                                                                                                                             |

| Main Amplifier, AC Performance21Guard Amplifier27Theory of Operation29ESD Structure29Input Stage29Gain Stage30Output Stage30Guard Buffer30Applications Information31                                                                                                   |

| Main Amplifier, AC Performance21Guard Amplifier27Theory of Operation29ESD Structure29Input Stage29Gain Stage30Output Stage30Guard Buffer30Applications Information31Input Protection.31                                                                                |

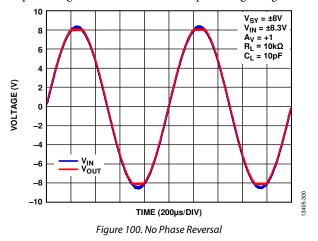

| Main Amplifier, AC Performance21Guard Amplifier27Theory of Operation29ESD Structure29Input Stage29Gain Stage30Output Stage30Guard Buffer30Applications Information31Input Protection31Single-Supply and Rail-to-Rail Output31                                          |

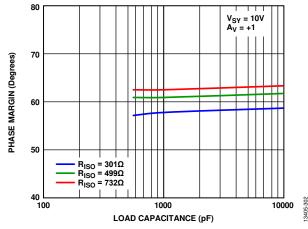

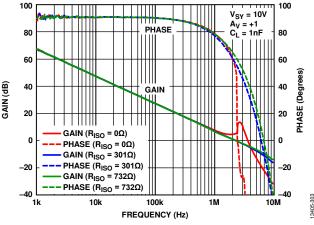

| Main Amplifier, AC Performance21Guard Amplifier27Theory of Operation29ESD Structure29Input Stage29Gain Stage30Output Stage30Guard Buffer30Guard Buffer30Applications Information31Input Protection31Single-Supply and Rail-to-Rail Output31Capacitive Load Stability31 |

| Input Resistance                               |

|------------------------------------------------|

| Input Offset Voltage                           |

| Insulation Resistance                          |

| Guarding                                       |

| Dielectric Relaxation                          |

| Humidity Effects                               |

| Contamination                                  |

| Cleaning and Handling                          |

| Solder Paste Selection                         |

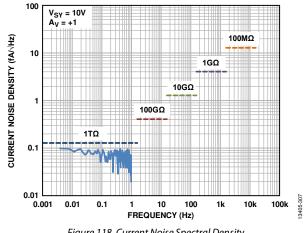

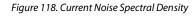

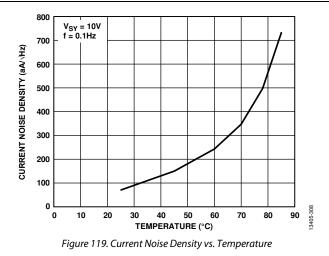

| Current Noise Considerations                   |

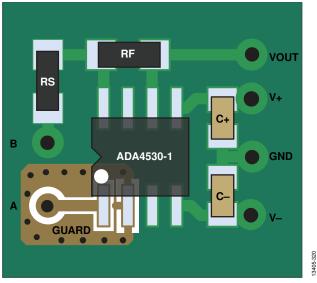

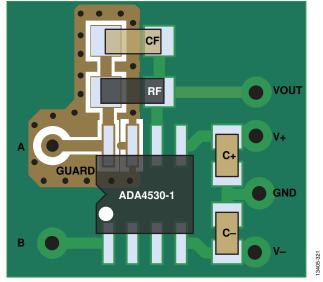

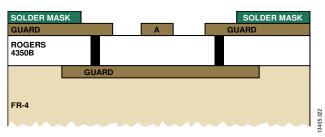

| Layout Guidelines                              |

| Physical Implementation of Guarding Techniques |

| Guard Ring 43                                  |

| Guard Plane 43                                 |

| Via Fence                                      |

| Cables and Connectors                          |

| Electrostatic Interferance                     |

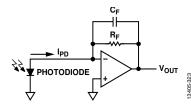

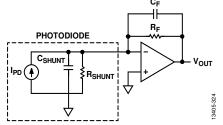

| Photodiode Interface                           |

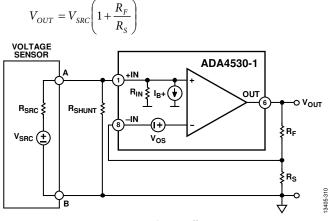

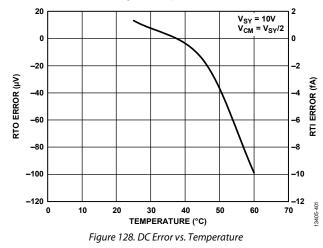

| DC Error Analysis                              |

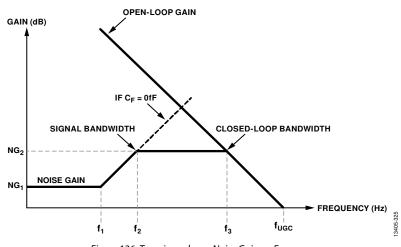

| AC Error Analysis                              |

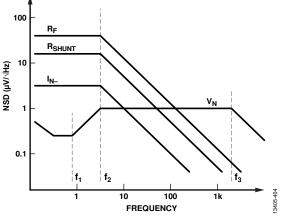

| Noise Analysis                                 |

| Design Recommendations                         |

| Design Example                                 |

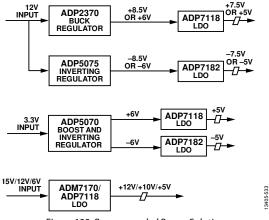

| Power Supply Recommendations                   |

| Power Supply Considerations                    |

Ordering Guide ...... 52

### **REVISION HISTORY**

| 5/2017—Rev. A to Rev. B                                      |

|--------------------------------------------------------------|

| Changes to Features Section and General Description Section1 |

| Changed Offset Voltage Parameter to Input Offset Voltage     |

| Parameter, Table 14                                          |

| Changed Offset Voltage Parameter to Input Offset Voltage     |

| Parameter, Table 2                                           |

| Changed Offset Voltage Parameter to Input Offset Voltage     |

| Parameter, Table 3                                           |

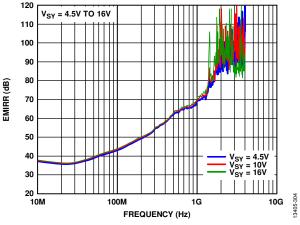

| Changes to EMI Rejection Ratio Section and Figure 10232      |

| Moved Figure 114                                             |

| Changes to Current Noise Considerations Section41            |

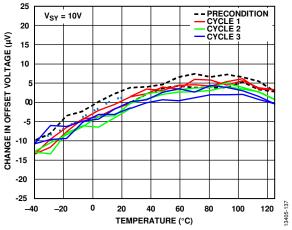

| Added Long-Term Drift Section, Temperature Hysteresis        |

| Section, Figure 136, Figure 137, and Figure 138; Renumbered  |

| Sequentially                                                 |

| Changes to Ordering Guide52                                  |

|                                                              |

| 3/2016—Rev. 0 to Rev. A                                    |

|------------------------------------------------------------|

| Changed DNC Pin to IC Pin Throughout                       |

| Changes to Figure 11                                       |

| Changes to Figure 3 and Table 610                          |

| Changes to Figure 2915                                     |

| Changes to Theory of Operation Section                     |

| Changes to Humidity Effects Section and Figure 112         |

| Added Power Supply Recommendations Section, Power          |

| Supply Considerations Section, Table 16, and Figure 133 to |

| Figure 135                                                 |

10/2015—Revision 0: Initial Version

### **SPECIFICATIONS** 5 V NOMINAL ELECTRICAL CHARACTERISTICS

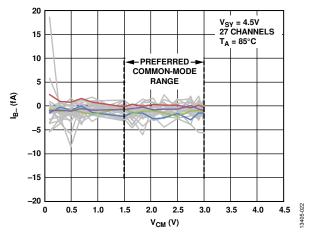

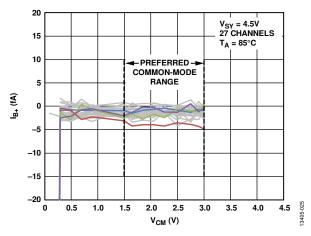

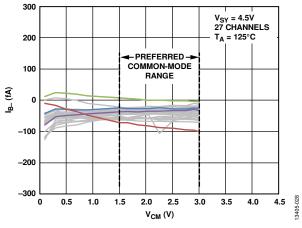

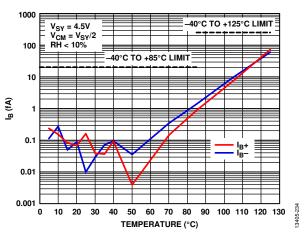

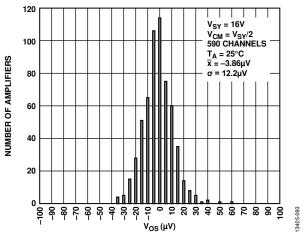

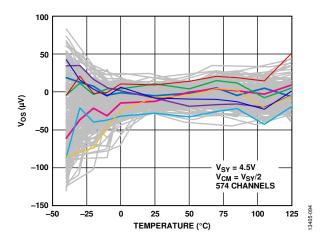

Supply voltage  $(V_{SY}) = 4.5$  V, common-mode voltage  $(V_{CM}) = V_{SY}/2$ ,  $T_A = 25^{\circ}$ C, unless otherwise specified. Typical specifications are equal to the average of the distribution from characterization, unless otherwise noted. Minimum and maximum specifications are tested in production, unless otherwise noted.

| Parameter <sup>1</sup>               | Symbol                     | Test Conditions/Comments                                                                     | Min  | Тур   | Max  | Unit   |

|--------------------------------------|----------------------------|----------------------------------------------------------------------------------------------|------|-------|------|--------|

| INPUT CHARACTERISTICS                |                            |                                                                                              |      |       |      |        |

| Input Bias Current <sup>2, 3</sup>   | IB                         | RH < 50%                                                                                     |      | <1    | ±20  | fA     |

|                                      |                            | -40°C < T <sub>A</sub> < +85°C, RH < 50%                                                     |      |       | ±20  | fA     |

|                                      |                            | −40°C < T <sub>A</sub> < +125°C, RH < 50%                                                    |      |       | ±250 | fA     |

| Input Offset Current <sup>3</sup>    | los                        | RH < 50%                                                                                     |      | <1    | ±20  | fA     |

|                                      |                            | −40°C < T <sub>A</sub> < +125°C, RH < 50%                                                    |      |       | ±150 | fA     |

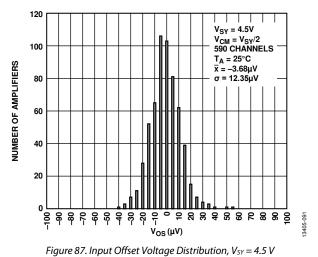

| Input Offset Voltage <sup>2, 4</sup> | Vos                        |                                                                                              |      | +8    | ±40  | μV     |

|                                      |                            | V <sub>CM</sub> = 1.5 V to 3 V                                                               |      | +9    | ±50  | μV     |

|                                      |                            | V <sub>CM</sub> = 1.5 V to 3 V, 0°C < T <sub>A</sub> < 125°C                                 |      |       | ±70  | μV     |

|                                      |                            | $V_{CM} = 1.5 \text{ V to } 3 \text{ V}, -40^{\circ}\text{C} < T_{A} < 0^{\circ}\text{C}$    |      |       | ±150 | μV     |

|                                      |                            | $V_{CM} = 0 V \text{ to } 3 V$                                                               |      |       | ±300 | μV     |

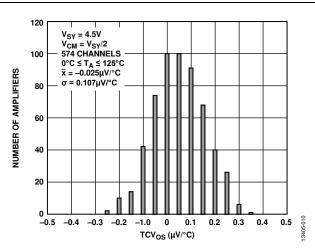

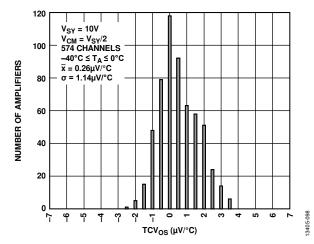

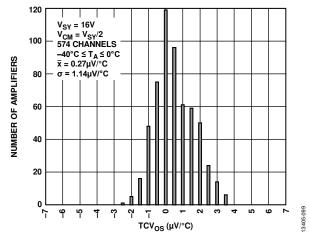

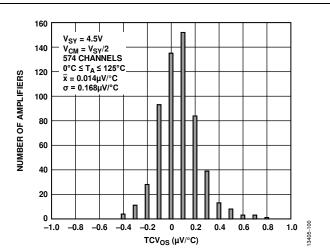

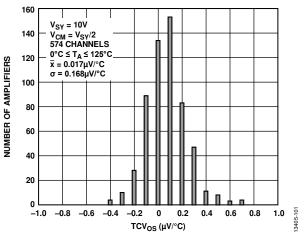

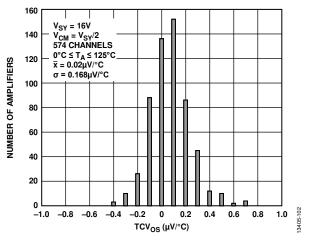

| Offset Voltage Drift <sup>2, 4</sup> | $\Delta V_{os} / \Delta T$ | 0°C < T <sub>A</sub> < 125°C                                                                 |      | +0.13 | ±0.5 | μV/°C  |

| 5                                    |                            | $-40^{\circ}C < T_{A} < 0^{\circ}C$                                                          |      | -0.7  | ±2.8 | μV/°C  |

| Input Voltage Range                  | IVR                        |                                                                                              | 0    |       | 3    | V      |

| Common-Mode Rejection Ratio          | CMRR                       | $V_{CM} = 1.5 V \text{ to } 3 V$                                                             | 92   | 114   |      | dB     |

| ,                                    |                            | -40°C < T <sub>A</sub> < +125°C                                                              | 90   |       |      | dB     |

|                                      |                            | $V_{CM} = 0 V \text{ to } 3 V$                                                               | 73   |       |      | dB     |

| Large Signal Voltage Gain            | Avo                        | $R_L = 2 \text{ k}\Omega$ to $V_{CM}$ , $V_{OUT} = 0.2 \text{ V}$ to 4.3 V                   | 120  | 143   |      | dB     |

| 5 5 5                                |                            | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                       | 120  |       |      | dB     |

| Input Resistance                     | R <sub>IN</sub>            | -40°C < T <sub>A</sub> < +125°C                                                              | -    | >100  |      | ТΩ     |

| Input Capacitance                    | CIN                        |                                                                                              |      | 8     |      | pF     |

| OUTPUT CHARACTERISTICS               |                            |                                                                                              |      | -     |      | - Ie . |

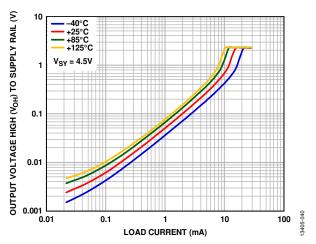

| Output Voltage High                  | Vон                        | $R_L = 10 \text{ k}\Omega \text{ to } V_{CM}$                                                | 4.47 | 4.49  |      | v      |

|                                      |                            | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                       | 4.46 |       |      | V      |

|                                      |                            | $R_L = 2 k\Omega \text{ to } V_{CM}$                                                         | 4.4  | 4.45  |      | v      |

|                                      |                            | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                       | 4.38 |       |      | v      |

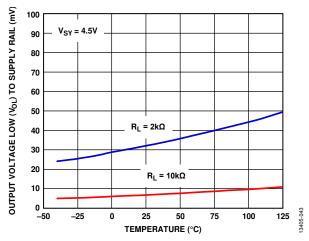

| Output Voltage Low                   | Vol                        | $R_L = 10 \text{ k}\Omega \text{ to } V_{CM}$                                                |      | 10    | 30   | mV     |

| output voltage zon                   | • OL                       | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                       |      | 10    | 40   | mV     |

|                                      |                            | $R_L = 2 k\Omega \text{ to } V_{CM}$                                                         |      | 30    | 100  | mV     |

|                                      |                            | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                       |      | 50    | 120  | mV     |

| Short-Circuit Current                | lsc                        | 10 C (14 (1125 C                                                                             |      |       | 120  |        |

| Source                               | 150                        |                                                                                              |      | 15    |      | mA     |

| Sink                                 |                            |                                                                                              |      | -30   |      | mA     |

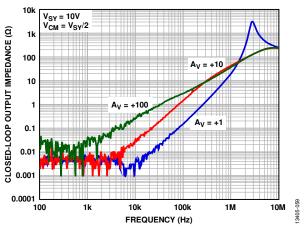

| Closed-Loop Output Impedance         | Zout                       | $f = 1 MHz, A_v = 1$                                                                         |      | 20    |      | Ω      |

| POWER SUPPLY                         | -001                       | · · · · · · · · · · · · · · · · · · ·                                                        |      | 20    |      |        |

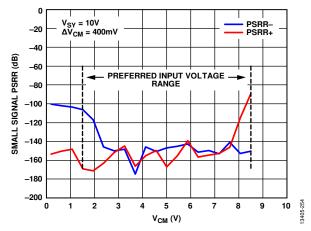

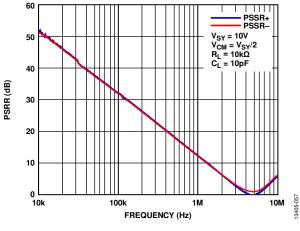

| Power Supply Rejection Ratio         | PSRR                       | $V_{SY} = 4.5 V$ to 16 V                                                                     | 130  | 150   |      | dB     |

| i ower supply nejection hado         | 1 5101                     | $-40^{\circ}C < T_A < +125^{\circ}C$                                                         | 130  | 150   |      | dB     |

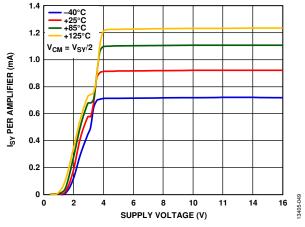

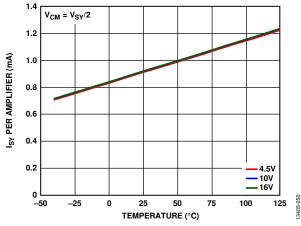

| Supply Current                       | lsy                        | $\int -40 C < T_A < T_Z S C$ $\int J_{OUT} = 0 mA$                                           | 150  | 0.9   | 1.3  | mA     |

| Supply current                       | 101                        | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                       |      | 0.2   | 1.5  | mA     |

| DYNAMIC PERFORMANCE                  |                            |                                                                                              |      |       | 1.5  |        |

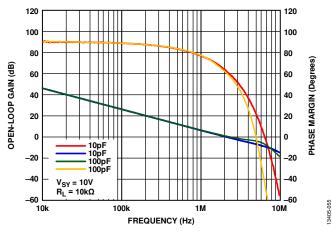

| Slew Rate                            | SR                         | $R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF}, A_V = 1$                                     |      | 1.4   |      | V/uc   |

|                                      |                            | -                                                                                            |      |       |      | V/µs   |

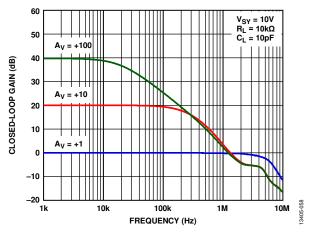

| Gain Bandwidth Product               | GBP                        | $V_{IN} = 10 \text{ mV rms}, R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF}, A_V = 100$       |      | 2     |      | MHz    |

| Unity-Gain Crossover                 | UGC                        | $V_{\rm IN} = 10 {\rm mV}$ rms, $R_{\rm L} = 10 {\rm k}\Omega$ , $C_{\rm L} = 10 {\rm pF}$ , |      | 2     |      | MHz    |

|                                      |                            | $A_{VO} = 1$                                                                                 |      | -     |      |        |

## ADA4530-1

| Parameter <sup>1</sup>                     | Symbol                    | Test Conditions/Comments                                                                                                     | Min | Тур    | Max | Unit    |

|--------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|---------|

| -3 dB Closed-Loop Bandwidth                | f <sub>-3dB</sub>         | $V_{\text{IN}}{=}10 \text{ mV rms},$ $R_{\text{L}}{=}10 \text{ k}\Omega,$ $C_{\text{L}}{=}10 \text{ pF},$ $A_{\text{V}}{=}1$ |     | 6      |     | MHz     |

| Phase Margin                               | Фм                        | $V_{\text{IN}}$ = 10 mV rms, $R_{\text{L}}$ = 10 k $\Omega,C_{\text{L}}$ = 10 pF, $A_{\text{VO}}$ = 1                        |     | 62     |     | Degrees |

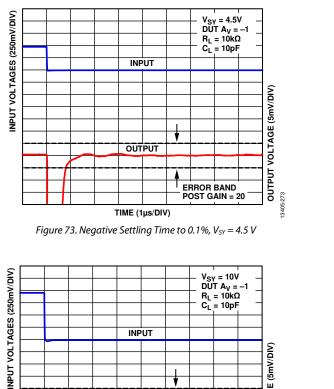

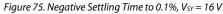

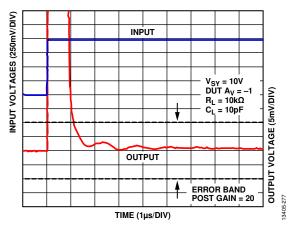

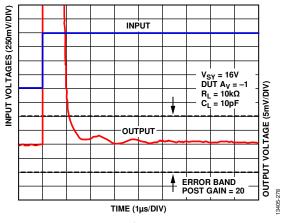

| Settling Time to 0.1%                      | ts                        | $V_{IN}$ = 0.5 V step, $R_L$ = 10 k $\Omega,$ $C_L$ = 10 pF, $A_V$ = $-1$                                                    |     | 5      |     | μs      |

| EMI Rejection Ratio of +IN                 | EMIRR                     | $V_{IN} = 100 \text{ mV} \text{ peak}, f = 400 \text{ MHz}$                                                                  |     | 50     |     | dB      |

|                                            |                           | V <sub>IN</sub> = 100 mV peak, f = 900 MHz                                                                                   |     | 60     |     | dB      |

|                                            |                           | V <sub>IN</sub> = 100 mV peak, f = 1800 MHz                                                                                  |     | 80     |     | dB      |

|                                            |                           | $V_{IN} = 100 \text{ mV peak}, f = 2400 \text{ MHz}$                                                                         |     | 90     |     | dB      |

| NOISE PERFORMANCE                          |                           |                                                                                                                              |     |        |     |         |

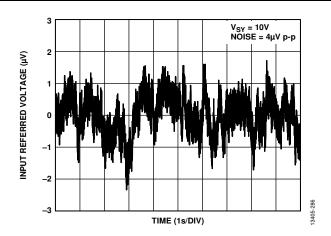

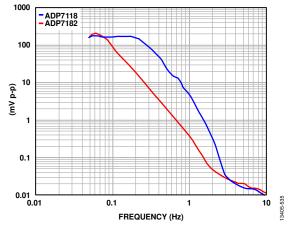

| Peak-to-Peak Voltage Noise                 | е⊾р-р                     | f = 0.1 Hz to 10 Hz                                                                                                          |     | 4      |     | μV p-р  |

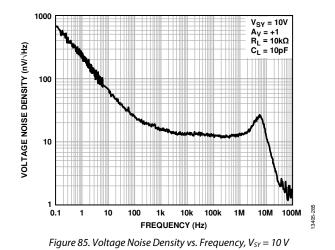

| Voltage Noise Density                      | e <sub>N</sub>            | f = 10 Hz                                                                                                                    |     | 80     |     | nV/√Hz  |

|                                            |                           | f = 1 kHz                                                                                                                    |     | 16     |     | nV/√Hz  |

|                                            |                           | f = 10 kHz                                                                                                                   |     | 14     |     | nV/√Hz  |

| Current Noise Density                      | IN                        | f = 0.1 Hz                                                                                                                   |     | 0.07   |     | fA/√Hz  |

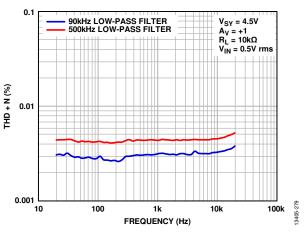

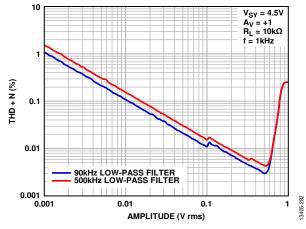

| Total Harmonic Distortion + Noise          | THD + N                   | $A_V = 1$ , f = 1 kHz, $V_{IN} = 0.5$ V rms                                                                                  |     |        |     |         |

| Bandwidth = 90 kHz                         |                           |                                                                                                                              |     | 0.003  |     | %       |

| Bandwidth = 500 kHz                        |                           |                                                                                                                              |     | 0.0045 |     | %       |

| GUARD BUFFER                               |                           |                                                                                                                              |     |        |     |         |

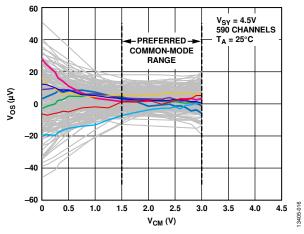

| Guard Offset Voltage <sup>2, 4, 5</sup>    | V <sub>GOS</sub>          | $V_{CM} = 1.5 V \text{ to } 3 V$                                                                                             |     | 15     | 100 | μV      |

|                                            |                           | $V_{CM} = 1.5 \text{ V to } 3 \text{ V}, 0^{\circ}\text{C} < T_A < 125^{\circ}\text{C}$                                      |     |        | 120 | μV      |

|                                            |                           | $V_{CM} = 1.5 \text{ V to } 3 \text{ V}, -40^{\circ}\text{C} < T_A < 0^{\circ}\text{C}$                                      |     |        | 250 | μV      |

|                                            |                           | $V_{CM} = 0.1 V \text{ to } 3 V$                                                                                             |     |        | 150 | μV      |

| Guard Offset Voltage Drift <sup>2, 4</sup> | $\Delta V_{GOS}/\Delta T$ | 0°C < T <sub>A</sub> < +125°C                                                                                                |     | 0.18   | 1   | μV/°C   |

|                                            |                           | $-40^{\circ}C < T_{A} < 0^{\circ}C$                                                                                          |     | 1.4    | 7   | μV/°C   |

| Output Impedance                           | ZGOUT                     |                                                                                                                              |     | 1      |     | kΩ      |

| Output Voltage Range                       |                           | $V_{GOS} < 150 \mu V$                                                                                                        | 0.1 |        | 3   | V       |

| –3 dB Bandwidth                            | f-3dBGUARD                | $V_{IN} = 10 \text{ mV rms}, C_L = 10 \text{ pF}$                                                                            |     | 5.5    |     | MHz     |

<sup>1</sup> These specifications represent the performance for 5 V  $\pm$  10% power supplies. All specifications are measured at the worst case 4.5 V supply voltage. <sup>2</sup> The maximum specifications at  $-40^{\circ}$ C < T<sub>A</sub>  $< +85^{\circ}$ C and  $-40^{\circ}$ C < T<sub>A</sub>  $< 0^{\circ}$ C are guaranteed from characterization. <sup>3</sup> RH is relative humidity (see the Humidity Effects section for more information). <sup>4</sup> The typical specifications are equal to the average plus the standard deviation of the distribution from characterization. <sup>5</sup> The guard offset voltage is the voltage difference between the guard output and the noninverting input.

#### **10 V NOMINAL ELECTRICAL CHARACTERISTICS**

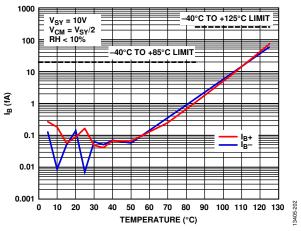

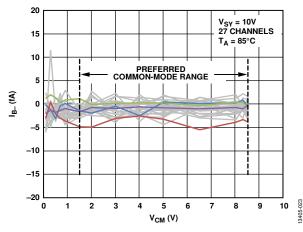

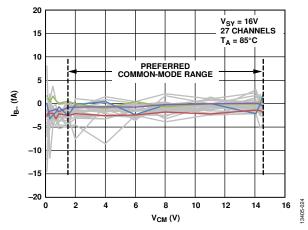

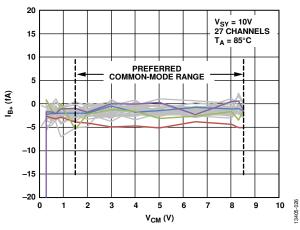

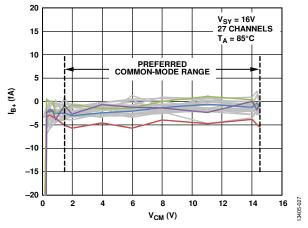

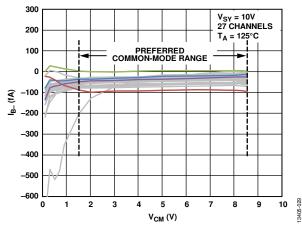

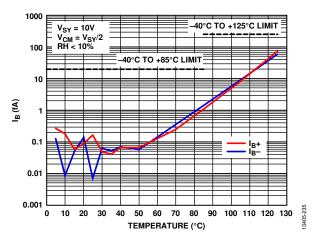

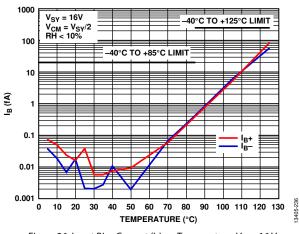

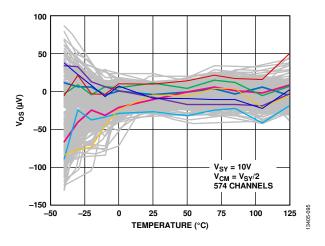

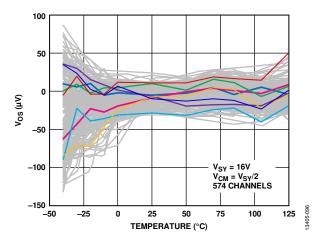

$V_{SY} = 10 \text{ V}, V_{CM} = V_{SY}/2, T_A = 25^{\circ}\text{C}$ , unless otherwise noted. Typical specifications are equal to the average of the distribution from characterization, unless otherwise noted. Minimum and maximum specifications are tested in production, unless otherwise noted.

| Parameter <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Symbol                   | Test Conditions/Comments                                                                                                    | Min  | Тур   | Max  | Unit       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-------|------|------------|

| INPUT CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                                                                                                             |      |       |      |            |

| Input Bias Current <sup>2, 3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IB                       | RH < 50%                                                                                                                    |      | <1    | ±20  | fA         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $-40^{\circ}C < T_A < +85^{\circ}C$ , RH $< 50\%$                                                                           |      |       | ±20  | fA         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | −40°C < T <sub>A</sub> < +125°C, RH < 50%                                                                                   |      |       | ±250 | fA         |

| Input Offset Current <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | los                      | RH < 50%                                                                                                                    |      | <1    | ±20  | fA         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | −40°C < T <sub>A</sub> < +125°C, RH < 50%                                                                                   |      |       | ±150 | fA         |

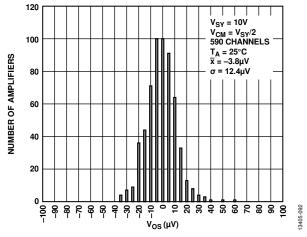

| Input Offset Voltage <sup>2, 4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Vos                      |                                                                                                                             |      | +8    | ±40  | μV         |

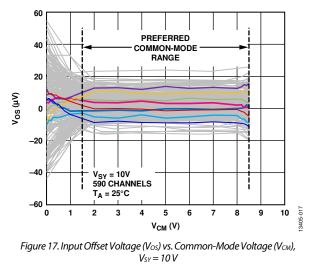

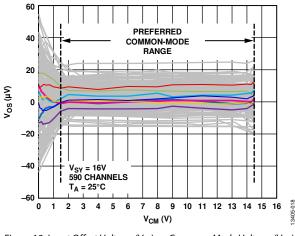

| . 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          | V <sub>CM</sub> = 1.5 V to 8.5 V                                                                                            |      | +9    | ±50  | μV         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $V_{CM} = 1.5 V$ to 8.5 V, 0°C < $T_A$ < 125°C                                                                              |      |       | ±70  | μV         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $V_{CM} = 1.5 V$ to 8.5 V, $-40^{\circ}C < T_A < 0^{\circ}C$                                                                |      |       | ±150 | μV         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $V_{CM} = 0 V \text{ to } 8.5 V$                                                                                            |      |       | ±300 | μV         |

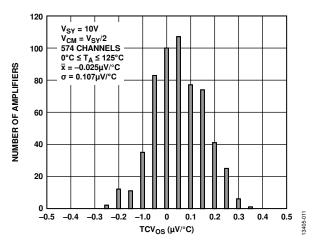

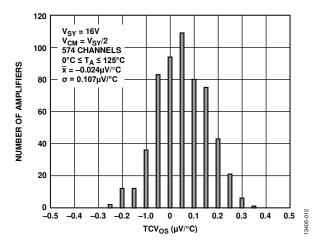

| Offset Voltage Drift <sup>2, 4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\Delta V_{os}/\Delta T$ | 0°C < T <sub>A</sub> < 125°C                                                                                                |      | +0.13 | ±0.5 | ,<br>μV/°C |

| , and the second s |                          | $-40^{\circ}C < T_{A} < 0^{\circ}C$                                                                                         |      | -0.7  | ±2.8 | μV/°C      |

| Input Voltage Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IVR                      |                                                                                                                             | 0    |       | 8.5  | V          |

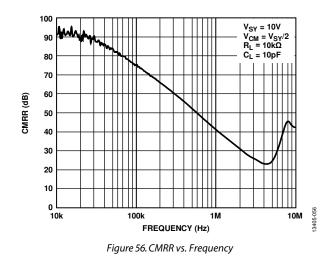

| Common-Mode Rejection Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CMRR                     | V <sub>CM</sub> = 1.5 V to 8.5 V                                                                                            | 105  | 114   |      | dB         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                                                      | 100  |       |      | dB         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $V_{CM} = 0$ V to 8.5 V                                                                                                     | 87   |       |      | dB         |

| Large Signal Voltage Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Avo                      | $R_L = 2 k\Omega \text{ to V}_{CM}, V_{OUT} = 0.5 \text{ V to } 9.5 \text{ V}$                                              | 125  | 150   |      | dB         |

| Large Signal Voltage Guilt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7.00                     | $-40^{\circ}C < T_A < +125^{\circ}C$                                                                                        | 125  | 150   |      | dB         |

| Input Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R <sub>IN</sub>          | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                                                      | 125  | >100  |      | ΤΩ         |

| Input Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |                                                                                                                             |      | 8     |      | pF         |

| OUTPUT CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |                                                                                                                             |      | 0     |      | Pi         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | N                        |                                                                                                                             | 0.06 | 0.07  |      | v          |

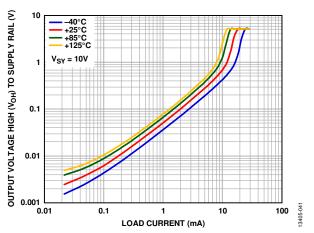

| Output Voltage High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Vон                      | $R_{L} = 10 \text{ k}\Omega \text{ to } V_{CM}$ $-40^{\circ}\text{C} < T_{A} < +125^{\circ}\text{C}$                        | 9.96 | 9.97  |      | V          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |                                                                                                                             | 9.94 | 0.07  |      |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $R_{L} = 2 k\Omega \text{ to } V_{CM}$                                                                                      | 9.93 | 9.87  |      | V          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .,                       | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                                                      | 9.75 | 4.5   |      | V          |

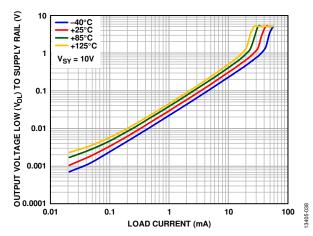

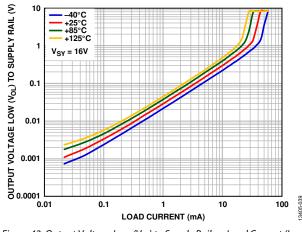

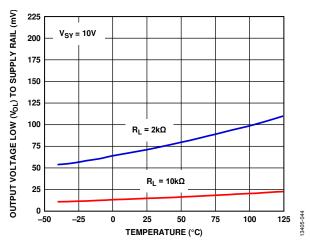

| Output Voltage Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Vol                      | $R_L = 10 k\Omega \text{ to } V_{CM}$                                                                                       |      | 15    | 40   | mV         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $-40^{\circ}C < T_{A} < +125^{\circ}C$                                                                                      |      |       | 60   | mV         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $R_L = 2 k\Omega \text{ to } V_{CM}$                                                                                        |      | 70    | 170  | mV         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | -40°C < T <sub>A</sub> < +125°C                                                                                             |      |       | 250  | mV         |

| Short-Circuit Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sub>sc</sub>          |                                                                                                                             |      |       |      |            |

| Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |                                                                                                                             |      | 15    |      | mA         |

| Sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |                                                                                                                             |      | -30   |      | mA         |

| Closed-Loop Output Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Zout                     | $f = 1 MHz, A_V = 1$                                                                                                        |      | 20    |      | Ω          |

| POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |                                                                                                                             |      |       |      |            |

| Power Supply Rejection Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PSRR                     | $V_{SY} = 4.5 V \text{ to } 16 V$                                                                                           | 130  | 150   |      | dB         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                                                                        | 130  |       |      | dB         |

| Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I <sub>SY</sub>          | $I_{OUT} = 0 \text{ mA}$                                                                                                    |      | 0.9   | 1.3  | mA         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | $-40^{\circ}C < T_A < +125^{\circ}C$                                                                                        |      |       | 1.5  | mA         |

| DYNAMIC PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |                                                                                                                             |      |       |      |            |

| Slew Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SR                       | $R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF}, A_V = 1$                                                                    |      | 1.4   |      | V/µs       |

| Gain Bandwidth Product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GBP                      | $V_{\text{IN}} = 10 \text{ mV rms}, R_{\text{L}} = 10 \text{ k}\Omega, C_{\text{L}} = 10 \text{ pF}, \\ A_{\text{V}} = 100$ |      | 2     |      | MHz        |

| Unity-Gain Crossover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | UGC                      | $\label{eq:VIN} \begin{array}{l} V_{IN}=10 \text{ mV rms}, R_L=10  k\Omega, C_L=10  p\text{F}, \\ A_{VO}=1 \end{array}$     |      | 2     |      | MHz        |

| -3 dB Closed-Loop Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f <sub>-3dB</sub>        | $\label{eq:VIN} \begin{array}{l} V_{IN}=10 \text{ mV rms}, R_L=10  k\Omega, C_L=10  p\text{F}, \\ A_V=1 \end{array}$        |      | 6     |      | MHz        |

| Phase Margin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Фм                       | $V_{IN} = 10 \text{ mV rms}, R_L = 10 \text{ k}\Omega, C_L = 10 \text{ pF},$<br>$A_{VO} = 1$                                |      | 62    |      | Degre      |

## ADA4530-1

| Parameter <sup>1</sup>                     | Symbol                      | Test Conditions/Comments                                                                           | Min | Тур    | Max | Unit   |

|--------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------|-----|--------|-----|--------|

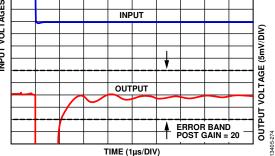

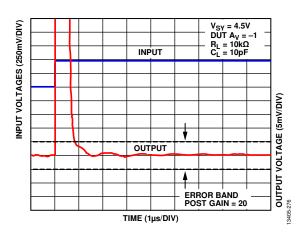

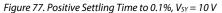

| Settling Time to 0.1%                      | ts                          | $\label{eq:VIN} \begin{array}{l} V_{IN}=1~V~step,~R_L=10~k\Omega,~C_L=10~pF,\\ A_V=-1 \end{array}$ |     | 6      |     | μs     |

| EMI Rejection Ratio of +IN                 | EMIRR                       | $V_{IN} = 100 \text{ mV} \text{ peak}, f = 400 \text{ MHz}$                                        |     | 50     |     | dB     |

|                                            |                             | V <sub>IN</sub> = 100 mV peak, f = 900 MHz                                                         |     | 60     |     | dB     |

|                                            |                             | $V_{IN} = 100 \text{ mV} \text{ peak}, f = 1800 \text{ MHz}$                                       |     | 80     |     | dB     |

|                                            |                             | $V_{IN} = 100 \text{ mV} \text{ peak}, f = 2400 \text{ MHz}$                                       |     | 90     |     | dB     |

| NOISE PERFORMANCE                          |                             |                                                                                                    |     |        |     |        |

| Peak-to-Peak Voltage Noise                 | е₀р-р                       | f = 0.1 Hz to 10 Hz                                                                                |     | 4      |     | μV p-p |

| Voltage Noise Density                      | e <sub>N</sub>              | f = 10 Hz                                                                                          |     | 80     |     | nV/√Hz |

|                                            |                             | f = 1 kHz                                                                                          |     | 16     |     | nV/√Hz |

|                                            |                             | f = 10 kHz                                                                                         |     | 14     |     | nV/√Hz |

| Current Noise Density                      | I <sub>N</sub>              | f = 0.1 Hz                                                                                         |     | 0.07   |     | fA/√Hz |

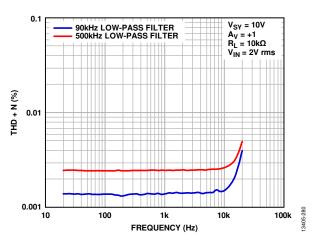

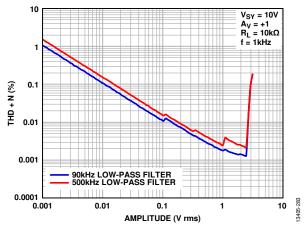

| Total Harmonic Distortion + Noise          | THD + N                     | $A_V = 1$ , f = 1 kHz, $V_{IN} = 2 V rms$                                                          |     |        |     |        |

| Bandwidth = 90 kHz                         |                             |                                                                                                    |     | 0.0015 |     | %      |

| Bandwidth = 500 kHz                        |                             |                                                                                                    |     | 0.0025 |     | %      |

| GUARD BUFFER                               |                             |                                                                                                    |     |        |     |        |

| Guard Offset Voltage <sup>2, 4, 5</sup>    | V <sub>GOS</sub>            | $V_{CM} = 1.5 V \text{ to } 8.5 V$                                                                 |     | 15     | 100 | μV     |

|                                            |                             | $V_{CM} = 1.5 V$ to 8.5 V, 0°C < $T_A$ < 125°C                                                     |     |        | 120 | μV     |

|                                            |                             | $V_{CM} = 1.5 V$ to 8.5 V, $-40^{\circ}C < T_A < 0^{\circ}C$                                       |     |        | 250 | μV     |

|                                            |                             | $V_{CM} = 0.1 V \text{ to } 8.5 V$                                                                 |     |        | 150 | μV     |

| Guard Offset Voltage Drift <sup>2, 4</sup> | $\Delta V_{GOS} / \Delta T$ | 0°C < T <sub>A</sub> < 125°C                                                                       |     | 0.18   | 1   | μV/°C  |

|                                            |                             | $-40^{\circ}C < T_{A} < 0^{\circ}C$                                                                |     | 1.4    | 7   | μV/°C  |

| Output Impedance                           | Z <sub>GOUT</sub>           |                                                                                                    |     | 1      |     | kΩ     |

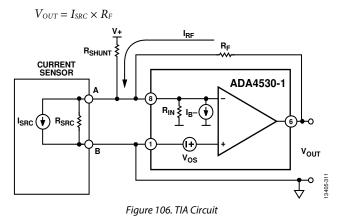

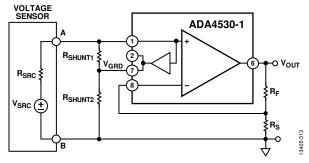

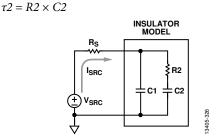

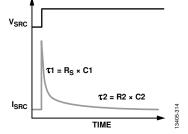

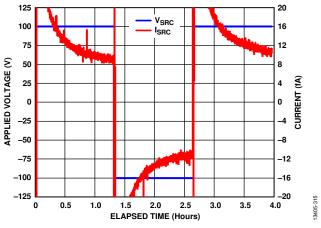

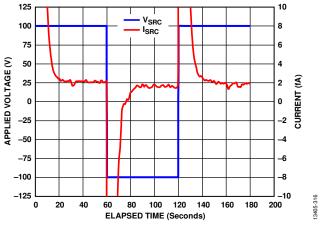

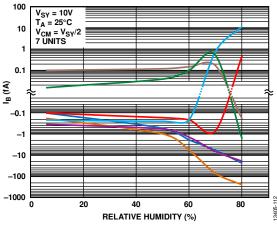

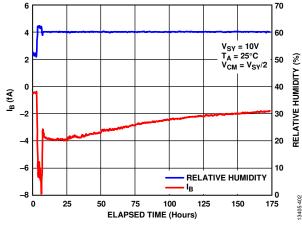

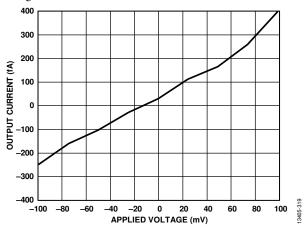

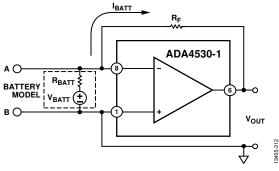

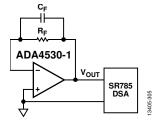

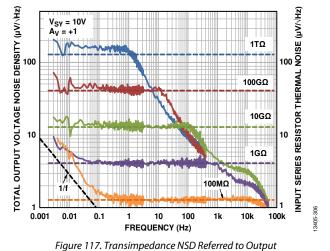

| Output Voltage Range                       |                             | $V_{GOS} < 150 \ \mu V$                                                                            | 0.1 |        | 8.5 | V      |