# National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

### LMV7231

# Hex Window Comparator with 1.5% Precision and 400mV Reference

### **General Description**

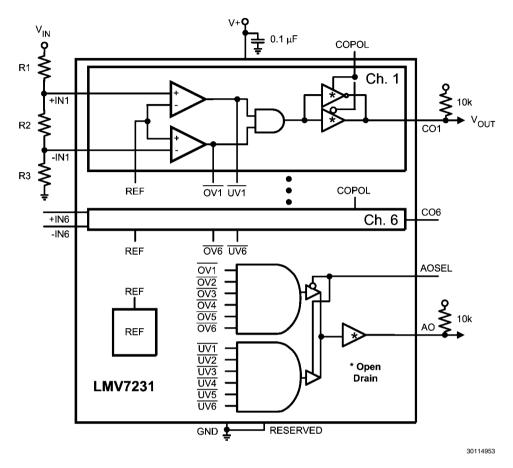

The LMV7231 is a 1.5% accurate Hex Window Comparator which can be used to monitor power supply voltages. The device uses an internal 400mV reference for the comparator trip value. The comparator set points can be set via external resistor dividers. The LMV7231 has 6 outputs (CO1-CO6) that signal an under-voltage or over-voltage event for each power supply input. An output (AO) is also provided to signal when any of the power supply inputs have an over-voltage or under-voltage event. This ability to signal an under-voltage or over-voltage event for the individual power supply inputs, in addition to an output to signal such an event on any of the power supply inputs adds unparalleled system protection capability.

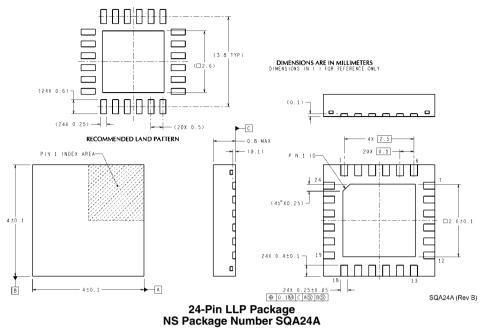

The LMV7231's +2.2V to +5.5V power supply voltage range, low supply current, and input/output voltage range above V+ make it ideal for a wide range of power supply monitoring applications. Operation is guaranteed over the -40°C to +125°C temperature range. The device is available in a 24-pin LLP package.

#### **Features**

(For  $V_S = 3.3V \pm 10\%$ , Typical unless otherwise noted)

- High accuracy voltage reference: 400 mV

- Threshold Accuracy: ±1.5% (max)

- Wide supply voltage range +2.2V to +5.5V

- Input/Output voltage range above V+

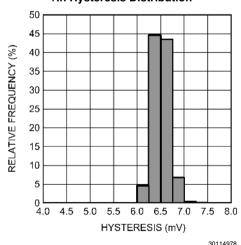

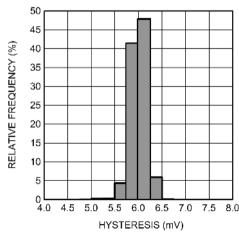

- Internal hysteresis: 6mV

- Propagation delay: 2.6 μs to 5.6 μs

- Supply Current 7.7 µA per channel

- 24 lead LLP package

- Temperature range: -40°C to 125°C

#### **Applications**

- Power Supply Voltage Detection

- Battery Monitoring

- Handheld Instruments

- Relay Driving

- Industrial Control Systems

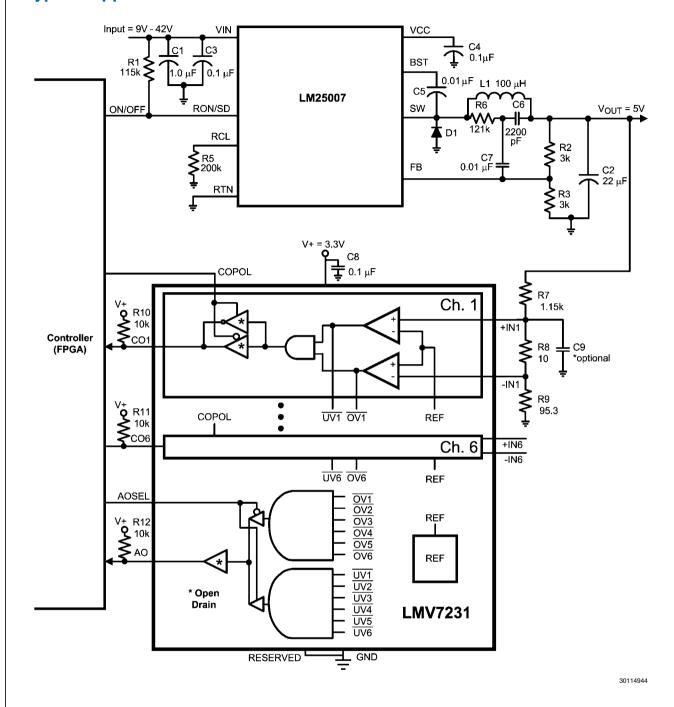

# **Typical Application Circuit**

150°C

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance (Note 2)

Human Body Model 2000V

Machine Model 200V

Supply Voltage 6V

Voltage at Input/Output Pin 6V to (GND – 0.3V)

Output Current 10mA

Total Package Current 50mA

Storage Temp Range –65°C to +150°C

Junction Temperature (Note 3)

For soldering specifications:

see product folder at www.national.com and www.national.com/ms/MS/MS-SOLDERING.pdf

## **Operating Ratings** (Note 1)

Supply Voltage 2.2V to 5.5V

Junction Temperature Range

(Note 3) -40°C to +125°C

Package Thermal Resistance,  $\theta_{IA}$

24 Lead LLP 38°C/W

+3.3V Electrical Characteristics Unless otherwise specified, all limits guaranteed for  $T_A = 25^{\circ}C$ ,  $V_{+} = 3.3V \pm 10^{\circ}$ , GND = 0V, and  $R_L > 1M\Omega$ . Boldface limits apply for  $T_A = -10^{\circ}C$  to +70°C.

| Symbol              | Parameter                                         | Condition                                      | Min<br>(Note 5)     | Typ<br>(Note 4) | Max<br>(Note 5)ns   | Units |

|---------------------|---------------------------------------------------|------------------------------------------------|---------------------|-----------------|---------------------|-------|

| V <sub>THR</sub>    | Threshold: Input Rising                           | $R_L = 10k\Omega$                              | 394<br><b>391.4</b> | 400             | 406<br><b>408.6</b> | mV    |

| $V_{THF}$           | Threshold: Input Falling                          | $R_L = 10k\Omega$                              | 386<br><b>383.8</b> | 394             | 401<br><b>403.2</b> | mV    |

| $V_{HYST}$          | Hysteresis (V <sub>THR</sub> – V <sub>THF</sub> ) | $R_L = 10k\Omega$                              | 3.9                 | 6.0             | 8.8                 | mV    |

| I <sub>BIAS</sub>   | Input Bias Current                                | $V_{IN} = V+$ , GND, and 5.5V                  | −5<br><b>−15</b>    | 0.05            | 5<br><b>15</b>      | nA    |

| V <sub>OL</sub>     | Output Low Voltage                                | I <sub>L</sub> = 5mA                           |                     | 160             | 200<br><b>250</b>   | mV    |

| I <sub>OFF</sub>    | Output Leakage Current                            | $V_{OUT} = V+$ , 5.5V and 40mV of overdrive    |                     |                 | 0.4<br><b>1</b>     | μΑ    |

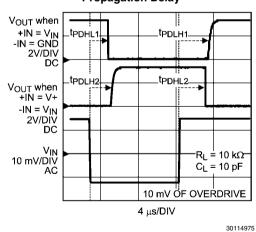

| t <sub>PDHL1</sub>  | High-to-Low Propagation Delay (+IN falling)       | 10mV of overdrive                              |                     | 2.6             | 6                   | μs    |

| t <sub>PDHL2</sub>  | High-to-Low Propagation Delay (-IN rising)        | 10mV of overdrive                              |                     | 5.4             | 10                  | μs    |

| t <sub>PDLH1</sub>  | Low-to-High Propagation Delay (+IN rising)        | 10mV of overdrive                              |                     | 5.6             | 10                  | μs    |

| t <sub>PDLH2</sub>  | Low-to-High Propagation Delay (-IN falling)       | 10mV of overdrive                              |                     | 2.8             | 6                   | μs    |

| t <sub>r</sub>      | Output Rise Time                                  | $C_L = 10pF, R_L = 10k\Omega$                  |                     | 0.5             |                     | μs    |

| t <sub>f</sub>      | Output Fall Time                                  | $C_L = 100pF, R_L = 10k\Omega$                 |                     |                 | 0.25<br><b>0.3</b>  | μs    |

| I <sub>IN(1)</sub>  | Digital Input Logic "1" Leakage Current           |                                                |                     |                 | 0.2<br><b>1</b>     | μΑ    |

| I <sub>IN(0)</sub>  | Digital Input Logic "0" Leakage Current           |                                                |                     |                 | 0.2<br><b>1</b>     | μΑ    |

| V <sub>IH</sub>     | Digital Input Logic "1" Voltage                   |                                                | 0.70 × V+           |                 |                     | V     |

| V <sub>IL</sub>     | Digital Input Logic "0" Voltage                   |                                                |                     |                 | 0.30 × V+           | V     |

| s                   | Power Supply Current                              | No loading (outputs high)                      |                     | 46              | 60<br><b>84</b>     | μΑ    |

| V <sub>TH</sub> PSS | V <sub>TH</sub> Power Supply Sensitivity (Note 6) | V+ Ramp Rate = 1.1ms<br>V+ Step = 2.5V to 4.5V |                     |                 | +400                | μV    |

|                     |                                                   | V+ Ramp Rate = 1.1ms<br>V+ Step = 4.5V to 2.5V | -400                |                 |                     | μV    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

Note 3: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

Note 4: Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

Note 5: Limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlations using the Statistical Quality Control (SQC) method.

Note 6: V<sub>TH</sub> Power Supply Sensitivity is defined as the temporary shift in the internal voltage reference due to a step on the V+ pin.

### **Connection Diagram**

###

30114942

# **Pin Descriptions**

| Pin | Symbol   | Туре                              | Description                                                                                                                                                                                    |  |

|-----|----------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | -IN1     | Analog Input                      | Negative input for window comparator 1.                                                                                                                                                        |  |

| 2   | +IN1     | Analog Input                      | Positive input for window comparator 1.                                                                                                                                                        |  |

| 3   | -IN2     | Analog Input                      | Negative input for window comparator 2.                                                                                                                                                        |  |

| 4   | +IN2     | Analog Input                      | Positive input for window comparator 2.                                                                                                                                                        |  |

| 5   | -IN3     | Analog Input                      | Negative input for window comparator 3.                                                                                                                                                        |  |

| 6   | +IN3     | Analog Input                      | Positive input for window comparator 3.                                                                                                                                                        |  |

| 7   | -IN4     | Analog Input                      | Negative input for window comparator 4.                                                                                                                                                        |  |

| 8   | +IN4     | Analog Input                      | Positive input for window comparator 4.                                                                                                                                                        |  |

| 9   | -IN5     | Analog Input                      | Negative input for window comparator 5.                                                                                                                                                        |  |

| 10  | +IN5     | Analog Input                      | Positive input for window comparator 5.                                                                                                                                                        |  |

| 11  | -IN6     | Analog Input                      | Negative input for window comparator 6.                                                                                                                                                        |  |

| 12  | +IN6     | Analog Input                      | Positive input for window comparator 6.                                                                                                                                                        |  |

| 13  | RESERVED | Digital Input                     | Connect to GND.                                                                                                                                                                                |  |

| 14  | GND      | Power                             | Ground reference pin for the power supply voltage.                                                                                                                                             |  |

| 15  | COPOL    | Digital Input                     | The state of this pin determines whether the CO1-CO6 pins are active "HIGH" or "LOW". When tied LOW the CO1-CO6 outputs will go LOW to indicate an out of window comparison.                   |  |

| 16  | AOSEL    | Digital Input                     | The state of this pin determines whether the AO pin is active on an over-voltage or under-voltage event. When tied LOW the AO output will be active upon an over-voltage event.                |  |

| 17  | АО       | Open-Drain NMOS<br>Digital Output | This output is the ANDED combination of either the overvoltage comparator outputs or the under-voltage comparator outputs and is controlled by the state of the AOSEL. AO pin is active "LOW". |  |

| 18  | CO6      | Open-Drain NMOS Digital Output    | Window comparator 6 NMOS open-drain output.                                                                                                                                                    |  |

| 19  | CO5      | Open-Drain NMOS Digital Output    | Window comparator 5 NMOS open-drain output.                                                                                                                                                    |  |

| 20  | CO4      | Open-Drain NMOS Digital Output    | Window comparator 4 NMOS open-drain output.                                                                                                                                                    |  |

| 21  | CO3      | Open-Drain NMOS Digital Output    | Window comparator 3 NMOS open-drain output.                                                                                                                                                    |  |

| 22  | CO2      | Open-Drain NMOS<br>Digital Output | Window comparator 2 NMOS open-drain output.                                                                                                                                                    |  |

| 23  | CO1      | Open-Drain NMOS<br>Digital Output | Window comparator 1 NMOS open-drain output.                                                                                                                                                    |  |

| 24  | V+       | Power                             | Power supply pin.                                                                                                                                                                              |  |

| DAP | DAP      | Thermal Pad                       | Die Attach Paddle (DAP) connect to GND.                                                                                                                                                        |  |

# **Ordering Information**

| Package    | Part Number | Package Marking | Transport Media          | NSC Drawing |

|------------|-------------|-----------------|--------------------------|-------------|

| 24-Pin LLP | LMV7231SQ   | L7231SQ         | 1000 Units Tape and Reel | SQA24A      |

| NOPB       | LMV7231SQE  |                 | 250 Units Tape and Reel  |             |

|            | LMV7231SQX  |                 | 4500 Units Tape and Reel |             |

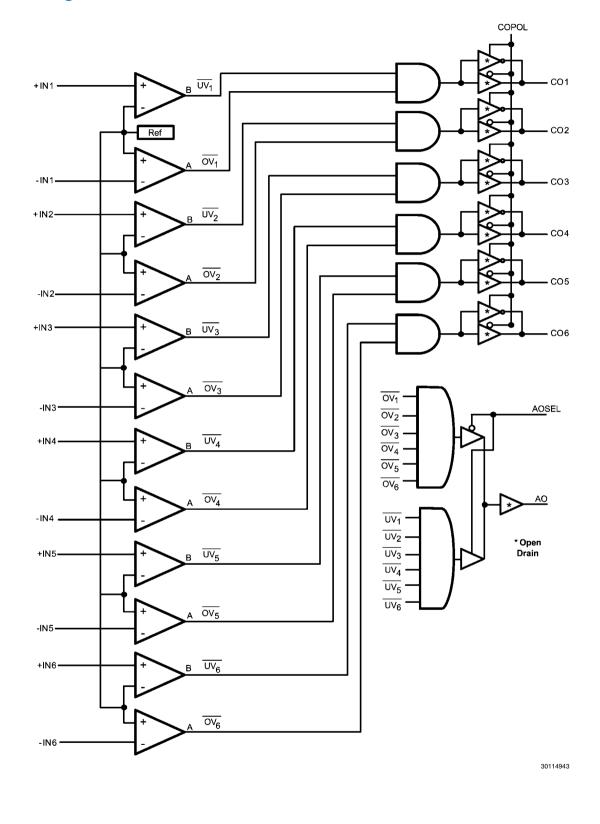

# **Block Diagram**

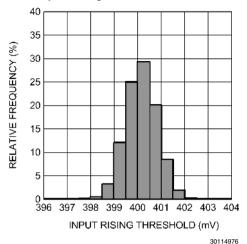

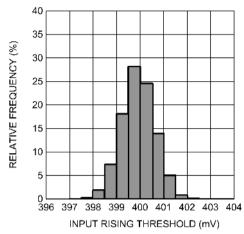

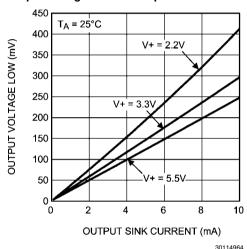

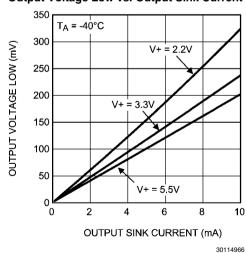

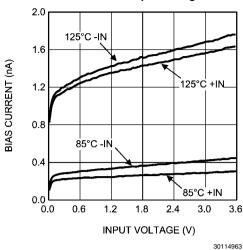

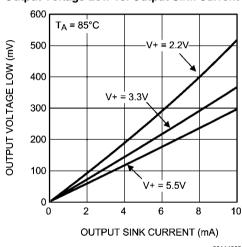

# **Typical Performance Characteristics** $V^+ = 3.3V$ and $T_A = 25^{\circ}C$ unless otherwise noted.

#### +In Input Rising Threshold Distribution

#### -In Input Rising Threshold Distribution

30114979

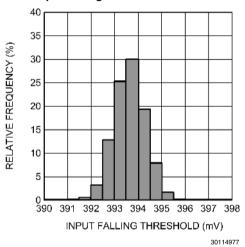

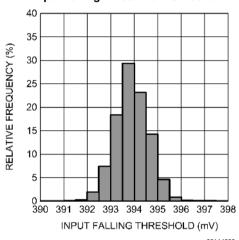

#### +In Input Falling Threshold Distribution

-In Input Falling Threshold Distribution

30114980

### +In Hysteresis Distribution

-In Hysteresis Distribution

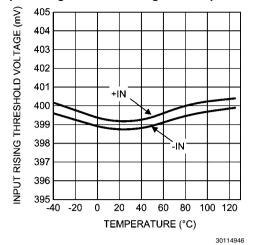

#### Input Rising Threshold Voltage vs. Temperature

# Input Rising Threshold Voltage vs. Supply Voltage

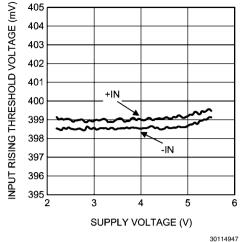

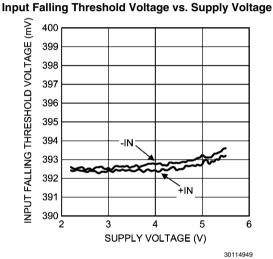

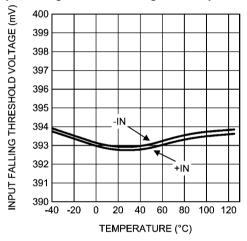

#### Input Falling Threshold Voltage vs. Temperature

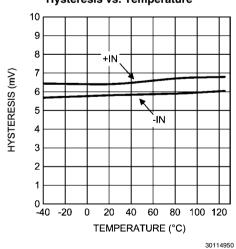

### Hysteresis vs. Temperature

#### Hysteresis vs. Supply Voltage

www.national.com

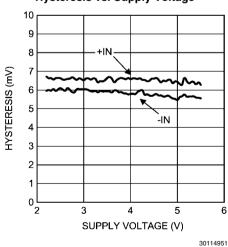

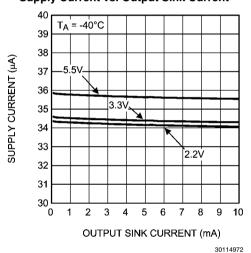

#### Supply Current vs. Supply Voltage and Temperature

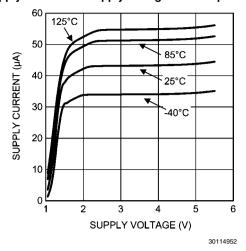

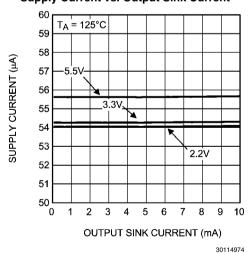

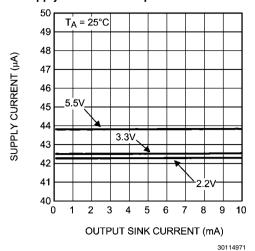

### **Supply Current vs. Output Sink Current**

### Supply Current vs. Output Sink Current

#### Supply Current vs. Output Sink Current

#### Supply Current vs. Output Sink Current

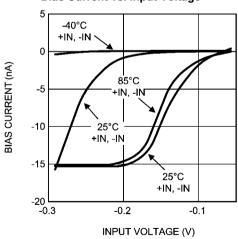

#### Bias Current vs. Input Voltage

30114961

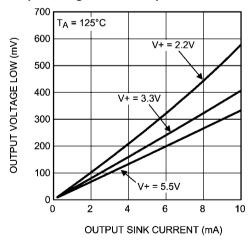

#### **Output Voltage Low vs. Output Sink Current**

#### **Output Voltage Low vs. Output Sink Current**

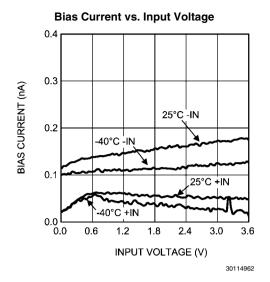

#### Bias Current vs. Input Voltage

#### **Output Voltage Low vs. Output Sink Current**

#### **Output Voltage Low vs. Output Sink Current**

30114967

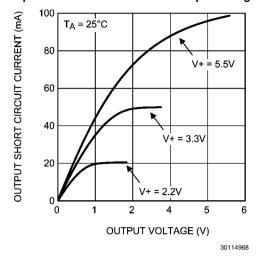

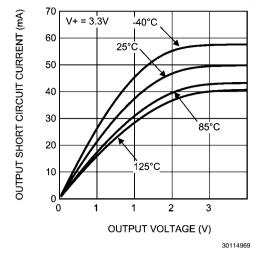

#### **Output Short Circuit Current vs. Output Voltage**

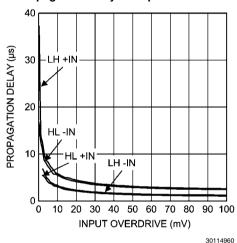

#### **Propagation Delay vs. Input Overdrive**

#### **Propagation Delay**

#### **Output Short Circuit Current vs. Output Voltage**

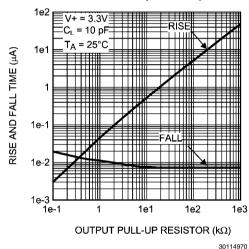

#### Rise and Fall Times vs. Output Pull-Up Resistor

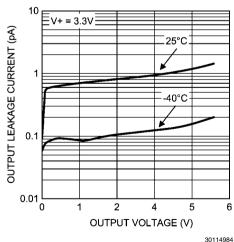

#### **Output Leakage Current vs. Output Voltage**

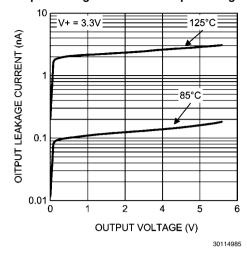

### Output Leakage Current vs. Output Voltage

## **Application Information**

#### **3 RESISTOR VOLTAGE DIVIDER SELECTION**

The LMV7231 trip points can be set by external resistor dividers as shown in Figure 1

**FIGURE 1. External Resistor Dividers**

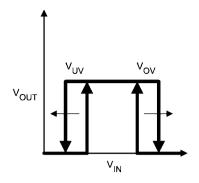

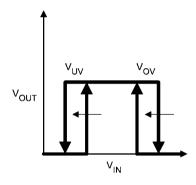

Each trip point, over-voltage, V<sub>OV</sub>, and under-voltage, V<sub>UV</sub>, can be optimized for a falling supply, V<sub>THF</sub>, or a rising supply,  $V_{THR}$ . Therefore there are  $2^2 = 4$  different optimization cases. Exiting the voltage detection window (Figure 2), entering the window (Figure 3), rising into and out of the window (Figure 4), falling into and out of the window (Figure 5). Note that for each case each trip point can be optimized for either a rising or falling signal, not both. The governing equations make it such that if the same resistor, R3, and over/under-voltage ratio, V<sub>OV</sub>/V<sub>UV</sub>, is used across the channels the same nominal current will travel through the resistor ladder. As a result R2 will also be the same across channels and only R1 needs to change to set voltage detection window maximizing reuse of resistor values and minimizing design complexity. Select the R3 resistor value to be below  $100k\Omega$  so the current through the divider ladder is much greater than the LMV7231 bias current. If the current traveling through the resistor divider is on the same magnitude of the LMV7231  $I_{BIAS}$ , the  $I_{BIAS}$  current will create error in your circuit and cause trip voltage shifts. Keep in mind the greatest error due to  $I_{\mbox{\footnotesize BIAS}}$  will be caused when that current passes through the greatest equivalent resistance, REQ = R1 (R2+R3), which will be seen by the positive input of the window comparator, +IN.

R3 set

$$R2 = R3((V_{THF}/V_{THR})V_{OV}/V_{UV} - 1)$$

$$R1 = R3((1/V_{THR})V_{OV} - (V_{THF}/V_{THR})V_{OV}/V_{UV})$$

Ex.

$$V_{OV} = 3.465V$$

,  $V_{UV} = 3.135V$ , i.e.  $V_{RANGE} = 3.3V + /-5\%$

R3 set to 10 k $\Omega$

$$R2 = 10k((0.394/0.4)3.465/3.135 - 1) \approx 887\Omega$$

$$\text{R1} = 10 \text{k} ((1/0.4)3.465 - (0.394/0.4)3.465/3.135) \approx 75 \text{ k}\Omega$$

3011495

#### FIGURE 2. Exiting the Voltage Detection Window

R3 set

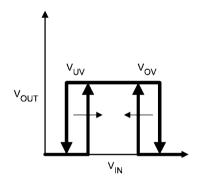

$$R2 = R3((V_{THR}/V_{THF})V_{OV}/V_{UV} - 1)$$

$$R1 = R3((1/V_{THF})V_{OV} - (V_{THR}/V_{THF})V_{OV}/V_{UV})$$

Ex.

$$V_{OV}$$

= 3.465V,  $V_{UV}$  = 3.135V, i.e.  $V_{RANGE}$  = 3.3V +/- 5%

R3 set to 10  $k\Omega$

R2 =  $10k((0.4/0.394)3.465/3.135 - 1) \approx 1.21 \text{ k}\Omega$

R1 = 10k((1/0.394)3.465 - (0.4/0.394)3.465/3.135)  $\approx$  76.8 k $\Omega$

30114955

#### FIGURE 3. Entering the Voltage Detection Window

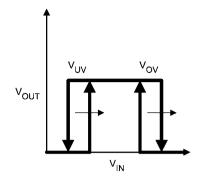

R3 set

$$R2 = R3(V_{OV}/V_{UV} - 1)$$

$$\mathsf{R1} = \mathsf{R3}((1/\mathsf{V}_\mathsf{THR})\mathsf{V}_\mathsf{OV} - \mathsf{V}_\mathsf{OV}/\mathsf{V}_\mathsf{UV})$$

Ex.

$$V_{OV}$$

= 3.465V,  $V_{UV}$  = 3.135V, i.e.  $V_{RANGE}$  = 3.3V +/- 5%

R3 set to 10 k $\Omega$

$$R2 = 10k((3.465/3.135) - 1) \approx 1.05 k\Omega$$

R1 =

$$10k((1/0.4)3.465 - 3.465/3.135) \approx 75 k\Omega$$

30114956

# FIGURE 4. Rising Into and Out Of the Voltage Detection Window

R3 set

$$R2 = R3(V_{OV}/V_{UV} - 1)$$

$$R1 = R3((1/V_{THF})V_{OV} - V_{OV}/V_{UV})$$

Ex.

$$V_{OV} = 3.465V$$

,  $V_{UV} = 3.135V$ , i.e.  $V_{RANGE} = 3.3V + /-5\%$

R3 set to 10  $k\Omega$

$$R2 = 10k((3.465/3.135) - 1) \approx 1.05 k\Omega$$

R1 =

$$10k((1/0.394)3.465 - 3.465/3.135) \approx 76.8 \text{ k}\Omega$$

30114957

# FIGURE 5. Falling Into and Out Of the Voltage Detection Window

#### INPUT/OUTPUT VOLTAGE RANGE ABOVE V+

The LMV7231 Hex Window Comparator with 1.5% precision can accurately monitor up to 6 power rails or batteries at one time. The input and output voltages of the device can exceed the supply voltage, V+, of the comparator, and can be up to the absolute maximum ratings without causing damage or performance degradation. The typical μC input pin with crowbar diode ESD protection circuitry will not allow the input to go above V+, and thus its usefulness is limited in power supply supervision applications.

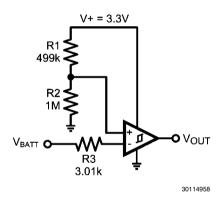

The supply independent inputs of the window comparator blocks allow the LMV7231 to be tolerant of system faults. For example if the power is suddenly removed from the LMV7231 due to a system malfunction yet there still exists a voltage on the input, this will not be an issue as long as the monitored input voltage does not exceed absolute maximum ratings. Another example where this feature comes in handy is a battery sense application such as the one in Figure 6. The boards may be sitting on the shelf unbiased with V+ grounded, and yet have a fully charged battery on board. If the comparator measuring the battery had crowbar diodes, the diode from -IN to V+ would turn on, sourcing current from the battery eventually draining the battery. However, when using the LMV7231 no current, except the low input bias current of the device, will flow into the chip, and the battery charge will be preserved.

FIGURE 6. Battery Sense Application

The output pin voltages of the device can also exceed the supply voltage, V+, of the comparator. This provides extra flexibility and enables designs which pull up the outputs to higher voltage levels to meet system requirements. For example it's possible to run the LMV7231 at its minimum operating voltage, V+ = +2.2V, but pull up the output up to the absolute maximum ratings to bias a blue LED, with a forward voltage of  $V_{\rm F} = +4V$ .

In a power supply supervision application the hardwired LMV7231 is a sound solution compared to the uC with software alternative for several reasons. First, startup is faster. During startup you don't need to account for code loading time, oscillator ramp time, and reset time. Second, operation is quick. The LMV7231 has a maximum propagation delay in the µs and isn't affected by sampling and conversion delays related to reading data, calculating data, and setting flags. Third, less overhead. The LMV7231 doesn't require an expensive power consuming microcontroller nor is it dependent on controller code which could get damaged or crash.

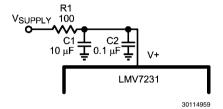

#### POWER SUPPLY BYPASSING

Bypass the supply pin, V+, with a 0.1  $\mu$ F ceramic capacitor placed close to the V+ pin. If transients with rise/fall times of 100's  $\mu$ s and magnitudes of 100's mV are expected on the power supply line a RC low pass filter network as shown in Figure 7 is recommended for additional bypassing. If no such bypass network is used power supply transients can cause the internal voltage reference of the comparator to temporarily shift potentially resulting in a brief incorrect comparator output. For example if an RC network with  $100\Omega$  resistance and  $10\mu$ F capacitance (1.1ms rise time) is used the voltage reference will shift temporarily the amount,  $V_{TH}$  Power Supply Sensitivity ( $V_{TH}$ PSS), specified in the Electrical Characteristics table.

FIGURE 7. Power Supply Bypassing

#### **POWER SUPPLY SUPERVISION**

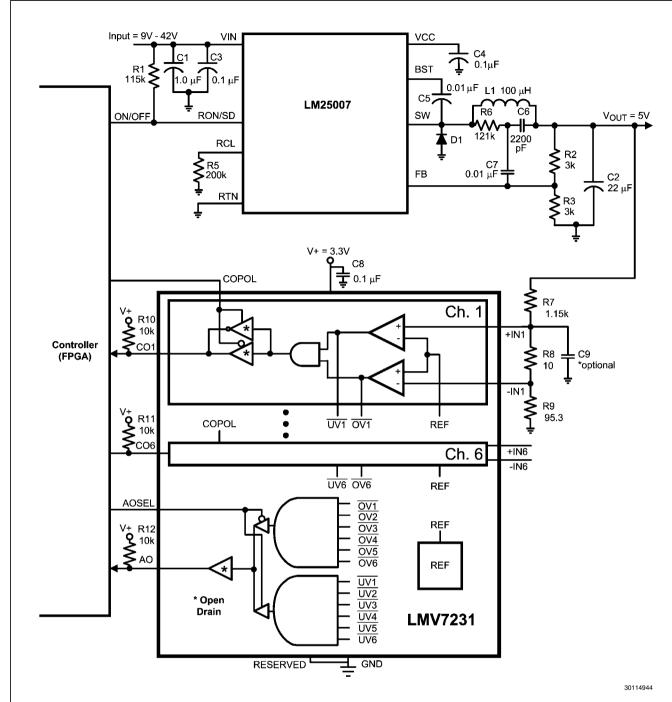

Figure 8 shows a power supply supervision circuit utilizing the LMV7231. This application uses the efficient, easy to use LM25007 step-down switching regulator. This switching regulator can handle a 9V - 42V input voltage range and it's regulated output voltage is set to 5V with R2 = R3 = 3k $\Omega$ .

$$V_{OUT} = 2.5 \times (R2 + R3)/R3$$

= 2.5 \times (3k + 3k)/3k = 5V

Resistor R6 and capacitors C6, C7 are utilized to minimize output ripple voltage per the LM25007 evaluation board application note.

The comparator voltage window is set to 5V +/- 5% by R7=1.15k $\Omega$ , R8=10 $\Omega$ , R9=95.3 $\Omega$ . See 3 RESISTOR VOLTAGE DIVIDER SELECTION section in the Application Information section of the datasheet for details on how to set the comparator voltage window.

With components selected the output ripple voltage seen on the LM25007 is approximately 30 - 35mV and is reduced to about 4mV at the comparator input, +IN1, by the resistor divider. This ripple voltage can be reduced multiple ways. First, user can operate the device in continuous conduction mode rather than discontinuous conduction mode. To do this increase the load current of the device (see LM25007 datasheet for more details). However, make sure not to exceed the power rating of the resistors in the resistor ladder. Second, ripple can be reduced further with a bypass cap, C9, at the resistor divider. If desired a user can select a 1uF capacitor to achieve less than 3mV ripple at +IN1. However, there is a tradeoff and adding capacitance at this node will lower the system response time.

FIGURE 8. Power Supply Supervision

# Physical Dimensions inches (millimeters) unless otherwise noted

# For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2010 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com