RM42L432

#### SPNS180B - SEPTEMBER 2012-REVISED JUNE 2015

# RM42L432 16- and 32-Bit RISC Flash Microcontroller

#### 1 Device Overview

#### 1.1 Features

- High-Performance Microcontroller for Safety-Critical Applications

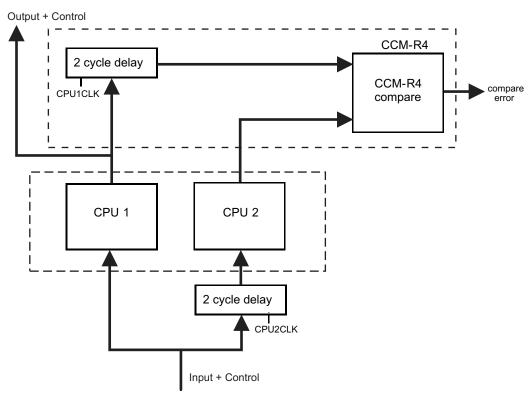

- Dual CPUs Running in Lockstep

- ECC on Flash and RAM Interfaces

- Built-In Self-Test for CPU and On-Chip RAMs

- Error Signaling Module With Error Pin

- Voltage and Clock Monitoring

- ARM<sup>®</sup> Cortex<sup>®</sup>-R4 32-Bit RISC CPU

- Efficient 1.66 DMIPS/MHz With 8-Stage Pipeline

- 8-Region Memory Protection Unit (MPU)

- Open Architecture With Third-Party Support

- Operating Conditions

- 100-MHz System Clock

- Core Supply Voltage (V<sub>CC</sub>): 1.2-V Nominal

- I/O Supply Voltage (V<sub>CCIO</sub>): 3.3-V Nominal

- ADC Supply Voltage (V<sub>CCAD</sub>): 3.3-V Nominal

- Integrated Memory

- 384KB of Program Flash With ECC

- 32KB of RAM With ECC

- 16KB of Flash for Emulated EEPROM With ECC

- Hercules<sup>™</sup> Common Platform Architecture

- Consistent Memory Map Across Family

- Real-Time Interrupt (RTI) Timer (OS Timer)

- 96-Channel Vectored Interrupt Module (VIM)

- 2-Channel Cyclic Redundancy Checker (CRC)

- Frequency-Modulated Phase-Locked Loop (FMPLL) With Built-In Slip Detector

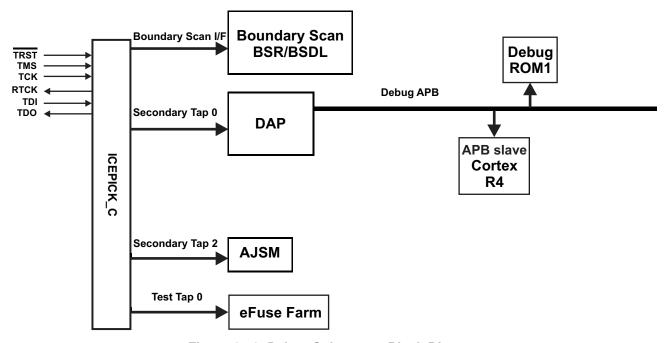

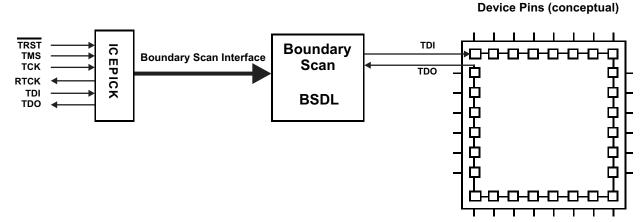

- IEEE 1149.1 JTAG Boundary Scan and ARM CoreSight™ Components

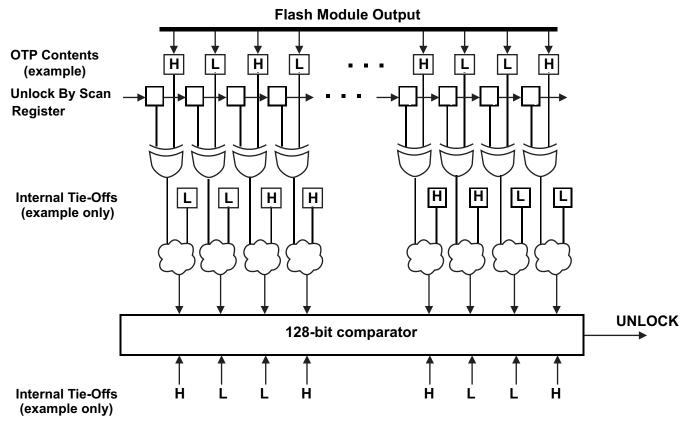

- Advanced JTAG Security Module (AJSM)

- · Multiple Communication Interfaces

- Two CAN Controllers (DCANs)

- DCAN1 32 Mailboxes With Parity Protection

- DCAN2 16 Mailboxes With Parity Protection

- Compliant to CAN Protocol Version 2.0B

- Multibuffered Serial Peripheral Interface (MibSPI) Module

- 128 Words With Parity Protection

- Two Standard Serial Peripheral Interface (SPI) Modules

- UART (SCI) Interface With Local Interconnect Network (LIN 2.1) Interface Support

- · Next Generation High-End Timer (N2HET) Module

- Up to 19 Programmable Pins

- 128-Word Instruction RAM With Parity Protection

- Includes Hardware Angle Generator

- Dedicated High-End Timer Transfer Unit (HTU)

With MPU

- Enhanced Quadrature Encoder Pulse (eQEP) Module

- Motor Position Encoder Interface

- 12-Bit Multibuffered Analog-to-Digital Converter (ADC) Module

- 16 Channels

- 64 Result Buffers With Parity Protection

- Up to 45 General-Purpose Input/Output (GPIO) Pins

- 8 Dedicated Interrupt-Capable GPIO Pins

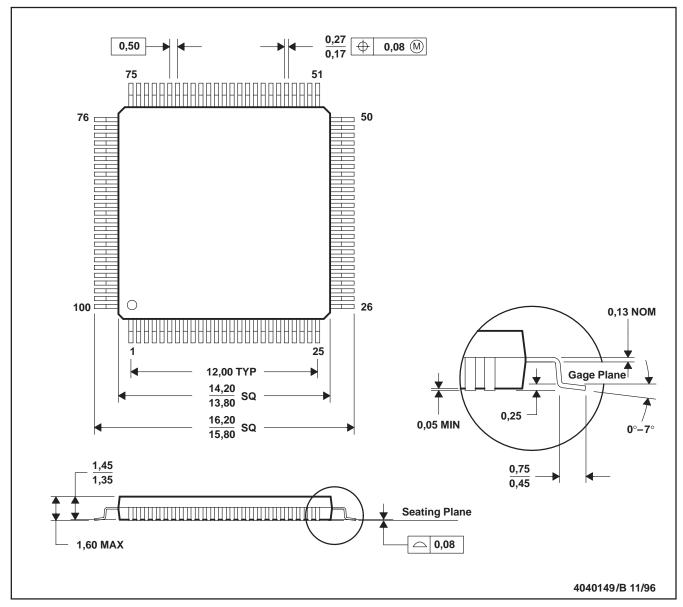

- Package

- 100-Pin Quad Flatpack (PZ) [Green]

## 1.2 Applications

- Industrial Safety Applications

- Industrial Automation

- Safe Programmable Logic Controllers (PLCs)

- Power Generation and Distribution

- Turbines and Windmills

- Elevators and Escalators

- Medical Applications

- Ventilators

- Defibrillators

- Infusion and Insulin Pumps

- Radiation Therapy

- Robotic Surgery

#### 1.3 Description

The RM42L432 device is a high-performance microcontroller for safety systems. The safety architecture includes dual CPUs in lockstep, CPU and Memory BIST logic, ECC on both the flash and the data SRAM, parity on peripheral memories, and loopback capability on peripheral I/Os.

The RM42L432 device integrates the ARM Cortex-R4 CPU. The CPU offers an efficient 1.66 DMIPS/MHz, and has configurations that can run up to 100 MHz, providing up to 166 DMIPS. The device operates in little-endian (LE) mode.

The RM42L432 device has 384KB of integrated flash and 32KB of data RAM. Both the flash and RAM have single-bit error correction and double-bit error detection. The flash memory on this device is a nonvolatile, electrically erasable, and programmable memory implemented with a 64-bit-wide data bus interface. The flash operates on a 3.3-V supply input (the same level as I/O supply) for all read, program, and erase operations. When in pipeline mode, the flash operates with a system clock frequency of up to 100 MHz. The SRAM supports single-cycle read and write accesses in byte, halfword, word, and double-word modes throughout the supported frequency range.

The RM42L432 device features peripherals for real-time control-based applications, including a Next Generation High-End Timer (N2HET) timing coprocessor with up to 19 I/O terminals and a 12-bit Analog-to-Digital Converter (ADC) supporting 16 inputs in the 100-pin package.

The N2HET is an advanced intelligent timer that provides sophisticated timing functions for real-time applications. The timer is software-controlled, using a small instruction set, with a specialized timer micromachine and an attached I/O port. The N2HET can be used for pulse-width-modulated outputs, capture or compare inputs, or GPIO. The N2HET is especially well suited for applications requiring multiple sensor information and drive actuators with complex and accurate time pulses. A High-End Timer Transfer Unit (HTU) can perform DMA-type transactions to transfer N2HET data to or from main memory. A Memory Protection Unit (MPU) is built into the HTU.

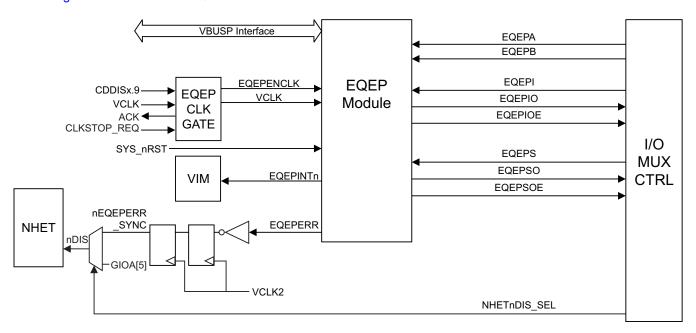

The Enhanced Quadrature Encoder Pulse (eQEP) module is used for direct interface with a linear or rotary incremental encoder to get position, direction, and speed information from a rotating machine as used in high-performance motion and position-control systems.

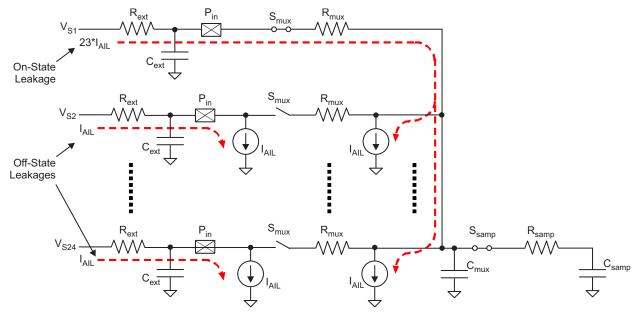

The device has a 12-bit-resolution MibADC with 16 channels and 64 words of parity-protected buffer RAM. The MibADC channels can be converted individually or can be grouped by software for sequential conversion sequences. There are three separate groupings. Each sequence can be converted once when triggered or configured for continuous conversion mode. The MibADC has a 10-bit mode for use when compatibility with older devices or faster conversion time is desired.

The device has multiple communication interfaces: one MibSPI, two SPIs, one UART/LIN, and two DCANs. The SPI provides a convenient method of serial high-speed communications between similar shift-register type devices. The UART/LIN supports the Local Interconnect standard 2.1 and can be used as a UART in full-duplex mode using the standard Non-Return-to-Zero (NRZ) format. The DCAN supports the CAN 2.0 (A and B) protocol standard and uses a serial, multimaster communication protocol that efficiently supports distributed real-time control with robust communication rates of up to 1 Mbps. The DCAN is ideal for applications operating in noisy and harsh environments (for example, automotive and industrial applications) that require reliable serial communication or multiplexed wiring.

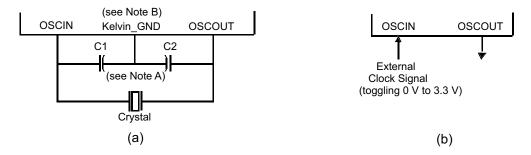

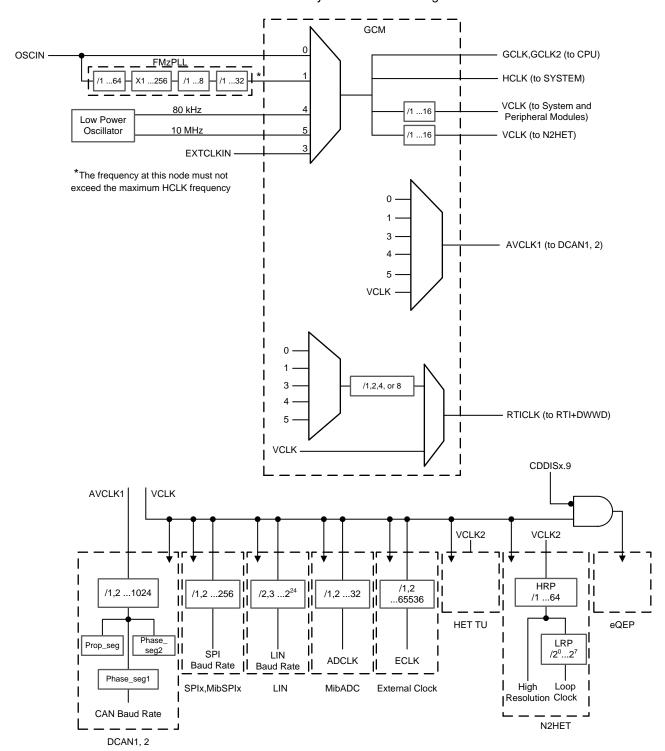

The Frequency-Modulated Phase-Locked Loop (FMPLL) clock module is used to multiply the external frequency reference to a higher frequency for internal use. The FMPLL provides one of the five possible clock source inputs to the Global Clock Module (GCM). The GCM manages the mapping between the available clock sources and the device clock domains.

The device also has an External Clock Prescaler (ECP) module that when enabled, outputs a continuous external clock on the ECLK pin. The ECLK frequency is a user-programmable ratio of the peripheral interface clock (VCLK) frequency. This low-frequency output can be monitored externally as an indicator of the device operating frequency.

www.ti.com

The Error Signaling Module (ESM) monitors all device errors and determines whether an interrupt is generated or the external nERROR pin is toggled when a fault is detected. The nERROR pin can be monitored externally as an indicator of a fault condition in the microcontroller.

The I/O Multiplexing and Control Module (IOMM) allows the configuration of the input/output pins to support alternate functions. See Table 4-17 for a list of the pins that support multiple functions on this device.

With integrated safety features and a wide choice of communication and control peripherals, the RM42L432 device is an ideal solution for real-time control applications with safety-critical requirements.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE           |

|-------------|------------|---------------------|

| RM42L432PZ  | LQFP (100) | 14.00 mm × 14.00 mm |

(1) For more information, see Section 9, Mechanical Packaging and Orderable Information.

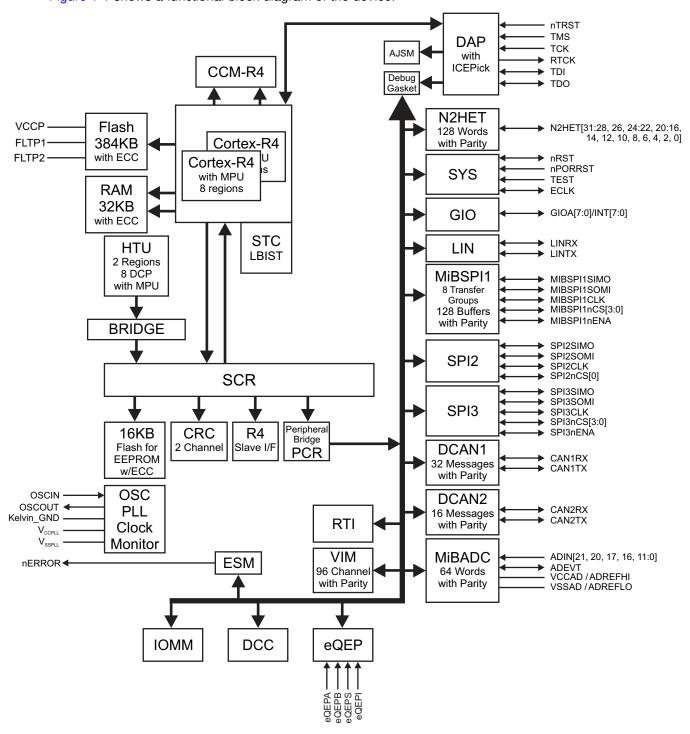

#### 1.4 Functional Block Diagram

Figure 1-1 shows a functional block diagram of the device.

Figure 1-1. Functional Block Diagram

# **Table of Contents**

| 1 | Devi | ce Overview                                | <u>1</u> |   | 6.9  | Flash Memory                                         | 49         |

|---|------|--------------------------------------------|----------|---|------|------------------------------------------------------|------------|

|   | 1.1  | Features                                   | . 1      |   | 6.10 | Flash Program and Erase Timings for Program          |            |

|   | 1.2  | Applications                               | . 2      |   |      | Flash                                                | 51         |

|   | 1.3  | Description                                | . 3      |   | 6.11 | Flash Program and Erase Timings for Data Flash       | <u>51</u>  |

|   | 1.4  | Functional Block Diagram                   | _        |   | 6.12 | Tightly Coupled RAM Interface Module                 | <u>52</u>  |

| 2 | Revi | sion History                               | _        |   | 6.13 | Parity Protection for Accesses to peripheral RAMs.   | <u>52</u>  |

| 3 |      | ce Comparison                              | _        |   | 6.14 | On-Chip SRAM Initialization and Testing              | <u>53</u>  |

| 4 |      | ninal Configuration and Functions          | _        |   | 6.15 | Vectored Interrupt Manager                           | <u>55</u>  |

|   | 4.1  | PZ QFP Package Pinout (100-Pin)            | _        |   | 6.16 | Real-Time Interrupt Module                           | <u>57</u>  |

|   | 4.2  | Terminal Functions                         |          |   | 6.17 | Error Signaling Module                               | <u>58</u>  |

|   | 4.3  | Output Multiplexing and Control            | 16       |   | 6.18 | Reset / Abort / Error Sources                        | 62         |

|   | 4.4  | Special Multiplexed Options                |          |   | 6.19 | Digital Windowed Watchdog                            | 63         |

| 5 |      | cifications                                | _        |   | 6.20 | Debug Subsystem                                      | 64         |

| _ | 5.1  | Absolute Maximum Ratings                   |          | 7 |      | pheral Information and Electrical                    |            |

|   | 5.2  | ESD Ratings                                |          |   | Spec | cifications                                          | <u>69</u>  |

|   | 5.3  | Power-On Hours (POH)                       |          |   | 7.1  | Peripheral Legend                                    | <u>69</u>  |

|   | 5.4  | Recommended Operating Conditions           |          |   | 7.2  | Multibuffered 12-Bit Analog-to-Digital Converter     | 69         |

|   | 5.5  | Switching Characteristics Over Recommended | <u></u>  |   | 7.3  | General-Purpose Input/Output                         | 77         |

|   | 0.0  | Operating Conditions for Clock Domains     | 19       |   | 7.4  | Enhanced High-End Timer (N2HET)                      | 78         |

|   | 5.6  | Wait States Required                       | 20       |   | 7.5  | Controller Area Network (DCAN)                       | 81         |

|   | 5.7  | Power Consumption                          | 21       |   | 7.6  | Local Interconnect Network Interface (LIN)           | 82         |

|   | 5.8  | Thermal Resistance Characteristics for PZ  | _        |   | 7.7  | Multibuffered / Standard Serial Peripheral Interface | 83         |

|   | 5.9  | Input/Output Electrical Characteristics    |          |   | 7.8  | Enhanced Quadrature Encoder (eQEP)                   | 93         |

|   | 5.10 | Output Buffer Drive Strengths              |          | 8 | Devi | ce and Documentation Support                         | 95         |

|   | 5.11 | Input Timings                              | _        |   | 8.1  | Device Support                                       | 95         |

|   | 5.12 | Output Timings                             |          |   | 8.2  | Documentation Support                                | 97         |

| 6 | Svst | em Information and Electrical              |          |   | 8.3  | Community Resources                                  | 97         |

|   |      | cifications                                | 27       |   | 8.4  | Trademarks                                           | 97         |

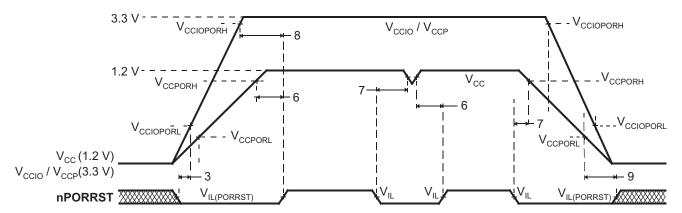

|   | 6.1  | Voltage Monitor Characteristics            | 27       |   | 8.5  | Electrostatic Discharge Caution                      | 97         |

|   | 6.2  | Power Sequencing and Power-On Reset        | 28       |   | 8.6  | Glossary                                             | 97         |

|   | 6.3  | Warm Reset (nRST)                          | 30       |   | 8.7  | Device Identification Code Register                  | 97         |

|   | 6.4  | ARM Cortex-R4 CPU Information              |          |   | 8.8  | Die Identification Registers                         |            |

|   | 6.5  | Clocks                                     | 35       |   | 8.9  | Module Certifications                                |            |

|   | 6.6  | Clock Monitoring                           | 41       | 9 | Mech | hanical Packaging and Orderable                      |            |

|   | 6.7  | Glitch Filters                             | 43       |   |      | endum                                                | <u>104</u> |

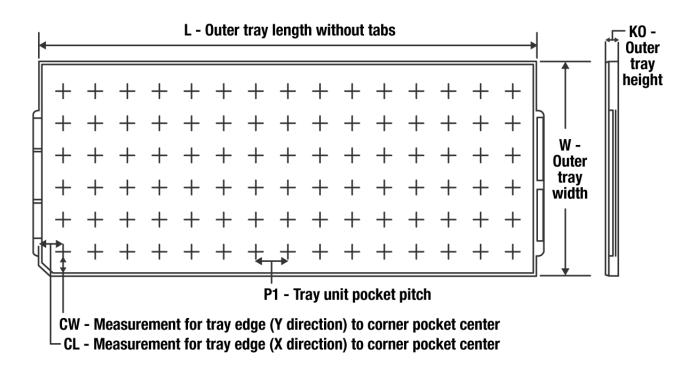

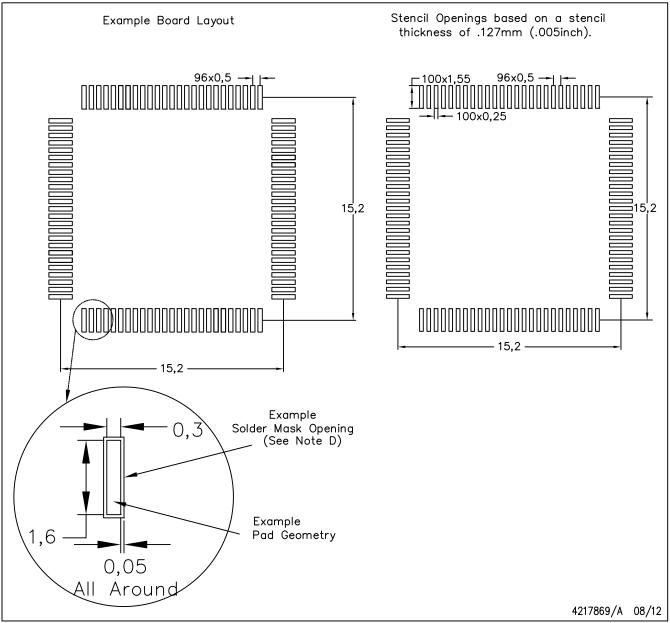

|   | 6.8  | Device Memory Map                          | 44       |   | 9.1  | Packaging Information                                | 104        |

# 2 Revision History

This data manual revision history highlights the technical changes made to the SPNS180A device-specific data manual to make it an SPNS180B revision.

**Scope:** Applicable updates to the Hercules™ MCU device family, specifically relating to the RM42L432 devices, which are now in the production data (PD) stage of development have been incorporated.

| Chan | ges from October 30, 2013 to June 30, 2015 (from A Revision (October 2013) to B Revision)                    | Page      |

|------|--------------------------------------------------------------------------------------------------------------|-----------|

| •    | Updated/Changed section title to "Device Overview"                                                           | 1         |

| •    | Added Section 1.3 (Description): Added paragraph describing IOMM                                             |           |

| •    | Section 1.3 (Description): Added the Device Information table                                                |           |

| •    | Added Section 3, Device Comparison                                                                           | {         |

| •    | Section 5 (Specifications): Updated/Changed section title                                                    | 18        |

| •    | Section 5.1 (Absolute Maximum Ratings): Added Latch-up Performance Specification                             |           |

| •    | Section 5.2 (ESD Ratings): Added section                                                                     |           |

| •    | Section 5.3 (Power-On Hours (POH)): Added table (new)                                                        | 18        |

| •    | Table 5-3 (Output Buffer Drive Strengths): Added the "SPI3nCS[0]" signal to the 2 mA zero-dominant signals   |           |

|      | row                                                                                                          | 23        |

| •    | Table 5-4 (Selectable 8mA/2mA Control): Clarified impact of SPI2PC9 register on drive strength of SPI2SOMI   |           |

|      | pin in footnote                                                                                              | 23        |

| •    | Section 6.4.1 (Summary of ARM Cortex-R4 CPU Features): Added Quantity of Breakpoints and Watchpoints         |           |

| •    | Section 6.20.3 (JTAG Identification Code): Added a table showing JTAG ID code for each silicon revision      |           |

| •    | Table 7-7 (MibADC Operating Characteristics ): Added missing footnote for Z <sub>SET</sub> 10-/12-bit modes  |           |

| •    | Section 7.7.1 (Features [MibSPI]): Updated/Changed size of SPI baud clock generator from "8-bit" to "11-bit" |           |

| •    | Section 8 (Device and Documentation Support): Updated/Changed section outline structure                      |           |

| •    | Section 8.1 (Device Support): Added section (new)                                                            | 95        |

| •    | Section 8.1.1 (Development Support, Hardware Development Tools): Updated/Changed the JTAG-based              |           |

|      | emulators specified                                                                                          | 95        |

| •    | Section 8.1.2 (Device Nomenclature): Updated/Changed section title                                           |           |

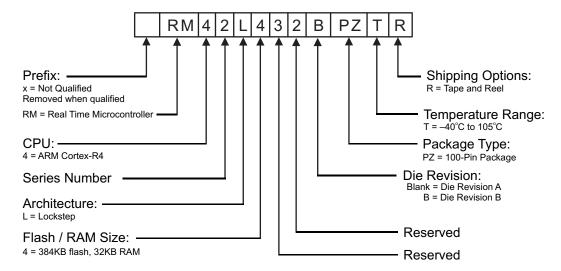

| •    | Figure 8-1 (Device Numbering Conventions): Updated/Change figure to include "Die Revision"                   |           |

| •    | Section 8.7 (Device Identification Code Register): Added silicon revision B device identification code       | 97        |

| •    | Section 8.8 (Die Identification Registers): Updated/Changed the DIEIDL and DIEIDH to point to the original   |           |

|      | registers at location 0xFFFFFF7C and 0xFFFFFF80                                                              | <u>98</u> |

# 3 Device Comparison

Table 3-1 lists the features of the RM42L432 devices.

## Table 3-1. RM42L432 Device Comparison<sup>(1)(2)</sup>

| FEATURES                    |                                 |                                 |                                |                               |                                |                               |                               |                               |  |  |  |

|-----------------------------|---------------------------------|---------------------------------|--------------------------------|-------------------------------|--------------------------------|-------------------------------|-------------------------------|-------------------------------|--|--|--|

| Generic Part<br>Number      | RM46L852ZWT (3)                 | RM44L922ZWT                     | RM44L920PGE                    | RM44L920PZ                    | RM44L520PGE                    | RM44L520PZ                    | RM42L432PZ (3)                | RM41L232PZ                    |  |  |  |

| Package                     | 337 BGA                         | 337 BGA                         | 144 QFP                        | 100 QFP                       | 144 QFP                        | 100 QFP                       | 100 QFP                       | 100 QFP                       |  |  |  |

| CPU                         | ARM Cortex-R4F                  | ARM Cortex-R4F                  | ARM Cortex-R4F                 | ARM Cortex-R4F                | ARM Cortex-R4F                 | ARM Cortex-R4F                | ARM Cortex-R4                 | ARM Cortex-R4                 |  |  |  |

| Frequency (MHz)             | 220                             | 220                             | 200                            | 120                           | 200                            | 120                           | 100                           | 80                            |  |  |  |

| Flash (KB)                  | 1280                            | 1024                            | 1024                           | 1024                          | 768                            | 768                           | 384                           | 128                           |  |  |  |

| RAM (KB)                    | 192                             | 128                             | 128                            | 128                           | 128                            | 128                           | 32                            | 32                            |  |  |  |

| Data Flash<br>[EEPROM] (KB) | 64                              | 64                              | 64                             | 64                            | 64                             | 64                            | 16                            | 16                            |  |  |  |

| USB OHCI +<br>Device        | 2+0 or 1+1                      | -                               | -                              | -                             | -                              | -                             | -                             | -                             |  |  |  |

| EMAC                        | 10/100                          | -                               | -                              | -                             | -                              | _                             | -                             | -                             |  |  |  |

| CAN                         | 3                               | 3                               | 3                              | 2                             | 3                              | 2                             | 2                             | 2                             |  |  |  |

| MibADC<br>12-bit (Ch)       | 2 (24ch)                        | 2 (24ch)                        | 2 (24ch)                       | 2 (24ch)                      | 2 (24ch)                       | 2 (16ch)                      | 1 (16ch)                      | 1 (16ch)                      |  |  |  |

| N2HET (Ch)                  | 2 (44)                          | 2 (44)                          | 2 (40)                         | 2 (21)                        | 2 (40)                         | 2 (21)                        | 1 (19)                        | 1 (19)                        |  |  |  |

| ePWM Channels               | 14                              | 14                              | 14                             | 8                             | 14                             | 8                             | -                             | -                             |  |  |  |

| eCAP Channels               | 6                               | 6                               | 6                              | 4                             | 6                              | 4                             | -                             | _                             |  |  |  |

| eQEP Channels               | 2                               | 2                               | 2                              | 1                             | 2                              | 1                             | 1                             | 1                             |  |  |  |

| MibSPI (CS)                 | 3 (6 + 6 + 4)                   | 3 (6 + 6 + 4)                   | 3 (5 + 6 + 1)                  | 2 (4 + 2)                     | 3 (5 + 6 + 1)                  | 2 (4 + 2)                     | 1 (4)                         | 1 (4)                         |  |  |  |

| SPI (CS)                    | 2 (2 + 1)                       | 2 (2 + 1)                       | 1 (1)                          | 1 (1)                         | 1 (1)                          | 1 (1)                         | 2 (4 + 4)                     | 2 (4 + 4)                     |  |  |  |

| SCI (LIN)                   | 2 (1 with LIN)                  | 2 (1 with LIN)                  | 2 (1 with LIN)                 | 1(with LIN)                   | 2 (1 with LIN)                 | 1(with LIN)                   | 1(with LIN)                   | 1(with LIN)                   |  |  |  |

| 12C                         | 1                               | 1                               | 1                              | -                             | 1                              | -                             | -                             | _                             |  |  |  |

| GPIO (INT) <sup>(4)</sup>   | 101 (with 16 interrupt capable) | 101 (with 16 interrupt capable) | 64 (with 16 interrupt capable) | 45 (with 9 interrupt capable) | 64 (with 10 interrupt capable) | 45 (with 9 interrupt capable) | 45 (with 8 interrupt capable) | 45 (with 8 interrupt capable) |  |  |  |

| EMIF                        | 16-bit data                     | _                               | _                              | _                             | _                              | _                             | _                             | _                             |  |  |  |

| ETM [Trace]<br>(Data)       | -                               | -                               | -                              | -                             | -                              | -                             | -                             | -                             |  |  |  |

| RTP/DMM (Data)              | _                               | _                               | _                              | _                             | _                              | _                             | _                             | _                             |  |  |  |

| Operating<br>Temperature    | -40°C to 105°C                  | -40°C to 105°C                  | -40°C to 105°C                 | -40°C to 105°C                | -40°C to 105°C                 | -40°C to 105°C                | -40°C to 105°C                | -40°C to 105°C                |  |  |  |

| Core Supply (V)             | 1.14 V – 1.32 V                 | 1.14 V – 1.32 V                 | 1.14 V – 1.32 V                | 1.14 V – 1.32 V               | 1.14 V – 1.32 V                | 1.14 V – 1.32 V               | 1.14 V – 1.32 V               | 1.14 V – 1.32 V               |  |  |  |

| I/O Supply (V)              | 3.0 V – 3.6 V                   | 3.0 V – 3.6 V                   | 3.0 V – 3.6 V                  | 3.0 V – 3.6 V                 | 3.0 V – 3.6 V                  | 3.0 V – 3.6 V                 | 3.0 V – 3.6 V                 | 3.0 V – 3.6 V                 |  |  |  |

<sup>(1)</sup> For additional device variants, see www.ti.com/rm

<sup>(2)</sup> This table reflects the maximum configuration for each peripheral. Some functions are multiplexed and not all pins are available at the same time.

<sup>(3)</sup> Superset device

<sup>(4)</sup> Total number of pins that can be used as general-purpose input or output when not used as part of a peripheral.

## 4 Terminal Configuration and Functions

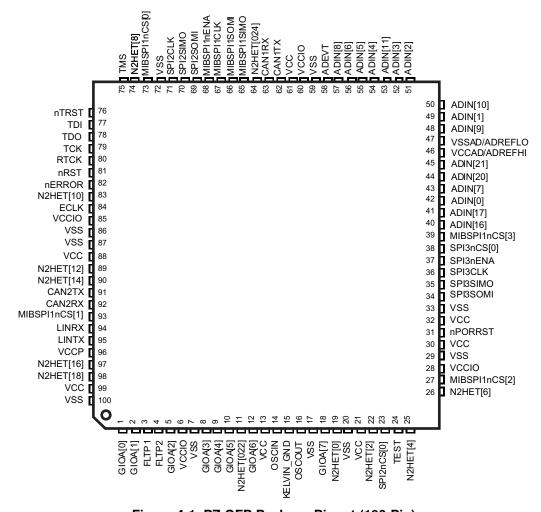

## 4.1 PZ QFP Package Pinout (100-Pin)

Figure 4-1 shows the 100-pin PZ QFP package pinout.

Figure 4-1. PZ QFP Package Pinout (100-Pin)

Note: Pins can have multiplexed functions. Only the default function is depicted in Figure 4-1.

#### 4.2 Terminal Functions

Table 4-1 through Table 4-16 identify the external signal names, the associated pin numbers along with the mechanical package designator, the pin type (Input, Output, I/O, Power, or Ground), whether the pin has any internal pullup/pulldown, whether the pin can be configured as a GPIO, and a functional pin description.

#### NOTE

In the Terminal Functions table below, the "Reset Pull State" is the state of the pull applied to the terminal while nPORRST is low and immediately after nPORRST goes High. The default pull direction may change when software configures the pin for an alternate function. The "Pull Type" is the type of pull asserted when the signal name in bold is enabled for the given terminal by the IOMM control registers.

All I/O signals except nRST are configured as inputs while nPORRST is low and immediately after nPORRST goes High. While nPORRST is low, the input buffers are disabled, and the output buffers are disabled with the default pulls enabled.

All output-only signals have the output buffer disabled and the default pull enabled while nPORRST is low, and are configured as outputs with the pulls disabled immediately after nPORRST goes High.

## 4.2.1 High-End Timer (N2HET)

Table 4-1. High-End Timer (N2HET)

| TERMINAL                                       |           | SIGNAL RESET | PULL TYPE     | DESCRIPTION   |                                                                                      |

|------------------------------------------------|-----------|--------------|---------------|---------------|--------------------------------------------------------------------------------------|

| SIGNAL NAME                                    | 100<br>PZ | TYPE         | PULL<br>STATE |               |                                                                                      |

| N2HET[0]                                       | 19        | I/O          | Pulldown      | Programmable, | Timer input capture or output compare. The                                           |

| N2HET[2]                                       | 22        |              |               | 20 μΑ         | N2HET applicable terminals can be programmed as general-purpose input/output (GPIO). |

| N2HET[4]                                       | 25        |              |               |               | Each terminal has a suppression filter with a                                        |

| N2HET[6]                                       | 26        |              |               |               | programmable duration.                                                               |

| N2HET[8]                                       | 74        |              |               |               |                                                                                      |

| N2HET[10]                                      | 83        |              |               |               |                                                                                      |

| N2HET[12]                                      | 89        |              |               |               |                                                                                      |

| N2HET[14]                                      | 90        |              |               |               |                                                                                      |

| N2HET[16]                                      | 97        |              |               |               |                                                                                      |

| MIBSPI1nCS[1]/EQEPS/<br>N2HET[17]              | 93        |              |               |               |                                                                                      |

| N2HET[18]                                      | 98        |              |               |               |                                                                                      |

| MIBSPI1nCS[2]/N2HET[20]/<br>N2HET[19]          | 27        |              |               |               |                                                                                      |

| MIBSPI1nCS[2]/ <b>N2HET[20]</b> /<br>N2HET[19] | 27        |              |               |               |                                                                                      |

| N2HET[22]                                      | 11        |              |               |               |                                                                                      |

| N2HET[24]                                      | 64        |              |               |               |                                                                                      |

| MIBSPI1nCS[3]/N2HET[26]                        | 39        |              |               |               |                                                                                      |

| ADEVT/N2HET[28]                                | 58        |              |               |               |                                                                                      |

| GIOA[7]/ <b>N2HET[29]</b>                      | 18        |              |               |               |                                                                                      |

| MIBSPI1nENA/N2HET[23]/<br>N2HET[30]            | 68        |              |               |               |                                                                                      |

| GIOA[6]/SPI2nCS[1]/ <b>N2HET[31]</b>           | 12        |              |               |               |                                                                                      |

## 4.2.2 Enhanced Quadrature Encoder Pulse Modules (eQEP)

Table 4-2. Enhanced Quadrature Encoder Pulse Modules (eQEP)

| TERMINAL                                |           | SIGNAL | RESET PULL TYPE |             | DESCRIPTION          |   |                      |  |  |  |  |  |

|-----------------------------------------|-----------|--------|-----------------|-------------|----------------------|---|----------------------|--|--|--|--|--|

| SIGNAL NAME                             | 100<br>PZ | TYPE   | PULL<br>STATE   |             |                      |   |                      |  |  |  |  |  |

| SPI3CLK/ <b>EQEPA</b>                   | 36        | Input  | Pullup          | Fixed 20 μA | Enhanced QEP Input A |   |                      |  |  |  |  |  |

| SPI3nENA/ <b>EQEPB</b>                  | 37        | Input  |                 |             |                      | ! | Enhanced QEP Input B |  |  |  |  |  |

| SPI3nCS[0]/ <b>EQEPI</b>                | 38        | I/O    |                 |             |                      |   |                      |  |  |  |  |  |

| MIBSPI1nCS[1]/ <b>EQEPS</b> /N2HET [17] | 93        | I/O    |                 |             | Enhanced QEP Strobe  |   |                      |  |  |  |  |  |

## 4.2.3 General-Purpose Input/Output (GPIO)

Table 4-3. General-Purpose Input/Output (GPIO)

| TERMINAL                     |           | SIGNAL | RESET         | PULL TYPE     | DESCRIPTION                                                                         |

|------------------------------|-----------|--------|---------------|---------------|-------------------------------------------------------------------------------------|

| SIGNAL NAME                  | 100<br>PZ | TYPE   | PULL<br>STATE |               |                                                                                     |

| GIOA[0]/SPI3nCS[3]           | 1         | I/O    | Pulldown      | Programmable, | General-purpose input/output                                                        |

| GIOA[1]/SPI3nCS[2]           | 2         |        |               |               | All GPIO terminals can generate interrupts to the CPU on rising/falling/both edges. |

| GIOA[2]/SPI3nCS[1]           | 5         |        |               |               |                                                                                     |

| GIOA[3]/SPI2nCS[3]           | 8         |        |               |               |                                                                                     |

| GIOA[4]/SPI2nCS[2]           | 9         |        |               |               |                                                                                     |

| GIOA[5]/EXTCLKIN             | 10        |        |               |               |                                                                                     |

| GIOA[6]/SPI2nCS[1]/N2HET[31] | 12        |        |               |               |                                                                                     |

| GIOA[7]/N2HET[29]            | 18        |        |               |               |                                                                                     |

## 4.2.4 Controller Area Network Interface Modules (DCAN1, DCAN2)

Table 4-4. Controller Area Network Interface Modules (DCAN1, DCAN2)

| TERMINAL    |           | SIGNAL |               |                        | DESCRIPTION                                  |                        |

|-------------|-----------|--------|---------------|------------------------|----------------------------------------------|------------------------|

| SIGNAL NAME | 100<br>PZ | TYPE   | PULL<br>STATE |                        |                                              |                        |

| CAN1RX      | 63        | I/O    | Pullup        | Programmable,<br>20 μΑ | CAN1 Receive, or general-purpose I/O (GPIO)  |                        |

| CAN1TX      | 62        |        |               |                        | CAN1 Transmit, or GPIO CAN2 Receive, or GPIO | CAN1 Transmit, or GPIO |

| CAN2RX      | 92        |        |               |                        |                                              | CAN2 Receive, or GPIO  |

| CAN2TX      | 91        |        |               |                        | CAN2 Transmit, or GPIO                       |                        |

## 4.2.5 Multibuffered Serial Peripheral Interface (MibSPI1)

Table 4-5. Multibuffered Serial Peripheral Interface (MibSPI1)

| TERMINAL                                      |           | SIGNAL | RESET         | PULL TYPE     | DESCRIPTION                          |

|-----------------------------------------------|-----------|--------|---------------|---------------|--------------------------------------|

| SIGNAL NAME                                   | 100<br>PZ | TYPE   | PULL<br>STATE |               |                                      |

| MIBSPI1CLK                                    | 67        | I/O    | Pullup        | Programmable, | MibSPI1 Serial Clock, or GPIO        |

| MIBSPI1nCS[0]                                 | 73        |        |               | 20 μΑ         | MibSPI1 Chip Select, or GPIO         |

| MIBSPI1nCS[1]/EQEPS/N2HET [17]                | 93        |        |               |               |                                      |

| <b>MIBSPI1nCS[2]</b> /N2HET[20]/N2<br>HET[19] | 27        |        |               |               |                                      |

| MIBSPI1nCS[3]/N2HET[26]                       | 39        |        |               |               |                                      |

| MIBSPI1nENA/N2HET[23]/N2H<br>ET[30]           | 68        |        |               |               | MibSPI1 Enable, or GPIO              |

| MIBSPI1SIMO                                   | 65        |        |               |               | MibSPI1 Slave-In-Master-Out, or GPIO |

| MIBSPI1SOMI                                   | 66        |        |               |               | MibSPI1 Slave-Out-Master-In, or GPIO |

## 4.2.6 Standard Serial Peripheral Interface (SPI2)

## Table 4-6. Standard Serial Peripheral Interface (SPI2)

| TERMINAL                              |           | SIGNAL | RESET         | PULL TYPE     | DESCRIPTION                       |  |

|---------------------------------------|-----------|--------|---------------|---------------|-----------------------------------|--|

| SIGNAL NAME                           | 100<br>PZ | TYPE   | PULL<br>STATE |               |                                   |  |

| SPI2CLK                               | 71        | I/O    | Pullup        | Programmable, | SPI2 Serial Clock, or GPIO        |  |

| SPI2nCS[0]                            | 23        |        | 20 μΑ         |               | SPI2 Chip Select, or GPIO         |  |

| GIOA[6]/ <b>SPI2nCS[1]</b> /N2HET[31] | 12        |        |               |               |                                   |  |

| GIOA[4]/ <b>SPI2nCS[2]</b>            | 9         |        |               |               |                                   |  |

| GIOA[3]/ <b>SPI2nCS[3]</b>            | 8         |        |               |               |                                   |  |

| SPI2SIMO                              | 70        |        |               |               | SPI2 Slave-In-Master-Out, or GPIO |  |

| SPI2SOMI                              | 69        |        |               |               | SPI2 Slave-Out-Master-In, or GPIO |  |

SRS = 0 for 8-mA drive (fast). This is the default mode as the SRS bits in the SPIPC9 register default to 0. SRS = 1 for 2-mA drive (slow)

| ,                  |    |     |        |               |                                   |

|--------------------|----|-----|--------|---------------|-----------------------------------|

| SPI3CLK/EQEPA      | 36 | I/O | Pullup | Programmable, | SPI3 Serial Clock, or GPIO        |

| SPI3nCS[0]/EQEPI   | 38 |     |        | 20 μΑ         | SPI3 Chip Select, or GPIO         |

| GIOA[2]/SPI3nCS[1] | 5  |     |        |               |                                   |

| GIOA[1]/SPI3nCS[2] | 2  |     |        |               |                                   |

| GIOA[0]/SPI3nCS[3] | 1  |     |        |               |                                   |

| SPI3nENA/EQEPB     | 37 |     |        |               | SPI3 Enable, or GPIO              |

| SPI3SIMO           | 35 |     |        |               | SPI3 Slave-In-Master-Out, or GPIO |

| SPI3SOMI           | 34 |     |        |               | SPI3 Slave-Out-Master-In, or GPIO |

## 4.2.7 Local Interconnect Network Controller (LIN)

**Table 4-7. Local Interconnect Network Controller (LIN)**

| TERMINAL    |           | SIGNAL | RESET         | PULL TYPE     | DESCRIPTION           |

|-------------|-----------|--------|---------------|---------------|-----------------------|

| SIGNAL NAME | 100<br>PZ | TYPE   | PULL<br>STATE |               |                       |

| LINRX       | 94        | I/O    | Pullup        | Programmable, | LIN Receive, or GPIO  |

| LINTX       | 95        |        |               | 20 114        | LIN Transmit, or GPIO |

# 4.2.8 Multibuffered Analog-to-Digital Converter (MibADC)

Table 4-8. Multibuffered Analog-to-Digital Converter (MibADC)

| TERMINAL        |           | SIGNAL TYPE  | RESET         | PULL TYPE              | DESCRIPTION                                   |

|-----------------|-----------|--------------|---------------|------------------------|-----------------------------------------------|

| SIGNAL NAME     | 100<br>PZ |              | PULL<br>STATE |                        |                                               |

| ADEVT/N2HET[28] | 58        | I/O          | Pullup        | Programmable,<br>20 μA | ADC event trigger or GPIO                     |

| ADIN[0]         | 42        | Input        | N/A           | None                   | Analog inputs                                 |

| ADIN[1]         | 49        |              |               |                        |                                               |

| ADIN[2]         | 51        |              |               |                        |                                               |

| ADIN[3]         | 52        |              |               |                        |                                               |

| ADIN[4]         | 54        |              |               |                        |                                               |

| ADIN[5]         | 55        |              |               |                        |                                               |

| ADIN[6]         | 56        |              |               |                        |                                               |

| ADIN[7]         | 43        |              |               |                        |                                               |

| ADIN[8]         | 57        |              |               |                        |                                               |

| ADIN[9]         | 48        |              |               |                        |                                               |

| ADIN[10]        | 50        |              |               |                        |                                               |

| ADIN[11]        | 53        |              |               |                        |                                               |

| ADIN[16]        | 40        |              |               |                        |                                               |

| ADIN[17]        | 41        |              |               |                        |                                               |

| ADIN[20]        | 44        |              |               |                        |                                               |

| ADIN[21]        | 45        |              |               |                        |                                               |

| VCCAD/ADREFHI   | 46        | Input/Power  | N/A           | None                   | ADC high reference level/ADC operating supply |

| VSSAD/ADREFLO   | 47        | Input/Ground | N/A           | None                   | ADC low reference level/ADC supply ground     |

# 4.2.9 System Module

Table 4-9. System Module

| TERMINAL         |           | SIGNAL | RESET         | PULL TYPE              | DESCRIPTION                                                                                                                                                                                                                                           |  |

|------------------|-----------|--------|---------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SIGNAL NAME      | 100<br>PZ | TYPE   | PULL<br>STATE |                        |                                                                                                                                                                                                                                                       |  |

| ECLK             | 84        | I/O    | Pulldown      | Programmable,<br>20 μA | External prescaled clock output, or GPIO.                                                                                                                                                                                                             |  |

| GIOA[5]/EXTCLKIN | 10        | Input  | Pulldown      | 20 μΑ                  | External Clock In                                                                                                                                                                                                                                     |  |

| nPORRST          | 31        | Input  | Pulldown      | 100 μΑ                 | Power-on reset, cold reset External power supply monitor circuitry must drive nPORRST low when any of the supplies to the microcontroller fall out of the specified range. This terminal has a glitch filter.                                         |  |

| nRST             | 81        | I/O    | Pullup        | 100 μΑ                 | The external circuitry can assert a system reset by driving nRST low. To ensure that an external reset is not arbitrarily generated, TI recommends that an external pullup resistor is connected to this terminal. This terminal has a glitch filter. |  |

Product Folder Links: RM42L432

## 4.2.10 Error Signaling Module (ESM)

## **Table 4-10. Error Signaling Module (ESM)**

| TERMINAL    |           | SIGNAL | RESET         | PULL TYPE | DESCRIPTION                                         |  |

|-------------|-----------|--------|---------------|-----------|-----------------------------------------------------|--|

| SIGNAL NAME | 100<br>PZ | TYPE   | PULL<br>STATE |           |                                                     |  |

| nERROR      | 82        | I/O    | Pulldown      | 20 μΑ     | ESM error signal. Indicates error of high severity. |  |

## 4.2.11 Main Oscillator

#### Table 4-11. Main Oscillator

| TERMINAL    |           | SIGNAL | RESET         | PULL TYPE | DESCRIPTION                                              |

|-------------|-----------|--------|---------------|-----------|----------------------------------------------------------|

| SIGNAL NAME | 100<br>PZ | TYPE   | PULL<br>STATE |           |                                                          |

| OSCIN       | 14        | Input  | N/A           | None      | From external crystal/resonator, or external clock input |

| OSCOUT      | 16        | Output | N/A           | None      | To external crystal/resonator                            |

| KELVIN_GND  | 15        | Input  | N/A           | None      | Dedicated ground for oscillator                          |

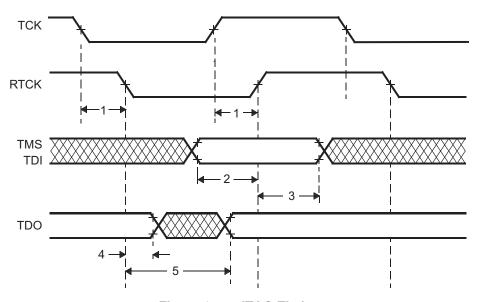

# 4.2.12 Test/Debug Interface

## Table 4-12. Test/Debug Interface

| TERMINAL    |           | SIGNAL | RESET                        | PULL TYPE     | DESCRIPTION                                                                                     |

|-------------|-----------|--------|------------------------------|---------------|-------------------------------------------------------------------------------------------------|

| SIGNAL NAME | 100<br>PZ | TYPE   | PULL<br>STATE                |               |                                                                                                 |

| nTRST       | 76        | Input  | Pulldown                     | Fixed, 100 μA | JTAG test hardware reset                                                                        |

| RTCK        | 80        | Output | N/A                          | None          | JTAG return test clock                                                                          |

| TCK         | 79        | Input  | Pulldown                     | Fixed, 100 μA | JTAG test clock                                                                                 |

| TDI         | 77        | I/O    | Pullup                       | Fixed, 100 μA | JTAG test data in                                                                               |

| TDO         | 78        | Output | Fixed,<br>100-μΑ<br>Pulldown | None          | JTAG test data out                                                                              |

| TMS         | 75        | I/O    | Pullup                       | Fixed, 100 μA | JTAG test select                                                                                |

| TEST        | 24        | I/O    | Pulldown                     | Fixed, 100 μA | Test enable. This terminal must be connected to ground directly or through a pulldown resistor. |

## 4.2.13 Flash

#### Table 4-13. Flash

| TERMINAL    |           | SIGNAL         | RESET         | PULL TYPE | DESCRIPTION                                                                                                                                                                       |

|-------------|-----------|----------------|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL NAME | 100<br>PZ | TYPE           | PULL<br>STATE |           |                                                                                                                                                                                   |

| FLTP1       | 3         | Input          | N/A           | None      | Flash test pins. For proper operation this terminal                                                                                                                               |

| FLTP2       | 4         | Input          | N/A           | None      | must connect only to a test pad or not be connected at all [no connect (NC)].  The test pad must not be exposed in the final product where it might be subjected to an ESD event. |

| VCCP        | 96        | 3.3-V<br>Power | N/A           | None      | Flash external pump voltage (3.3 V). This terminal is required for both flash read and flash program and erase operations.                                                        |

# 4.2.14 Core Supply

## Table 4-14. Core Supply

| TERMINAL    |           | SIGNAL | RESET         | PULL TYPE | DESCRIPTION                  |

|-------------|-----------|--------|---------------|-----------|------------------------------|

| SIGNAL NAME | 100<br>PZ | TYPE   | PULL<br>STATE |           |                              |

| VCC         | 13        | 1.2-V  | N/A           | None      | Digital logic and RAM supply |

| VCC         | 21        | Power  |               |           |                              |

| VCC         | 30        |        |               |           |                              |

| VCC         | 32        |        |               |           |                              |

| VCC         | 61        |        |               |           |                              |

| VCC         | 88        |        |               |           |                              |

| VCC         | 99        |        |               |           |                              |

# 4.2.15 I/O Supply

## Table 4-15. I/O Supply

| TERMINAL    |           | SIGNAL | RESET PULL TYPE | PULL TYPE | DESCRIPTION |

|-------------|-----------|--------|-----------------|-----------|-------------|

| SIGNAL NAME | 100<br>PZ | TYPE   | PULL<br>STATE   |           |             |

| VCCIO       | 6         | 3.3-V  | N/A             | None      | I/O supply  |

| VCCIO       | 28        | Power  |                 |           |             |

| VCCIO       | 60        |        |                 |           |             |

| VCCIO       | 85        |        |                 |           |             |

## 4.2.16 Core and I/O Supply Ground Reference

## Table 4-16. Core and I/O Supply Ground Reference

| TERMINAL    |           | SIGNAL | RESET         | PULL TYPE | DESCRIPTION                                                  |

|-------------|-----------|--------|---------------|-----------|--------------------------------------------------------------|

| SIGNAL NAME | 100<br>PZ | TYPE   | PULL<br>STATE |           |                                                              |

| VSS         | 7         | Ground | N/A           | None      | Device Ground Reference. This is a single                    |

| VSS         | 17        |        |               |           | ground reference for all supplies except for the ADC supply. |

| VSS         | 20        |        |               |           | уче в варру.                                                 |

| VSS         | 29        |        |               |           |                                                              |

| VSS         | 33        |        |               |           |                                                              |

| VSS         | 59        |        |               |           |                                                              |

| VSS         | 72        |        |               |           |                                                              |

| VSS         | 86        |        |               |           |                                                              |

| VSS         | 87        |        |               |           |                                                              |

| VSS         | 100       |        |               |           |                                                              |

## 4.3 Output Multiplexing and Control

Output multiplexing will be used in the device. The multiplexing is used to allow development of additional package and feature combinations as well as to maintain pinout compatibility with the marketing device family.

In all cases indicated as multiplexed, the output buffers are multiplexed.

#### 4.3.1 Notes on Output Multiplexing

Table 4-17 shows the output signal multiplexing and control signals for selecting the desired functionality for each pin.

- The pins default to the signal defined by the DEFAULT FUNCTION column in Table 4-17

- The CONTROL 1, CONTROL 2, and CONTROL 3 columns indicate the multiplexing control register and the bit that must be set in order to select the corresponding functionality to be output on any particular pin.

For example, consider the multiplexing on pin 18, shown in Table 4-18.

**Table 4-17. Output Mux Options**

| 100 PZ PIN | DEFAULT<br>FUNCTION | CONTROL 1   | OPTION2    | CONTROL 2   | OPTION 3  | CONTROL 3   |

|------------|---------------------|-------------|------------|-------------|-----------|-------------|

| 1          | GIOA[0]             | PINMMR0[8]  | SPI3nCS[3] | PINMMR0[9]  | _         | _           |

| 2          | GIOA[1]             | PINMMR1[0]  | SPI3nCS[2] | PINMMR1[1]  | _         | _           |

| 5          | GIOA[2]             | PINMMR1[8]  | SPI3nCS[1] | PINMMR1[9]  | _         | _           |

| 8          | GIOA[3]             | PINMMR1[16] | SPI2nCS[3] | PINMMR1[17] | _         | _           |

| 9          | GIOA[4]             | PINMMR1[24] | SPI2nCS[2] | PINMMR1[25] | _         | _           |

| 10         | GIOA[5]             | PINMMR2[0]  | EXTCLKIN   | PINMMR2[1]  | _         | _           |

| 12         | GIOA[6]             | PINMMR2[8]  | SPI2nCS[1] | PINMMR2[9]  | N2HET[31] | PINMMR2[10] |

| 18         | GIOA[7]             | PINMMR2[16] | N2HET[29]  | PINMMR2[17] | _         | _           |

| 93         | MIBSPI1nCS[1]       | PINMMR6[8]  | EQEPS      | PINMMR6[9]  | N2HET[17] | PINMMR6[10] |

| 27         | MIBSPI1nCS[2]       | PINMMR3[0]  | N2HET[20]  | PINMMR3[1]  | N2HET[19] | PINMMR3[2]  |

| 39         | MIBSPI1nCS[3]       | PINMMR4[8]  | N2HET[26]  | PINMMR4[9]  | _         | _           |

| 68         | MIBSPI1nENA         | PINMMR5[8]  | N2HET[23]  | PINMMR5[9]  | N2HET[30] | PINMMR5[10] |

| 36         | SPI3CLK             | PINMMR3[16] | EQEPA      | PINMMR3[17] | _         | _           |

| 38         | SPI3nCS[0]          | PINMMR4[0]  | EQEPI      | PINMMR4[1]  | _         | _           |

| 37         | SPI3nENA            | PINMMR3[24] | EQEPB      | PINMMR3[25] | _         | _           |

| 58         | ADEVT               | PINMMR4[16] | N2HET[28]  | PINMMR4[17] | _         | _           |

#### Table 4-18. Muxing Example

| 100 PZ PIN | DEFAULT<br>FUNCTION | CONTROL 1   | OPTION2   | CONTROL 2   | OPTION 3 | CONTROL 3 |

|------------|---------------------|-------------|-----------|-------------|----------|-----------|

| 18         | GIOA[7]             | PINMMR2[16] | N2HET[29] | PINMMR2[17] | _        | -         |

- When GIOA[7] is configured as an output pin in the GPIO module control register, then the programmed output level appears on pin 18 by default. The PINMMR2[16] bit is set by default to indicate that the GIOA[7] signal is selected to be output.

- If the application must output the N2HET[29] signal on pin 18, it must clear PINMMR2[16] and set PINMMR2[17].

- The pin is connected as input to both the GPIO and N2HET modules. That is, there is no input multiplexing on this

pin.

#### 4.3.2 General Rules for Multiplexing Control Registers

- The PINMMR control registers can only be written in privileged mode. A write in a nonprivileged mode will generate an error response.

- If the application writes all 0s to any PINMMR control register, then the default functions are selected for the

affected pins.

- Each byte in a PINMMR control register is used to select the functionality for a given pin. If the application sets more than 1 bit within a byte for any pin, then the default function is selected for this pin.

- Some bits within the PINMMR registers could be associated with internal pads that are not brought out in the 100pin package. As a result, bits marked reserved should not be written as 1.

#### 4.4 Special Multiplexed Options

Special controls are implemented to affect particular functions on this microcontroller. These controls are described in this section.

## 4.4.1 Filtering for eQEP Inputs

#### 4.4.1.1 eQEPA Input

- When PINMMR8[0] = 1, the eQEPA input is double-synchronized using VCLK.

- When PINMMR8[0] = 0 and PINMMR8[1] = 1, the eQEPA input is double-synchronized and then qualified through a fixed 6-bit counter using VCLK.

- PINMMR8[0] = 0 and PINMMR8[1] = 0 is an illegal combination and behavior defaults to PINMMR8[0] = 1.

## 4.4.1.2 eQEPB Input

- When PINMMR8[8] = 1, the eQEPB input is double-synchronized using VCLK.

- When PINMMR8[8] = 0 and PINMMR8[9] = 1, the eQEPB input is double-synchronized and then qualified through a fixed 6-bit counter using VCLK.

- PINMMR8[8] = 0 and PINMMR8[9] = 0 is an illegal combination and behavior defaults to PINMMR8[8] = 1.

#### 4.4.1.3 eQEPI Input

- When PINMMR8[16] = 1, the eQEPI input is double-synchronized using VCLK.

- When PINMMR8[16] = 0 and PINMMR8[17] = 1, the eQEPI input is double-synchronized and then qualified through a fixed 6-bit counter using VCLK.

- PINMMR8[16] = 0 and PINMMR8[17] = 0 is an illegal combination and behavior defaults to PINMMR8[16] = 1.

#### 4.4.1.4 **eQEPS** Input

- When PINMMR8[24] = 1, the eQEPS input is double-synchronized using VCLK.

- When PINMMR8[24] = 0 and PINMMR8[25] = 1, the eQEPS input is double-synchronized and then qualified through a fixed 6-bit counter using VCLK.

- PINMMR8[24] = 0 and PINMMR8[25] = 0 is an illegal combination and behavior defaults to PINMMR8[24] = 1.

#### 4.4.2 N2HET PIN\_nDISABLE Input Port

- When PINMMR9[0] = 1, GIOA[5] is connected directly to N2HET PIN nDISABLE input of the N2HET module.

- When PINMMR9[0] = 0 and PINMMR9[1] = 1, EQEPERR is inverted and double-synchronized using VCLK before

connecting directly to the N2HET PIN nDISABLE input of the N2HET module.

- PINMMR9[0] = 0 and PINMMR9[1] = 0 is an illegal combination and behavior defaults to PINMMR9[0] = 1.

## 5 Specifications

## 5.1 Absolute Maximum Ratings<sup>(1)</sup>

Over Operating Free-Air Temperature Range

|                                                |                                                                                               | MIN  | MAX  | UNIT |

|------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|

|                                                | V <sub>CC</sub> <sup>(2)</sup>                                                                | -0.3 | 1.43 |      |

| Supply voltage                                 | V <sub>CCIO</sub> , V <sub>CCP</sub> <sup>(2)</sup>                                           | -0.3 | 4.6  | V    |

|                                                | V <sub>CCAD</sub>                                                                             | -0.3 | 3.6  |      |

| lanut valtaga                                  | All input pins                                                                                | -0.3 | 4.6  |      |

| Input voltage                                  | ADC input pins                                                                                | -0.3 | 4.6  | V    |

|                                                | $I_{IK}$ (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>CCIO</sub> )<br>All pins, except ADIN | -20  | 20   |      |

| Input clamp current                            | $I_{IK}$ (V <sub>I</sub> < 0 or V <sub>I</sub> > V <sub>CCAD</sub> )<br>ADIN                  | -10  | 10   | mA   |

|                                                | Total                                                                                         | -40  | 40   |      |

| Operating free-air temperature, T <sub>A</sub> |                                                                                               | -40  | 105  | °C   |

| Operating junction temperature, T <sub>J</sub> |                                                                                               | -40  | 130  | °C   |

| Latch-up performance                           | I-test, All I/O pins                                                                          | -100 | 100  | mA   |

| Storage temperature, T                         | sta                                                                                           | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 5.2 ESD Ratings

|                    |                                            |                                                 |                           | VALUE | UNIT |

|--------------------|--------------------------------------------|-------------------------------------------------|---------------------------|-------|------|

|                    | Floatroatatio discharge (FSD)              | Human Body Model (HBM), per ANSI/ESDA/J         | EDEC JS001 <sup>(1)</sup> | ±2    | kV   |

| V <sub>(ESD)</sub> | Electrostatic discharge (ESD) performance: | Charged Device Model (CDM), per JESD22-C101 (2) | All pins                  | ±250  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 5.3 Power-On Hours (POH)(1)(2)

| NOMINAL CORE VOLTAGE (V <sub>CC</sub> ) | JUNCTION<br>TEMPERATURE (Tj) | LIFETIME POH |

|-----------------------------------------|------------------------------|--------------|

| 1.2                                     | 105ºC                        | 100K         |

<sup>(1)</sup> This information is provided solely for your convenience and does not extend or modify the warranty provided under TI's standard terms and conditions for TI semiconductor products.

<sup>(2)</sup> Maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to their associated grounds.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> To avoid significant degradation, the device power-on hours (POH) must be limited to those specified in this table. To convert to equivalent POH for a specific temperature profile, see the *Calculating Equivalent Power-on-Hours for Hercules Safety MCUs* Application Report (SPNA207).

#### Recommended Operating Conditions(1) 5.4

|                                          |                                                                                                    | MIN  | NOM | MAX  | UNIT |

|------------------------------------------|----------------------------------------------------------------------------------------------------|------|-----|------|------|

| $V_{CC}$                                 | Digital logic supply voltage (Core)                                                                | 1.14 | 1.2 | 1.32 | ٧    |

| $V_{CCIO}$                               | Digital logic supply voltage (I/O)                                                                 | 3    | 3.3 | 3.6  | ٧    |

| V <sub>CCAD /</sub> V <sub>ADREFHI</sub> | MibADC supply voltage / A-to-D high-voltage reference source                                       | 3    | 3.3 | 3.6  | ٧    |

| $V_{CCP}$                                | Flash pump supply voltage                                                                          | 3    | 3.3 | 3.6  | ٧    |

| $V_{SS}$                                 | Digital logic supply ground                                                                        |      | 0   |      | V    |

| V <sub>SSAD /</sub> V <sub>ADREFLO</sub> | MibADC supply ground / A-to-D low-voltage reference source                                         | -0.1 |     | 0.1  | ٧    |

| V <sub>SLEW</sub>                        | Maximum positive slew rate for V <sub>CCIO</sub> , V <sub>CCAD</sub> and V <sub>CCP</sub> supplies |      |     | 1    | V/µs |

| T <sub>A</sub>                           | Operating free-air temperature                                                                     | -40  |     | 105  | °C   |

| $T_J$                                    | Operating junction temperature (2)                                                                 | -40  |     | 130  | ô    |

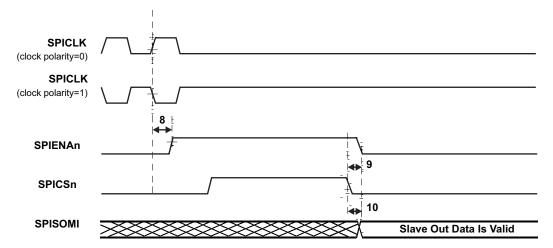

#### **Switching Characteristics Over Recommended Operating Conditions for Clock Domains** 5.5

**Table 5-1. Clock Domains Timing Specifications**

|                     | PARAMETER                                                                      | CONDITIONS | MIN MAX | UNIT |

|---------------------|--------------------------------------------------------------------------------|------------|---------|------|

| f <sub>HCLK</sub>   | HCLK - System clock frequency                                                  |            | 100     | MHz  |

| f <sub>GCLK</sub>   | GCLK - CPU clock frequency (ratio f <sub>GCLK</sub> : f <sub>HCLK</sub> = 1:1) |            | fuclk   | MHz  |

| f <sub>VCLK</sub>   | VCLK - Primary peripheral clock frequency                                      |            | 100     | MHz  |

| f <sub>VCLK2</sub>  | VCLK2 - Secondary peripheral clock frequency                                   |            | 100     | MHz  |

| f <sub>VCLKA1</sub> | VCLKA1 - Primary asynchronous peripheral clock frequency                       |            | 100     | MHz  |

| f <sub>RTICLK</sub> | RTICLK - clock frequency                                                       |            | fvclk   | MHz  |

All voltages are with respect to  $V_{SS}$ , except  $V_{CCAD}$ , which is with respect to  $V_{SSAD}$ Reliability data is based upon a temperature profile that is equivalent to 100,000 power-on hours at 105°C junction temperature.

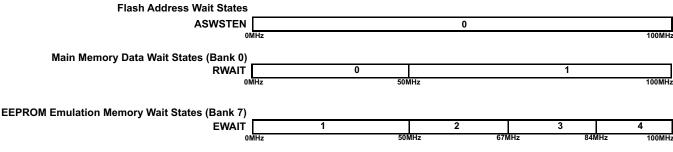

#### 5.6 Wait States Required

The TCM RAM can support program and data fetches at full CPU speed without any address or data wait states required. There are no registers which need to be programmed for RAM wait states.

The TCM flash can support zero address and data wait states up to a CPU speed of 50 MHz in nonpipelined mode. The flash supports a maximum CPU clock speed of 100 MHz in pipelined mode with no address wait states and one data wait state.

The proper wait states should be set in the register fields Address Setup Wait State Enable (ASWSTEN 0xFFF87000[4]), Random Wait states (RWAIT 0xFFF87000[11:8]), and Emulation Wait states (EWAIT 0xFFF872B8[19:16]) as shown in Figure 5-1.

Figure 5-1. Wait States Scheme

The flash wrapper defaults to nonpipelined mode with address wait states disabled, ASWSTEN=0; the main memory random-read data wait state, RWAIT=1; and the emulation memory random-read wait states, EWAIT=1.

20

#### 5.7 **Power Consumption**

Over Recommended Operating Conditions

|                                                           | PARAMETER                                                 | TEST CONDITIONS                                                                                               | MIN | TYP | MAX                   | UNIT |

|-----------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-----|-----------------------|------|

|                                                           | V <sub>CC</sub> digital supply current (operating mode)   | f <sub>HCLK</sub> = 100 MHz<br>f <sub>VCLK</sub> = 100 MHz,<br>Flash in pipelined<br>mode, V <sub>CCmax</sub> |     |     | 150 <sup>(1)</sup>    |      |

| Icc                                                       | V <sub>CC</sub> digital supply current (LBIST mode)       | LBIST clock rate = 50 MHz                                                                                     |     |     | 165 <sup>(2)(3)</sup> | mA   |

|                                                           | V <sub>CC</sub> digital supply current (PBIST mode)       | PBIST ROM clock<br>frequency =<br>100 MHz                                                                     |     |     | 150 (2)(3)            |      |

| I <sub>CCREFHI</sub>                                      | AD <sub>REFHI</sub> supply current (operating mode)       | AD <sub>REFHImax</sub>                                                                                        |     |     | 3                     | mA   |

| I <sub>CCAD</sub>                                         | V <sub>CCAD</sub> supply current (operating mode)         | V <sub>CCADmax</sub>                                                                                          |     |     |                       |      |

| I <sub>CCIO</sub>                                         | V <sub>CCIO</sub> digital supply current (operating mode) | No DC load, V <sub>CCmax</sub>                                                                                |     |     | 45 <sup>(4)</sup>     | mA   |

| I <sub>CCP</sub>                                          | V <sub>CCP</sub> pump supply current                      | Read mode                                                                                                     |     |     |                       |      |

| I <sub>CCP,</sub><br>I <sub>CCIO,</sub> I <sub>CCAD</sub> | 3.3-V supply current                                      | Read from one bank<br>and program or<br>erase another,<br>V <sub>CCPmax</sub>                                 |     |     | 65 <sup>(4)</sup>     | mA   |

- (1) The maximum I<sub>CC</sub>, value can be derated

- linearly with voltage

by 0.76 mA/MHz for lower operating frequency when f<sub>HCLK</sub>= f<sub>VCLK</sub>

- for lower junction temperature by the equation below where T<sub>JK</sub> is the junction temperature in Kelvin and the result is in milliamperes.

36 0.001 0.026T<sub>JK</sub>

(2) The maximum I<sub>CC</sub>, value can be derated

- - linearly with voltage

- for lower junction temperature by the equation below where T<sub>JK</sub> is the junction temperature in Kelvin and the result is in milliamperes.

36 0.001 <sup>0.026T</sup><sub>JK</sub>

LBIST and PBIST currents are for a short duration, typically less than 10 ms. They are usually ignored for thermal calculations for the

- device and the voltage regulator

- Maximum current requirement of the three combined supplies

#### 5.8 Thermal Resistance Characteristics for PZ

Table 5-2 shows the thermal resistance characteristics for the PQFP - PZ mechanical packages.

Table 5-2. Thermal Resistance Characteristics (S-PQFP Package) [PZ]

| PARAMETER       | °C/W |

|-----------------|------|

| $R_{\theta JA}$ | 48   |

| $R_{	heta JC}$  | 5    |

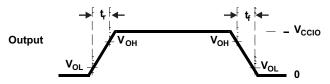

## 5.9 Input/Output Electrical Characteristics<sup>(1)</sup>

Over Recommended Operating Conditions

|                  | PARAMETER                     |                                 | TEST CONDITIONS                                       | MIN                     | TYP | MAX                   | UNIT |

|------------------|-------------------------------|---------------------------------|-------------------------------------------------------|-------------------------|-----|-----------------------|------|

| V <sub>hys</sub> | Input hysteresis              | All inputs                      |                                                       | 180                     |     |                       | mV   |

| $V_{IL}$         | Low-level input voltage       | All inputs (2)                  |                                                       | -0.3                    |     | 0.8                   | ٧    |

| $V_{IH}$         | High-level input voltage      | All inputs <sup>(2)</sup>       |                                                       | 2                       |     | $V_{CCIO} + 0.3$      | V    |

|                  |                               | ·                               | $I_{OL} = I_{OLmax}$                                  |                         |     | 0.2 V <sub>CCIO</sub> |      |

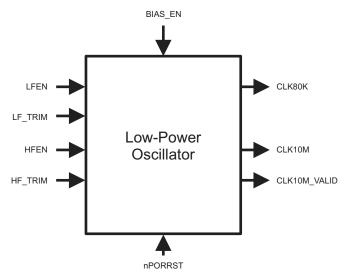

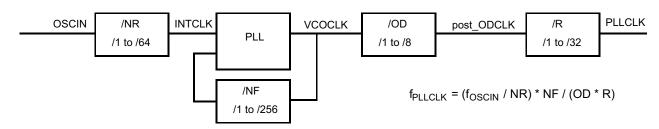

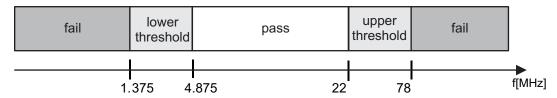

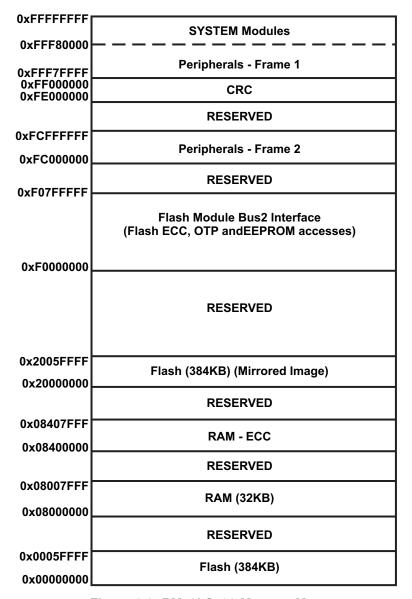

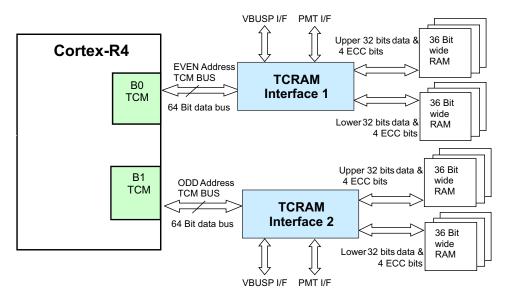

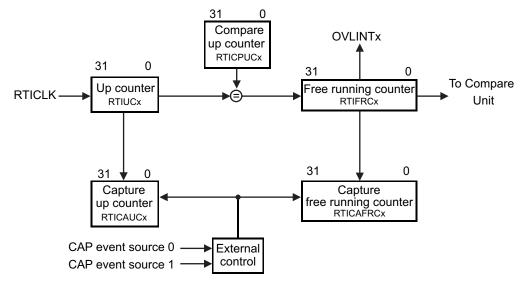

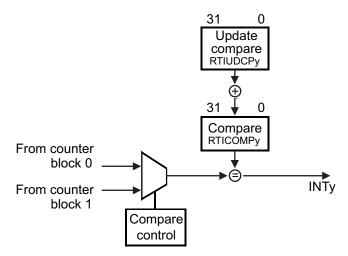

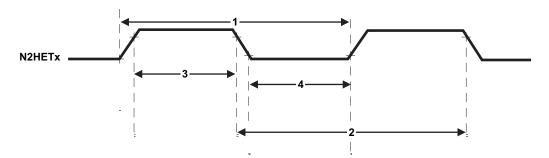

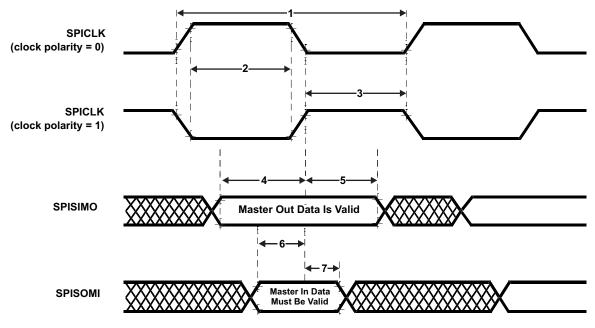

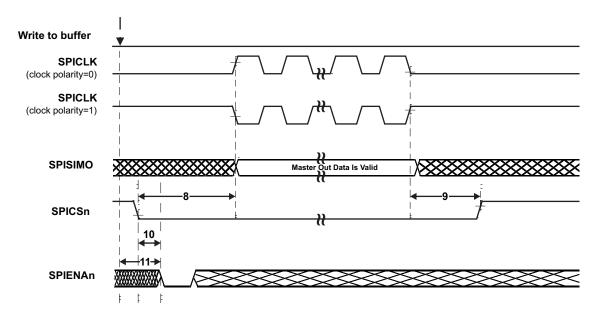

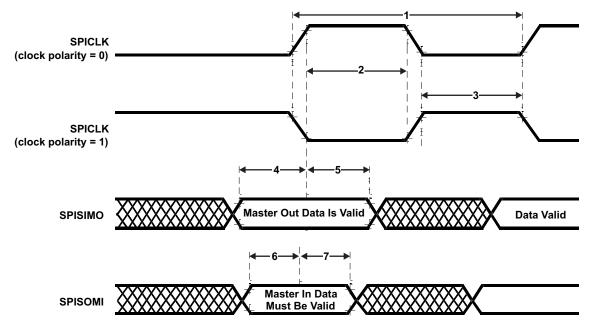

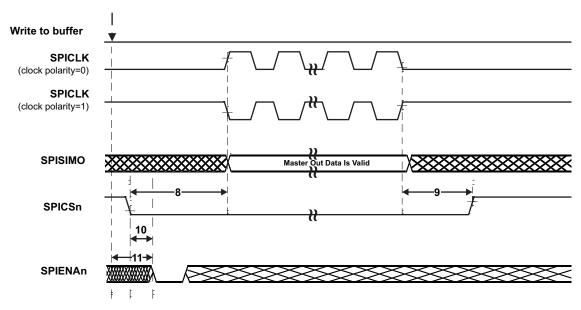

| V <sub>OL</sub>  | Low-level output voltage      |                                 | $I_{OL} = 50 \; \mu A, \\ standard \; output \\ mode$ |                         |     | 0.2                   | V    |