# MC9S12DJ64

# **Target Applications**

- > Automotive applications

- > Industrial control

### **Overview**

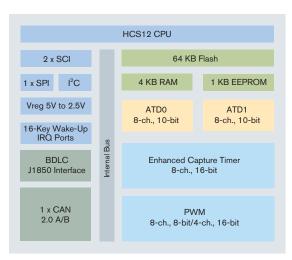

Freescale Semiconductor's HCS12 family of microcontrollers (MCUs) is the next generation of the highly successful 68HC12 architecture. Using Freescale's industry-leading 0.25 µs Flash, the MC9S12DJ64 is part of a pin-compatible family that scales from 32 KB to 512 KB of Flash memory. The DJ64 provides an upward migration path from Freescale's 68HC08, 68HC11 and 68HC12 architectures for applications that need larger memory, more peripherals and higher performance. Also, with the increasing number of CAN/J1850-based electronic control units (ECUs), its multiple network modules support this environment by enabling highly efficient communications between different network buses.

| Features                                                                                                      | Benefits                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Performance 16-bit HCS12 CPU Core                                                                        |                                                                                                                                                                                                                                          |

| > 25 MHz bus operation at 5V for 40 ns minimum instruction cycle time                                         | > Object code compatible 68HC12                                                                                                                                                                                                          |

|                                                                                                               | > Assembly source code compatible with the 68HC11                                                                                                                                                                                        |

|                                                                                                               | > C-optimized architecture produces extremely compact code                                                                                                                                                                               |

| On-Chip Debug Interface                                                                                       |                                                                                                                                                                                                                                          |

| <ul><li>&gt; Dedicated serial debug interface</li><li>&gt; On-chip breakpoints</li></ul>                      | <ul> <li>Real-time in-circuit emulation and debug<br/>without expensive and cumbersome box<br/>emulators</li> </ul>                                                                                                                      |

|                                                                                                               | > Read/write memory and registers while running at full speed                                                                                                                                                                            |

| Network Modules                                                                                               |                                                                                                                                                                                                                                          |

| > One msCAN module implementing the CAN                                                                       | > Programmable bit rate up to 1 Mbps                                                                                                                                                                                                     |

| 2.0 A/B protocol  • Five receive buffers per module with FIFO storage scheme                                  | > FIFO receive approach superior for event-driven networks                                                                                                                                                                               |

| Three transmit buffers per module with internal prioritization                                                | > Ability to send and receive messages across<br>an SAE J1850 serial communication network                                                                                                                                               |

| > One J1850 module                                                                                            |                                                                                                                                                                                                                                          |

| Integrated Third-Generation Flash Memory                                                                      |                                                                                                                                                                                                                                          |

| > In-application reprogrammable                                                                               | > Flexibility to change code in the field                                                                                                                                                                                                |

| > Self-timed, fast programming                                                                                | > Efficient end-of-line programming                                                                                                                                                                                                      |

| <ul> <li>Fast Flash page erase—20 ms (512 bytes)</li> </ul>                                                   | > Total program time for 128 KB code                                                                                                                                                                                                     |

| - Can program 16 bits in 20 μs while                                                                          | is less than five seconds                                                                                                                                                                                                                |

| in burst mode > 5V Flash program/erase/read                                                                   | <ul> <li>Reduces production programming cost<br/>through ultra-fast programming</li> </ul>                                                                                                                                               |

| > Flash granularity—512 byte Flash erase/<br>2 byte Flash program                                             | No external high voltage or charge<br>pump required                                                                                                                                                                                      |

| > Flexible block protection and security                                                                      | > Virtual EEPROM implementation, Flash array usable for EE extension                                                                                                                                                                     |

| 1 KB Integrated EEPROM                                                                                        |                                                                                                                                                                                                                                          |

| > Flexible protection scheme for protection against accidental program or erase                               | <ul> <li>Can erase 4 bytes at a time and program<br/>2 bytes at a time for calibration, security,<br/>personality and diagnostic information</li> </ul>                                                                                  |

| > EEPROM can be programmed in 46 µs                                                                           |                                                                                                                                                                                                                                          |

| 10-bit Analog-to-Digital Converter (ADC)                                                                      |                                                                                                                                                                                                                                          |

| <ul> <li>Two, 8-channel ADCs</li> <li>7 μs, 10-bit single conversion time, scan<br/>mode available</li> </ul> | <ul> <li>Fast, easy conversion from analog inputs like temperature, pressure and fluid levels to digita values for CPU processing</li> <li>Can effectively have 3.5 μs conversion time by sampling same signal with both ADCs</li> </ul> |

|                                                                                                               | , , ,                                                                                                                                                                                                                                    |

### **Benefits** Clock Generation Module with Phase-Lock Loop (PLL) > Clock monitor with self clock mode in case > Reliable, robust operation of no external clock Provides high performance using low-cost > Programmable clock frequency with 1024 reference crystals options ranging from divide by 16 to multiply > Reduces generated noise by 64 from base oscillator > Reduces power consumption > Real-time interrupt > Easily able to implement real-time clock > Watchdog **Enhanced Capture Timer** 8-channel, 16-bit with input capture, output > Flexible, programmable timer system compare and pulse accumulator > 16-bit modulus down counter 8-bit or 16-bit Pulse-Width Modulation (PWM) > 8-channel, 8-bit or 4-channel, 16-bit PWM > Efficiently implement motor control, battery charging or digital-to-analog (DAC) functions > PWM supports center-aligned operation **Two Serial Communications Interfaces** > Asynchronous communication between the > 8192 prescaler options MCU and a terminal, computer or a network of MCUs > Exact baud rate matching One Serial Peripheral Interface > Up to 12.5 Mbps > High-speed synchronous communication between multiple MCUs or between MCU and serial peripherals Inter-IC (I2C) Bus > 256 clock-rate options > Provides a simple, efficient method of data exchange between devices > Minimizes the need for large numbers of connections between devices and eliminates the need for an address decoder Up to 91 Input/Output (I/O) Lines > Programmable pull-ups/pull-downs > Reduce system cost > Dual drive capability > Able to tailor application for minimum EMC or high current loads

| Annlication | Notae | and | Enaineerina | Rullatine |

|-------------|-------|-----|-------------|-----------|

|             |       |     |             |           |

| AN1284     | Transporting M68HC11 Code to M68HC12 Devices                      |

|------------|-------------------------------------------------------------------|

| AN1716     | Using M68HC12 Indexed Indirect Addressing                         |

| AN1775     | Expanding Digital Input with an A/D Converter                     |

| AN1783     | Determining MCU Oscillator Start-Up Parameters                    |

| AN2104     | Using Background Debug Mode for the M68HC12 Family                |

| AN2204     | Fast NVM Programming for the MC9S12DP256                          |

| AN2216     | MC9S12DP256 Software Development Using Metrowerks CodeWarrior™    |

| AN2318     | Using the I <sup>2</sup> C Bus with HCS12 Microcontrollers        |

| BCANPSV2.0 | Bosch Controller Area Network (CAN) Version 2.0 Protocol Standard |

| BDLCRM     | Byte Data Link Controller Reference Manual                        |

| EB396      | Use of OSC2/XTAL as a Clock Output on Motorola Microcontrollers   |

|            |                                                                   |

### **Data Sheets**

9S12DJ64DGV1 MC9S12A64 Device Guide MC9S12A64 Port Integration S12A64PIMV1 Module Block Guide

S12BDMV4 HCS12 Background Debug (BDM)

Block Guide

HCS12 Breakpoint (BKP) Block Guide S12BKVD1 S12CPUV2 HCS12 CPU Reference Manual S12MSCANV2 HCS12 Motorola Scalable Controller Area Network Block Guide

S12ATD10B8CV2 HCS12 10-bit 8-channel Analog to

Digital Block Guide

S12CRGV3 HCS12 Clock Reset Generator

Block Guide

S12ECT16B8CV1 HCS12 16-bit 8-channel Enhanced Capture Timer Block Guide

S12EETS2KV1 HCS12 2K EEPROM Block Guide S12FTS128KV1 HCS12 128K Flash Block Guide S12IICV2 HCS12 I2C Block Guide

S12INTV1 HCS12 Interrupt (INT) Block Guide S12MEBIV3 HCS12 Multiplexed External Bus Interface (MEBI) Block Guide HCS12 Module Mapping Control S12MMCV4 (MMC) Block Guide

S12PWM8B8CV1 HCS12 8-bit 8-channel Pulse-Width

Modulator Block Guide S12SCIV2 HCS12 Serial Communications

Interface Block Guide S12SPIV2 HCS12 Serial Peripheral Interface

Block Guide

HCS12 Voltage Regulator S12VRFGV1

Block Guide S12BDLCV1 HCS12 Byte Data Link Controller

Block Guide

# Cost-Effective Development Tools

For more information on development tools, please refer to the Freescale Development Tool Selector Guide (SG1011).

M68KIT912DP256

\$495\*

Evaluation kit for development and evaluation of HCS12 application code that includes the M68EVB912DP256 and

**USBMULTILINKBDM**

M68CYCLONEPRO

\$499

HC08/HCS08/HC12/HCS12 stand-alone Flash programmer or in-circuit emulator, debugger, Flash programmer; USB, serial or Ethernet

interface options

USBMULTILINKBDM Universal HCS08/HCS12 in-circuit \$99\* emulator, debugger, and Flash programmer; USB PC interface

CWX-H12-SE Free\*

CodeWarrior™ Special Edition for HCS12 MCUs; includes integrated development environment (IDE), linker, debugger, unlimited assembler, Processor Expert™ auto-code generator, full-chip simulation and limited C compiler

## Package Options

| Part Number   | Раскаде  |

|---------------|----------|

| MC9S12DJ64CFU | 80 QFP   |

| MC9S12DJ64VFU | 80 QFP   |

| MC9S12DJ64MFU | 80 QFP   |

| MC9S12DJ64CPV | 112 LQFP |

| MC9S12DJ64VPV | 112 LQFP |

| MC9S12DJ64MPV | 112 LQFP |

|               |          |

Temp. Range -40°C to +85°C -40°C to +105°C -40°C to +125°C -40°C to +85°C -40°C to +105°C -40°C to +125°C

80-Lead QFP ...... FU ....

Learn More: For more information about Freescale products, please visit www.freescale.com.