#### ZL50050

#### 8 K-Channel Digital Switch with High Jitter Tolerance, Per Stream Rate Conversion (2, 4, 8, 16, or 32 Mbps), and 32 Inputs and 32 Outputs

Data Sheet

#### Features

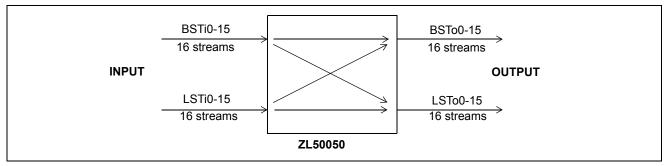

- 8,192-channel x 8,192-channel non-blocking unidirectional switching. The Backplane and Local inputs and outputs can be combined to form a non-blocking switching matrix with 32 input streams and 32 output streams

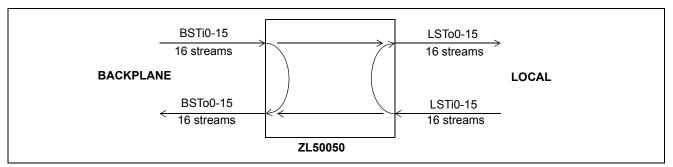

- 4,096-channel x 4,096-channel non-blocking Backplane input to Local output stream switch

- 4,096-channel x 4,096-channel non-blocking Local input to Backplane output stream switch

- 4,096-channel x 4,096-channel non-blocking Backplane input to Backplane output switch

- 4,096-channel x 4,096-channel non-blocking Local input to Local output stream switch

- Rate conversion on all data paths, Backplane-to-Local, Local-to-Backplane, Backplane-to-Backplane and Local-to-Local streams

- Backplane port accepts 16 input and 16 output ST-BUS streams with data rates of 2.048 Mbps, 4.096 Mbps, 8.192 Mbps or 16.384 Mbps in any combination, or a fixed allocation of 8 input and 8 output streams at 32.768 Mbps

- Local port accepts 16 input and 16 output ST-BUS streams with data rates of 2.048 Mbps,

#### Ordering Information

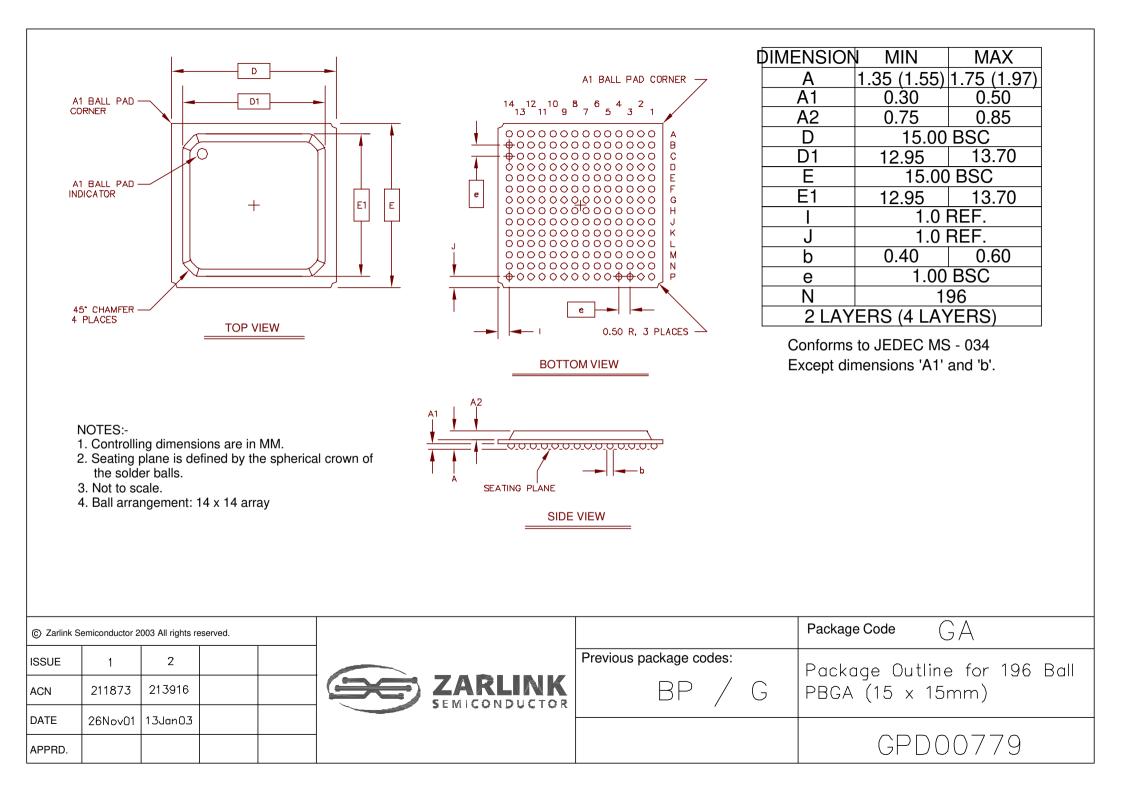

ZL50050GAC 196 Ball PBGA Trays ZL50050GAG2 196 Ball PBGA\*\* Trays \*Pb Free Tin/Silver/Copper

#### -40°C to +85°C

4.096 Mbps, 8.192 Mbps or 16.384 Mbps in any combination, or a fixed allocation of 8 input and 8 output streams at 32.768 Mbps

- Exceptional input clock jitter tolerance (17ns for 16Mbps or lower data rates, 14ns for 32 Mbps)

- Per-stream channel and bit delay for Local and Backplane input streams

- Per-stream advancement for Local and Backplane

output streams

- Constant 2-frame throughput delay for frame integrity

- Per-channel high impedance output control for Local and Backplane streams

- Per-channel driven-high output control for Local and Backplane streams

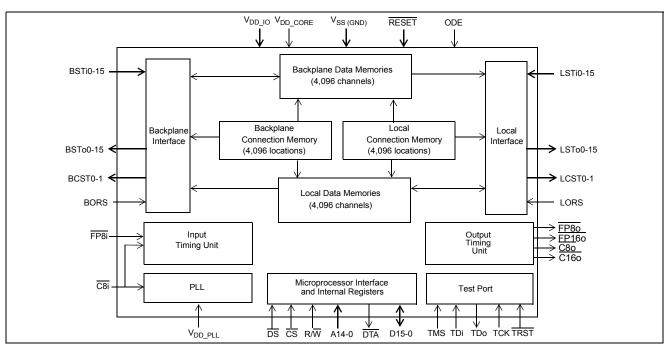

#### Figure 1 - ZL50050 Functional Block Diagram

- · High impedance-control outputs for external drivers on Local and Backplane ports

- · Per-channel message mode for Local and Backplane output streams

- Connection memory block programming for fast device initialization

- BER testing for Local and Backplane ports.

- Automatic selection between ST-BUS and GCI-Bus operation

- Non-multiplexed Motorola microprocessor interface

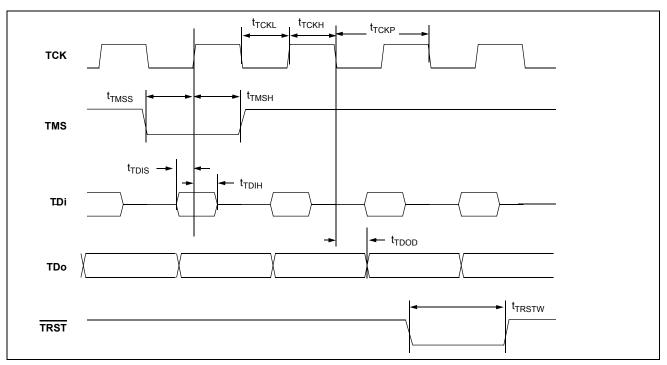

- Conforms to the mandatory requirements of the IEEE-1149.1 (JTAG) standard

- Memory Built-In-Self-Test (BIST), controlled via microprocessor register

- 1.8 V core supply voltage

- 3.3 V I/O supply voltage

- 5 V tolerant inputs, outputs and I/Os

- Pin-to-pin compatible with Zarlink's MT90871 device <sup>1</sup>

Note 1: For software compatibility between ZL50050 and MT90871, please refer to Section 2.6.

## Applications

- Central Office Switches (Class 5)

- Media Gateways

- Class-independent switches

- Access Concentrators

- Scalable TDM-Based Architectures

- Digital Loop Carriers

#### **Device Overview**

The ZL50050 has two data ports, the Backplane and the Local port. Both the Backplane and Local ports have two independent modes of operation, either 16 input and 16 output streams operated at 2.048 Mbps, 4.096 Mbps, 8.192 Mbps or 16.384 Mbps, in any combination, or 8 input and 8 output streams operated at 32.768 Mbps.

The ZL50050 contains two data memory blocks (Backplane and Local) to provide the following switching path configurations:

- Input-to-Output Unidirectional, supporting 8 K x 8 K switching

- Backplane-to-Local Bi-directional, supporting 4 K x 4 K data switching,

- Local-to-Backplane Bi-directional, supporting 4 K x 4 K data switching,

- Backplane-to-Backplane Bi-directional, supporting 4 K x 4 K data switching.

- Local-to-Local Bi-directional, supporting 4 K x 4 K data switching.

The device contains two connection memory blocks, one for the Backplane output and one for the Local output. Data to be output on the serial streams may come from either of the data memories (Connection Mode) or directly from the connection memory contents (Message Mode).

In Connection Mode, the contents of the connection memory define, for each output stream and channel, the source stream and channel (stored in data memory) to be switched.

In Message Mode, microprocessor data can be written to the connection memory for broadcast on the output streams on a per channel basis. This feature is useful for transferring control and status information to external circuits or other ST-BUS devices.

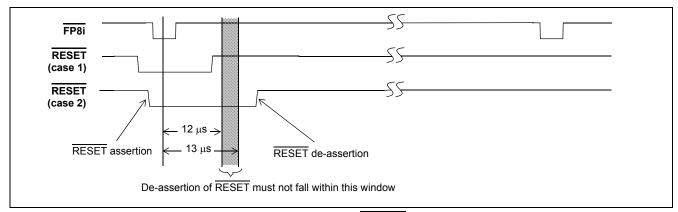

The device uses a master frame pulse ( $\overline{FP8i}$ ) and master clock ( $\overline{C8i}$ ) to define the input frame boundary and timing for both the Backplane port and the Local port. The device will automatically detect whether an ST-BUS or a GCI-Bus style frame pulse is being used. There is a two-frame delay from the time RESET is de-asserted to the establishment of full switch functionality. During this period, the input frame pulse format is determined before switching begins.

The device provides FP8o, FP16o, C8o and C16o outputs to support external devices connected to the outputs of the Backplane and Local ports.

A non-multiplexed Motorola microprocessor port allows programming of the various device operation modes and switching configurations. The microprocessor port provides access for Register read/write, Connection Memory read/write and Data Memory read-only operations. The port has a 15-bit address bus, 16-bit data bus and 4 control signals. The microprocessor may monitor channel data in the Backplane and Local data memories.

The mandatory requirements of the IEEE-1149.1 (JTAG) standard are fully supported via a dedicated test port.

The ZL50050 is available in one package:

• a 15 mm x 15 mm body, 1mm ball-pitch, 196-PBGA.

## **Table of Contents**

| 1.0 Unidirectional and Bi-directional Switching Applications                   |             |

|--------------------------------------------------------------------------------|-------------|

| 1.1 Flexible Configuration                                                     |             |

| 1.1.1 Non-Blocking Unidirectional Configuration (Typical System Configuration) |             |

| 1.1.2 Non-Blocking Bi-directional Configuration                                |             |

| 1.1.3 Blocking Bi-directional Configuration                                    |             |

| 2.0 Functional Description                                                     |             |

| 2.1 Switching Configuration                                                    |             |

| 2.1.1 Unidirectional Switch                                                    |             |

| 2.1.2 Backplane-to-Local Path                                                  |             |

| 2.1.3 Local-to-Backplane Path                                                  |             |

| 2.1.4 Backplane-to-Backplane Path                                              |             |

| 2.1.5 Local-to-Local Path                                                      |             |

|                                                                                |             |

| 2.1.7 Local Port Rate Selection.                                               |             |

| 2.1.7.1 Local Input Port                                                       |             |

| 2.1.7.2 Local Output Port                                                      |             |

| 2.1.8.1 Backplane Input Port                                                   |             |

| 2.1.8.2 Backplane Output Port                                                  |             |

| 2.1.0.2 Backplane Output Port                                                  |             |

| 2.3 Input Frame Pulse and Generated Frame Pulse Alignment                      |             |

| 2.4 Jitter Tolerance Improvement Circuit - Frame Boundary Discriminator.       |             |

| 2.5 Input Clock Jitter Tolerance                                               |             |

| 2.6 Backward Compatibility with MT90871                                        |             |

| 3.0 Input and Output Offset Programming                                        |             |

| 3.1 Input Offsets                                                              |             |

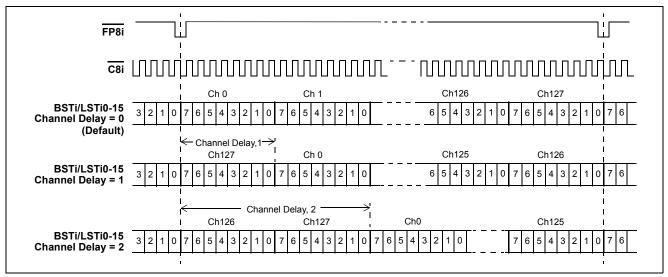

| 3.1.1 Input Channel Delay Programming (Backplane and Local Input Streams)      |             |

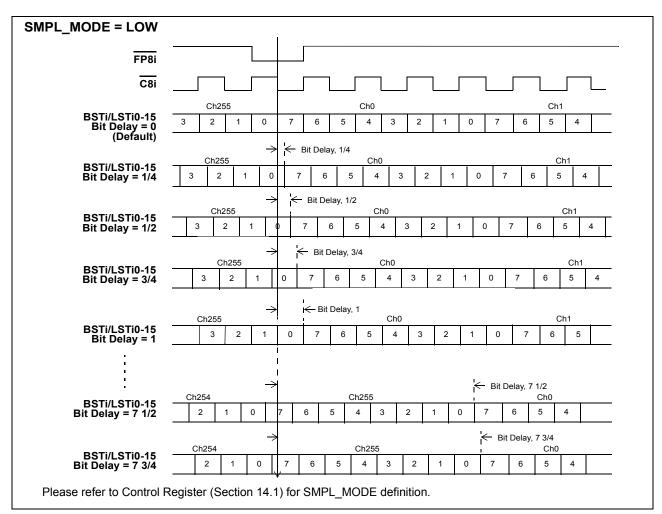

| 3.1.2 Input Bit Delay Programming (Backplane and Local Input Streams)          |             |

| 3.2 Output Advancement Programming (Backplane and Local Output Streams)        |             |

| 4.0 Port High-Impedance Control                                                |             |

| 4.1 LORS/BORS Asserted LOW, Non-32Mbps Mode.                                   |             |

| 4.1 LORS/BORS Asserted LOW, Non-S2Mbps Mode                                    |             |

| 4.3 LORS/BORS Asserted HIGH                                                    |             |

| 5.0 Data Delay Through the Switching Paths                                     |             |

|                                                                                |             |

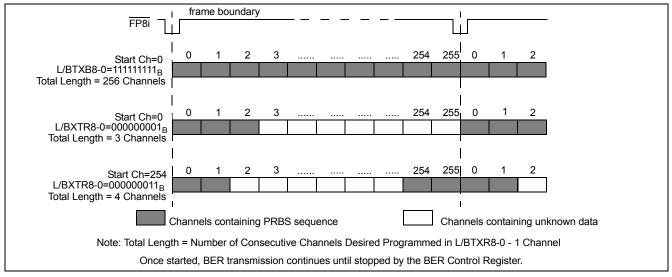

| 6.0 Bit Error Rate Test                                                        |             |

| 7.0 Microprocessor Port                                                        | . 43        |

| 8.0 Device Power-up, Initialization and Reset                                  |             |

| 8.1 Power-Up Sequence                                                          |             |

| 8.2 Initialization                                                             |             |

| 8.3 Reset                                                                      |             |

| 9.0 Connection Memory                                                          | . <b>44</b> |

| 9.1 Local Connection Memory                                                    | . 44        |

| 9.2 Backplane Connection Memory                                                |             |

| 9.3 Connection Memory Block Programming                                        |             |

| 9.3.1 Memory Block Programming Procedure:                                      |             |

| 10.0 Memory Built-In-Self-Test (BIST) Mode                                     | . <b>46</b> |

| 11.0 JTAG Port                                                                 |             |

| 11.1 Test Access Port (TAP)                                                    |             |

| 11.2 TAP Registers                                                             |             |

| 11.2.1 Test Instruction Register                                               |             |

| 11.2.2 Test Data Registers                                                     | . 47        |

|                                                                                |             |

# **Table of Contents**

| 11.2.2.3 The Device Identification Register                    | . 47  |

|----------------------------------------------------------------|-------|

| 11.3 Boundary Scan Description Language (BSDL) File            | . 47  |

| 12.0 Memory Address Mappings                                   | . 48  |

| 12.1 Local Data Memory Bit Definition                          | . 48  |

| 12.2 Backplane Data Memory Bit Definition                      | . 49  |

| 12.3 Local Connection Memory Bit Definition                    | . 49  |

| 12.4 Backplane Connection Memory Bit Definition                | . 50  |

| 13.0 Internal Register Mappings                                | . 52  |

| 14.0 Detailed Register Descriptions                            | . 53  |

| 14.1 Control Register (CR)                                     |       |

| 14.2 Block Programming Register (BPR)                          |       |

| 14.3 Bit Error Rate Test Control Register (BERCR)              | . 58  |

| 14.4 Local Input Channel Delay Registers (LCDR0 to LCDR15)     | . 59  |

| 14.4.1 Local Channel Delay Bits 8-0 (LCD8 - LCD0)              | . 60  |

| 14.5 Local Input Bit Delay Registers (LIDR0 to LIDR15)         | . 61  |

| 14.5.1 Local Input Delay Bits 4-0 (LID[4:0])                   |       |

| 14.6 Backplane Input Channel Delay Registers (BCDR0 to BCDR15) |       |

| 14.6.1 Backplane Channel Delay Bits 8-0 (BCD8 - BCD0)          |       |

| 14.7 Backplane Input Bit Delay Registers (BIDR0 to BIDR15)     |       |

| 14.7.1 Backplane Input Delay Bits 4-0 (BID[4:0])               |       |

| 14.8 Local Output Advancement Registers (LOAR0 to LOAR15)      |       |

| 14.8.1 Local Output Advancement Bits 1-0 (LOA1-LOA0)           |       |

| 14.9 Backplane Output Advancement Registers (BOAR0 - BOAR15)   |       |

| 14.9.1 Backplane Output Advancement Bits 1-0 (BOA1-BOA0).      |       |

| 14.10 Local Bit Error Rate (BER) Registers                     |       |

| 14.10.1 Local BER Start Send Register (LBSSR)                  |       |

| 14.10.2 Local Transmit BER Length Register (LTXBLR)            |       |

| 14.10.3 Local Receive BER Length Register (LRXBLR)             |       |

| 14.10.4 Local BER Start Receive Register (LBSRR)               |       |

| 14.10.5 Local BER Count Register (LBCR)                        |       |

| 14.11 Backplane Bit Error Rate (BER) Registers                 |       |

| 14.11.1 Backplane BER Start Send Register (BBSSR)              |       |

| 14.11.2 Backplane Transmit BER Length Register (BTXBLR)        | . / 1 |

| 14.11.4 Backplane BER Start Receive Register (BRSRR)           |       |

| 14.11.5 Backplane BER Count Register (BBCR)                    |       |

| 14.12 Local Bit Rate Registers                                 |       |

| 14.12.1 Local Input Bit Rate Registers (LIBRR0 - LIBRR15)      | .73   |

| 14.12.2 Local Output Bit Rate Registers (LOBRR0 - LOBRR15)     |       |

| 14.13 Backplane Bit Rate Registers                             |       |

| 14.13.1 Backplane Input Bit Rate Registers (BIBRR0 - BIBRR15). |       |

| 14.13.2 Backplane Output Bit Rate Registers (BOBRR0 - BOBRR15) |       |

| 14.14 Memory BIST Register                                     |       |

| 14.15 Device Identification Register                           |       |

| 15.0 DC Electrical Characteristics                             |       |

|                                                                |       |

| 16.0 AC Electrical Characteristics                             | . 00  |

# List of Figures

| Figure 1 - ZL50050 Functional Block Diagram1                                                                |

|-------------------------------------------------------------------------------------------------------------|

| Figure 2 - ZL50050 PBGA Connections (196 PBGA, 15 mm x 15 mm) Pin Diagram                                   |

| (as viewed through top of package)                                                                          |

| Figure 3 - 8,192 x 8,192 Channels (16 Mbps), Unidirectional Switching                                       |

| Figure 4 - 4,096 x 4,096 Channels (16 Mbps), Bi-directional Switching                                       |

| Figure 5 - 6,144 by 2,048 Channels Blocking Bi-directional Configuration                                    |

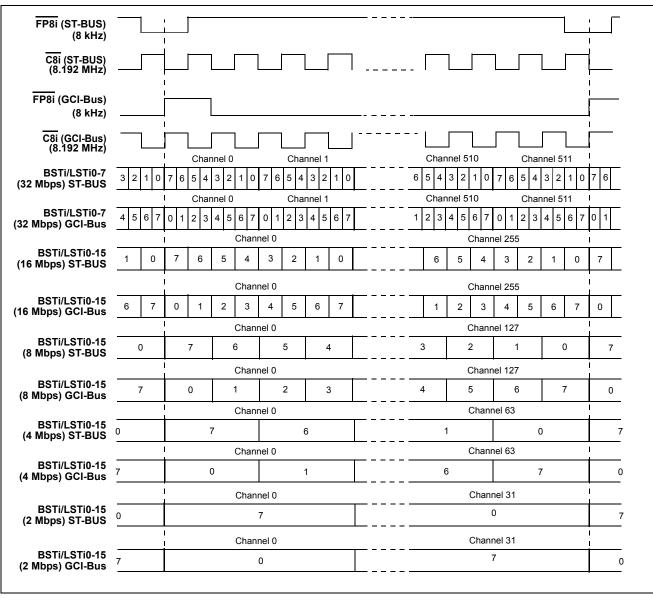

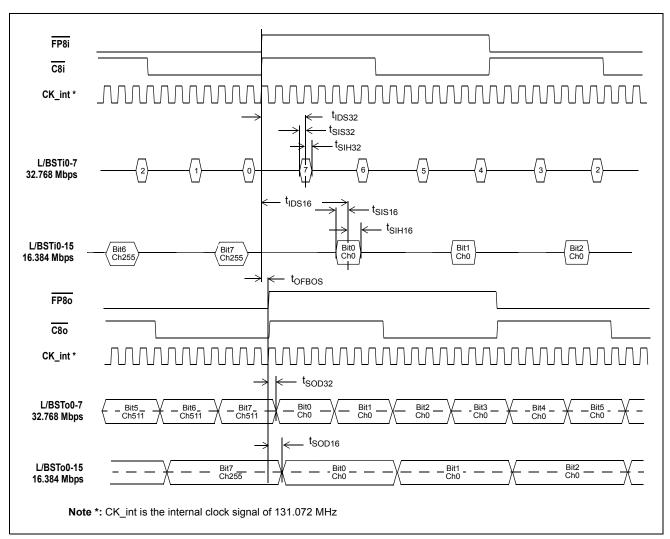

| Figure 6 - ST-BUS and GCI-Bus Input Timing Diagram for Different Data Rates                                 |

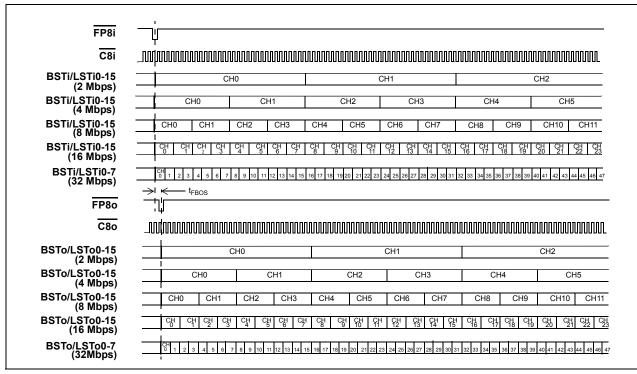

| Figure 7 - Input and Output (Generated) Frame Pulse Alignment for Different Data Rates                      |

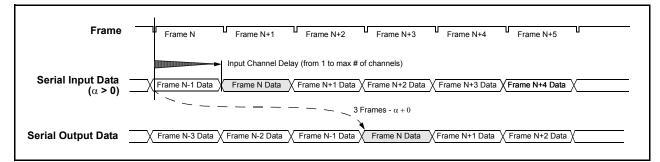

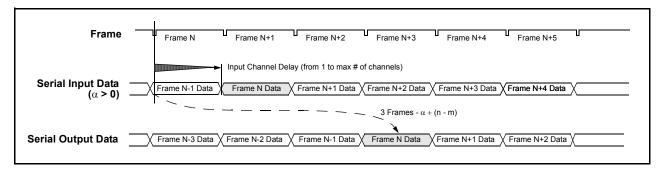

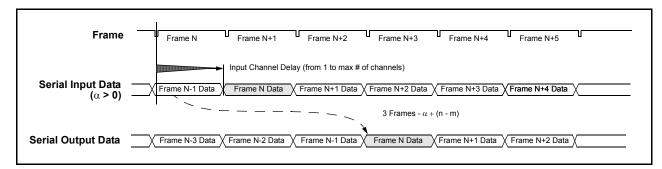

| Figure 8 - Backplane and Local Input Channel Delay Timing Diagram (assuming 8 Mbps operation) 27            |

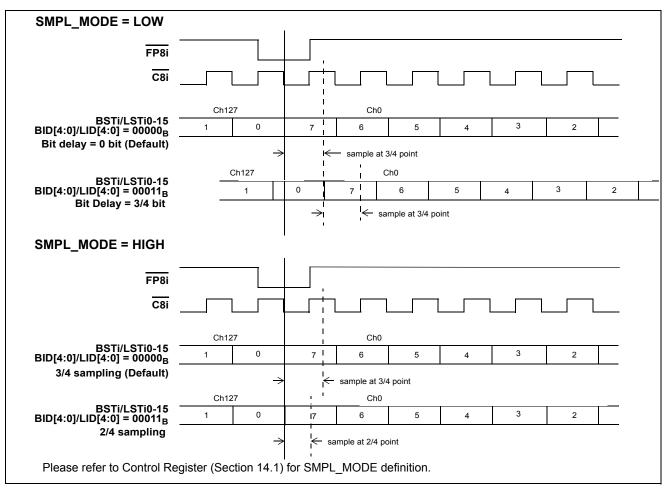

| Figure 9 - Backplane and Local Input Bit Delay Timing Diagram for Data Rate of 16 Mbps                      |

| Figure 10 - Backplane and Local Input Bit Delay or Sampling Point Selection Timing Diagram for Data Rate of |

| 8 Mbps                                                                                                      |

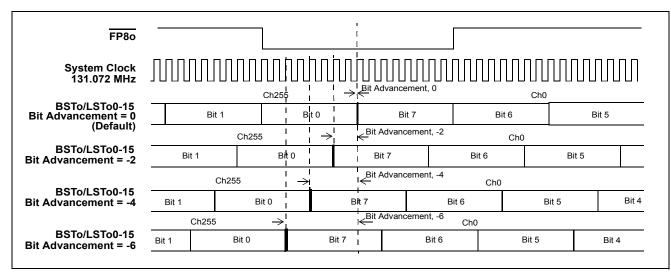

| Figure 11 - Local and Backplane Output Advancement Timing Diagram for Data Rate of 16 Mbps                  |

| Figure 12 - Local/Backplane Port External High-Impedance Control Bit Timing (Non-32 Mbps Mode)              |

| Figure 13 - Local and Backplane Port External High-Impedance Control Timing (32 Mbps Mode)                  |

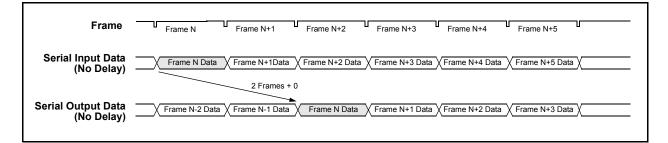

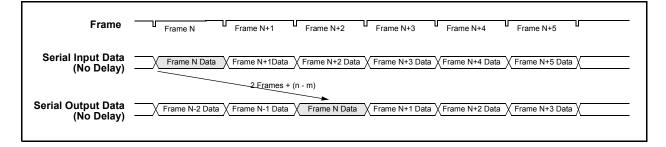

| Figure 14 - Data Throughput Delay with Input Channel Delay Disabled, Input Ch0 Switched to Output Ch040     |

| Figure 15 - Data Throughput Delay with Input Channel Delay Disabled, Input Ch0 Switched to Output Ch1340    |

| Figure 16 - Data Throughput Delay with Input Channel Delay Disabled, Input Ch13 Switched to Output Ch040    |

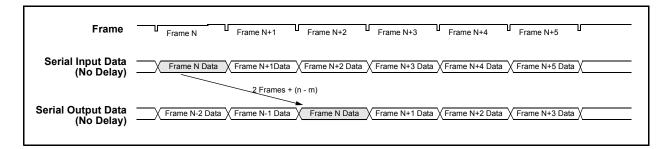

| Figure 17 - Data Throughput Delay with Input Channel Delay Enabled, Input Ch0 Switched to Output Ch0 41     |

| Figure 18 - Data Throughput Delay with Input Channel Delay Enabled, Input Ch0 Switched to Output Ch13 41    |

| Figure 19 - Data Throughput Delay with Input Channel Delay Enabled, Input Ch13 Switched to Output Ch0 41    |

| Figure 20 - Examples of BER Transmission Channels on a 16 Mbps Output Stream                                |

| Figure 21 - Hardware RESET De-assertion                                                                     |

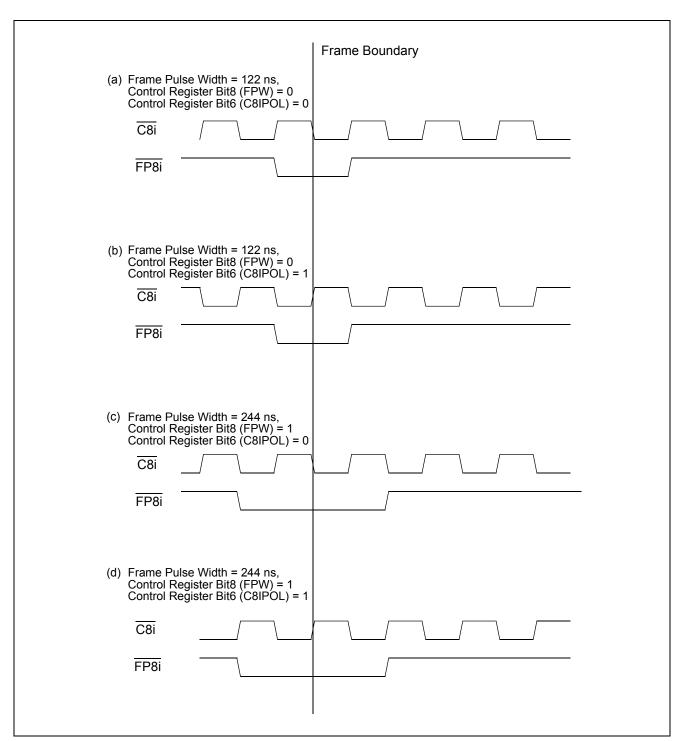

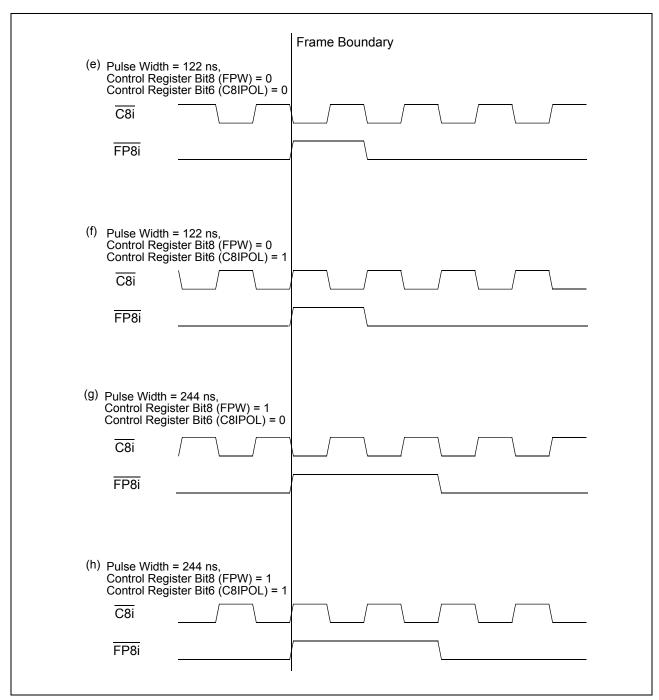

| Figure 22 - Frame Boundary Conditions, ST-BUS Operation                                                     |

| Figure 23 - Frame Boundary Conditions, GCI-Bus Operation                                                    |

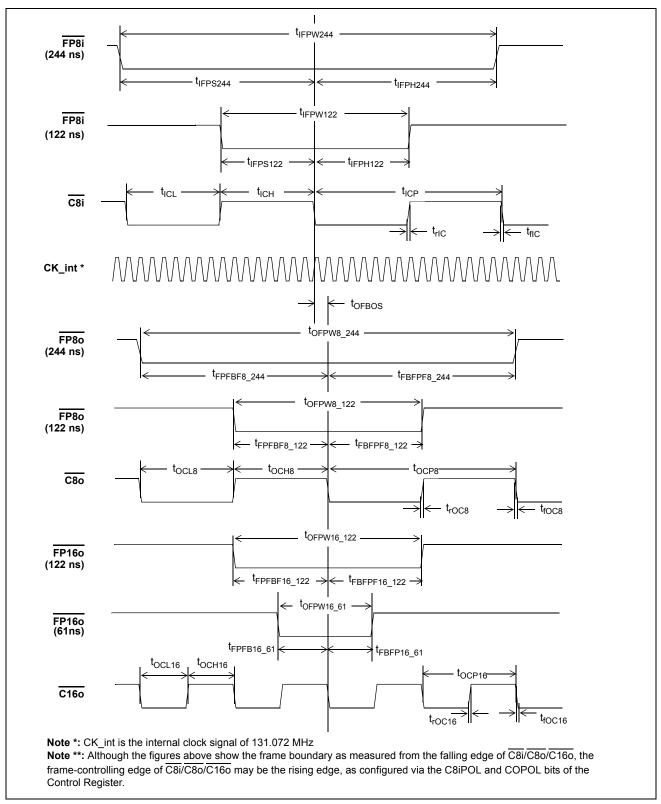

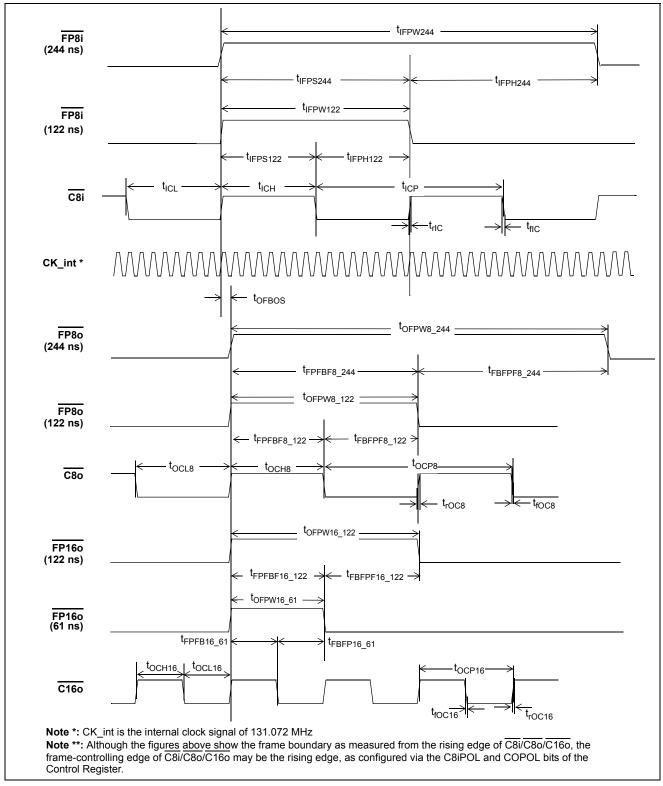

| Figure 24 - Input and Output Clock Timing Diagram for ST-BUS                                                |

| Figure 25 - Input and Output Clock Timing Diagram for GCI-Bus                                               |

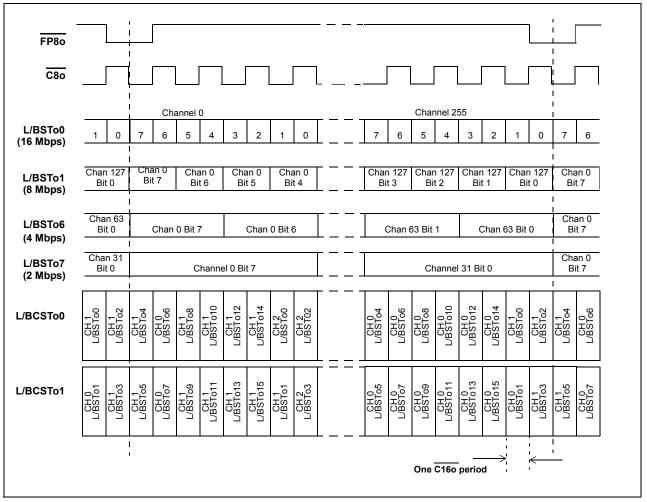

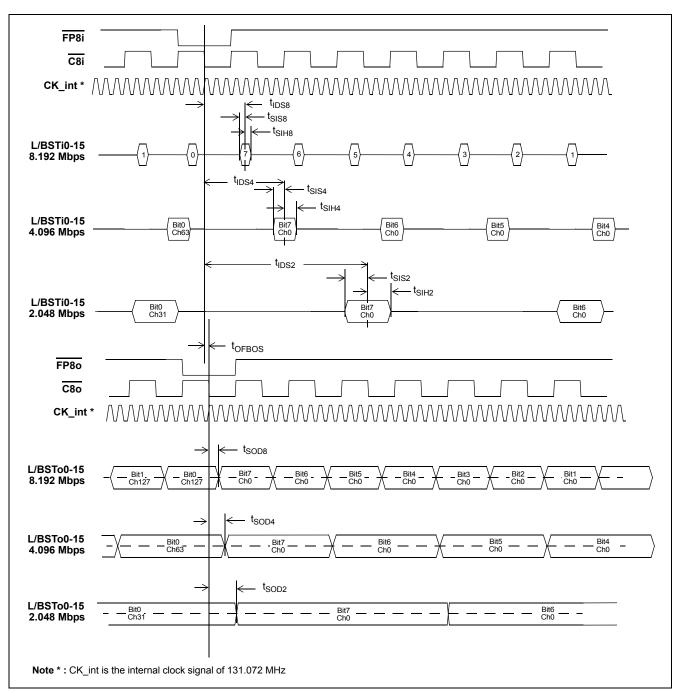

| Figure 26 - ST-BUS Local/Backplane Data Timing Diagram (8 Mbps, 4 Mbps, 2 Mbps)                             |

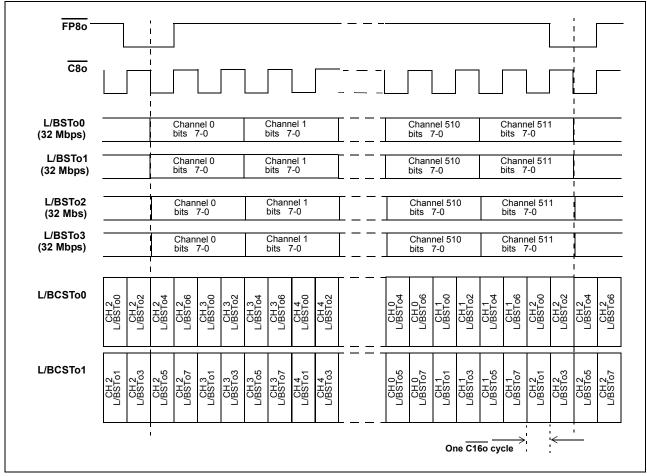

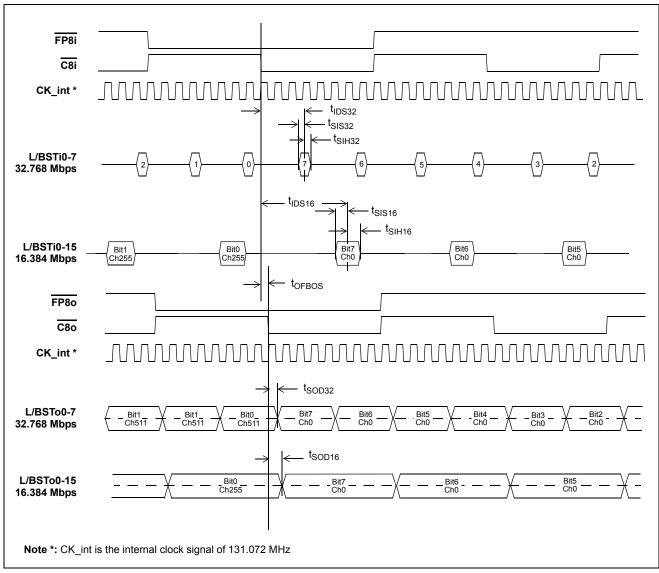

| Figure 27 - ST-BUS Local/Backplane Data Timing Diagram (32 Mbps, 16 Mbps)                                   |

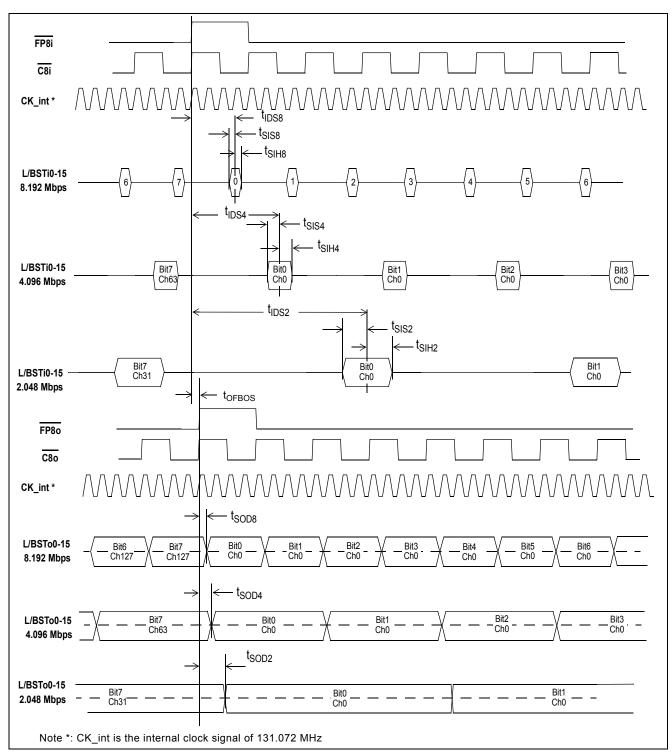

| Figure 28 - GCI-Bus Local/Backplane Data Timing Diagram (8 Mbps, 4 Mbps, 2 Mbps)                            |

| Figure 29 - GCI-Bus Local/Backplane Data Timing Diagram (32 Mbps, 16 Mbps)                                  |

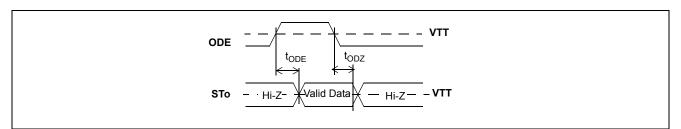

| Figure 30 - Serial Output and External Control    89                                                        |

| Figure 31 - Output Driver Enable (ODE)                                                                      |

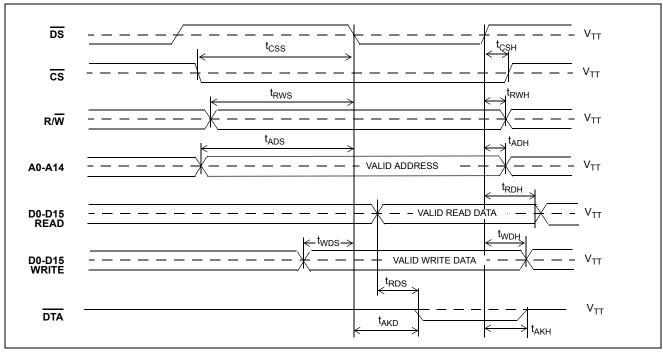

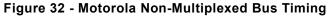

| Figure 32 - Motorola Non-Multiplexed Bus Timing                                                             |

| Figure 33 - JTAG Test Port Timing Diagram    92                                                             |

## List of Tables

| Table 1 - Per-stream Input and Output Data Rate Selection: Backplane and Local, Non-32 Mbps Mode and 32 Mbps Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 21 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Table 2 - Local and Backplane Output Enable Control Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| Table 3 - L/BCSTo Allocation of Channel Control Bits to Output Streams (Non-32 Mbps Mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Table 4 - L/BCSTo Allocation of Channel Control Bits to Output Streams (32 Mbps Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 36 |

| Table 5 - Variable Range for Input Streams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Table 6 - Variable Range for Output Streams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 39 |

| Table 7 - Data Throughput Delay    Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 39 |

| Table 8 - Local and Backplane Connection Memory Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 45 |

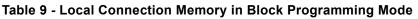

| Table 9 - Local Connection Memory in Block Programming Mode         Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 45 |

| Table 10 - Backplane Connection Memory in Block Programming Mode         Mathematical State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| Table 11 - Address Map for Data and Connection Memory Locations (A14 = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 48 |

| Table 12 - Local Data Memory (LDM) Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 48 |

| Table 13 - Backplane Data Memory (BDM) Bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 49 |

| Table 14 - LCM Bits for Non-32Mbps Source-to-Local Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 49 |

| Table 15 - LCM Bits for 32 Mbps Source-to-Local Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 50 |

| Table 16 - BCM Bits for Non-32Mbps Source-to-Backplane Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 51 |

| Table 17 - BCM Bits for 32 Mbps Source-to-Backplane Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 51 |

| Table 18 - Address Map for Registers (A14 = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 52 |

| Table 19 - Control Register Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 53 |

| Table 20 - Block Programming Register Bits    Image: Comparison of the second se | . 57 |

| Table 21 - Bit Error Rate Test Control Register (BERCR) Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 58 |

| Table 22 - Local Input Channel Delay Register (LCDRn) Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 59 |

| Table 23 - Local Input Channel Delay (LCD) Programming Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 60 |

| Table 24 - Local Input Bit Delay Register (LIDRn) Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Table 25 - Local Input Bit Delay and Sampling Point Programming Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 61 |

| Table 26 - Backplane Input Channel Delay Register (BCDRn) Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 63 |

| Table 27 - Backplane Input Channel Delay (BCD) Programming Table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| Table 28 - Backplane Input Bit Delay Register (BIDRn) Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Table 29 - Backplane Input Bit Delay and Sampling Point Programming Table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |