## **Wideband Operational Amplifier**

### **FEATURES**

Wide Bandwidth: 3 GHz High Slew Rate: 830 V/µs

Low Voltage Noise: 2.4 nV/√Hz

Single Supply: 5 V, 3 V **Quiescent Current: 18 mA**

### **APPLICATIONS**

- **Active Filter**

- **ADC Driver**

- **Ultrasound**

- Gamma Camera

- RF/Telecom

### **DESCRIPTION**

The THS4304 is a wideband, voltage-feedback operational amplifier designed for use in high-speed analog signal-processing chains operating with a single 5-V power supply. Developed in the BiCom3 silicon germanium process technology, the THS4304 offers best-in-class performance using a single 5-V supply as opposed to previous generations of operational amplifiers requiring ±5-V supplies.

The THS4304 is a traditional voltage-feedback topology that provides the following benefits: balanced inputs, low offset voltage and offset current, low offset drift, high common mode and power supply rejection ratio.

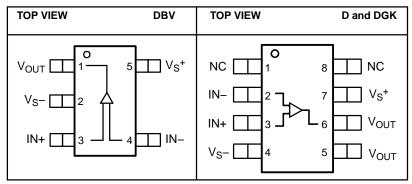

The THS4304 is offered in 8-pin MSOP package (DGK), the 8-pin SOIC package (D), and the space-saving 5-pin SOT-23 package (DBV).

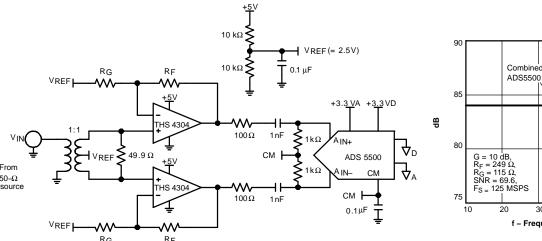

#### DIFFERENTIAL ADC DRIVE

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **PINOUT DRAWING**

NOTE: NC indicates there is no internal connection to these pins.

### **PACKAGING / ORDERING INFORMATION**

| PACKAGED DEVICES | PACKAGE TYPE | PACKAGE MARKINGS | TRANSPORT MEDIA,<br>QUANTITY |

|------------------|--------------|------------------|------------------------------|

| THS4304DBVT      | SOT-23-5     | AKW              | Tape and Reel, 250           |

| THS4304DBVR      | 301-23-3     | ANV              | Tape and Reel, 3000          |

| THS4304D         | SOIC-8       |                  | Rails, 75                    |

| THS4304DR        | 50IC-6       | _                | Tape and Reel, 2500          |

| THS4304DGK       | MSOP-8       | AKU              | Rails, 100                   |

| THS4304DGKR      | WISOF-6      | ANU              | Tape and Reel, 2500          |

## **DISSIPATION RATINGS**

| PACKAGE | θης    | $\theta_{JA}$         | POWER RATING <sup>(2)</sup> |                       |  |  |

|---------|--------|-----------------------|-----------------------------|-----------------------|--|--|

| PACKAGE | (°C/W) | (°C/W) <sup>(1)</sup> | T <sub>A</sub> ≤ 25°C       | T <sub>A</sub> = 85°C |  |  |

| DBV (5) | 55     | 255.4                 | 391 mW                      | 156 mW                |  |  |

| D (8)   | 38.3   | 97.5                  | 1.02 W                      | 410 mW                |  |  |

| DGK (8) | 71.5   | 180.8                 | 553 mW                      | 221 mW                |  |  |

<sup>(1)</sup> This data was taken using the JEDEC standard High-K test PCB.

<sup>(2)</sup> Power rating determined with a junction temperature of 125°C. This is the point where distortion starts to substantially increase. Thermal management of the final PCB should strive to keep the junction temperature at or below 125°C for best performance and long-term reliability.

## **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                    |                                                | UNIT            |

|------------------|--------------------|------------------------------------------------|-----------------|

| Vs               | Supply voltage     | +6.0 V                                         |                 |

| VI               | Input voltage      |                                                | ±V <sub>S</sub> |

| Io               | Output current     |                                                | 150 mA          |

| V <sub>ID</sub>  | Differential input | voltage                                        | ±2 V            |

|                  | Continuous powe    | See Dissipation Rating Table                   |                 |

| _                | Maximum junction   | n temperature, any condition <sup>(2)</sup>    | 150°C           |

| TJ               | Operating free-air | 125°C                                          |                 |

| T <sub>stg</sub> | Storage temperat   | rure range                                     | -65°C to 150°C  |

|                  | Lead temperature   | e: 1,6 mm (1/16 inch) from case for 10 seconds | 300°C           |

|                  |                    | НВМ                                            | 1600 V          |

|                  | ESD Ratings        | CDM                                            | 1000 V          |

|                  |                    | MM                                             | 100 V           |

<sup>(1)</sup> The absolute maximum ratings under any condition is limited by the constraints of the silicon process. Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

## RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                                                        |                    | MIN                   | MAX  | UNIT |

|--------------------------------------------------------|--------------------|-----------------------|------|------|

| Cumply voltage ()/ and )/                              | Dual supply        | ±1.35                 | ±2.5 | V    |

| Supply voltage, (V <sub>S+</sub> and V <sub>S-</sub> ) | Single supply      | 2.7                   | 5    | V    |

| Input common-mode voltage rang                         | V <sub>S</sub> 0.2 | V <sub>S+</sub> + 0.2 | ٧    |      |

<sup>(2)</sup> The maximum junction temperature for continuous operation is limited by package constraints. Operation above this temperature may result in reduced reliability and/or lifetime of the device.

## **ELECTRICAL CHARACTERISTICS**

Specifications: V  $_{S}$  = 5 V: R  $_{F}$  = 249  $\Omega,$  R  $_{L}$  = 100  $\Omega,$  and G = +2 unless otherwise noted

|                                                            |                                               | TYP                       | TYP OVER TEMPERATURE |               |                |                  |                    |             |                              |

|------------------------------------------------------------|-----------------------------------------------|---------------------------|----------------------|---------------|----------------|------------------|--------------------|-------------|------------------------------|

| PARAMETER                                                  | CON                                           | DITIONS                   | 25°C                 | 25°C          | 0°C to<br>70°C | –40°C to<br>85°C | UNITS              | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |

| AC PERFORMANCE                                             | •                                             |                           | •                    |               |                | •                |                    |             |                              |

|                                                            | G = +1, V <sub>O</sub> = 1                    | 00 mVpp                   | 3                    |               |                |                  | GHz                | Тур         | С                            |

| Conall Cianal Bandwidth                                    | $G = +2, V_O = 1$                             | 1                         |                      |               |                | GHz              | Тур                | С           |                              |

| Small-Signal Bandwidth                                     | $G = +5, V_O = 1$                             | 00 mVpp                   | 187                  |               |                |                  | MHz                | Тур         | С                            |

|                                                            | G = +10, V <sub>O</sub> =                     | 100 mVpp                  | 87                   |               |                |                  | MHz                | Тур         | С                            |

| Gain Bandwidth Product                                     | G >+10                                        |                           | 870                  |               |                |                  | MHz                | Тур         | С                            |

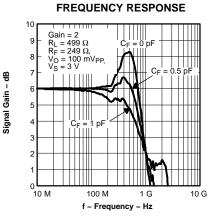

| 0.1-dB Flat Bandwidth                                      | $G= +2, V_O = 10$<br>$C_F = 0.5 pF$           | 00 mVpp,                  | 300                  |               |                |                  | MHz                | Тур         | С                            |

| Large-Signal Bandwidth                                     | $G = +2, V_O = 2$                             | V <sub>PP</sub>           | 240                  |               |                |                  | MHz                | Тур         | С                            |

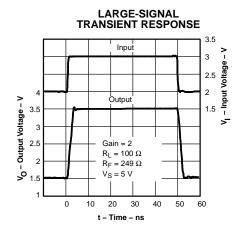

| Clay Data                                                  | G = +2, V <sub>O</sub> = 1                    | -V Step                   | 830                  |               |                |                  | V/μs               | Тур         | С                            |

| Slew Rate                                                  | $G = +2, V_O = 2$                             | -V Step                   | 790                  |               |                |                  | V/µs               | Тур         | С                            |

| Settling Time to 1%                                        | $G = -2, V_0 = 2$                             | -V Step                   | 4.5                  |               |                |                  | ns                 | Тур         | С                            |

| Settling Time to 0.1%                                      | $G = -2, V_O = 2$                             | -V Step                   | 7.5                  |               |                |                  | ns                 | Тур         | С                            |

| Settling Time to 0.01%                                     | $G = -2, V_O = 2$                             | -V Step                   | 35                   |               |                |                  | ns                 | Тур         | С                            |

| Rise / Fall Times                                          | $G = +2, V_O = 2$                             | -V Step                   | 2.5                  |               |                |                  | ns                 | Тур         | С                            |

| Harmonic Distortion                                        |                                               |                           |                      |               |                |                  |                    |             |                              |

| Second Harmonic Distortion                                 |                                               | R <sub>L</sub> = 100 Ω    | -84                  |               |                |                  | dBc                | Тур         | С                            |

|                                                            | G = +2,                                       | $R_L = 1 k\Omega$         | -95                  |               |                |                  | dBc                | Тур         | С                            |

| Third Harmonic Distortion                                  | $V_O = 2 V_{PP},$<br>f = 10 MHz               | $R_L = 100 \Omega$        | -100                 |               |                |                  | dBc                | Тур         | С                            |

|                                                            |                                               | $R_L = 1 \text{ k}\Omega$ | -100                 |               |                |                  | dBc                | Тур         | С                            |

| Third-Order Intermodulation Distortion (IMD <sub>3</sub> ) | G = +2, V <sub>O</sub> = 2-<br>200-kHz tone s |                           | -84                  |               |                |                  | dBc                | Тур         | С                            |

| Third-Order Output Intercept (OIP <sub>3</sub> )           | f = 20 MHz                                    | ърасіну,                  | 48                   |               |                |                  | dBm                | Тур         | С                            |

| Noise Figure                                               | G = +2, f = 1 G                               | 6Hz                       | 15                   |               |                |                  | dB                 | Тур         | С                            |

| Input Voltage Noise                                        | f = 1 MHz                                     |                           | 2.4                  |               |                |                  | nV/√ <del>Hz</del> | Тур         | С                            |

| Input Current Noise                                        | f = 1 MHz                                     |                           | 2.1                  |               |                |                  | pA/√ <del>Hz</del> | Тур         | С                            |

| DC PERFORMANCE                                             |                                               |                           |                      |               |                | •                |                    |             |                              |

| Open-Loop Voltage Gain (A <sub>OL</sub> )                  | $V_0 = \pm 0.8 \text{ V}, \text{ V}$          | / <sub>CM</sub> = 2.5 V   | 65                   | 54            | 50             | 50               | dB                 | Min         | Α                            |

| Input Offset Voltage                                       |                                               |                           | 0.5                  | 4             | 5              | 5                | mV                 | Max         | Α                            |

| Input Offset Voltage Drift                                 |                                               |                           |                      |               | 5              | 5                | μV/°C              | Тур         | В                            |

| Input Bias Current                                         | ],, 25,,                                      |                           | 7                    | 12            | 18             | 18               | μΑ                 | Max         | Α                            |

| Input Bias Current Drift                                   | V <sub>CM</sub> = 2.5 V                       |                           |                      |               | 50             | 50               | nA/°C              | Тур         | В                            |

| Input Offset Current                                       |                                               |                           | 0.5                  | 1             | 1.2            | 1.2              | μΑ                 | Max         | Α                            |

| Input Offset Current Drift                                 |                                               |                           |                      | 10            | 10             | nA/°C            | Тур                | В           |                              |

| INPUT CHARACTERISTICS                                      |                                               |                           |                      |               |                |                  |                    |             |                              |

| Common-Mode Input Range                                    |                                               |                           | -0.2 to 5.2          | 0.2 to<br>4.8 | 0.4 to<br>4.6  | 0.4 to<br>4.6    | V                  | Min         | А                            |

| Common-Mode Rejection<br>Ratio                             | $V_0 = \pm 0.2 \text{ V, } $                  | / <sub>CM</sub> = 2.5 V   | 95                   | 80            | 73             | 73               | dB                 | Min         | А                            |

| Input Resistance                                           | Food innut ==f                                | oronood to CND            | 100                  |               |                |                  | kΩ                 | Тур         | С                            |

| Input Capacitance                                          | Zach input, ref                               | erenced to GND            | 1.5                  |               |                |                  | pF                 | Тур         | С                            |

<sup>(1)</sup> Test levels: (A) 100% tested at 25°C. Over temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

## **ELECTRICAL CHARACTERISTICS (continued)**

Specifications: V  $_{\text{S}}$  = 5 V: R  $_{\text{F}}$  = 249  $\Omega,~R_{\text{L}}$  = 100  $\Omega,$  and G = +2 unless otherwise noted

|                                |                                                                  | TYP           |               | OVER 1         | EMPERAT          | URE   |             | TEST                         |

|--------------------------------|------------------------------------------------------------------|---------------|---------------|----------------|------------------|-------|-------------|------------------------------|

| PARAMETER                      | CONDITIONS                                                       | 25°C          | 25°C          | 0°C to<br>70°C | –40°C to<br>85°C | UNITS | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |

| OUTPUT CHARACTERISTICS         | <b>,</b>                                                         |               |               |                |                  |       |             |                              |

| Output Voltage Swing           | R <sub>L</sub> = 100 Ω                                           | 1.1 to<br>3.9 | 1.2 to<br>3.8 | 1.3 to<br>3.7  | 1.3 to<br>3.7    | V     | Min         | Α                            |

| Output Voltage Swing           | $R_L = 1 \text{ k}\Omega$                                        | 1 to 4        | 1.1 to<br>3.9 | 1.2 to<br>3.8  | 1.2 to<br>3.8    | V     | IVIIII      | A                            |

| Output Current (Sourcing)      | $R_L = 10 \Omega$                                                | 140           | 100           | 57             | 57               | mA    | Min         | Α                            |

| Output Current (Sinking)       | $R_L = 10 \Omega$                                                | 92            | 65            | 40             | 40               | mA    | Min         | Α                            |

| Output Impedance               | f = 100 kHz                                                      | 0.016         |               |                |                  | Ω     | Тур         | А                            |

| POWER SUPPLY                   |                                                                  |               |               |                |                  |       |             |                              |

| Maximum Operating Voltage      |                                                                  | 5             | 5.5           | 5.5            | 5.5              | V     | Max         | А                            |

| Minimum Operating Voltage      |                                                                  | 5             | 2.7           | 2.7            | 2.7              | , v   | Min         |                              |

| Maximum Quiescent Current      |                                                                  | 18            | 18.9          | 19.4           | 19.4             | mA    | Max         | А                            |

| Minimum Quiescent Current      |                                                                  | 18            | 17.5          | 16.6           | 16.6             | mA    | Min         | А                            |

| Power Supply Rejection (+PSRR) | $V_{S+} = 5.5 \text{ V to } 4.5 \text{ V}, V_{S-} = 0 \text{ V}$ | 80            | 73            | 66             | 66               | dB    | Min         | Α                            |

| Power Supply Rejection (-PSRR) | $V_{S+} = 5 \text{ V}, V_{S-} = -0.5 \text{ V} \text{ to } +0.5$ | 60            | 57            | 54             | 54               | dB    | Min         | Α                            |

## **ELECTRICAL CHARACTERISTICS**

Specifications: V  $_{S}$  = 3 V: R  $_{F}$  = 249  $\Omega,~R_{L}$  = 499  $\Omega,$  and G = +2 unless otherwise noted

|                                           |                                     |                                   |                |               | OVER           | TEMPE               | RATURE             |             |                              |

|-------------------------------------------|-------------------------------------|-----------------------------------|----------------|---------------|----------------|---------------------|--------------------|-------------|------------------------------|

| PARAMETER                                 | COND                                | ITIONS                            | 25°C           | 25°C          | 0°C to<br>70°C | -40°C<br>to<br>85°C | UNITS              | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |

| AC PERFORMANCE                            |                                     |                                   |                |               |                |                     |                    |             |                              |

|                                           | $G = +1, V_O = 100$                 | ) mVpp                            | 3              |               |                |                     | GHz                | Тур         | С                            |

| Small-Signal Bandwidth                    | $G = +2, V_O = 100$                 | G = +2, V <sub>O</sub> = 100 mVpp |                |               |                |                     | MHz                | Тур         | С                            |

| Smail-Signal Bandwidth                    | $G = +5, V_O = 100$                 | ) mVpp                            | 190            |               |                |                     | MHz                | Тур         | С                            |

|                                           | $G = +10, V_O = 10$                 | 00 mVpp                           | 83             |               |                |                     | MHz                | Тур         | С                            |

| Gain Bandwidth Product                    | G >+10                              |                                   | 830            |               |                |                     | MHz                | Тур         | С                            |

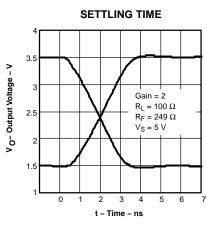

| Large-Signal Bandwidth                    | G = +2, V <sub>O</sub> = 1 V        | PP                                | 450            |               |                |                     | MHz                | Тур         | С                            |

| Slew Rate                                 | $G = +2, V_O = 1-V$                 | Step                              | 750            |               |                |                     | V/μs               | Тур         | С                            |

| Siew Rate                                 | $G = +2, V_O = 1-V$                 | Step                              | 675            |               |                |                     | V/μs               | Тур         | С                            |

| Settling Time to 1%                       | $G = -2$ , $V_O = 0.5$              | -V Step                           | 4.5            |               |                |                     | ns                 | Тур         | С                            |

| Settling Time to 0.1%                     | $G = -2$ , $V_O = 0.5$              | -V Step                           | 20             |               |                |                     | ns                 | Тур         | С                            |

| Rise / Fall Times                         | $G = +2, V_O = 0.5$                 | -V Step                           | 1.5            |               |                |                     | ns                 | Тур         | С                            |

| Harmonic Distortion                       |                                     |                                   |                |               |                |                     |                    |             |                              |

| Second Harmonic Distortion                | G = +2,                             |                                   | -92            |               |                |                     | dBc                | Тур         | С                            |

| Third Harmonic Distortion                 | $V_{O} = 0.5 V_{PP},$<br>f = 10 MHz | $R_L = 499 \Omega$                | -91            |               |                |                     | dBc                | Тур         | С                            |

| Noise Figure                              | G = +2, f = 1 GH                    | Z                                 | 15             |               |                |                     | dB                 | Тур         | С                            |

| Input Voltage Noise                       | f = 1 MHz                           |                                   | 2.4            |               |                |                     | nV/√ <del>Hz</del> | Тур         | С                            |

| Input Current Noise                       | f = 1 MHz                           |                                   | 2.1            |               |                |                     | pA/√ <del>Hz</del> | Тур         | С                            |

| DC PERFORMANCE                            |                                     |                                   |                |               |                |                     |                    |             |                              |

| Open-Loop Voltage Gain (A <sub>OL</sub> ) | $V_{O} = \pm 0.5 \text{ V}, V_{CI}$ | <sub>M</sub> = 1.5 V              | 49             | 44            |                |                     | dB                 | Min         | Α                            |

| Input Offset Voltage                      |                                     |                                   | 2              | 4             | 5              | 5                   | mV                 | Max         | Α                            |

| Input Offset Voltage Drift                |                                     |                                   |                |               | 5              | 5                   | μV/°C              | Тур         | В                            |

| Input Bias Current                        | 151/                                |                                   | 7              | 12            | 18             | 18                  | μΑ                 | Max         | Α                            |

| Input Bias Current Drift                  | $V_{CM} = 1.5 \text{ V}$            |                                   |                |               | 50             | 50                  | nA/°C              | Тур         | В                            |

| Input Offset Current                      |                                     |                                   | 0.4            | 1             | 1.2            | 1.2                 | μA                 | Max         | А                            |

| Input Offset Current Drift                |                                     |                                   |                | 10            | 10             | nA/°C               | Тур                | В           |                              |

| INPUT CHARACTERISTICS                     |                                     |                                   |                |               |                |                     |                    |             |                              |

| Common-Mode Input Range                   |                                     |                                   | -0.2<br>to 3.2 | 0.2 to<br>2.8 | 0.4 to<br>2.6  | 0.4 to<br>2.6       | V                  | Min         | Α                            |

| Common-Mode Rejection Ratio               | $V_0 = \pm 0.09 \text{ V}, V_0$     | <sub>CM</sub> = 1.5 V             | 92             | 80            | 70             | 70                  | dB                 | Min         | Α                            |

| Input Resistance                          | Food innut refer                    | anood to CND                      | 100            |               |                |                     | kΩ                 | Тур         | С                            |

| Input Capacitance                         | Each input, refere                  | enced to GND                      | 1.5            |               |                |                     | pF                 | Тур         | С                            |

<sup>(1)</sup> Test levels: (A) 100% tested at 25°C. Over temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

## **ELECTRICAL CHARACTERISTICS (continued)**

Specifications: V  $_{\text{S}}$  = 3 V: R  $_{\text{F}}$  = 249  $\Omega,$  R  $_{\text{L}}$  = 499  $\Omega,$  and G = +2 unless otherwise noted

|                                |                                                                    | TYP           |               | OVER           | TEMPE               | RATURE |             |                              |

|--------------------------------|--------------------------------------------------------------------|---------------|---------------|----------------|---------------------|--------|-------------|------------------------------|

| PARAMETER                      | CONDITIONS                                                         | 25°C          | 25°C          | 0°C to<br>70°C | -40°C<br>to<br>85°C | UNITS  | MIN/<br>MAX | TEST<br>LEVEL <sup>(1)</sup> |

| OUTPUT CHARACTERISTIC          |                                                                    |               |               |                |                     |        |             |                              |

| Output Voltage Swing           | R <sub>L</sub> = 100 Ω                                             | 1.1 to<br>1.9 | 1.2 to<br>1.8 | 1.3 to<br>1.7  | 1.3 to<br>1.7       | V      | Min         | Α                            |

| Output Voltage Swing           | $R_L = 1 \text{ k}\Omega$                                          | 1 to 2        | 1.1 to<br>1.9 | 1.2 to<br>1.8  | 1.2 to<br>1.8       | V      |             | A                            |

| Output Current (Sourcing)      | $R_L = 10 \Omega$                                                  | 57            | 50            | 40             | 40                  | mA     | Min         | Α                            |

| Output Current (Sinking)       | $R_L = 10 \Omega$                                                  | 57            | 45            | 35             | 35                  | mA     | Min         | Α                            |

| Output Impedance               | f = 100 kHz                                                        | 0.016         |               |                |                     | Ω      | Тур         | Α                            |

| POWER SUPPLY                   |                                                                    |               |               |                |                     |        |             |                              |

| Maximum Operating Voltage      |                                                                    | 3             | 5.5           | 5.5            | 5.5                 | V      | Max         | Α                            |

| Minimum Operating Voltage      |                                                                    | 3             | 2.7           | 2.7            | 2.7                 | V      | Min         | ^                            |

| Maximum Quiescent Current      |                                                                    | 17.2          | 17.9          | 18.4           | 18.4                | mA     | Max         | Α                            |

| Minimum Quiescent Current      |                                                                    | 17.2          | 16.5          | 15.6           | 15.6                | mA     | Min         | Α                            |

| Power Supply Rejection (+PSRR) | $V_{S+} = 3.3 \text{ V to } 2.7 \text{ V}, V_{S-} = 0 \text{ V}$   | 80            | 60            | 54             | 54                  | dB     | Min         | Α                            |

| Power Supply Rejection (-PSRR) | $V_{S+} = 5 \text{ V}, V_{S-} = -0.5 \text{ V to } +0.5 \text{ V}$ | 60            | 55            | 52             | 52                  | dB     | Min         | А                            |

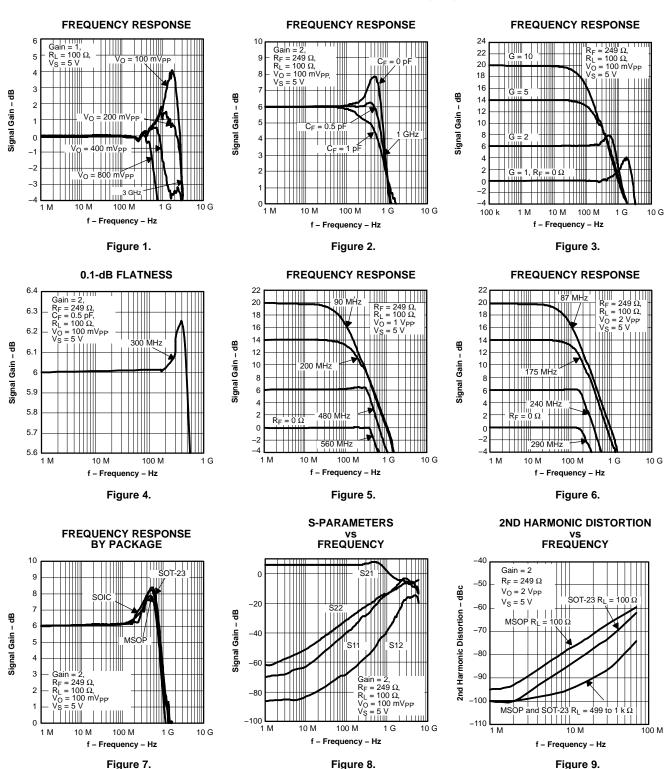

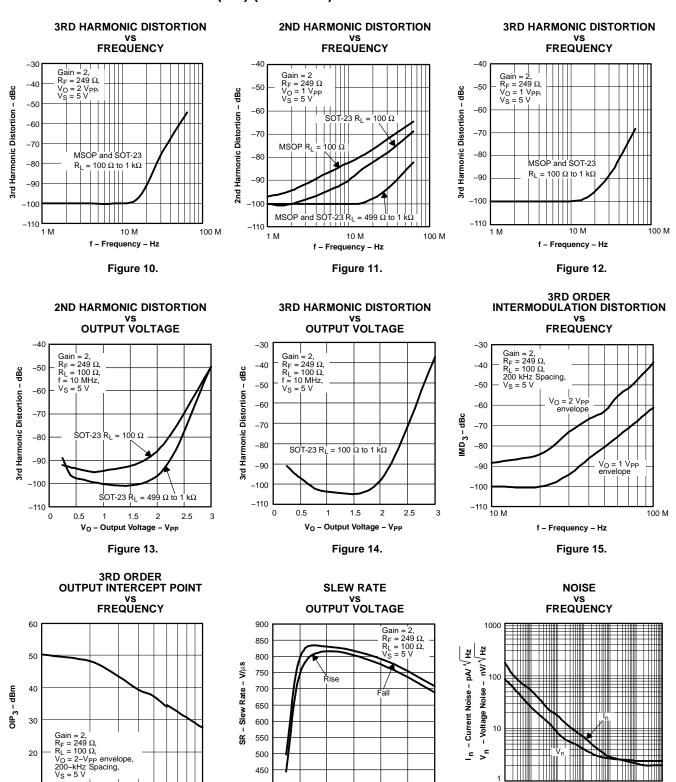

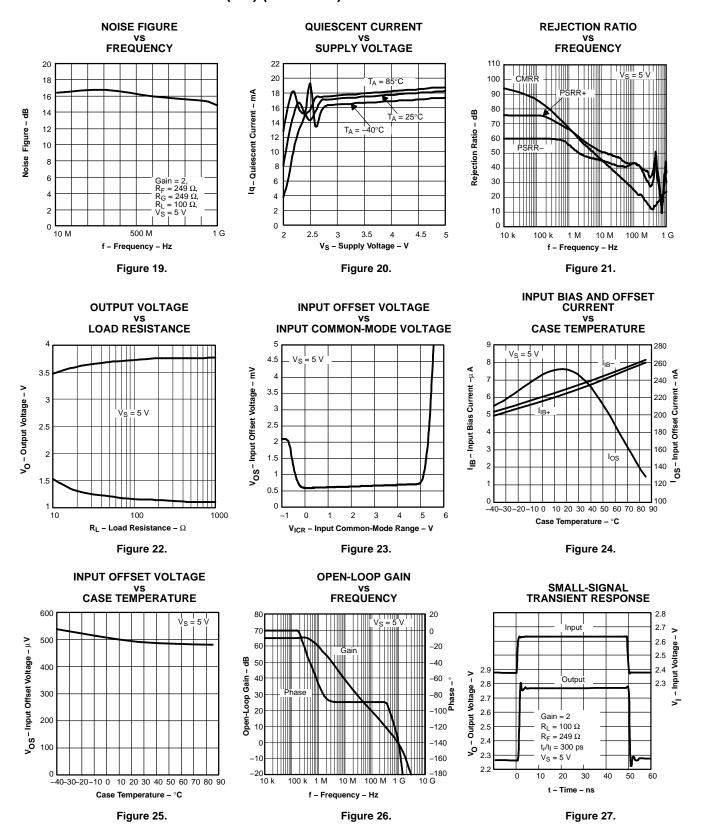

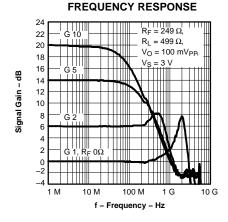

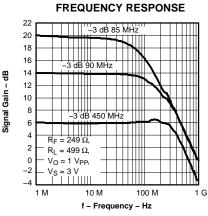

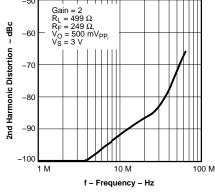

## **TYPICAL CHARACTERISTICS**

## **Table of Graphs**

|                                |                                      |                              | FIGURE    |

|--------------------------------|--------------------------------------|------------------------------|-----------|

| 5 V                            |                                      |                              |           |

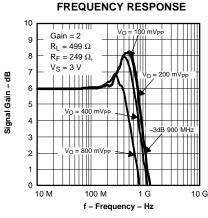

|                                | Frequency response                   |                              | 1–3, 5, 6 |

|                                | 0.1-dB Flatness                      |                              | 4         |

|                                | Frequency response by package        |                              | 7         |

|                                | S-Parameters                         | vs Frequency                 | 8         |

|                                | 2nd Harmonic distortion              | vs Frequency                 | 9, 11     |

|                                | 3rd Harmonic distortion              | vs Frequency                 | 10, 12    |

|                                | 2nd Harmonic distortion              | vs Output voltage            | 13        |

|                                | 3rd Harmonic distortion              | vs Output voltage            | 14        |

| IMD <sub>3</sub>               | 3rd Order intermodulation distortion | vs Frequency                 | 15        |

| OIP <sub>3</sub>               | 3rd Order output intercept point     | vs Frequency                 | 16        |

| SR                             | Slew rate                            | vs Output voltage            | 17        |

| V <sub>n</sub> /I <sub>n</sub> | Noise                                | vs Frequency                 | 18        |

|                                | Noise figure                         | vs Frequency                 | 19        |

| I <sub>q</sub>                 | Quiescent current                    | vs Supply voltage            | 20        |

|                                | Rejection ratio                      | vs Frequency                 | 21        |

| Vo                             | Output voltage                       | vs Load resistance           | 22        |

| Vos                            | Input offset voltage                 | vs Input common-mode voltage | 23        |

| I <sub>IB</sub>                | Input bias and offset current        | vs Case temperature          | 24        |

| Vos                            | Input offset voltage                 | vs Case temperature          | 25        |

|                                | Open-loop gain                       | vs Frequency                 | 26        |

| Vo                             | Small-signal transient response      |                              | 27        |

| Vo                             | Large-signal transient response      |                              | 28        |

| Vo                             | Settling time                        |                              | 29        |

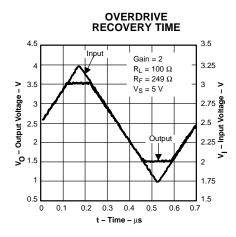

| Vo                             | Overdrive recovery time              |                              | 30        |

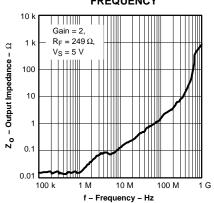

| Z <sub>O</sub>                 | Output impedance                     | vs Frequency                 | 31        |

| 3 V                            |                                      |                              |           |

|                                | Frequency response                   |                              | 32–35     |

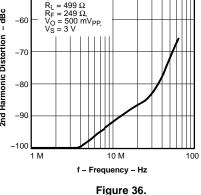

|                                | 2nd Harmonic distortion              | vs Frequency                 | 36        |

|                                | 3rd Harmonic distortion              | vs Frequency                 | 37        |

|                                | Harmonic Distortion                  | vs Output voltage            | 38        |

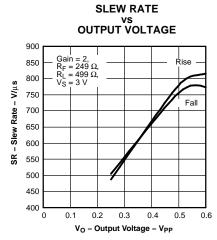

| SR                             | Slew rate                            | vs Output voltage            | 39        |

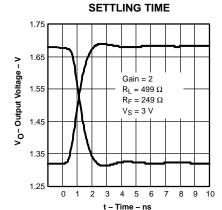

| V <sub>O</sub>                 | Settling time                        |                              | 40        |

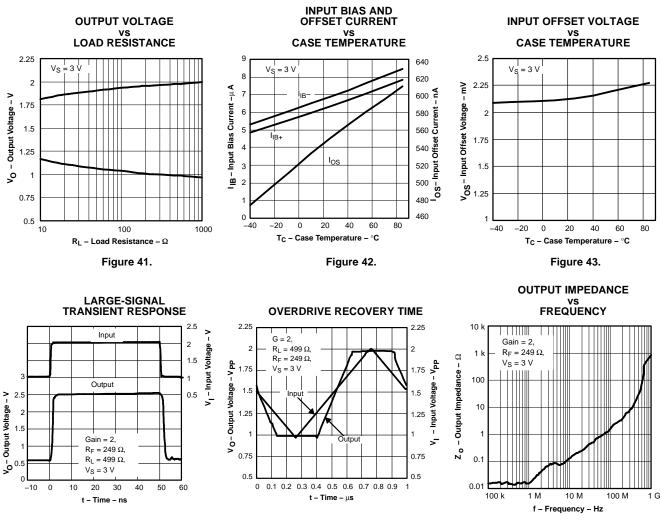

| V <sub>O</sub>                 | Output voltage                       | vs Load resistance           | 41        |

| I <sub>IB</sub>                | Input bias and offset current        | vs Case temperature          | 42        |

| Vos                            | Input offset voltage                 | vs Case temperature          | 43        |

| Vo                             | Large-signal transient response      |                              | 44        |

| V <sub>O</sub>                 | Overdrive recovery time              |                              | 45        |

| Z <sub>O</sub>                 | Output impedance                     | vs Frequency                 | 46        |

## **TYPICAL CHARACTERISTICS (5 V)**

### TYPICAL CHARACTERISTICS (5 V) (continued)

Figure 16.

f - Frequency - Hz

V<sub>O</sub> – Output Voltage –V<sub>PP</sub>

Figure 17.

1.5

2.5

400

0.5

\_ 100 M

Figure 18.

10 k 100 k 1 M 10 M

f - Frequency - Hz

10 100

10

10 M

## TYPICAL CHARACTERISTICS (5 V) (continued)

## TYPICAL CHARACTERISTICS (5 V) (continued)

Figure 28.

Figure 29.

Figure 30.

#### OUTPUT IMPEDANCE vs FREQUENCY

Figure 31.

## **TYPICAL CHARACTERISTICS (3 V)**

Figure 32.

Figure 33.

2ND HARMONIC DISTORTION

vs FREQUENCY

Figure 34. **3RD HARMONIC DISTORTION**

vs FREQUENCY

$\begin{aligned} & \text{Gain} = 2 \\ & \text{R}_{\text{L}} = 499 \ \Omega \\ & \text{R}_{\text{F}} = 249 \ \Omega, \\ & \text{V}_{\text{O}} = 500 \ \text{mV}_{\text{PP}}, \\ & \text{V}_{\text{S}} = 3 \ \text{V} \end{aligned}$ 3rd Harmonic Distortion - dBc -60 -70 -80 -90 -100 1 M 10 M 100 M f - Frequency - Hz

Figure 37.

HARMONIC DISTORTION VS OUTPUT VOLTAGE

Figure 40.

-40  $\begin{aligned} &\text{Gain} = 2 \\ &\text{R}_{L} = 499 \ \Omega \\ &\text{R}_{F} = 249 \ \Omega, \\ &\text{f} = 10 \ \text{MHz}, \\ &\text{V}_{S} = 3 \ \text{V} \end{aligned}$ -50 Harmonic Distortion – dBc -60 -70 -80 -90 -100 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 V<sub>O</sub> - Output Voltage - V<sub>PP</sub>

Figure 38.

Figure 39.

## TYPICAL CHARACTERISTICS (3 V) (continued)

Figure 44. Figure 45. Figure 46.

### **APPLICATION INFORMATION**

For many years, high-performance analog design has required the generation of split power supply voltages, like  $\pm 15$  V,  $\pm 8$  V, and more recently  $\pm 5$  V, in order to realize the full performance of the amplifiers available. Modern trends in high-performance analog are moving towards single-supply operation at 5 V, 3 V, and lower. This reduces power supply cost due to less voltages being generated and conserves energy in low power applications. It can also take a toll on available dynamic range, a valuable commodity in analog design, if the available voltage swing of the signal must also be reduced.

Two key figures of merit for dynamic range are signal-to-noise ratio (SNR) and spurious free dynamic range (SFDR).

SNR is simply the signal level divided by the noise:

$$SNR = \frac{Signal}{Noise}$$

and SFDR is the signal level divided by the highest spur:

$$SFDR = \frac{Signal}{Spur}$$

In an operational amplifier, reduced supply voltage typically results in reduced signal levels due to lower voltage available to operate the transistors within the amplifier. When noise and distortion remain constant, the result is a commensurate reduction in SNR and SFDR. To regain dynamic range, the process and the architecture used to make the operational amplifier must have superior noise and distortion performance with lower power supply overhead required for proper transistor operation.

The THS4304 BiCom3 operational amplifier is just such a device. It is able to provide 2-Vpp signal swing at its output on a single 5-V supply with noise and distortion performance similar to the best 10-V operational amplifiers on the market today

### **GENERAL APPLICATION**

The THS4304 is a traditional voltage-feedback topology with wideband performance up to 3 GHz at unity gain. Care must be taken to ensure that parasitic elements do not erode the phase margin.

Capacitance at the output and inverting input, and resistance and inductance in the feedback path, can cause problems.

To reduce parasitic capacitance, the ground plane should be removed from under the part.

To reduce inductance in the feedback, the circuit traces should be kept as short and direct as possible. For best performance in non-inverting unity gain (G=+1V/V), it is recommended to use a wide trace directly between the output and inverting input.

For a gain of +2V/V, it is recommended to use a 249- $\Omega$  feedback resistor. With good layout, this should keep the frequency response peaking to around 2 dB. This resistance is high enough to not load the output excessively, and the part is capable of driving 100- $\Omega$  load with good performance. Higher-value resistors can be used, with more peaking. For example, 499  $\Omega$  gives about 5 dB of peaking, and gives slightly better distortion performance with 100- $\Omega$  load. Lower value feedback resistors can also be used to reduce peaking, but degrades the distortion performance with heavy loads.

Power supply bypass capacitors are required for proper operation. The most critical are 0.1-µF ceramic capacitors; these should be placed as close to the part as possible. Larger bulk capacitors can be shared with other components in the same area as the operational amplifier.

### HARMONIC DISTORTION

For best second harmonic (HD2), it is important to use a single-point ground between the power supply bypass capacitors when using a split supply. It is also recommended to use a single ground or reference point for input termination and gain-setting resistors (R8 and R11 in the non-inverting circuit). It is recommended to follow the EVM layout closely in your application.

## **APPLICATION INFORMATION (continued)**

## **SOT-23 versus MSOP**

With light loading of  $500-\Omega$  and higher resistance, the THS4304 shows HD2 that is not dependant of package. With heavy output loading of  $100~\Omega$ , the THS4304 in SOT-23 package shows about 6 dB better HD2 performance versus the MSOP package.

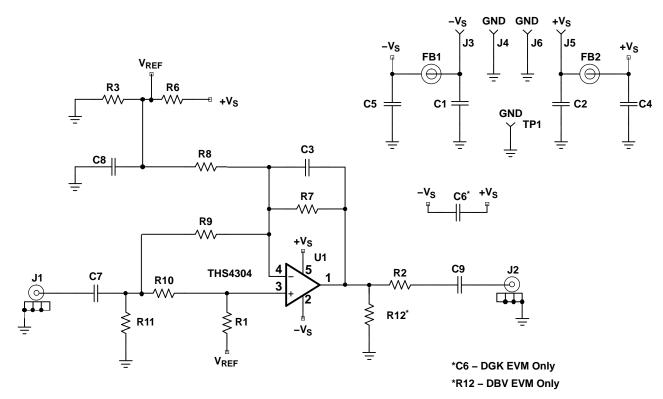

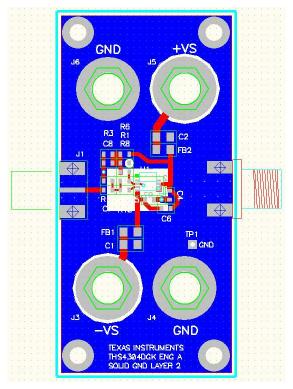

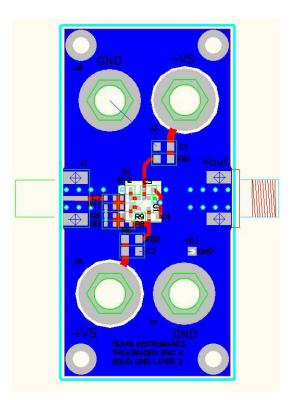

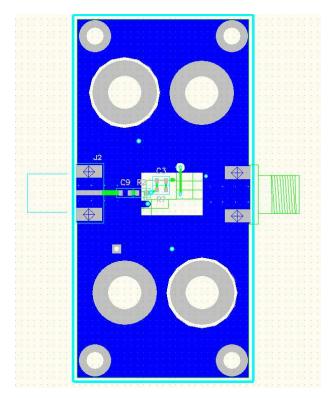

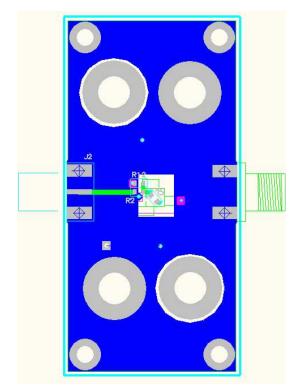

### **EVALUATION MODULES**

The THS4304 has two evaluation modules (EVMs) available. One is for the MSOP (DGK) package and the other for the SOT-23 (DBV) package. These provide a convenient platform for evaluating the performance of the part and building various different circuits. The full schematics, board layout, and bill of materials (as supplied) for the boards are shown in the following illustrations.

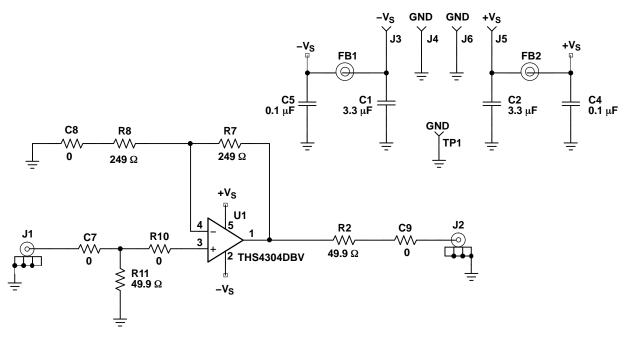

Figure 47. EVM Full Schematic

## **APPLICATION INFORMATION (continued)**

## **EVM BILL OF MATERIALS**

|      |                                                 |             | THS430                                | 04 EVM <sup>(1)</sup> |                                                    |                              |

|------|-------------------------------------------------|-------------|---------------------------------------|-----------------------|----------------------------------------------------|------------------------------|

| Item | Description                                     | SMD<br>Size | Reference<br>Designator               | PCB<br>Quantity       | Manufacturer's<br>Part Number                      | Distributor's<br>Part Number |

| 1    | Bead, ferrite, 3-A, 80-Ω                        | 1206        | FB1, FB2                              | 2                     | (STEWARD)<br>HI1206N800R-00                        | (DIGI-KEY)<br>240-1010-1-ND  |

| 2    | Capacitor, 3.3-µF, Ceramic                      | 1206        | C1, C2                                | 2                     | (AVX) 1206YG335ZAT2A                               | (GARRETT)<br>1206YG335ZAT2A  |

| 3    | Capacitor, 0.1-μF, Ceramic                      | 0603        | C4, C5                                | 2                     | (AVX) 0603YC104KAT2A                               | (GARRETT)<br>0603YC104KAT2A  |

| 4    | Open                                            | 0603        | C3, C6 <sup>(2)</sup>                 | 2                     |                                                    |                              |

| 5    | Open                                            | 0603        | R1, R3, R6,<br>R9, R12 <sup>(3)</sup> | 5                     |                                                    |                              |

| 6    | Resistor, 0-Ω, 1/10-W, 1%                       | 0603        | C7. C8, C9,<br>C10                    | 4                     | (KOA) RK73Z1JTTD                                   | (GARRETT)<br>RK73Z1JTTD      |

| 7    | Resistor, 49.9-Ω, 1/10-W, 1%                    | 0603        | R2, R11                               | 2                     | (KOA) RK73H1JLTD49R9F                              | (GARRETT)<br>RK73H1JLTD49R9F |

| 8    | Resistor, 249-Ω, 1/10-W, 1%                     | 0603        | R7, R8                                | 2                     | (KOA) RK73H1JLTD2490F                              | (GARRETT)<br>RK73H1JLTD2490F |

| 9    | Jack, banana recepticle, 0.25-in. diameter hole |             | J3, J4, J5, J6                        | 4                     | (HH SMITH) 101                                     | (NEWARK) 35F865              |

| 10   | Test point, black                               |             | TP1                                   | 1                     | (KEYSTONE) 5001                                    | (DIGI-KEY) 5001K-ND          |

| 11   | Connector, edge, SMA PCB jack                   |             | J1, J2                                | 2                     | (JOHNSON) 142-0701-801                             | (NEWARK) 90F2624             |

| 12   | Integrated Circuit, THS4304                     |             | U1                                    | 1                     | (TI) THS4304DGK, or<br>(TI) THS4304DBV             |                              |

| 13   | Standoff, 4-40 HEX, 0.625-in.<br>Length         |             |                                       | 4                     | (KEYSTONE) 1808                                    | NEWARK) 89F1934              |

| 14   | Screw, Phillips, 4-40, 0.250-in.                |             |                                       | 4                     | SHR-0440-016-SN                                    |                              |

| 15   | Board, printed-circuit                          |             |                                       | 1                     | (TI) THS4304DGK ENG A, or<br>(TI) THS4304DBV ENG A |                              |

<sup>(1)</sup> NOTE: All items are designated for both the DBV and DGK EVMs unless otherwise noted.

(2) C6 used on DGK EVM only.

(3) R12 used on DBV EVM only.

Figure 48. THS4304DGK EVM Layout Top and L2

Figure 50. THS4304DBV EVM Layout Top and L2

Figure 49. THS4304DGK EVM Layout Bottom and L3

Figure 51. THS4304DBV EVM Layout Bottom and L3

## NON-INVERTING GAIN WITH SPLIT SUPPLY

The following schematic shows how to configure the operational amplifier for non-inverting gain with split power supply ( $\pm$  2.5V). This is how the EVM is supplied from TI. This configuration is convenient for test purposes because most signal generators and analyzer are designed to use ground-referenced signals by default. Note the input and output provides  $50-\Omega$  termination.

Figure 52. Non-Inverting Gain with Split Power Supply

## **INVERTING GAIN WITH SPLIT POWER SUPPLY**

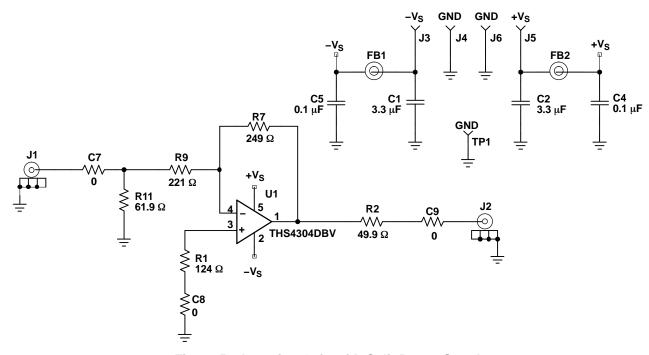

The following schematic shows how to configure the operational amplifier for inverting gain of 1 (–1 V/V) with split power supply ( $\pm 2.5$  V). Note the input and output provides 50- $\Omega$  termination for convenient interface to common test equipment.

Figure 53. Inverting Gain with Split Power Supply

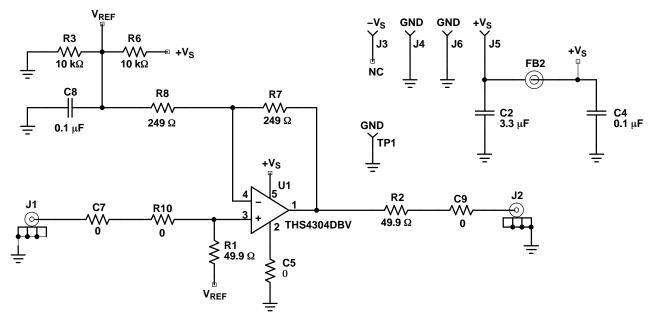

### NON-INVERTING SINGLE-SUPPLY OPERATION

The THS4304 EVM can easily be configured for single 5-V supply operation, as shown in the following schematic, with no change in performance. This circuit passes dc signals at the input, so care must be taken to reference (or bias) the input signal to mid-supply.

If dc operation is not required, the amplifier can be ac coupled by inserting a capacitor in series with the input (C7) and output (C9).

Figure 54. Non-Inverting 5-V Single-Supply Amplifier

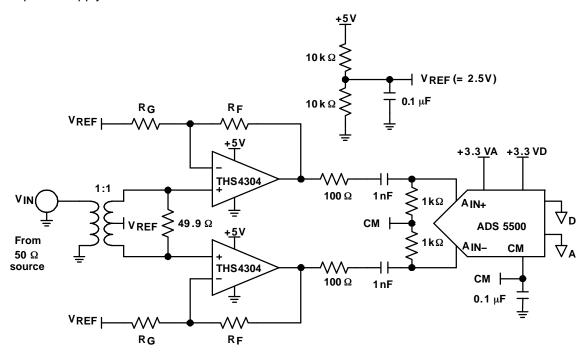

### **DIFFERENTIAL ADC DRIVE AMPLIFIER**

The circuit shown in Figure 54 is adapted as shown in Figure 55 to provide a high-performance differential amplifier drive circuit for use with high-performance ADCs, like the ADS5500 (14-bit 125-MSP ADC). For testing purposes, the circuit uses a transformer to convert the signal from a single-ended source to differential. If the input signal source in your application is differential and biased to mid-rail, no transformer is required.

The circuit employs two amplifiers to provide a differential signal path to the ADS5500. A resistor divider (two  $10\text{-k}\Omega$  resistors) is used to obtain a mid-supply reference voltage of 2.5 V (VREF) (the same as shown in the single-supply circuit of Figure 54). Applying this voltage to the one side of RG and to the positive input of the operational amplifier (via the center-tap of the transformer) sets the input and output common-mode voltage of the operational amplifiers to mid-rail to optimize their performance. The ADS5500 requires an input common-mode voltage of 1.5 V. Due to the mismatch in required common-mode voltage, the signal is ac coupled from the amplifier output, via the two 1-nF capacitors, to the input of the ADC. The CM voltage of the ADS5500 is used to bias the ADC input to the required voltage, via the 1-k $\Omega$  resistors. Note:  $100\text{-}\mu\text{A}$  common-mode current is drawn by the ADS5500 input stage (at 125 MSPS). This causes a 100-mV shift in the input common-mode voltage, which does not impact the performance when driving the input to -1 dB of full scale. To offset this effect, a voltage divider from the power supply can be used to derive the input common-mode voltage reference.

Because the operational amplifiers are configured as non-inverting, the inputs are high impedance. This is particularly useful when interfacing to a high-impedance source. In this situation, the amplifiers provide impedance matching and amplification of the signal.

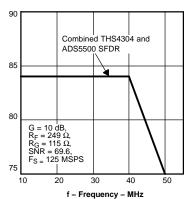

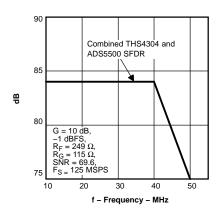

The SFDR performance of the circuit is shown in the following graph (see Figure 56) and provides for full performance from the ADS5500 to 40 MHz.

The differential topology employed in this circuit provides for significant suppression of the 2nd-order harmonic distortion of the amplifiers. This, along with the superior 3rd-order harmonic distortion performance of the amplifiers, results in the SFDR performance of the circuit (at frequencies up to 40 MHz) being set by higher-order harmonics generated by the sampling process of the ADS5500.

The amplifier circuit (with resistor divider for bias voltage generation) requires a total of 185 mW of power from a single 5-V power supply.

Figure 55. Differential ADC Drive Amplifier Circuit

Figure 56. SFDR Performance versus Frequency – THS4304 Driving ADS5500

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

| THS4304D         | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 4304                 | Samples |

| THS4304DBVR      | ACTIVE     | SOT-23       | DBV                | 5    | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AKW                  | Samples |

| THS4304DBVT      | ACTIVE     | SOT-23       | DBV                | 5    | 250            | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AKW                  | Samples |

| THS4304DG4       | ACTIVE     | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | 4304                 | Samples |

| THS4304DGK       | ACTIVE     | VSSOP        | DGK                | 8    | 80             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AKU                  | Samples |

| THS4304DGKR      | ACTIVE     | VSSOP        | DGK                | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | AKU                  | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

## **PACKAGE OPTION ADDENDUM**

10-Dec-2020

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF THS4304:

■ Space: THS4304-SP

NOTE: Qualified Version Definitions:

• Space - Radiation tolerant, ceramic packaging and qualified for use in Space-based application

www.ti.com 5-Jan-2022

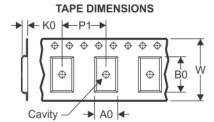

## TAPE AND REEL INFORMATION

|   |    | Dimension designed to accommodate the component width     |

|---|----|-----------------------------------------------------------|

|   |    | Dimension designed to accommodate the component length    |

|   | K0 | Dimension designed to accommodate the component thickness |

|   | W  | Overall width of the carrier tape                         |

| Γ | P1 | Pitch between successive cavity centers                   |

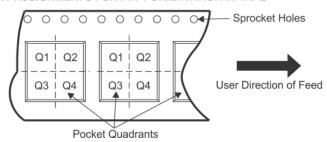

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| All differsions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| THS4304DBVR                 | SOT-23          | DBV                | 5 | 3000 | 180.0                    | 9.0                      | 3.15       | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| THS4304DBVT                 | SOT-23          | DBV                | 5 | 250  | 180.0                    | 9.0                      | 3.15       | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| THS4304DGKR                 | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

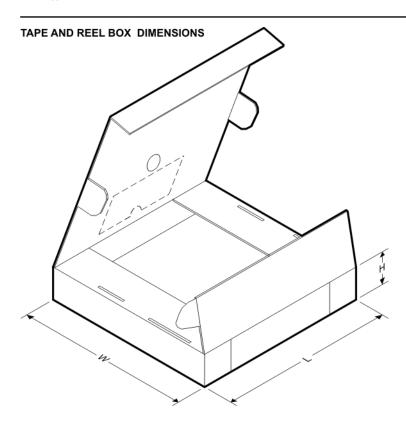

www.ti.com 5-Jan-2022

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins SPQ |      | Length (mm) | Width (mm) | Height (mm) |  |

|-------------|--------------|-----------------|----------|------|-------------|------------|-------------|--|

| THS4304DBVR | SOT-23       | DBV             | 5        | 3000 | 182.0       | 182.0      | 20.0        |  |

| THS4304DBVT | SOT-23       | DBV             | 5        | 250  | 182.0       | 182.0      | 20.0        |  |

| THS4304DGKR | VSSOP        | DGK             | 8        | 2500 | 346.0       | 346.0      | 29.0        |  |

## PACKAGE MATERIALS INFORMATION

www.ti.com 5-Jan-2022

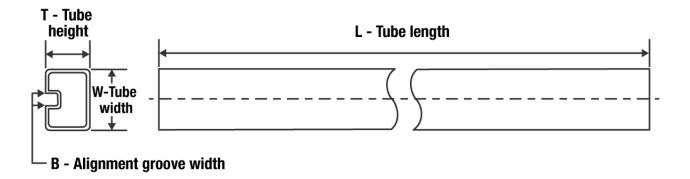

## **TUBE**

### \*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| THS4304D   | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

| THS4304DG4 | D            | SOIC         | 8    | 75  | 505.46 | 6.76   | 3810   | 4      |

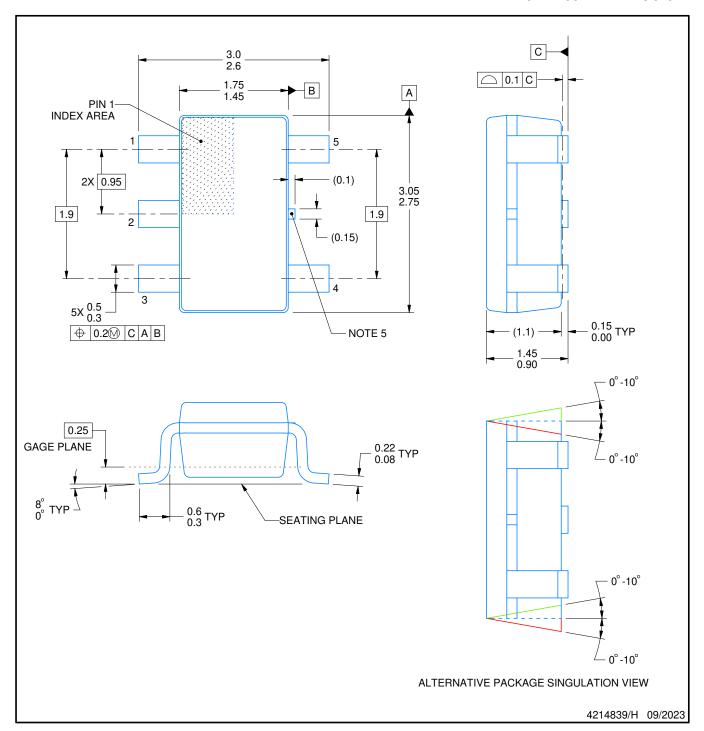

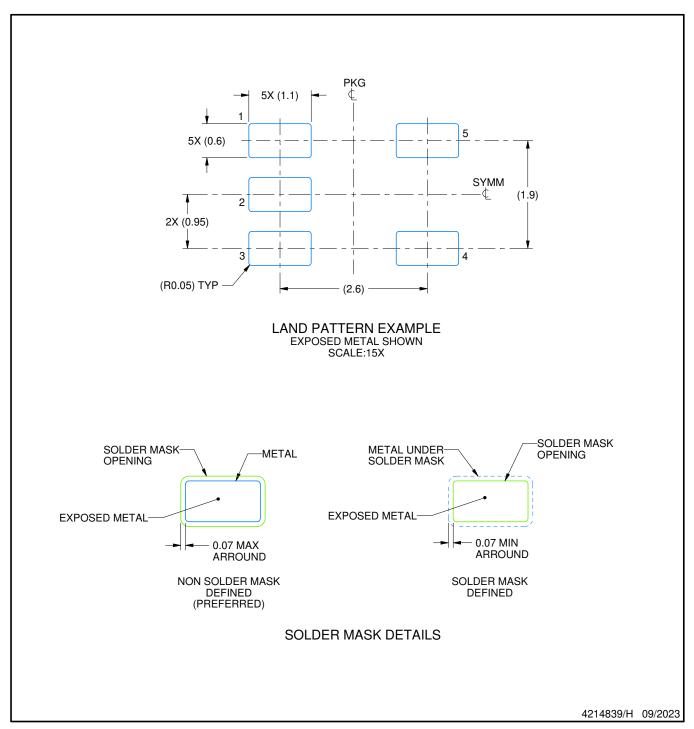

SMALL OUTLINE TRANSISTOR

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 5. Support pin may differ or may not be present.

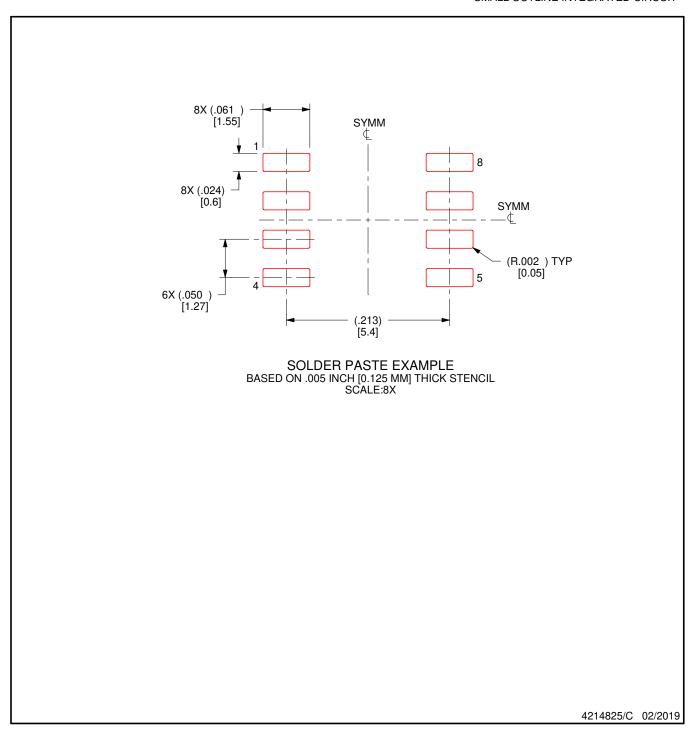

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

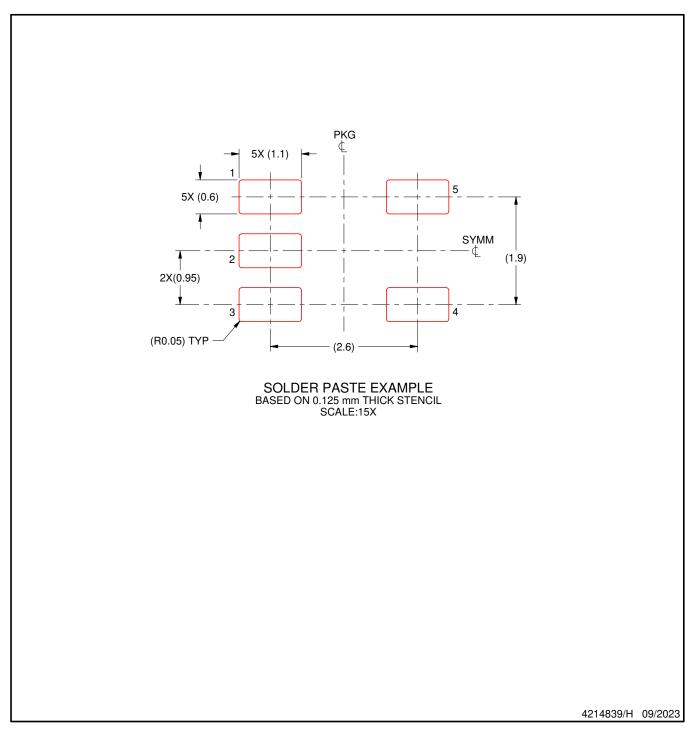

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

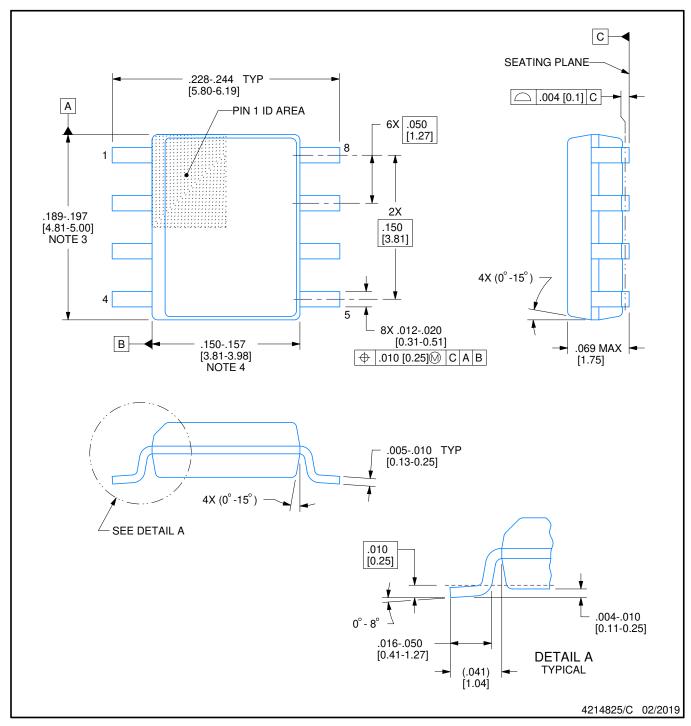

## **PACKAGE OUTLINE**

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.5. Reference JEDEC registration MS-012, variation AA.

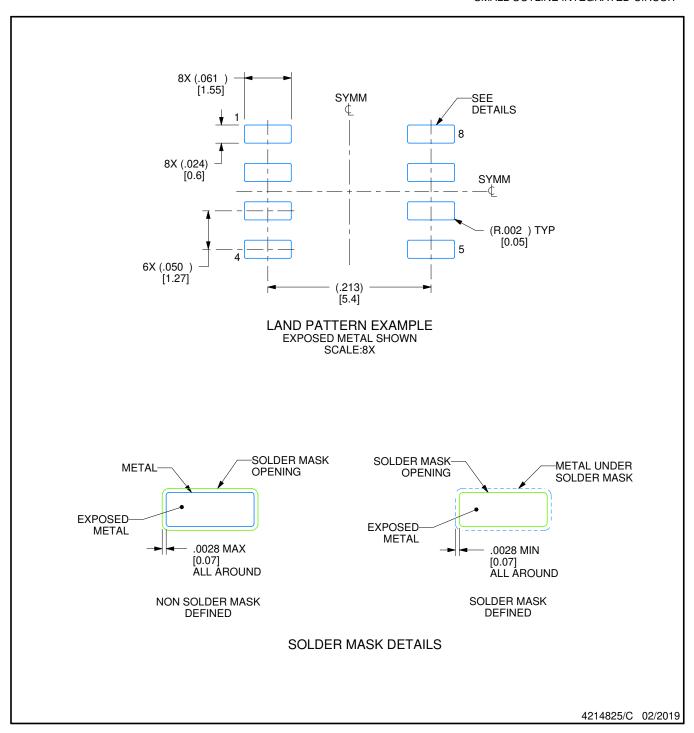

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

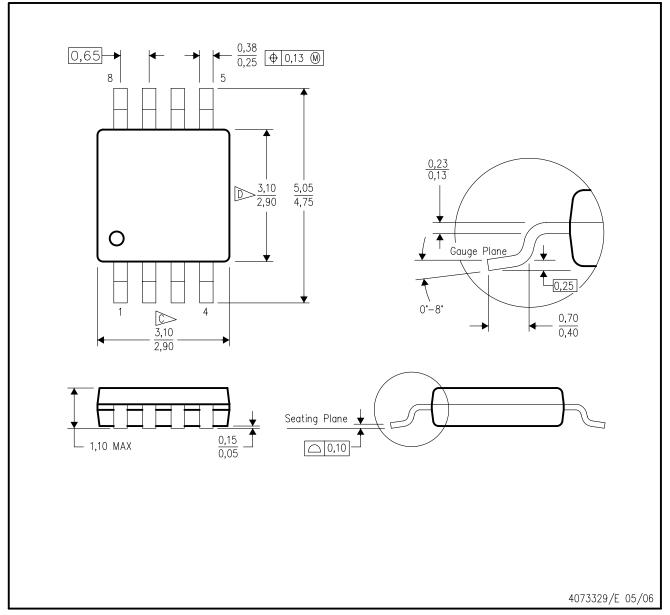

# DGK (S-PDSO-G8)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

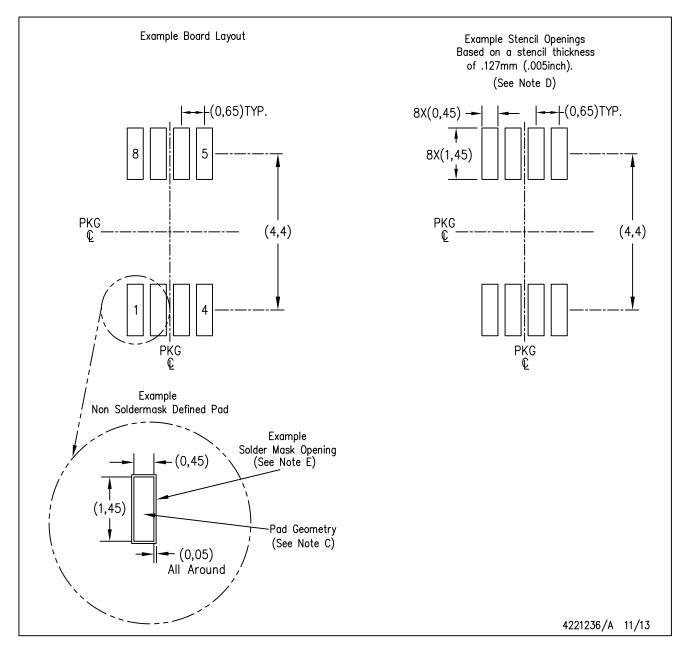

# DGK (S-PDSO-G8)

## PLASTIC SMALL OUTLINE PACKAGE

### NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated