March 1989 Revised February 2000

### **DM96L02**

# **Dual Retriggerable Resettable Monostable Multivibrator**

#### **General Description**

The DM96L02 is a dual TTL monostable multivibrator with trigger mode selection, reset capability, rapid recovery, internally compensated reference levels and high speed capability. Output pulse duration and accuracy depend on external timing components, and are therefore under user control for each application. It is well suited for a broad variety of applications, including pulse delay generators, square wave generators, long delay timers, pulse absence detectors, frequency detectors, clock pulse generators and fixed-frequency dividers. Each input is provided with a clamp diode to limit undershoot and minimize ringing induced by fast fall times acting on system wiring impedances.

#### **Features**

- Retriggerable, 0% to 100% duty cycle

- DC level triggering, insensitive to transition times

- Leading or trailing-edge triggering

- Complementary outputs with active pull-ups

- $\blacksquare$  Pulse width compensation for  $\Delta V_{CC}$  and  $\Delta T_{A}$

- 50 ns to ∞ output pulse width range

- Optional retrigger lock-out capability

- Resettable, for interrupt operations

### **Ordering Code:**

| Order Number | Package Number | Package Description                                                   |

|--------------|----------------|-----------------------------------------------------------------------|

| DM96L02N     | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

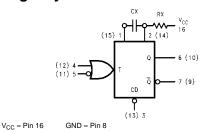

#### **Logic Symbol**

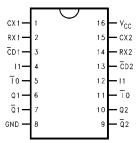

#### **Connection Diagram**

#### **Pin Descriptions**

| Pin Names        | Description                         |

|------------------|-------------------------------------|

| ĪO               | Trigger Input (Active Falling Edge) |

| I1               | Trigger Input (Active Rising Edge)  |

| $\overline{C}_D$ | Direct Clear Input (Active LOW)     |

| Q                | Positive Pulse Output               |

| Q                | Complementary Pulse Output          |

| CX               | External Capacitor Connection       |

| RX               | External Resistor Connection        |

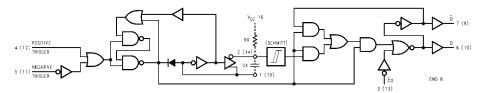

#### **Functional Block Diagram**

#### **Operation Notes**

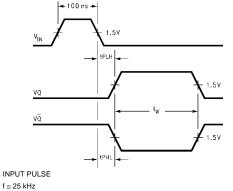

- 1. TRIGGERING—can be accomplished by a positive-going transition on pin 4 (12) or a negative-going transition on pin 5 (11). Triggering begins as a signal crosses the input V<sub>IL</sub>:V<sub>IH</sub> threshold region; this activates an internal latch whose unbalanced cross-coupling causes it to assume a preferred state. As the latch output goes LOW it disables the gates leading to the Q output and, through an inverter, turns on the capacitor discharge transistor. The inverted signal is also fed back to the latch input to change its state and effectively end the triggering action; thus the latch and its associated feedback perform the function of a differentiator.

- The emitters of the latch transistors return to ground through an enabling transistor which must be turned off between successive triggers in order for the latch to proceed through the proper sequence when triggering is desired. Pin 5 (11) must be HIGH in order to trigger at pin 4 (12); conversely, pin 4 (12) must be LOW in order to trigger at pin 5 (11).

- 2. RETRIGGERING—In a normal cycle, triggering initiates a rapid discharge of the external timing capacitor, followed by a ramp voltage run-up at pin 2 (14). The delay will time out when the ramp voltage reaches the upper trigger point of a Schmitt circuit, causing the outputs to revert to the quiescent state. If another trigger occurs before the ramp voltage reaches the Schmitt threshold, the capacitor will be discharged and the ramp will start again without having disturbed the output. The delay period can therefore be extended for an arbitrary length of time by insuring that the interval between triggers is less than the delay time, as determined by the external capacitor and resistor.

- 3. NON-RETRIGGERABLE OPERATION—Retriggering can be inhibited logically, by connecting pin 6 (10) back to pin 4 (12) or by connecting pin 7 (9) back to pin 5 (11). Either hook-up has the effect of keeping the latchenabling transistor turned on during the delay period, which prevents the input latch from cycling as discussed above in the section on triggering.

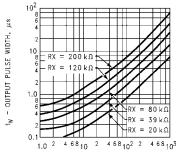

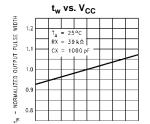

4. OUTPUT PULSE WIDTH—An external resistor  $R_X$  and an external capacitor  $C_X$  are required, as shown in the functional block diagram. To minimize stray capacitance and noise pickup,  $R_X$  and  $C_X$  should be located as close as possible to the circuit. In applications which require remote trimming of the pulse width, as with a variable resistor,  $R_X$  should consist of a fixed resistor in series with the variable resistor; the fixed resistor should be located as close as possible to the circuit. The output pulse width  $t_W$  is defined as follows, where  $R_X$  is in  $k\Omega$ ,  $C_X$  is in pF and  $t_W$  is in ns.

$$\begin{split} &t_{W}=0.33~R_{X}C_{X}~(1+3/R_{X})~for~C_{X}\geq10^{3}~pF\\ &16~k\Omega\leq R_{X}\leq220~k\Omega~for~0^{\circ}C~to~+75^{\circ}C\\ &20~k\Omega\leq R_{X}\leq100~k\Omega~for~-55^{\circ}C~to~+125^{\circ}C \end{split}$$

$C_X\,\text{may}$  vary from 0 to any value. For pulse widths with  $C_X\,\text{less}$  than  $10^3\,\text{pF}$  see Figure 1.

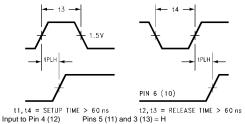

- 5. SETUP AND RELEASE TIMES—The setup times listed below are necessary to allow the latch-enabling transistor to turn off and the node voltages within the input latch to stabilize, thus insuring proper cycling of the latch when the next trigger occurs. The indicated release times (equivalent to trigger duration) allow time for the input latch to cycle and its signal to propagate.

- 6. RESET OPERATION—A LOW signal on \(\overline{\overline{C}}\_D\), pin 3 (13), will terminate an output pulse, causing Q to go LOW and \(\overline{Q}\) to go HIGH. As long as \(\overline{C}\_D\) is held LOW, a delay period cannot be initiated nor will attempted triggering cause spikes at the outputs. A reset pulse duration, in the LOW state, of 25 ns is sufficient to insure resetting. If the reset input goes LOW at the same time that a trigger transition occurs, the reset will dominate and the outputs will not respond to the trigger. If the reset input goes HIGH coincident with a trigger transition, the circuit will respond to the trigger.

#### 96L02 Pulse Width vs. $\boldsymbol{R}_{\boldsymbol{X}}$ and $\boldsymbol{C}_{\boldsymbol{X}}$

CX - TIMING CAPACITANCE - pF FIGURE 1.

$Amp \cong 3.0 \text{V}$

$Width \cong 100 \ ns$

# **Typical Characteristics**

## Absolute Maximum Ratings(Note 1)

Supply Voltage 7V Input Voltage 5.5V Operating Free Air Temperature Range 0°C to +70°C Storage Temperature Range  $-65^{\circ}$ C to +150°

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol                                   | Parameter                            | Conditions                                                                                               | Min  | Nom | Max  | Units |

|------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>CC</sub>                          | Supply Voltage                       |                                                                                                          | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub>                          | HIGH Level Input Voltage             |                                                                                                          | 2    |     |      | V     |

| V <sub>IL</sub>                          | LOW Level Input Voltage              |                                                                                                          |      |     | 0.7  | V     |

| I <sub>OH</sub>                          | HIGH Level Output Current            |                                                                                                          |      |     | 0.36 | mA    |

| I <sub>OL</sub>                          | LOW Level Output Current             |                                                                                                          |      |     | 4.8  | mA    |

| T <sub>A</sub>                           | Free Air Operating Temperature       |                                                                                                          | 0    |     | 70   | °C    |

| t <sub>W</sub> (L)<br>t <sub>W</sub> (H) | Minimum Input Pulse<br>Width, I1, Ī0 | V <sub>CC</sub> = 5.0V                                                                                   |      |     |      | ns    |

| t <sub>W</sub> (min)                     | Minimum Output Pulse Width at Q, Q   | $\begin{split} &V_{CC}=5.0\text{V},\\ &R_X=20\text{ k}\Omega,\\ &C_X=0,\\ &C_L=15\text{ pF} \end{split}$ |      | 110 |      | ns    |

| t <sub>W</sub>                           | Output Pulse Width, Q, Q             | $V_{CC} = 5.0V,$ $R_X = 39 \text{ k}\Omega,$ $C_X = 1000 \text{ pF}$                                     | 12.4 |     | 15.2 | μs    |

| R <sub>X</sub>                           | Timing Resistor Range                |                                                                                                          |      |     | 220  | kΩ    |

#### **Electrical Characteristics**

over recommended operating free air temperature (unless otherwise noted)

| Symbol          | Parameter                         | Conditions                                                    | Min  | Typ<br>(Note 2) | Max   | Units |

|-----------------|-----------------------------------|---------------------------------------------------------------|------|-----------------|-------|-------|

| VI              | Input Clamp Voltage               | $V_{CC} = Min, I_I = -10 \text{ mA}$                          |      |                 | -1.5  | V     |

| V <sub>OH</sub> | HIGH Level Output Voltage         | $V_{CC} = Min, I_{OH} = Max,$<br>$V_{IL} = Max, V_{IH} = Min$ | 2.4  |                 |       | V     |

| V <sub>OL</sub> | LOW Level Output Voltage          | $V_{CC} = Min, I_{OL} = Max,$<br>$V_{IL} = Min, V_{IL} = Max$ |      |                 | 0.3   | V     |

| I <sub>I</sub>  | Input Current @ Max Input Voltage | $V_{CC} = Max, V_I = 5.5V$                                    |      |                 | 1     | mA    |

| I <sub>IH</sub> | HIGH Level Input Current          | $V_{CC} = Max, V_I = 2.4V$                                    |      |                 | 20    | μΑ    |

| I <sub>IL</sub> | LOW Level Input Current           | $V_{CC} = Max, V_I = 0.3V$                                    |      |                 | -0.4  | mA    |

| Ios             | Short Circuit Output Current      | V <sub>CC</sub> = Max (Note 3) V <sub>O</sub> = 1.0V          | -2.0 |                 | -13.0 | mA    |

| I <sub>CC</sub> | Supply Current                    | V <sub>CC</sub> = Max (Note 4)                                |      |                 | 16    | mA    |

|                 |                                   |                                                               |      |                 |       |       |

Note 2: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 4:  $\rm I_{CC}$  is measured with all outputs open and all inputs grounded.

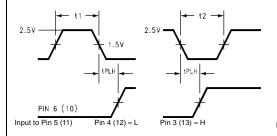

## **Switching Characteristics**

$V_{CC} = +5.0V, T_A = +25^{\circ}C$

| Symbol           | Parameter                                                                                   | Conditions                                                                  | Min | Max | Units |

|------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-------|

| t <sub>PLH</sub> | Propagation Delay $\overline{10}$ to Q,                                                     | $V_{CC} = 5.0V, R_X = 20 \text{ k}\Omega$<br>$C_X = 0, C_L = 15 \text{ pF}$ |     | 80  | ns    |

| t <sub>PHL</sub> | Propagation Delay $\overline{0}$ to $\overline{\mathbb{Q}}$ , I1 to $\overline{\mathbb{Q}}$ | $V_{CC} = 5.0V, R_X = 20 \text{ k}\Omega$<br>$C_X = 0, C_L = 15 \text{ pF}$ |     | 65  | ns    |

| t <sub>PLH</sub> | Propagation Delay $\overline{CD}$ to $\overline{Q}$ , $\overline{CD}$ to $Q$                | $V_{CC} = 5.0V$ , $R_X = 39 \text{ k}\Omega$<br>$C_X = 1000 \text{ pF}$     |     |     | ns    |

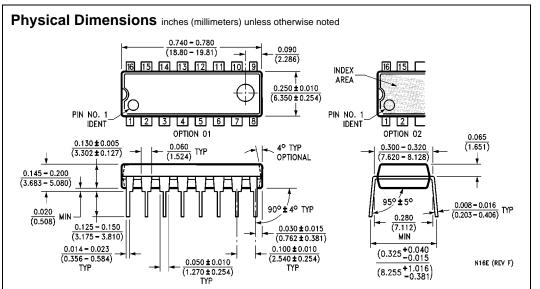

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com