### General Description

The MAX100 evaluation kit (EV kit) allows high-speed digitizing of analog signals at 250Msps, using the MAX100 ADC. All circuitry required to support the ADC is supplied. Data output is available in three formats: divide-by-1, divide-by-2, or divide-by-5 mode. Clocking is provided by an external clock source input through an SMA connector.

The MAX100 EV kit main board comes complete with a MAX100 high-speed, 8-bit flash ADC with strobed comparators, latched outputs, and an internal track/hold. Analog input to the board is through two SMA coaxial connectors, for use with either differential or singleended inputs.

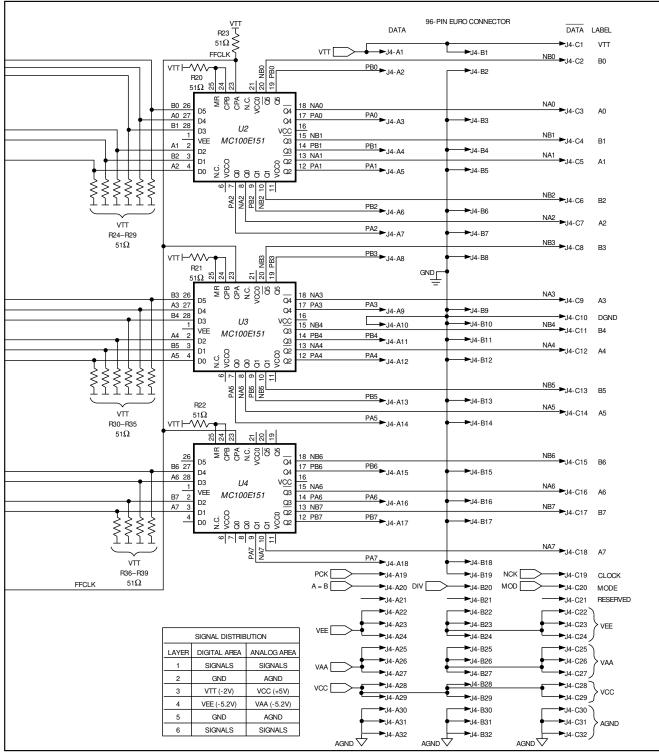

Signals from the main board include dual-output data paths that allow easy interfacing to external circuitry. These two outputs can be configured either to provide two identical fast outputs (A and B), or an 8-to-16 demultiplexer mode that reduces the output data rates to one-half the sample clock rate. This demux is internal to the MAX100 ADC and is one of the key features of this device.

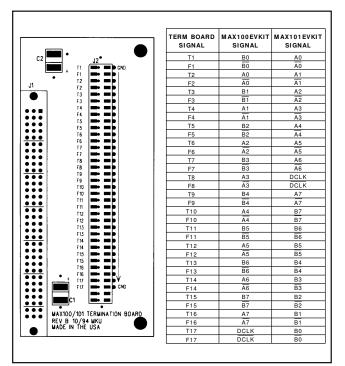

A termination board with  $50\Omega$  ECL pull-down resistors is also supplied, and is connected to the main board with a 3x32 pin EURO-card connector. It provides access to the converter output data and provides proper ECL data termination. In addition to the pull-down resistors, this board has two ranks of square pins, each providing eight differential data outputs plus clock outputs. Either AData or BData may be observed with a high-speed logic analyzer.

Standard power supplies of +5V and -5.2V are needed to operate the MAX100 EV kit board. Power can be supplied through the 3x32 EURO-card connector or through the pads on the edge of the board. Nominal power dissipation for both boards is 12W. The board set comes fully assembled and tested, with the MAX100 installed. Features

- ♦ 6.8 Effective Bits at 125MHz

- On-Board Reference Generator/Buffer

- 50Ω Input Through SMA Coaxial Connectors

- Dual Differential-Output Data Paths

- ±270mV Input Signal Range

- + Latched 100k ECL Outputs

- ♦ 3x32 Pin EURO-Card Connector

### Ordering Information

| PART        | TEMP. RANGE  | BOARD TYPE  |

|-------------|--------------|-------------|

| MAX100EVKIT | 0°C to +70°C | Multi-Layer |

**Call toll free 1-800-998-8800 for free literature.**

### \_Component List

| DESIGNATION                                                                      | QTY | DESCRIPTION                                       |  |

|----------------------------------------------------------------------------------|-----|---------------------------------------------------|--|

| U5                                                                               | 1   | Motorola MC100E116<br>(quintuple line receiver)   |  |

| U2, U3, U4                                                                       | 3   | Motorola MC100E151 (Hex D flip-flop)              |  |

| U9                                                                               | 1   | Motorola MC100E157<br>(quadruple 2:1 multiplexer) |  |

| U6                                                                               | 1   | LM337T negative voltage regulator                 |  |

| Install on back<br>of board<br>behind U6                                         | 1   | Insulating washer                                 |  |

| U7                                                                               | 1   | Maxim MAX412CPA                                   |  |

| U8                                                                               | 1   | Maxim MX580KH                                     |  |

| D1, D2                                                                           | 2   | Central Semiconductor CMPSH-3                     |  |

| D3                                                                               | 1   | Central Semiconductor CMPD4448                    |  |

| C25, C27                                                                         | 2   | 0.22µF ceramic SMD capacitors                     |  |

| C2, C6, C9                                                                       | 3   | 0.1µF ceramic SMD capacitors                      |  |

| C1, C3, C5,<br>C8, C11, C12,<br>C14, C16, C18,<br>C20, C22–C24,<br>C26, C28, C29 | 16  | 0.01µF ceramic SMD capacitors                     |  |

| C13, C15,<br>C17, C19,<br>C21, C30                                               | 6   | 100pF ceramic SMD capacitors                      |  |

| C4, C7, C10                                                                      | 3   | 10µF surface-mount tantalum capacitors            |  |

| SW1                                                                              | 1   | 8-pin dip switch                                  |  |

| L1, L2                                                                           | 2   | Surface-mount ferrite bead                        |  |

| R14, R15                                                                         | 2   | $20\Omega$ , 5% surface-mount resistors           |  |

| R18, R19                                                                         | 2   | 27.4 $\Omega$ , 1% surface-mount resistors        |  |

| R7, R8, R13,<br>R20–R45                                                          | 29  | 51 $\Omega$ , 5% surface-mount resistors          |  |

| R1, R3, R6                                                                       | 3   | 82.5 $\Omega$ , 1% surface-mount resistors        |  |

| R5, R10                                                                          | 2   | 121 $\Omega$ , 1% surface-mount resistors         |  |

| R9                                                                               | 1   | 150 $\Omega$ , 1% surface-mount resistor          |  |

| R2, R4                                                                           | 2   | 221 $\Omega$ , 1% surface-mount resistors         |  |

| R16, R17                                                                         | 2   | 12.1k $\Omega$ , 1% surface-mount resistors       |  |

| R11, R12                                                                         | 2   | 100 $\Omega$ trim pots                            |  |

| J1, J2, J3                                                                       | 3   | Female SMA connectors                             |  |

| J4                                                                               | 1   | 96-pin EURO-style plug                            |  |

| None                                                                             | 1   | MAX100 clamp kit                                  |  |

### Quick Start

- 1) Plug the termination board into the 96-pin connector of the MAX100 EV kit board.

- 2) Use a fan to provide at least 200 lineal feet per minute airflow to the MAX100's heatsink.

- 3) Connect the power supplies. The power-supply input pads are in the lower right corner of the MAX100 EV kit board. The board requires a 12W power supply that provides +5V and -5.2V with a common ground.

- Turn on the -5.2V power supply, followed by the +5V power supply. The -5.2V power supply should be the first supply turned on and the last supply turned off.

- 5) Connect a low-phase-jitter RF source with an input range of -4dBm to +10dBm to the clock input.

- Connect a test signal to the analog inputs. Use IN+ and IN- if the signal is differential, or use IN+ if the signal is single-ended.

- 7) Use a logic analyzer (such as the HP8000 or an equivalent data-acquisition system) to observe the digitized results on the termination board pins. The outputs are 100k ECL compatible.

### Detailed Description

### **Board Set**

The MAX100 EV kit is a two-board set. The first contains ECL-interface circuitry and the MAX100 ADC. The second (termination board) provides for high-speed signal termination and access to the data. For further signal processing, the board containing the MAX100 can be plugged into a larger customer system via the provided EURO-card connector.

### **Clock Input**

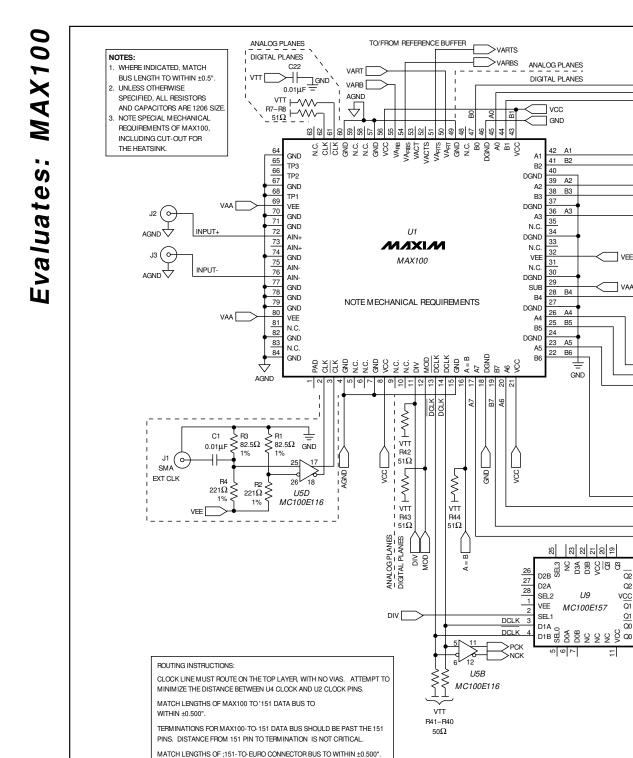

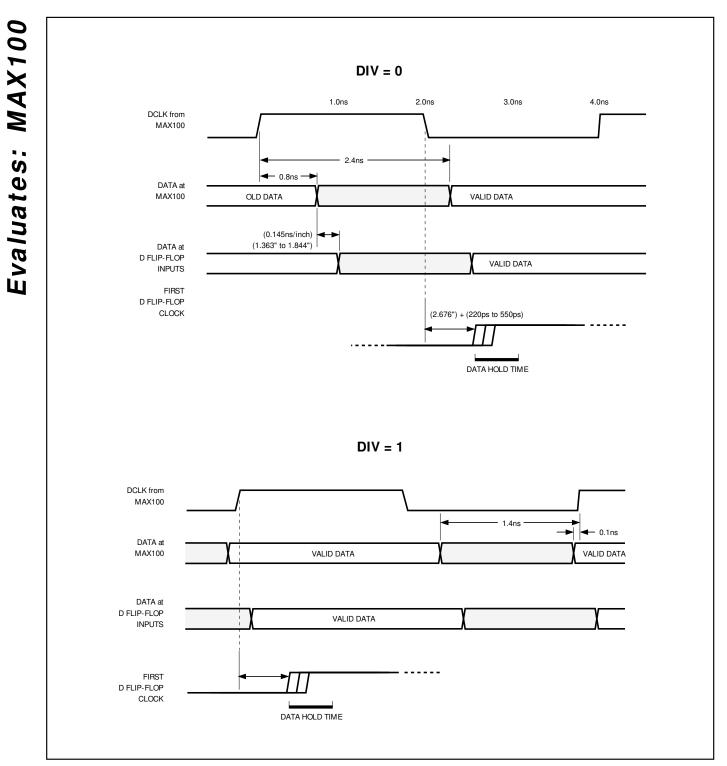

The ADC clock is provided through an external clock input. The external clock supplied to the board must be very stable, with low phase jitter (-150dBc/Hz at 0.2kHz from fundamental) for best effective bits performance. Figure 2 in the MAX100 data sheet shows the input to output clock and data timing relationships.

The MAX100 will accurately operate with low-repetitionrate clocks (DC to 250MHz) as long as the proper  $t_{pwl}$ is observed (nominally 2ns to 5ns). Refer to Figures 1–4 in the MAX100 data sheet for further information.

### Analog Input

Analog input to the ADC is made through one or both of the SMA coaxial connectors (IN+, IN-) provided. Each input is a direct connection to the ADC.  $50\Omega$  terminations are provided (at AIN+ and AIN- inputs) internal to the MAX100 ADC. Optimum performance is achieved

by using the converter in differential input mode. Single-ended drive is handled by choosing either input, and leaving open or terminating the other in the system characteristic impedance. In this mode, the unused input can provide a DC offset to the incoming signal. (See the *Electrical Characteristics* in the MAX100 data sheet for this DC voltage range.)

To obtain a digital output of all ones (11....1) with differential input drive, apply 270mV between AlN+ and AlN-. That is, AlN+ = +135mV and AlN- = -135mV (when no DC offset is applied). Mid-scale digital output code occurs when there is no voltage difference across the analog inputs. Zero-scale digital output code, with differential drive, occurs when AlN+ = -135mV and AlN- = +135mV. The converter's output stays at all ones (full scale) or all zeros (zero scale) when over-ranged or under-ranged, respectively. Table 1 shows these relationships.

**Digital Outputs** The MAX100 EV kit provides complementary ECL digital outputs. Data output from the ADC is available in several selectable options (Table 2). Two 8-bit-wide data paths from the ADC are latched in D flip-flops (MC100E151), and are provided as unterminated differential outputs at the 3x32 pin EURO-card connector on the main board. Output timing clocks DCLK and DCLK are also available unterminated at the connector.

### **Clock Phasing**

The MAX100 contains an internal track/hold (T/H) amplifier. The differential inputs, AIN+ and AIN-, are tracked continuously between data samples. When a negative CLK is applied, the T/H enters the hold mode. When CLK reaches the low state, the just-acquired sample is presented to the ADC's input comparators. After additional clock cycles required for internal processing, the sampled data is available at the AData or BData outputs. All output data is timed from the output clocks, DCLK and DCLK. (See Figure 2 in the MAX100 data sheet.)

### **ADC Reference Resistors**

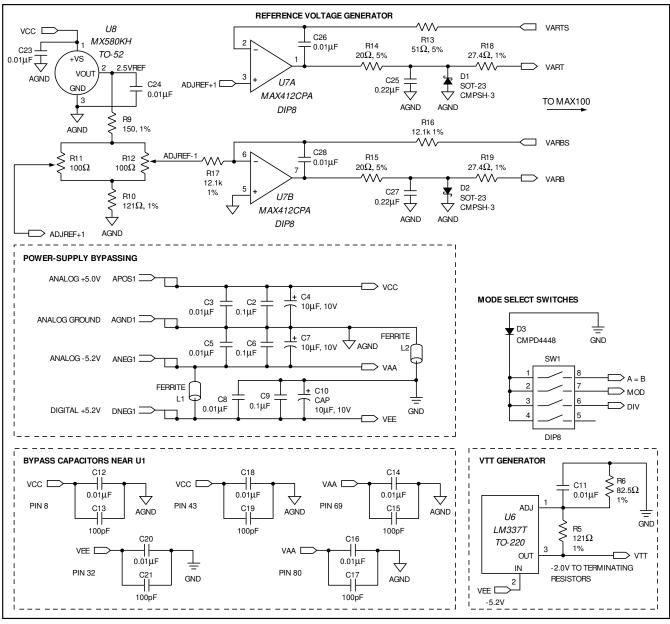

An on-board reference supply and op-amp circuit drive the ADC reference-resistor string. Adjustments can be made through the two potentiometers provided. After the MAX100 ADC is installed, follow the *Calibration Procedure.*

Buffer amplifiers are used to drive the top and bottom inputs of the reference-resistor string. (The resistor string center-tap is not made available for adjustment on this board.) A 2.5V reference (MX580KH) is divided down and buffered through a MAX412 op amp. The relatively low 146 $\Omega$  input impedance of this string will draw approximately 14mA. A reference voltage of nominally ±1.02V is set by trim pots R11 and R12 at the factory, and can be measured at the VARTS and VARBS sense input pins. This reference controls the comparator input windows, and can be adjusted between ±1.4V to accommodate other reference voltages (MAX100 accuracy specifications are based on a reference voltage of ±1.02V).

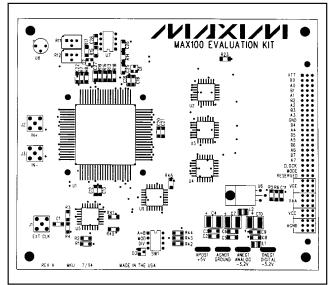

### DIV, MOD, A=B

Three dip switches (SW1), DIV, MOD, and A=B, program converter operation and the characteristics of the two output data paths. Six options are available, but the normal operating configuration is set to 0 0 1 on the A=B, MOD, and DIV switches, respectively (Table 2). This gives the most current sample at AData, with the older data on BData. Both outputs are synchronous and are output at half the input clock rate. Figure 4 shows the location of these switches on the ADC board. Refer to Table 1 for mode-selection instructions.

### **Power Supplies**

Two supplies are needed for normal operation of both boards with a device installed: +5V at 0.6A and -5.2V at 1.7A. The pads APOS1 and ANEG1 are located in the lower right corner of the ADC board, and are labeled accordingly. The ADC runs off both supplies.

Power may also be applied at the EURO-card connector pins, which are labeled as follows: VCC (+5V), VEE (-5.2V for digital DNEG1), VAA (-5.2V for analog ANEG1), and AGND (AGND1 ground). The ferrite beaded jumper (L1) in the lower right corner of the board connects VAA and VEE for a single -5.2V supply.

### **Board Layout**

The MAX100 requires proper PC board layout for device operation. This section explains the layout requirements and demonstrates how the EV kit achieves these goals.

Use power and ground planes to deliver power to the devices, keeping the digital planes separate from the analog planes. The EV kit uses layers 3, 4, and 5 for power and ground planes. Tie digital ground and analog ground together at a single point, as close to the power supply as possible. On the EV kit, digital ground ties to analog ground at ferrite bead L1. Likewise, tie digital power (VEE) and analog power (VAA) together at a single point, as close to the power supply as possible. On the EV kit, digital power at a single point, as close to the power supply as possible. On the EV kit, digital power at a single point, as close to the power supply as possible. On the EV kit, digital power ties to analog -5.2V power at ferrite bead L2.

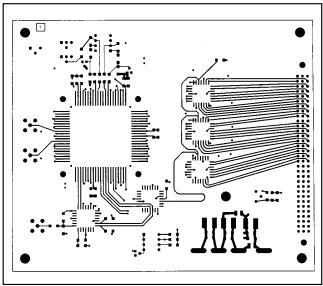

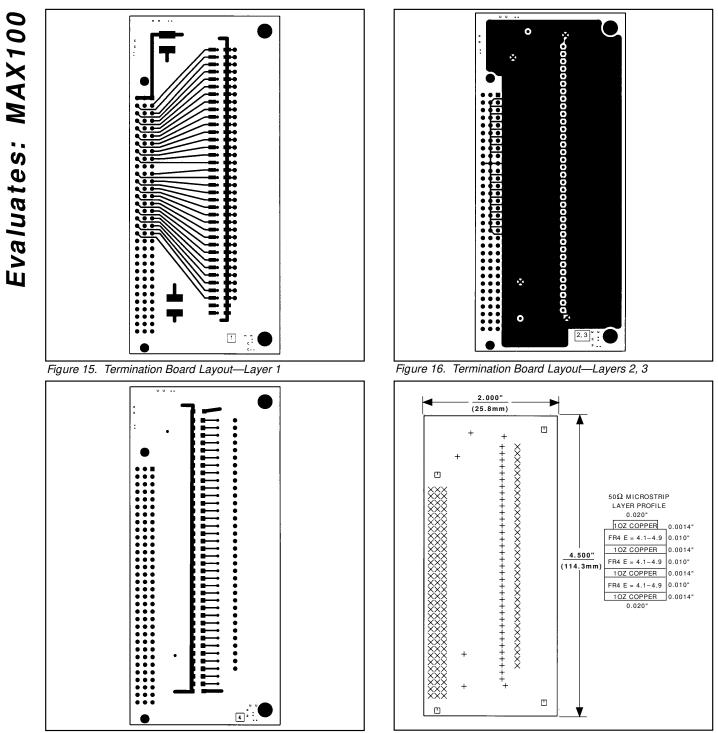

Use transmission lines for the analog input and for the high-speed digital outputs. The MAX100 EV kit uses  $50\Omega$  microstrip lines that occupy layers 1 and 2, and

FR4 epoxy dielectric material with a relative dielectric constant between 4.1 and 4.9. The nominal design has a foil thickness of 0.0014 inch (0.0355 mm) for layer 1 (the signal layer) and 0.0014 inch (0.0355 mm) for layer 2 (the ground return). Dieletric thickness between layers is nominally 0.011 inch (0.28 mm), with a signal trace width of 0.020 inch (0.50 mm). Refer to Motorola's MECL<sup>™</sup> or ECLinPS<sup>™</sup> data book for an introduction to microstrip design.

Due to the high-speed nature of this part, the propagation delay of the PC board traces becomes a significant design consideration. For the EV kit design, the propagation delay is approximately 145ps per inch (5.7ps/mm). For best results, try to match the lengths of the data traces to within 0.5 inch (12 mm). The EV kit board matches the data-bus lengths by using curved traces on layer 6. A computer-aided design system can be helpful in measuring the trace lengths accurately. The clock signal must be routed on one layer only, without using any throughhole vias. The MAX100 EV kit is a controlled-impedance board (50 $\Omega$ ) and has a total board thickness of 0.062 inches (1.57 mm) using six copper layers (Figure 3).

### Testing

We recommend that a digital acquisition instrument like the HP8000 logic analyzer be used to acquire and process the output data. At Maxim, the data acquired from the converter is evaluated in an effective-bits software program developed in-house. The effective-bits measurement is a good tool to determine and compare ADC accuracy.

### \_Calibration Procedure

The MAX100 EV kit comes ready to operate from the factory. If other devices are to be used in the same fixture, the EV kit should be recalibrated according to the following procedure:

- 1) With the ADC removed, adjust the +5V and -5.2V supplies.

- Set the mode-select options (A=B, DIV, MOD) for the desired operation using the on-board DIP switches. See Table 1.

- 3) With the power off, insert the MAX100. The MAX100's heatsink fits down through the board with the device leads resting on top. Be sure to place the part in the board with pin 1 in the correct location. Provide at least 200 lineal feet per minute airflow whenever power is applied. Turn on the power supplies with -5.2V first, then the +5V. The -5.2V power supply should be the first supply turned on and the last supply turned off.

™ MECL and ECLinPS are trademarks of Motorola Corp.

### AIN+\*\* AIN-\*\* OUTPUT (MSB INPUT (mV) (mV) CODE TO LSB) +135 -135 Full scale 11111111 Differential 0 0 10000000 Mid scale

+135

0

0

0

Table 1. Input Voltage Range

-135

+270

-270

0

Single-

Ended

\*\* An offset, VIO, as specified in the DC Electrical

*Characteristics,* is present at the input. Compensate for this offset either by adjusting the reference voltage VA<sub>RT</sub>, VA<sub>RB</sub>, or by introducing an offset voltage in one of the input terminals, AIN+ or AIN-.

0000000

11111111

1000000

00000000

Zero scale

Full scale

Mid scale

Zero scale

### Table 2. Output-Mode Control

| DIV   | MOD              | A = B  | DCLK*  | DESCRIPTION                                                                                                                                                                 |  |

|-------|------------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Divid | Divide-by-1 Mode |        |        |                                                                                                                                                                             |  |

| 0     | х                | 0      | 250MHz | Data appears on AData only.<br>BData port inactive (see<br>Figure 3 of MAX100 data sheet).                                                                                  |  |

| 0     | х                | 1      | 250MHz | AData identical to BData (see<br>Figure 3 of MAX100 data sheet).                                                                                                            |  |

| Divid | de-by-2          | 2 Mode |        |                                                                                                                                                                             |  |

| 1     | 0                | 0      | 125MHz | 8:16 demux mode. AData and<br>BData ports are active. BData<br>carries older sample and AData<br>carries most recent sample (see<br>Figure 4 of MAX100 data sheet).         |  |

| 1     | 0                | 1      | 125MHz | AData and BData ports are<br>active. Both carry identical sam-<br>pled data. Alternate samples are<br>taken but discarded.                                                  |  |

| Divid | Divide-by-5 Mode |        |        |                                                                                                                                                                             |  |

| 1     | 1                | 0      | 50MHz  | AData port updates data on 5th<br>input CLK. BData port inactive.<br>The other four sampled data<br>points are discarded.                                                   |  |

| 1     | 1                | 1      | 50MHz  | AData and BData ports are both<br>active with identical data. Data<br>is updated on output ports every<br>fifth input clock (CLK). The other<br>four samples are discarded. |  |

\* Input clocks (CLK, CLK) = 250MHz for all above combinations. In divide-by-2 or divide-by-5 mode, the output clock DCLK is always a 50% duty-cycle signal. In divide-by-1 mode, DCLK has the same duty cycle as CLK.

- 4) After the part has warmed up for several minutes, adjust the reference voltages to  $\pm 1.02V$  nominally. The test points for these voltages are at the bottom of the sense resistors, R13 and R16, located just above the sense pins VARTS and VARBS (Figure 4).

- Adjust mid-code level. With no analog input (AIN+ -(AIN-) = 0V) the output code should match that specified in Table 1. If there is an offset, adjust either the positive or negative reference until the expected code

of 10 00 00 (MSB to LSB) is achieved. After adjusting to the proper level, the references need to be balanced to  $\pm 1.02V$  around any offset that was introduced. (If the negative reference was moved by +32mV, the positive reference must be moved by that same amount to ensure the correct LSB size.) It may be necessary to repeat the reference offset adjustment again after the correct 2.04V differential reference voltage is re-established around the common-mode offset.

Figure 1. MAX100 EV Kit Schematic

M/IXI/M

5

Figure 1. MAX100 EV Kit Schematic (continued)

-50Ω

FFCLK

18

17

14

13

12

Q2

Q2 16

vcc 15

Q1

<u>Q1</u>

Q0

÷

U9

VEE

VAA

GND

Figure 1. MAX100 EV Kit Schematic (continued)

Figure 2. Evaluation Kit Timing

M/IXI/M

| Copper Layer 1                                               | Copper thickness = 0.0014" (1 oz copper) |  |

|--------------------------------------------------------------|------------------------------------------|--|

| Epoxy FR4                                                    | Dielectric layer thickness = 0.01072"    |  |

| Copper Layer 2                                               | Copper thickness = 0.0014" (1 oz copper) |  |

| Epoxy FR4                                                    | Dielectric layer thickness = 0.01072"    |  |

| Copper Layer 3                                               | Copper thickness = 0.0014" (1 oz copper) |  |

| Epoxy FR4                                                    | Dielectric layer thickness = 0.01072"    |  |

| Copper Layer 4                                               | Copper thickness = 0.0014" (1 oz copper) |  |

| Epoxy FR4                                                    | Dielectric layer thickness = 0.01072"    |  |

| Copper Layer 5                                               | Copper thickness = 0.0014" (1 oz copper) |  |

| Epoxy FR4 Dielectric layer thickness = 0.01072"              |                                          |  |

| Copper Layer 6                                               | Copper thickness = 0.0014" (1 oz copper) |  |

| Microstrip traces are 20 mils wide for $50\Omega$ impedance. |                                          |  |

Figure 3. Layer Profile

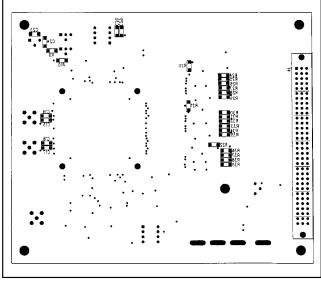

Figure 5. Main Board Component Placement Guide-Solder Side

# MAX100 Evaluation Kit

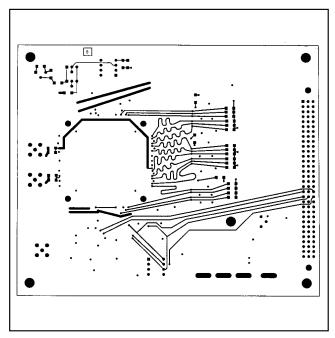

Figure 4. Main Board Component Placement Guide-Component Side

Figure 6. Main Board Layout—Copper Layer 1 (Top)

Figure 7. Main Board Layout—Copper Layer 2 (negative image)

*Figure 9. Main Board Layout—Copper Layer 4 (negative image)*

Figure 8. Main Board Layout—Copper Layer 3 (negative image)

Figure 10. Main Board Layout—Copper Layer 5 (negative image)

Figure 11. Main Board Layout—Copper Layer 6 (Bottom)

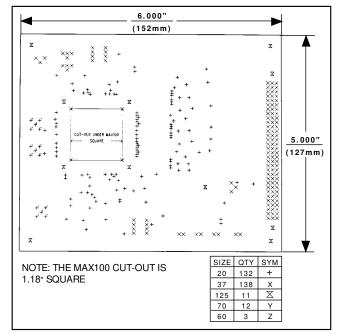

Figure 12. Main Board Mechanical Outline

Figure 13. Termination Board Component Placement Guide and Signal Connections—Component Side

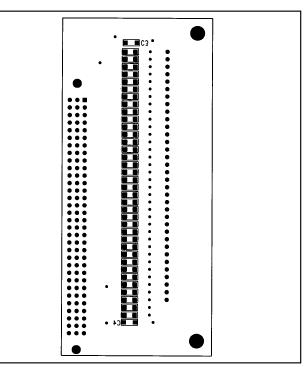

Figure 14. Termination Board Component Placement Guide—Solder Side

# Evaluates: MAX100

### MIXI/M \_

Figure 17. Termination Board Layout—Layer 4 (Bottom)

Figure 18. Termination Board Mechanical Guide

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

### \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1994 Maxim Integrated Products

12

Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.