## P2954; Rev 1; 1/04 EVALUATION KIT AVAILABLE 4MHz, 500mA Synchronous Step-Down DC-DC Converters in Thin SOT and TDFN

# **General Description**

The MAX8560/MAX8561/MAX8562 step-down DC-DC converters are optimized for applications that prioritize small size and high efficiency. They utilize a proprietary hysteretic-PWM control scheme that switches with fixed frequency and is adjustable up to 4MHz, allowing customers to trade efficiency for smaller external components. Output current is guaranteed up to 500mA, while quiescent current is only 40µA (typ).

Internal synchronous rectification greatly improves efficiency and eliminates the external Schottky diode required in conventional step-down converters. Built-in soft-start eliminates inrush current to reduce input capacitor requirements. The MAX8561 features logiccontrolled output voltage, while the MAX8562 drives an external bypass FET.

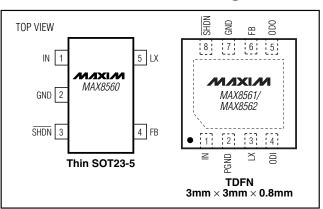

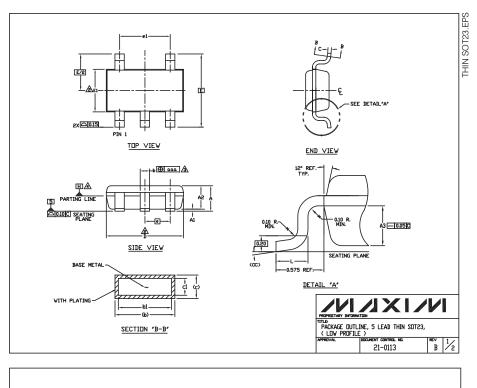

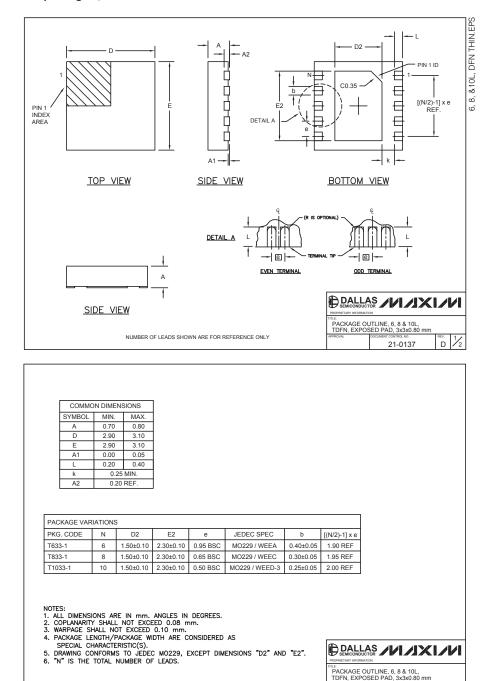

The MAX8560 is available in a 5-pin Thin SOT23 package. The MAX8561/MAX8562 are available in spacesaving 8-pin 3mm x 3mm Thin DFN packages.

## **\_Features**

- Up to 4MHz PWM Switching Frequency

- 500mA Guaranteed Output Current

- ♦ 40µA (typ) Quiescent Current

- Adjustable Output Voltage from 0.6V to 2.5V

- Logic-Controlled Output Voltage (MAX8561)

- Drives External Bypass FET (MAX8562)

- ±1.5% Initial Accuracy

- Soft-Start Eliminates Inrush Current

- ♦ Fast Voltage-Positioning Transient Response

- Internal Synchronous Rectifier

- ♦ 2.7V to 5.5V Input

- ♦ 0.1µA Logic-Controlled Shutdown

- Thermal Shutdown

- Thin SOT23 or Space-Saving 3mm x 3mm x 0.8mm TDFN Packages

## \_Ordering Information

| PART         | TEMP RANGE     | PIN-PACKAGE    | TOP<br>MARK |

|--------------|----------------|----------------|-------------|

| MAX8560EZK-T | -40°C to +85°C | 5 Thin SOT23-5 | ADRX        |

| MAX8561ETA   | -40°C to +85°C | 8 TDFN         | AHD         |

| MAX8562ETA   | -40°C to +85°C | 8 TDFN         | AHE         |

## Microprocessor/DSP Core Supplies

**Applications**

Cellular and Smart Phones

CDMA/RF Power-Amplifier Supplies PDAs, DSC, and MP3 Players

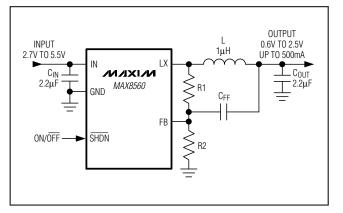

# **Typical Operating Circuit**

# Pin Configurations

##

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| IN, FB, SHDN, ODI, ODO to GND | -0.3V to +6V                     |

|-------------------------------|----------------------------------|

| LX to GND (Note 1)            | 0.3V to (V <sub>IN</sub> + 0.3V) |

| PGND to GND                   | -0.3V to +0.3V                   |

| LX Current                    | 1.27A                            |

| Output Chart Circuit to CND   |                                  |

| (typical operating circuit)10                         | )s |

|-------------------------------------------------------|----|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |    |

| 5-Pin Thin SOT23 (derate 9.1mW/°C above +70°C)727mV   | Ν  |

8-Pin TDFN (derate 24.4mW/°C above +70°C) .........1951mW

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Note 1: LX has internal clamp diodes to PGND (GND for MAX8560) and IN. Applications that forward bias these diodes should take care not to exceed the IC's package power-dissipation limits.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 3.6V, \overline{SHDN} = IN, T_A = -40^{\circ}C$  to +85°C, typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                                  | SYMBOL           | CONDITIONS                                                                                             |                                               | MIN  | ТҮР    | MAX  | UNITS |  |

|------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|--------|------|-------|--|

| Supply Voltage Range                                       | VIN              |                                                                                                        |                                               | 2.7  |        | 5.5  | V     |  |

| UVLO Threshold                                             | UVLO             | V <sub>IN</sub> rising, 60mV h                                                                         | ysteresis                                     | 2.4  | 2.5    | 2.6  | V     |  |

|                                                            |                  | I <sub>LOAD</sub> = 0mA, no s                                                                          | witching                                      |      | 40     | 80   |       |  |

| Supply Current                                             | lin              | SHDN = GND                                                                                             | $T_A = +25^{\circ}C$                          |      | 0.01   | 0.1  | μA    |  |

|                                                            |                  |                                                                                                        | $T_A = +85^{\circ}C$                          |      | 0.1    |      | 1     |  |

| Output Voltage Range                                       | Vout             |                                                                                                        |                                               | 0.6  |        | 2.5  | V     |  |

| FB Threshold Voltage                                       | V <sub>FB</sub>  | V <sub>FB</sub> falling                                                                                |                                               |      | 0.6    |      | V     |  |

| FB Threshold Line Regulation                               |                  | $V_{IN} = 2.7V$ to 5.5V                                                                                |                                               |      | 0.3    |      | %/V   |  |

| FB Threshold Load Regulation                               |                  | $I_{OUT} = 0$ to 500mA                                                                                 | l                                             |      | -0.001 |      | %/mA  |  |

| FB Threshold Voltage Accuracy                              |                  |                                                                                                        | $T_A = +25^{\circ}C$                          | -1.5 |        | +1.5 | 0/    |  |

| (Falling) (% of V <sub>FB</sub> )                          |                  | $I_{LOAD} = 0mA$                                                                                       | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | -2.5 |        | +2.5 | %     |  |

| FB Threshold Voltage Hysteresis<br>(% of V <sub>FB</sub> ) | V <sub>HYS</sub> |                                                                                                        |                                               |      | 1.0    |      | %     |  |

|                                                            |                  | $\overline{\text{SHDN}}$ = GND, T <sub>A</sub> = +25°C, V <sub>IN</sub> = 5.5V                         |                                               |      | 0.01   | 0.1  | μA    |  |

|                                                            | I <sub>FB</sub>  | $\overline{\text{SHDN}} = \text{GND}, T_{\text{A}} = +85^{\circ}\text{C}, V_{\text{IN}} = 5.5\text{V}$ |                                               |      | 0.1    |      |       |  |

| FB Bias Current                                            |                  | $V_{FB} = 0.5V, T_A = +25^{\circ}C, V_{IN} = 5.5V$                                                     |                                               |      | 0.01   | 0.1  |       |  |

|                                                            |                  | V <sub>FB</sub> = 0.5V, T <sub>A</sub> = +                                                             | -85°C, V <sub>IN</sub> = 5.5V                 |      | 0.1    |      | 1     |  |

| Logic Input High Voltage<br>(SHDN, ODI)                    | VIH              | V <sub>IN</sub> = 2.7V to 5.5V                                                                         |                                               | 1.41 |        |      |       |  |

| Logic Input Low Voltage<br>(SHDN, ODI)                     | VIL              | V <sub>IN</sub> = 2.7V to 5.5V                                                                         |                                               |      |        | 0.4  | V     |  |

|                                                            |                  | $V_{IN} = 5.5V$ , $\overline{SHDN} = ODI = GND$ or IN,<br>T <sub>A</sub> = +25°C                       |                                               |      | 0.001  | 0.1  |       |  |

| Logic Input Bias Current                                   | lih, li∟         | $V_{IN} = 5.5V, \overline{SHDN}$<br>$T_A = +85^{\circ}C$                                               | = ODI = GND or IN,                            |      | 0.01   |      | μA    |  |

| ODO Output Low Voltage<br>(MAX8562 Only)                   | V <sub>OL</sub>  | 1mA sink current, V <sub>IN</sub> = 2.7V                                                               |                                               |      | 0.02   | 0.1  | V     |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 3.6V, \overline{SHDN} = IN, T_A = -40^{\circ}C$  to +85°C, typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                       | SYMBOL             | CONDITIONS                                                                        | MIN     | ТҮР  | МАХ  | UNITS |  |

|---------------------------------|--------------------|-----------------------------------------------------------------------------------|---------|------|------|-------|--|

| ODO Pullup to IN (MAX8562 Only) |                    |                                                                                   | 5       | 10   | 20   | kΩ    |  |

| Open Drein Output Leekege       |                    | $V_{IN} = 5.5V$ , ODO = IN, $T_A = +25^{\circ}C$                                  |         | 0.01 | 0.1  |       |  |

| Open-Drain Output Leakage       | IOHLEAK            | $V_{IN} = 5.5V, ODO = IN, T_A = +85^{\circ}C$                                     |         | 0.1  |      | μA    |  |

| Current Limit                   | ILIMP              | PFET switch                                                                       | 600     | 990  | 1500 |       |  |

|                                 | ILIMN              | NFET rectifier                                                                    | 490     | 680  | 900  | mA    |  |

| On Registeres                   | Ronp               | PFET switch, $I_{LX} = -40mA$                                                     | 0.8 1.5 |      |      |       |  |

| On-Resistance                   | Ronn               | NFET rectifier, $I_{LX} = +40mA$                                                  |         | 0.4  | 0.82 | Ω     |  |

| Rectifier-Off Current Threshold | I <sub>LXOFF</sub> |                                                                                   | 0       | 30   | 60   | mA    |  |

|                                 |                    | $V_{IN} = 5.5V$ , LX = GND to IN, ODO = IN,<br>T <sub>A</sub> = +25°C, SHDN = GND |         | 0.1  | 1    |       |  |

| LX Leakage Current              | ILXLKG             | $V_{IN} = 5.5V$ , LX = GND to IN, ODO = IN,<br>T <sub>A</sub> = +85°C, SHDN = GND |         | 1    |      | μA    |  |

| Minimum On- and Off-Times       | ton(min)           |                                                                                   |         | 107  |      |       |  |

| Minimum On- and On-Times        | toff(MIN)          |                                                                                   |         | 95   |      | ns    |  |

| Thermal Shutdown                |                    |                                                                                   |         | +160 |      | °C    |  |

| Thermal-Shutdown Hysteresis     |                    |                                                                                   |         | 20   |      | °C    |  |

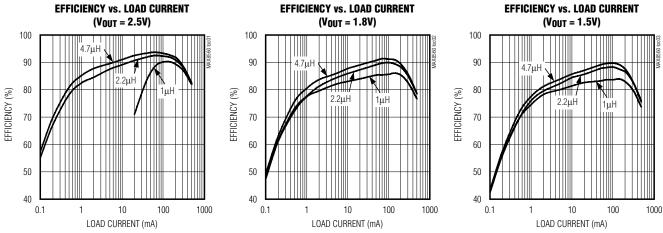

Typical Operating Characteristics

(VIN = 3.6V, V<sub>OUT</sub> = 1.2V, L = 1μH (LQH32CN1R0M53), C<sub>OUT</sub> = 2.2μF, T<sub>A</sub> = +25°C, unless otherwise noted.)

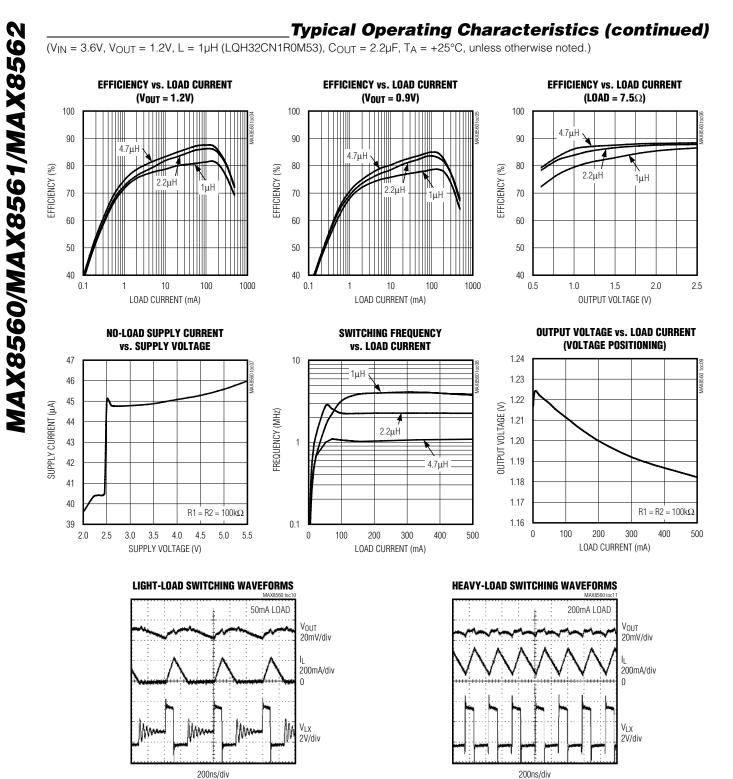

# **Typical Operating Characteristics (continued)**

(V<sub>IN</sub> = 3.6V, V<sub>OUT</sub> = 1.2V, L = 1 $\mu$ H (LQH32CN1R0M53), C<sub>OUT</sub> = 2.2 $\mu$ F, T<sub>A</sub> = +25°C, unless otherwise noted.)

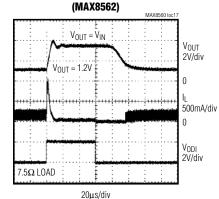

LOAD-TRANSIENT RESPONSE MXX5550 to:15 VOUT 500mV/div L 500mA/div 20mA LOAD 20mA LOAD 2us/div

40µs/div

BYPASS-FET TRANSIENT RESPONSE

**Pin Description**

| P       | PIN                |      |                                                                                                                                                                                                                                                                |  |  |  |

|---------|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX8560 | MAX8561<br>MAX8562 | NAME | FUNCTION                                                                                                                                                                                                                                                       |  |  |  |

| 1       | 1                  | IN   | Supply Voltage Input. 2.7V to 5.5V. Bypass with a 2.2 $\mu F$ ceramic capacitor as close as possible to the IN and GND pins.                                                                                                                                   |  |  |  |

| 2       | 7                  | GND  | Ground                                                                                                                                                                                                                                                         |  |  |  |

| 3       | 8                  | SHDN | Active-Low Shutdown Input. Connect to IN or logic high for normal operation. Connect to GND or logic low for shutdown mode.                                                                                                                                    |  |  |  |

| 4       | 6                  | FB   | Voltage Feedback Input. FB regulates to 0.6V nominal. Connect FB to the center of an external resistive divider (see the <i>Setting the Output Voltage</i> section).                                                                                           |  |  |  |

| _       | 2                  | PGND | Power Ground. Must connect to GND.                                                                                                                                                                                                                             |  |  |  |

| 5       | 3                  | LX   | Inductor connection to the drains of the internal P-channel and N-channel MOSFETs.                                                                                                                                                                             |  |  |  |

| —       | 5                  | ODO  | Auxiliary Open-Drain Output                                                                                                                                                                                                                                    |  |  |  |

| _       | 4                  | ODI  | Digital Input for Open-Drain MOSFET. Connect to IN or logic high to internally pull ODO low (and force the MAX8562 into 100% duty cycle). Connect to GND or logic low to force ODO to high impedance (MAX8561) or $10k\Omega$ pullup from ODO to IN (MAX8562). |  |  |  |

| _       | EP                 | EP   | Exposed Pad. Connect to GND.                                                                                                                                                                                                                                   |  |  |  |

# **Detailed Description**

The MAX8560/MAX8561/MAX8562 step-down converters deliver a guaranteed 500mA at output levels from 0.6V to 2.5V. They use a proprietary hysteretic-PWM control scheme that switches up to 4MHz, allowing a trade-off between efficiency and tiny external components. At light loads below 100mA, the MAX8560/MAX8561/MAX8562 automatically switch to pulse-skipping mode to keep quiescent supply current as low as 40µA (typ).

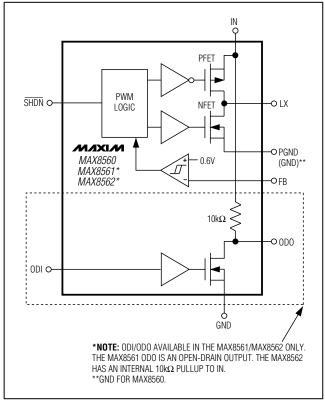

#### **Control Scheme**

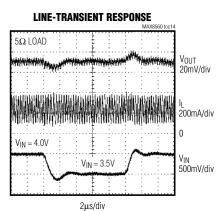

A proprietary hysteretic-PWM control scheme ensures high efficiency, fast switching, fast transient response, low output ripple, and physically tiny external components. This control scheme is simple: when the output voltage falls below the regulation threshold, the error comparator begins a switching cycle by turning on the high-side switch. This switch remains on until the minimum on-time expires and the output voltage is in regulation or the current-limit threshold is exceeded. Once off, the high-side switch remains off until the minimum off-time expires and the output voltage falls again, below the regulation threshold. During this period, the low-side synchronous rectifier turns on and remains on until either the high-side switch turns on again or the inductor current approaches zero. The internal synchronous rectifier eliminates the need for an external Schottky diode.

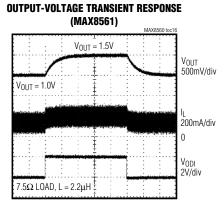

**Voltage-Positioning Load Regulation** As seen in the *Typical Operating Circuit*, the MAX8560/MAX8561/MAX8562 use a unique feedback network. By taking feedback from the LX node through R1, the usual phase lag due to the output capacitor is removed, making the loop exceedingly stable and allowing the use of a very small ceramic output capacitor. This configuration causes the output voltage to shift by the inductor series resistance multiplied by the load current. This voltage-positioning load regulation greatly reduces overshoot during load transients, which effectively halves the peak-to-peak output-voltage excursions compared to traditional step-down converters. See the Load Transient Response graph in the *Typical Operating Characteristics* section.

#### Shutdown Mode

Connecting SHDN to GND or logic low places the MAX8560/MAX8561/MAX8562 in shutdown mode and reduces supply current to 0.1 $\mu$ A. In shutdown, the control circuitry, internal-switching P-channel MOSFET, and synchronous rectifier (N-channel MOSFET) turn off and LX becomes high impedance. Connect SHDN to IN or logic high for normal operation.

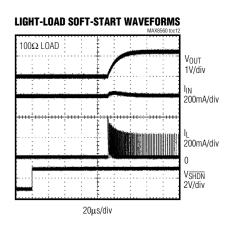

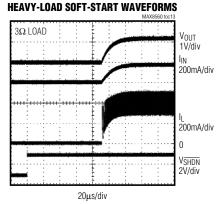

#### Soft-Start

The MAX8560/MAX8561/MAX8562 have internal softstart circuitry that eliminates inrush current at startup, reducing transients on the input source. Soft-start is particularly useful for higher impedance input sources, such as Li+ and alkaline cells. See the Soft-Start and Shutdown Response graphs in the *Typical Operating Characteristics* section.

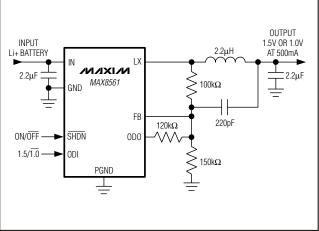

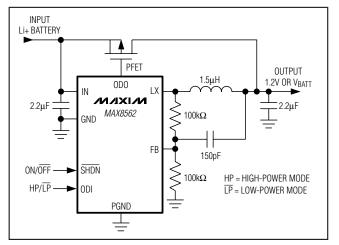

#### **Open-Drain Output**

The 8-pin TDFN versions, the MAX8561 and MAX8562, include an extra, internal, open-drain N-channel MOSFET switch that can save an additional package in space-constrained applications. The open drain is connected to ODO, while the gate is controlled by a digital input at ODI. For the MAX8561, this circuit can be used to toggle between two regulated output voltages, as in Figure 2. For the MAX8562, a 10k $\Omega$  resistor pulls ODO up to IN when ODI is low, and the buck converter is forced into 100% duty cycle when ODI is high. This makes the MAX8562 ideal for driving an external bypass PFET for high-power mode in CDMA cell phones, as in Figure 3.

## **Applications Information**

The MAX8560/MAX8561/MAX8562 are optimized for use with tiny inductors and small ceramic capacitors. The correct selection of external components, especially CFF, ensures high efficiency, low output ripple, and fast transient response.

#### Setting the Output Voltage

Select an output voltage between 0.6V and 2.5V by connecting FB to a resistive voltage-divider between LX and GND (see the *Typical Operating Circuit*). Choose R2 for a reasonable bias current in the resistive divider. A wide range of resistor values is acceptable, but a good starting point is to choose R2 as  $100k\Omega$ . Then, R1 is given by:

$$R1 = R2\left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

where  $V_{FB} = 0.6V$ .

Figure 1. Simplified Functional Diagram

#### **Inductor Selection**

The MAX8560/MAX8561/MAX8562 operate with inductors of 1µH to 4.7µH. Low inductance values are smaller but require faster switching, which results in some efficiency loss. See the *Typical Operating Characteristics* section for efficiency and switching frequency vs. inductor value. The inductor's DC current rating only needs to match the maximum load current of the application + 50mA because the MAX8560/MAX8561/ MAX8562 feature zero current overshoot during startup and load transients.

For output voltages above 2.0V, when light-load efficiency is important, the minimum recommended inductor is 2.2µH. For optimum voltage-positioning load transients, choose an inductor with DC series resistance in the 50m $\Omega$  to 150m $\Omega$  range. For higher efficiency at heavy loads (above 200mA) or minimal load regulation (but some transient overshoot), the resistance should be kept below 100m $\Omega$ . For light-load applications up to 200mA, much higher resistance is acceptable with very little impact on performance.

Figure 2. Using ODI/ODO to Obtain Two Output Voltages from the MAX8561

### **Capacitor Selection**

#### **Output Capacitor**

The output capacitor,  $C_{OUT}$ , is required to keep the output voltage ripple small and to ensure regulation loop stability.  $C_{OUT}$  must have low impedance at the switching frequency. Ceramic capacitors with X5R or X7R dielectrics are highly recommended due to their small size, low ESR, and small temperature coefficients. Due to the unique feedback network, the output capacitance can be very low. For most applications, a 2.2µF capacitor is sufficient. For optimum load-transient performance and very low output ripple, the output capacitor value in µFs should be equal to or larger than the inductor value in µHs.

#### Input Capacitor

The input capacitor, C<sub>IN</sub>, reduces the current peaks drawn from the battery or input power source and reduces switching noise in the IC. The impedance of C<sub>IN</sub> at the switching frequency should be kept very low. Ceramic capacitors with X5R or X7R dielectrics are highly recommended due to their small size, low ESR, and small temperature coefficients. Due to the MAX8560/MAX8561/MAX8562s' soft-start, the input capacitance can be very low. For most applications, a  $2.2\mu$ F capacitor is sufficient.

Figure 3. Using the MAX8562 to Control an External Bypass PFET for a Two-Step  $V_{CC}$  in CDMA-PA Applications

#### Feed-Forward Capacitor

The feed-forward capacitor, CFF, sets the feedback loop response, controls the switching frequency, and is critical in obtaining the best efficiency possible. Choose a small ceramic X7R capacitor with a value given by:

$$C_{FF} = \frac{L}{R1} \times 10$$

Siemens

Select the closest standard value to CFF as possible.

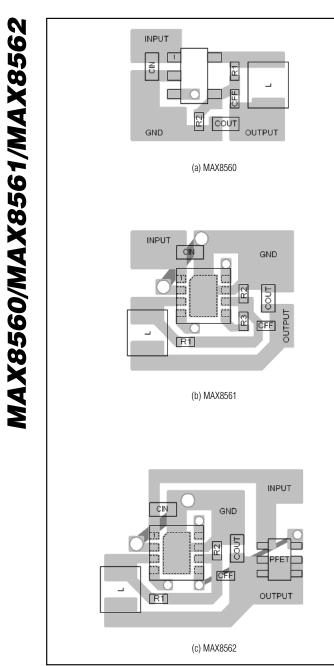

#### PC Board Layout and Routing

High switching frequencies and relatively large peak currents make the PC board layout a very important part of design. Good design minimizes excessive EMI on the feedback paths and voltage gradients in the ground plane, both of which can result in instability or regulation errors. Connect C<sub>IN</sub> close to IN and GND. Connect the inductor and output capacitor as close to the IC as possible and keep their traces short, direct, and wide. Connect GND and PGND separately to the ground plane. The external feedback network should be very close to the FB pin, within 0.2in (5mm). Keep noisy traces, such as the LX node, as short as possible. For the 8-pin TDFN package, connect GND to the exposed paddle directly under the IC. Figure 4 illustrates an example PC board layout and routing scheme.

## **Table 1. Suggested Inductors**

| MANUFACTURER | SERIES    | INDUCTANCE<br>(µH)              | ESR<br>(Ω)                           | CURRENT RATING<br>(mA)          | DIMENSIONS                                      |

|--------------|-----------|---------------------------------|--------------------------------------|---------------------------------|-------------------------------------------------|

|              | LB2012    | 1.0<br>2.2                      | 0.15<br>0.23                         | 300<br>240                      | $2.0 \times 1.25 \times 1.45 = 3.6 \text{mm}^3$ |

|              | LB2016    | 1.0<br>1.5<br>2.2<br>3.3        | 0.09<br>0.11<br>0.13<br>0.20         | 455<br>350<br>315<br>280        | 2.0 x 1.6 x 1.8 = 5.8mm <sup>3</sup>            |

| Taiyo Yuden  | LB2518    | 1.0<br>1.5<br>2.2<br>3.3        | 0.06<br>0.07<br>0.09<br>0.11         | 500<br>400<br>340<br>270        | 2.5 x 1.8 x 2.0 = 9mm <sup>3</sup>              |

|              | LBC2518   | 1.0<br>1.5<br>2.2<br>3.3<br>4.7 | 0.08<br>0.11<br>0.13<br>0.16<br>0.20 | 775<br>660<br>600<br>500<br>430 | 2.5 x 1.8 x 2.0 = 9mm <sup>3</sup>              |

|              | LQH31C_03 | 1.0                             | 0.28                                 | 510                             | $3.2 \times 1.6 \times 2.0 = 10 \text{mm}^3$    |

| Murata       | LQH32C_53 | 1.0<br>2.2<br>4.7               | 0.06<br>0.10<br>0.15                 | 1000<br>790<br>650              | 3.2 x 2.5 x 1.7 = 14mm <sup>3</sup>             |

|              | LQM43FN   | 2.2<br>4.7                      | 0.10<br>0.17                         | 400<br>300                      | $4.5 \times 3.2 \times 0.9 = 13 \text{mm}^3$    |

|              | D310F     | 1.5<br>2.2<br>3.3               | 0.13<br>0.17<br>0.19                 | 1230<br>1080<br>1010            | 3.6 x 3.6 x 1.0 = 13mm <sup>3</sup>             |

| ТОКО         | D312C     | 1.5<br>2.2<br>2.7<br>3.3        | 0.10<br>0.12<br>0.15<br>0.17         | 1290<br>1140<br>980<br>900      | 3.6 x 3.6 x 1.2 = 16mm <sup>3</sup>             |

| Sumida       | CDRH2D11  | 1.5<br>2.2<br>3.3<br>4.7        | 0.05<br>0.08<br>0.10<br>0.14         | 900<br>780<br>600<br>500        | 3.2 x 3.2 x 1.2 = 12mm <sup>3</sup>             |

Figure 4. Recommended PC Board Layout

Chip Information

TRANSISTOR COUNT: 1271 PROCESS: BICMOS

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- \*D" AND "E1" ARE REFERENCE DATUM AND DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS, AND ARE MEASURED AT THE BOTTOM PARTING LINE. MOLD FLASH OR PROTRUSION SHALL NOT EXCEED 0.15mm ON "D" AND 0.25mm ON "E" PER SIDE.

- THE LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.07mm TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION.

- A datum plane "H" located at mold parting line and coincident with lead, where lead exits plastic body at the bottom of parting line.

- ☆ THE LEAD TIPS MUST LINE WITHIN A SPECIFIED TOLERANCE ZONE. THIS TOLERANCE ZONE IS DEFINED BY TWO PARALLEL LINES. ONE PLANE IS THE SEATING PLANE, DATUM [-C-]; AND THE OTHER PLANE IS AT THE SPECIFIED DISTANCE FROM [-C-] IN THE DIRECTION INDICATED. FORMED LEADS SHALL BE PLANAR WITH RESPECT TO ONE ANOTHER WITH 0.10mm AT SEATING PLANE.

- THIS PART IS COMPLIANT WITH JEDEC SPECIFICATION MO-193 EXCEPT FOR THE "e" DIMENSION WHICH IS 0.95Mmm INSTEAD OF 1.00mm. THIS PART IS IN FULL COMPLIANCE TO EIAJ SPECIFICATION SC-74.

|     | SYMB        | OLS      |      |  |  |  |  |

|-----|-------------|----------|------|--|--|--|--|

|     | MIN NOM MAX |          |      |  |  |  |  |

| A   | -           | -        | 1.10 |  |  |  |  |

| A1  | 0.05        | 0.075    | 0.10 |  |  |  |  |

| A2  | 0.85        | 0.88     | 0.90 |  |  |  |  |

| A3  |             | 0.50 BSC |      |  |  |  |  |

| ю   | 0.30        | -        | 0.45 |  |  |  |  |

| b1  | 0.25        | 0.35     | 0.40 |  |  |  |  |

| с   | 0.15        | -        | 0.20 |  |  |  |  |

| c1  | 0.12        | 0.127    | 0.15 |  |  |  |  |

| D   | 2.80        | 2.90     | 3.00 |  |  |  |  |

| E   | 2.75 BSC    |          |      |  |  |  |  |

| E1  | 1.55        | 1.60     | 1.65 |  |  |  |  |

| L   | 0.30        | 0.40     | 0.50 |  |  |  |  |

| e1  | 1.90 BSC    |          |      |  |  |  |  |

| e   | 0.95 BSC    |          |      |  |  |  |  |

| 20  | 0-          | 4-       | 8-   |  |  |  |  |

| ممم | 0.20        |          |      |  |  |  |  |

## \_Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

12

Printed USA

**MAXIM** is a registered trademark of Maxim Integrated Products.

21-0137

D 2/2