RoHS V

# FRACTIONAL-N PLL WITH INTEGRATED VCO 1025 - 1150, 2050 - 2300, 4100 - 4600 MHz

## Absolute Maximum Ratings

| AVDD, RVDD, DVDD3V, VCCPD, VCCHF, VCCPS                           | -0.3V to +3.6V |  |  |  |

|-------------------------------------------------------------------|----------------|--|--|--|

| VPPCP, VDDCP, VCC1                                                | -0.3V to +5.8V |  |  |  |

| VCC2                                                              | -0.3V to +5.5V |  |  |  |

| Operating Temperature                                             | -40°C to +85°C |  |  |  |

| Storage Temperature                                               | -65°C to 125°C |  |  |  |

| Maximum Junction Temperature                                      | 125 °C         |  |  |  |

| Thermal Resistance (R <sub>TH</sub> ) (junction to ground paddle) | 20 °C/W        |  |  |  |

| Reflow Soldering                                                  |                |  |  |  |

| Peak Temperature                                                  | 260°C          |  |  |  |

| Time at Peak Temperature                                          | 40 sec         |  |  |  |

| ESD Sensitivity (HBM)                                             | Class 1B       |  |  |  |

v00.1210

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

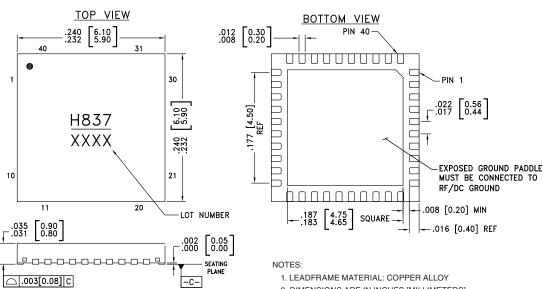

### **Outline Drawing**

- 2. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 3. LEAD SPACING TOLERANCE IS NON-CUMULATIVE

- 4. PAD BURR LENGTH SHALL BE 0.15mm MAXIMUM. PAD BURR HEIGHT SHALL BE 0.05mm MAXIMUM.

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm.

- 6. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

- 7. REFER TO HITTITE APPLICATION NOTE FOR SUGGESTED PCB LAND PATTERN.

## Package Information

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating | Package Marking [1] |

|-------------|----------------------------------------------------|---------------|------------|---------------------|

| HMC837LP6CE | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1       | H837<br>XXXX        |

[1] 4-Digit lot number XXXX

# FRACTIONAL-N PLL WITH INTEGRATED VCO 1025 - 1150, 2050 - 2300, 4100 - 4600 MHz

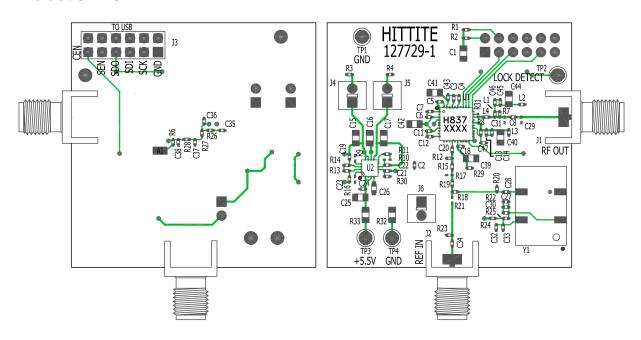

#### **Evaluation PCB**

v00.1210

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

### **Evaluation PCB Schematic**

To view this <u>Evaluation PCB Schematic</u> please visit <u>www.hittite.com</u> and choose HMC837LP6CE from the "Search by Part Number" pull down menu to view the product splash page.

#### **Evaluation Order Information**

| Item                | Contents                                                                                                                                                                                                                        | Part Number        |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Evaluation DCB Only | HMC837LP6CE F <sub>0</sub> /2 & F <sub>0</sub> Evaluation PCB                                                                                                                                                                   | EVAL01-HMC837LP6CE |

| Evaluation PCB Only | HMC837LP6CE 2xF <sub>0</sub> Evaluation PCB                                                                                                                                                                                     | EVAL02-HMC837LP6CE |

| Eurhalia Kit        | HMC837LP6CE F <sub>o</sub> /2 & F <sub>o</sub> Evaluation PCB USB Interface Board 6' USB A Male to USB B Female Cable CD ROM (Contains User Manual, Evaluation PCB Schematic, Evaluation Software, Hittite PLL Design Software) | 131995-HMC837LP6CE |

| Evaluation Kit      | HMC837LP6CE 2xF <sub>o</sub> Evaluation PCB USB Interface Board 6' USB A Male to USB B Female Cable CD ROM (Contains User Manual, Evaluation PCB Schematic, Evaluation Software, Hittite PLL Design Software)                   | 131997-HMC837LP6CE |

v00.1210

FRACTIONAL-N PLL WITH INTEGRATED VCO 1025 - 1150, 2050 - 2300, 4100 - 4600 MHz

v00.12

**ANALOG**DEVICES

Notes: