# AN1206: Differences between Si5342H/44H and Si5371/72

This document highlights the key differences between the highperformance Coherent Optics Jitter Attenuators Si5342H/44H products and the Si5371/72 products. Consult the data sheet and reference manual for more details.

In summary, the Si5371A/5371J (revision A) and Si5372A/5372J (revision A) are next generation versions of the Si5342H (revision D) and Si5344H (revision D).

The Si5371A and Si5372A both use an external reference crystal, like Si5342H and 44H; however, the Si5371J and Si5372J both use an internal reference crystal.

The Si5371/72 devices have the following improvements over 42H/44H:

- New Grade J has internal crystal reference (also available in Grade A with external crystal reference)

- · Lower jitter in high-speed integer mode

- · More clock inputs

- · Frequency-on-the-fly (FOTF) feature

- · Input clock switching improvements

- · Zero Delay Mode feature

- · New standard CMOS DC-coupled input

- Migrating from Si5342H/44H to Si5371/72

- · Drop-in compatible with Si5342H/44H

#### **KEY FEATURES**

- NEW Grade J option with internal crystal reference

- Lower high-speed integer mode jitter performance

- · Additional clock inputs

- · Frequency-on-the-fly feature

- · Input Clock Switching Improvements

- · Zero Delay Mode feature

- · New Standard CMOS DC-Coupled Input

- Easy migration from Si5342H/44H to Si5371/72

- Drop-in compatible with Si5342H/44H

# 1. New Features and Capabilities

This section provides details on the improvements made to the Si5371 and 5372 coherent optics jitter attenuating clocks.

#### 1.1 External and Internal Crystal Reference Options

Si5371 and 5372 are available in two grades. Grade A, which utilizes an external reference crystal (like Si5342H/44H) as well as the new Grade J, which utilizes an internal reference crystal. Both grades of the Si5371/72 are drop-in compatible to the Si5342H or Si5344H.

The internal reference uses a high-quality Japanese crystal which is prescreened for activity dips. The overall stability specification for the internal crystal includes initial accuracy, frequency characteristics across temperature, aging, reflow, and activity dips. See the data sheet for crystal specifications and details.

An additional benefit of the Grade J (internal crystal) is that the device takes up approximately 45 mm<sup>2</sup> less board area and does not require the PCB layer ground shield beneath the crystal compared to the Grade A (external crystal).

The Si5372 evaluation board is available in either the Grade A external crystal (Si5372A-A-EVB) or the Grade J internal crystal (Si5372J-A-EVB). Customers must specify the proper grade when ordering the evaluation board.

Table 1.1. Si5371 and Si5372 Ordering Guide

| Ordering Part                | Number of Input/ | Maximum Output Frequency |                       | Dackage                       | Deference |

|------------------------------|------------------|--------------------------|-----------------------|-------------------------------|-----------|

| Number (OPN)                 | Output Clocks    | High-Frequency Clock     | General-Purpose Clock | Package                       | Reference |

| Si5372                       |                  |                          |                       |                               |           |

| Si5372A-A-GM <sup>1, 2</sup> | 4/4              | 0.615 to 2.75 GHz        | 0.0001 to 717.5 MHz   | 44-QFN<br>7×7 mm              | External  |

| Si5372J-A-GM <sup>1, 2</sup> |                  |                          |                       | 44-LGA<br>7×7 mm              | Internal  |

| Si5371                       |                  |                          |                       |                               |           |

| Si5371A-A-GM <sup>1, 2</sup> | 4/2              | 0.615 to 2.75 GHz        | 0.0001 to 717.5 MHz   | 44-QFN<br>7×7 mm              | External  |

| Si5371J-A-GM <sup>1, 2</sup> |                  |                          |                       | 44-LGA<br>7×7 mm              | Internal  |

| Si5372 Evaluation Board      |                  |                          |                       |                               |           |

| Si5372A-A-EVB                | 4-output         | _                        | _                     | 44-QFN<br>Evaluation<br>Board | External  |

| Si5372J-A-EVB                | 4-output         | _                        | _                     | 44-LGA<br>Evaluation<br>Board | Internal  |

#### Notes:

- Add an "R" at the end of the OPN to denote tape and reel ordering options.

- 2. Custom, factory preprogrammed devices are available. Ordering part numbers are assigned by Silicon Labs and the ClockBuilder Pro software utility. Custom part number format is "Si5372A-Axxxxx-GM" where "xxxxx" is a unique numerical sequence representing the preprogrammed configuration.

#### 1.2 Jitter Performance

The outputs of the Si5371 (2-output, same as Si5342H) and Si5372 (4-output, same as Si5344H) can be assigned as either high-speed integer mode capable of up to 2.75 GHz at 45 fs-rms typical phase jitter (1 MHz–40 MHz) or as multiSynth any-frequency mode of up to 750 MHz at 90 fs-rms typical phase jitter (12 kHz-20 MHz).

Table 1.2. RMS Phase Jitter for the Si5371 and Si5372

| Parameter                  | Symbol           | Test Condition                                                                                              | Min | Тур | Max | Unit   |

|----------------------------|------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| RMS Phase Jitter (Grade J) | J <sub>GEN</sub> | High-speed integer mode – f <sub>IN</sub> = 19.44<br>MHz;<br>f <sub>OUT</sub> = 2750 MHz (12 kHz to 20 MHz) | _   | 75  | 90  | fs RMS |

|                            |                  | High-speed integer mode – f <sub>IN</sub> = 19.44<br>MHz;<br>f <sub>OUT</sub> = 2750 MHz (1 MHz to 40 MHz)  | _   | 45  | _   | fs RMS |

|                            |                  | Multisynth Mode – $f_{IN}$ = 19.44 MHz;<br>$f_{OUT}$ = 156.25 MHz (12 kHz to 20 MHz)                        | _   | 90  | 125 | fs RMS |

#### 1.3 Additional Clock Inputs

The Si5371 and Si5372 each have four clock inputs, two more than Si5342H and Si5344H.

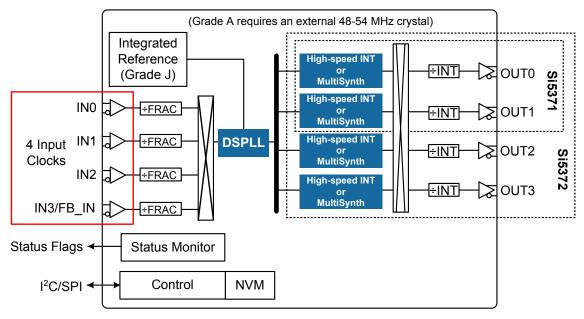

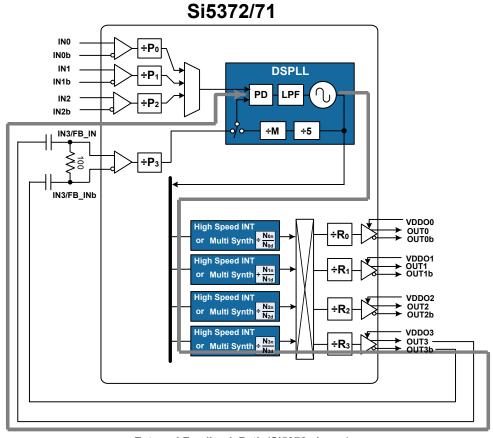

Figure 1.1. Clock Inputs for Si5371 and Si5372

#### 1.4 Frequency-on-the-fly (FOTF) Feature

The Si5371/72 use register writes to support frequency-on-the-fly to allow frequency changes on one MultiSynth without affecting the clocks generated from other MultiSynths. See the Family Reference Manual for more details.

#### 1.5 Input Clock Switching Improvements

Hitless switching and frequency-ramped switching are requirements found in many communications systems that use clock frequency and phase synchronization reference. Switching between two inputs can occur either internally to the Si5371/72 using the internal crosspoint multiplexer or externally via external MUX/FPGA. The Si5371/72 has enhanced hitless switching to deliver low phase and frequency transient for both internal and external switching. Switching between two inputs using the internal crosspoint multiplexer will give lower phase and frequency transient performance compared to external switching.

Hitless and frequency-ramped switching behavior for the Si5371/72 are supported in Skyworks' Clock-Builder™ Pro software version 2.31 or later.

**Table 1.3. Input Clock Switching Comparison**

| Si5342H/44H Operation                                                                                                                                                                                       | Si5371/72 Operation                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Si5342H/44H devices feature hitless switching but may exhibit larger phase/ frequency transients at low phase detector input frequency typically associated with low input clock frequencies (e.g., 8 kHz). | The Si5371/72 devices feature significantly improved hitless switching at all frequencies, including low-phase detector input frequency typically associated with low-input clock frequencies. This includes both manual and automatic reference switching. |

| Si5342H/44H devices have the option to enable a frequency ramp/phase buildout upon exit from holdover or freerun (start-up/reset).                                                                          | Si5371/72 devices have the option of enabling a more precise phase buildout upon exit from holdover or freerun.                                                                                                                                             |

Hitless switching performance is dependent on the phase detector input frequency (Fpfd) associated with the frequency plan. The table below shows the performance with both automatic and manual hitless switching with 8 kHz and 2 MHz Fpfd frequencies at the specified DSPLL bandwidth.

Table 1.4. Hitless Switching Performance Between Two Inputs at the Same Frequency

| Switching             | Fpfd  | DSPLL BW Output Phase Transien |        |

|-----------------------|-------|--------------------------------|--------|

|                       |       |                                | Max    |

| Single Auto or Manual | 2 MHz | 400 Hz                         | 0.3 ns |

| Single Auto or Manual | 8 kHz | 40 Hz                          | 1.5 ns |

#### 1.6 Zero Delay Mode (ZDM) Feature

A zero delay mode is available for applications that require fixed and consistent minimum delay between the selected input and outputs. The zero delay mode is configured by opening the internal feedback loop through software configuration and closing the loop externally as shown in the figure below. (Zero delay mode is only available for clock inputs that are higher than 128 kHz.)

This configuration process helps cancel out the internal delay introduced by the dividers, crosspoint, input, and output drivers. Any one of the outputs can be fed back to the FB\_IN pins, although using the output driver that achieves the shortest trace length will help minimize the input-to-output delay. For Si5372, OUT3 and FB\_IN pins are recommended for the external feedback connection. For Si5371, OUT1 and FB\_IN pins are recommended. The FB\_IN input pins must be terminated and ac-coupled when zero delay mode is used. A differential external feedback path connection is necessary for best performance. Note that the hitless switching feature is not available when zero delay mode is enabled. See the data sheet and reference manual for additional information.

External Feedback Path (Si5372 shown)

Figure 1.2. Zero Delay Mode

#### 1.7 New Standard CMOS DC-Coupled Input

The Si5371/72 devices support standard, non-standard, and pulsed dc-coupled CMOS inputs. Non-standard CMOS and pulsed CMOS are backward compatible to Si5342H/44H; however, standard CMOS is new to Si5371/72.

Regardless of which input type is used, any CMOS input signal that exceeds 3.3 V + 5% must use a resistive attenuation network to guarantee that the input voltage at the pin does not violate the device's input ratings. Refer to the data sheet for input ratings and the Family Reference Manual for more details.

# 2. Migrating from Si5342H/44H to Si5371/72 using CBPro

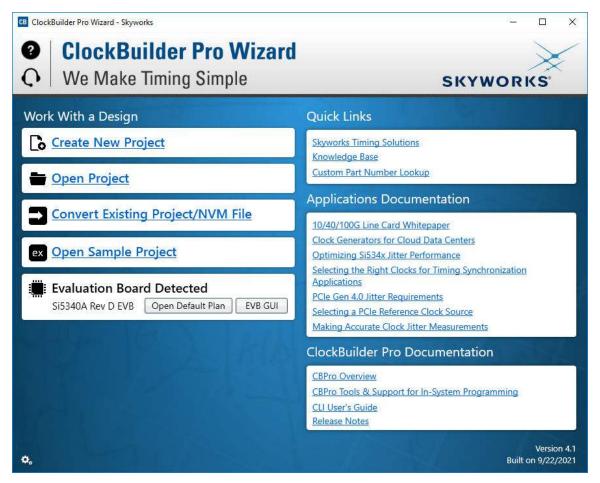

Migration from Si5342H/44H to Si5371/72 can be done with an import tool built into CBPro. First, ensure that the latest version of CBPro (version 2.31 or later) is installed on your computer and follow the steps shown below.

Step 1: Click Convert Existing Project/NVM File on the main page.

Figure 2.1. Migrating to Si5371/72 by Importing an Si5342H/44H Project File

**Step 2:** Select the part that you want to convert from and the new part you want to convert to. Then follow instructions to complete the new project file.

Figure 2.2. Select Part Number to Convert

#### 3. Drop-in Compatible with Si5342H/44H

The Si5371A and Si5372A have two additional inputs compared to the Si5342H/4H, and all four parts use the same 44-QFN package as well as an external reference crystal.

The Si5371J and Si5372J use the new internal reference crystal and have two additional inputs compared to the Si5342H/44H. The Si5371J/72J use a 44-LGA package and the Si5342H/44H use a 44-QFN package.

Customers should consult the product data sheets to compare the specific differences between each of the parts.

Section 2. Migrating from Si5342H/44H to Si5371/72 using CBPro explains how to convert Si5342H/44H project files to new Si5371/72 project files.

# 4. Register Changes

To preserve backward compatibility, all the setting names in Si5342H/44H revision D have been left unchanged in the Si5371/72. Several new registers have been added to support the new features described above.

Writing a Si532H/44H register file to a Si5371/72 device is **not supported**. The project file must first be converted into the Si5371/72 project using the CBPro conversion tool, and then re-exported to a programming file. This will also ensure new device features are enabled correctly.

Details about converting old plans to new plans are provided in Section 2. Migrating from Si5342H/44H to Si5371/72 using CBPro and detailed descriptions of the new features can be found in the reference manual for each device.

# 5. Supporting Documentation

Table 5.1. Related Documentation and Software

| Document/Resource                                                                 | Description/URL                                                                                                                                                                     |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Si5372/71 Family Reference Manual                                                 | To be used in conjunction with the data sheet, which contains more detailed explanations about the operation of the device. Contact a local sales representative for this document. |

| Crystal Reference Manual                                                          | https://www.skyworksinc.com/-/media/Skyworks/SL/documents/public/reference-manuals/si534x-8x-9x-recommended-crystals-rm.pdf                                                         |

| Frequently Asked Questions                                                        | https://www.skyworksinc.com/Products/Timing                                                                                                                                         |

| Quality and Reliability                                                           | https://www.skyworksinc.com/quality                                                                                                                                                 |

| Development Kits                                                                  | https://www.skyworksinc.com/en/Products/Timing                                                                                                                                      |

| ClockBuilder Pro (CBPro) Software                                                 | https://www.skyworksinc.com/en/Application-Pages/Clockbuilder-Pro-Software                                                                                                          |

| AN947: Implementing Zero Delay Mode Using the Si5340/41/42/44/45/80               | https://www.skyworksinc.com/-/media/Skyworks/SL/documents/public/application-notes/AN947.pdf                                                                                        |

| AN1178: Frequency-On-the-Fly for Skyworks Jitter Attenuators and Clock Generators | https://www.skyworksinc.com/-/media/Skyworks/SL/documents/public/application-notes/an1178-frequency-otf-jitter-atten-clock-gen.pdf                                                  |

| Si5372/71 Data Sheet                                                              | Contact a local sales representative for this document.                                                                                                                             |

www.skyworksinc.com/CBPro

**Quality** www.skyworksinc.com/quality

**Support & Resources** www.skyworksinc.com/support

#### Copyright © 2021 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters.

Skyworks, the Skyworks symbol, Sky5®, SkyOne®, SkyBlue™, Skyworks Green™, Clockbuilder®, DSPLL®, ISOmodem®, ProSLIC®, and SiPHY® are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.