# **Low Power Video Op Amp with Disable**

Data Sheet AD810

### **FEATURES**

### **High speed**

80 MHz typical -3 dB bandwidth (G = +1)

75 MHz typical -3 dB bandwidth (G = +2)

1000 V/µs typical slew rate

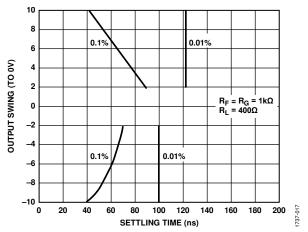

50 ns typical settling time to 0.1% (Vout = 10 V step)

### Ideal for video applications

30 MHz typical 0.1 dB bandwidth (G = +2,  $V_S = \pm 15 \text{ V}$ )

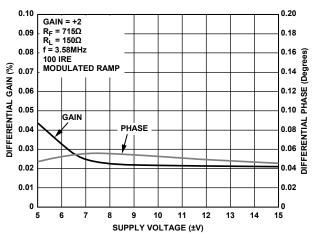

0.02% typical differential gain ( $V_s = \pm 15 \text{ V}$ )

0.04° typical differential phase ( $V_s = \pm 15 \text{ V}$ )

#### Low noise

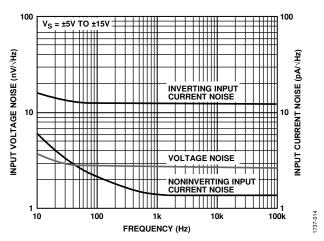

2.9 nV/√Hz typical input voltage noise

13 pA/√Hz typical inverting input current noise

#### Low power

8.0 mA maximum supply current (quiescent)

2.1 mA typical supply current (power-down mode)

### High performance disable function

Turn off time: 100 ns typical

Break before make guaranteed

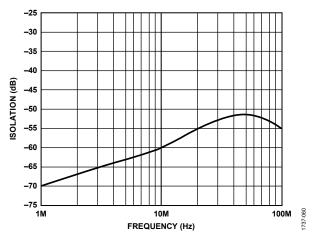

Input to output isolation of 64 dB (off state)

Flexible operation

Specified for ±5 V and ±15 V operation

$\pm 2.9 \text{ V typical output swing into a 150 } \Omega \text{ load } (V_S = \pm 5 \text{ V})$

### **APPLICATIONS**

Professional video cameras

Multimedia systems

NTSC-, PAL-, and SECAM-compatible systems

Video line drivers

ADC or DAC buffers

DC restoration circuits

### **GENERAL DESCRIPTION**

The AD810 is a composite and HDTV-compatible, current feedback, video operational amplifier, ideal for use in systems such as multimedia, digital tape recorders, and video cameras. The 0.1 dB flatness specification at a bandwidth of 30 MHz (G=+2) and the differential gain and phase of 0.02% and 0.04° (NTSC) make the AD810 ideal for any broadcast quality video system. All these specifications are under load conditions of 150  $\Omega$  (one 75  $\Omega$  back terminated cable).

The AD810 is ideal for power sensitive applications such as video cameras, offering a low power supply current of 8.0 mA

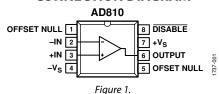

#### CONNECTION DIAGRAM

maximum. The disable feature reduces the power supply current to only 2.1 mA, while the amplifier is not in use, to conserve power. Furthermore, the AD810 is specified over a power supply range of  $\pm 5$  V to  $\pm 15$  V.

The AD810 works well as an ADC or DAC buffer in video systems due to its unity gain (G = +1) -3 dB bandwidth of 80 MHz. Because the AD810 is a transimpedance amplifier, this bandwidth can be maintained over a wide range of gains while featuring a low noise of 2.9 nV/ $\sqrt{\rm Hz}$  for wide dynamic range applications.

# **TABLE OF CONTENTS**

| reatures                                               |

|--------------------------------------------------------|

| Applications1                                          |

| Connection Diagram                                     |

| General Description1                                   |

| Revision History2                                      |

| Specifications3                                        |

| Absolute Maximum Ratings5                              |

| Thermal Resistance                                     |

| Maximum Power Dissipation                              |

| ESD Caution5                                           |

| Pin Configurations and Function Descriptions6          |

| Typical Performance Characteristics                    |

| Test Circuits14                                        |

| Theory of Operation15                                  |

| General Design Considerations15                        |

| Achieving Very Flat Gain Response at High Frequency 15 |

|                                                        |

|   | Choice of Feedback Resistor      | 15 |

|---|----------------------------------|----|

|   | Printed Circuit Board Layout     | 15 |

|   | Quality of Coaxial Cable         | 15 |

|   | Power Supply Bypassing           | 15 |

|   | Power Supply Operating Range     | 15 |

|   | Offset Nulling                   | 16 |

|   | Disable Mode                     | 16 |

| A | pplications Information          | 17 |

|   | Capacitive Loads                 | 17 |

|   | Operation As a Video Line Driver | 18 |

|   | 2:1 Video Multiplexer            | 19 |

|   | 4:1 Multiplexer                  | 20 |

| 0 | outline Dimensions               | 21 |

|   | Ordering Guide                   | 22 |

### **REVISION HISTORY**

### 5/2019—Rev. A to Rev. B

| Updated FormatUniversal                                     |

|-------------------------------------------------------------|

| Changed Vo to Vout and                                      |

| AD810S to 5962-9313201MPAThroughout                         |

| Deleted Closed-Loop Gain and Phase vs. Frequency Plot and   |

| Differential Gain and Phase vs. Supply Voltage Plot 1       |

| Changes to General Description Section                      |

| Changes to Table 1                                          |

| Deleted Figure 2; Renumbered Sequentially4                  |

| Changes to Table 2, Maximum Power Dissipation Section 5     |

| Added Thermal Resistance Section and Table 3; Renumbered    |

| Sequentially5                                               |

| Added Pin Configurations and Function Descriptions Section, |

| Figure 3, Figure 4, Figure 5, and Table 4; Renumbered       |

| Sequentially6                                               |

| Changes to Figure 6 Caption and Figure 7 Caption            |

| Changes to Figure 14 Caption and Figure 16                  |

| Changes to Figure 19                                        |

| Added Test Circuits Section                                 |

| Moved Figure 45 and Figure 46                               |

| Changed Choice of Feedback and Gain Resistor Section to     |

| Choice of Feedback Resistor Section                         |

| Changes to Achieving Very Flat Gain Response at High        |      |

|-------------------------------------------------------------|------|

| Frequency Section, Choice of Feedback Resistor Section, and |      |

| Power Supply Bypassing Section                              | . 15 |

| Moved Figure 45                                             | . 16 |

| Changes to Disable Mode Section                             | . 16 |

| Added Applications Information Section                      | . 17 |

| Moved Capacitive Loads Section and Figure 48 to Figure 51   | . 17 |

| Changes to Figure 48 and Figure 50                          | . 17 |

| Moved Operation As a Video Line Driver Section and Figure   | 52   |

| to Figure 56                                                | . 18 |

| Change to Figure 54                                         | . 18 |

| Moved 2:1 Video Multiplexer Section and Figure 57 to        |      |

| Figure 60                                                   | . 19 |

| Changes to Figure 58                                        | . 19 |

| Moved 4:1 Multiplexer Section and Figure 61 to Figure 63    | . 20 |

| Changes to 4:1 Multiplexer Section                          | . 20 |

| Updated Outline Dimensions                                  | . 21 |

| Changes to Ordering Guide                                   | . 22 |

10/1992—Rev. 0 to Rev. A

## **SPECIFICATIONS**

$T_A$  = 25°C, supply voltage (Vs) = ±15 V dc, load resistance (RL) = 150  $\Omega$ , unless otherwise noted.

Table 1.

|                                    |                                                                                               |      | AD810A |      |      | 5962-9313201MPA <sup>1</sup> | _    |         |

|------------------------------------|-----------------------------------------------------------------------------------------------|------|--------|------|------|------------------------------|------|---------|

| Parameter                          | Test Conditions/Comments                                                                      | Min  | Тур    | Max  | Min  | Тур                          | Max  | Unit    |

| DYNAMIC PERFORMANCE                |                                                                                               |      |        |      |      |                              |      |         |

| −3 dB Bandwidth                    | $G = +2$ , feedback resistor (R <sub>F</sub> ) = 715 $\Omega$ , V <sub>S</sub> = ±5 V         | 40   | 50     |      | 40   | 50                           |      | MHz     |

|                                    | $G = +2$ , $R_F = 715 \Omega$ , $V_S = \pm 15 V$                                              | 55   | 75     |      | 55   | 75                           |      | MHz     |

|                                    | $G = +1$ , $R_F = 1000 \Omega$ , $V_S = \pm 15 V$                                             | 40   | 80     |      | 40   | 80                           |      | MHz     |

|                                    | $G = +10$ , $R_F = 270 \Omega$ , $V_S = \pm 15 V$                                             | 50   | 65     |      | 50   | 65                           |      | MHz     |

| 0.1 dB Bandwidth                   | $G = +2$ , $R_F = 715 \Omega$ , $V_S = \pm 5 V$                                               | 13   | 22     |      | 13   | 22                           |      | MHz     |

|                                    | $G = +2$ , $R_F = 715 \Omega$ , $V_S = \pm 15 V$                                              | 15   | 30     |      | 15   | 30                           |      | MHz     |

| Full Power Bandwidth               | Output voltage (Vout) = 20 V p-p                                                              |      |        |      |      |                              |      |         |

|                                    | $R_L = 400 \Omega$                                                                            |      | 16     |      | 8    | 16                           |      | MHz     |

| Slew Rate <sup>2</sup>             | $R_L = 150 \Omega, V_S = \pm 5 V$                                                             |      | 350    |      | 175  | 350                          |      | V/µs    |

|                                    | $R_L = 400 \Omega, V_S = \pm 15 V$                                                            |      | 1000   |      | 500  | 1000                         |      | V/µs    |

| Settling Time to 0.1%              | 10 V step, G = −1                                                                             |      | 50     |      |      | 50                           |      | ns      |

| Settling Time to 0.01%             | 10 V step, G = −1                                                                             |      | 125    |      |      | 125                          |      | ns      |

| Differential Gain                  | $f = 3.58 \text{ MHz}, V_S = \pm 15 \text{ V}$                                                |      | 0.02   | 0.05 |      | 0.02                         | 0.05 | %       |

|                                    | $f = 3.58 \text{ MHz}, V_S = \pm 5 \text{ V}$                                                 |      | 0.04   | 0.07 |      | 0.04                         | 0.07 | %       |

| Differential Phase                 | $f = 3.58 \text{ MHz}, V_S = \pm 15 \text{ V}$                                                |      | 0.04   | 0.07 |      | 0.04                         | 0.07 | Degrees |

|                                    | $f = 3.58 \text{ MHz}, V_S = \pm 5 \text{ V}$                                                 |      | 0.045  | 0.08 |      | 0.045                        | 0.08 | Degrees |

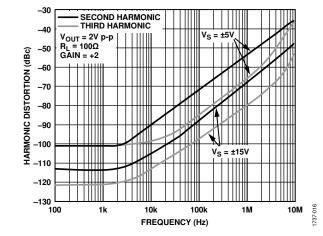

| Total Harmonic<br>Distortion       | f = 10 MHz, V <sub>OUT</sub> = 2 V p-p                                                        |      |        |      |      |                              |      |         |

|                                    | $R_L = 400 \Omega, G = +2$                                                                    |      | -61    |      |      | <b>–61</b>                   |      | dBc     |

| INPUT OFFSET VOLTAGE               | $V_{S} = \pm 5 \text{ V and } \pm 15 \text{ V}$                                               |      | 1.5    | 6    |      | 1.5                          | 6    | mV      |

|                                    | $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 5$ V and $\pm 15$ V                                       |      | 2      | 7.5  |      | 4                            | 15   | mV      |

| Offset Voltage Drift               |                                                                                               |      | 7      |      |      | 15                           |      | μV/°C   |

| INPUT BIAS CURRENT                 |                                                                                               |      |        |      |      |                              |      |         |

| Negative Input                     | $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 5$ V and $\pm 15$ V                                       |      | 0.7    | 5    |      | 0.8                          | 5    | μΑ      |

| Positive Input                     | $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 5$ V and $\pm 15$ V                                       |      | 2      | 7.5  |      | 2                            | 10   | μΑ      |

| OPEN-LOOP<br>TRANSRESISTANCE       | T <sub>MIN</sub> to T <sub>MAX</sub>                                                          |      |        |      |      |                              |      |         |

|                                    | $V_{OUT} = \pm 10 \text{ V}, R_L = 400 \Omega, V_S = \pm 15 \text{ V}$                        | 1.0  | 3.5    |      | 1.0  | 3.5                          |      | ΜΩ      |

|                                    | $V_{OUT} = \pm 2.5 \text{ V}, R_L = 100 \Omega, V_S = \pm 5 \text{ V}$                        | 0.3  | 1.2    |      | 0.2  | 1.0                          |      | ΜΩ      |

| OPEN-LOOP DC VOLTAGE<br>GAIN       | T <sub>MIN</sub> to T <sub>MAX</sub>                                                          |      |        |      |      |                              |      |         |

|                                    | $V_{OUT} = \pm 10 \text{ V}, R_L = 400 \Omega, V_S = \pm 15 \text{ V}$                        | 86   | 100    |      | 80   | 100                          |      | dB      |

|                                    | $V_{OUT} = \pm 2.5 \text{ V}, R_L = 100 \Omega, V_S = \pm 5 \text{ V}$                        | 76   | 88     |      | 72   | 88                           |      | dB      |

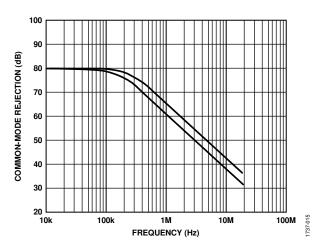

| COMMON-MODE<br>REJECTION           | T <sub>MIN</sub> to T <sub>MAX</sub>                                                          |      |        |      |      |                              |      |         |

| Offset Voltage (Vos)               | Common-mode voltage ( $V_{CM}$ ) = $\pm 12 V$ , $V_S = \pm 15 V$                              | 56   | 64     |      | 56   | 64                           |      | dB      |

|                                    | $V_{CM} = \pm 2.5 \text{ V}, V_{S} = \pm 5 \text{ V}$                                         | 52   | 60     |      | 50   | 60                           |      | dB      |

| Input Bias Current                 | $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 5$ V and $\pm 15$ V                                       |      | 0.1    | 0.4  | -0.4 | 0.1                          | +0.4 | μA/V    |

| POWER SUPPLY REJECTION             |                                                                                               |      |        |      |      |                              |      | 1       |

| Vos                                | $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 4.5$ V to $\pm 18$ V                                      | 65   | 72     |      | 60   | 72                           |      | dB      |

| Input Bias Current                 | T <sub>MIN</sub> to T <sub>MAX</sub>                                                          |      | 0.05   | 0.3  | -0.3 | 0.05                         | +0.3 | μA/V    |

| INPUT VOLTAGE NOISE                | $f = 1 \text{ kHz}, V_S = \pm 5 \text{ V and } \pm 15 \text{ V}$                              |      | 2.9    |      |      | 2.9                          |      | nV/√Hz  |

| INPUT CURRENT NOISE                | Negative input current $(-I_{IN})$ ,<br>f = 1 kHz, V <sub>S</sub> = ±5 V and ±15 V            |      | 13     |      |      | 13                           |      | pA/√Hz  |

|                                    | Positive input current (+ $I_{IN}$ ), f = 1 kHz,<br>V <sub>S</sub> = $\pm$ 5 V and $\pm$ 15 V |      | 1.5    |      |      | 1.5                          |      | pA/√Hz  |

| INPUT COMMON-MODE<br>VOLTAGE RANGE | $V_S = \pm 5 \text{ V}$                                                                       | ±2.5 | ±3.0   |      | ±2.5 | ±3                           |      | V       |

|                                    | $V_S = \pm 15 \text{ V}$                                                                      | ±12  | ±13    |      | ±12  | ±13                          |      | V       |

|                                            |                                                                |       | AD810A               |      |       | 5962-9313201MPA <sup>1</sup> |      |      |

|--------------------------------------------|----------------------------------------------------------------|-------|----------------------|------|-------|------------------------------|------|------|

| Parameter                                  | Test Conditions/Comments                                       | Min   | Тур                  | Max  | Min   | Тур                          | Max  | Unit |

| OUTPUT CHARACTERISTICS                     |                                                                |       |                      |      |       |                              |      |      |

| Output Voltage Swing <sup>3</sup>          | $R_L = 150 \Omega$ , $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 5 V$  | ±2.5  | ±2.9                 |      | ±2.5  | ±2.9                         |      | ٧    |

|                                            | $R_L = 400 \Omega, V_S = \pm 15 V$                             | ±12.5 | ±12.9                |      | ±12.5 | ±12.9                        |      | ٧    |

|                                            | $R_L = 400 \Omega$ , $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 15 V$ | ±12   |                      |      | ±12   |                              |      | ٧    |

| Short-Circuit Current                      |                                                                |       | 150                  |      |       | 150                          |      | mA   |

| Output Current                             | $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 5$ V and $\pm 15$ V        | 40    | 60                   |      | 30    | 60                           |      | mA   |

| OUTPUT RESISTANCE                          | Open loop (5 MHz)                                              |       | 15                   |      |       | 15                           |      | Ω    |

| INPUT CHARACTERISTICS                      |                                                                |       |                      |      |       |                              |      |      |

| Input Resistance                           | Positive input                                                 | 2.5   | 10                   |      | 2.5   | 10                           |      | МΩ   |

|                                            | Negative input                                                 |       | 40                   |      |       | 40                           |      | Ω    |

| Input Capacitance                          | Positive input                                                 |       | 2                    |      |       | 2                            |      | рF   |

| DISABLE CHARACTERISTICS <sup>4</sup>       |                                                                |       |                      |      |       |                              |      |      |

| Off Isolation                              | f = 5 MHz, see Figure 59                                       |       | 64                   |      |       | 64                           |      | dB   |

| Off Output Resistance                      | See Figure 15, R <sub>G</sub> is gain resistor                 |       | $(R_F + R_G)  13 pF$ |      |       | $(R_F + R_G)  13 pF$         |      | Ω    |

| Turn On Time <sup>5</sup>                  | Output impedance (Z <sub>OUT</sub> ) = low, see Figure 59      |       | 170                  |      |       | 170                          |      | ns   |

| Turn Off Time                              | Z <sub>OUT</sub> = high                                        |       | 100                  |      |       | 100                          |      | ns   |

| DISABLE Pin Current                        | $\overline{\text{DISABLE}}$ pin = 0 V, V <sub>S</sub> = ±5 V   |       | 50                   | 75   |       | 50                           | 75   | μΑ   |

|                                            | $\overline{\text{DISABLE}}$ pin = 0 V, V <sub>S</sub> = ±15 V  |       | 290                  | 400  |       | 290                          | 400  | μΑ   |

| Minimum DISABLE Pin                        | $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 5$ V and $\pm 15$ V        |       | 30                   |      | 10    | 30                           | 40   | μΑ   |

| Current to Disable                         |                                                                |       |                      |      |       |                              |      |      |

| POWER SUPPLY                               |                                                                |       |                      |      |       |                              |      |      |

| Operating Range                            | 25°C to T <sub>MAX</sub>                                       | ±2.5  |                      | ±18  | ±2.5  |                              | ±18  | ٧    |

|                                            | T <sub>MIN</sub>                                               | ±3.0  |                      | ±18  | ±3.5  |                              | ±18  | ٧    |

| Quiescent Current                          | $V_S = \pm 5 \text{ V}$                                        |       | 6.7                  | 7.5  |       | 6.7                          | 7.5  | mA   |

|                                            | $V_S = \pm 15 \text{ V}$                                       |       | 6.8                  | 8.0  |       | 6.8                          | 8.0  | mA   |

|                                            | $T_{MIN}$ to $T_{MAX}$ , $V_S = \pm 5$ V and $\pm 15$ V        |       | 8.3                  | 10.0 |       | 9                            | 11.0 | mA   |

| Power-Down Current                         | $V_S = \pm 5 \text{ V}$                                        |       | 1.8                  | 2.3  |       | 1.8                          | 2.3  | mA   |

|                                            | $V_S = \pm 15 \text{ V}$                                       |       | 2.1                  | 2.8  |       | 2.1                          | 2.8  | mA   |

| TEMPERATURE                                |                                                                |       |                      |      |       |                              |      |      |

| Operating Range ( $T_{MIN}$ to $T_{MAX}$ ) |                                                                | -40   |                      | +85  | -55   |                              | +125 | °C   |

$<sup>^1</sup>$  See the Analog Devices military data sheet for 883B specifications.  $^2$  Slew rate measurement is based on 10% to 90% rise time with the amplifier configured for a gain of -10.  $^3$  Voltage swing is defined as useful operating range, not the saturation range.  $^4$  Disable guaranteed break before make.  $^5$  Turn on time is defined with  $\pm 5$  V supplies using complementary output CMOS to drive the disable pin.

### **ABSOLUTE MAXIMUM RATINGS**

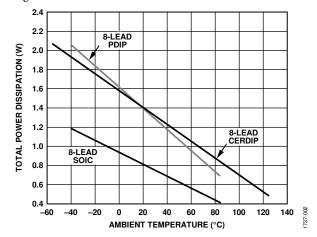

Table 2.

| Parameter                                  | Rating          |  |  |  |  |  |

|--------------------------------------------|-----------------|--|--|--|--|--|

| Supply Voltage                             | ±18 V           |  |  |  |  |  |

| Internal Power Dissipation                 | See Figure 2    |  |  |  |  |  |

| Output Short-Circuit Duration <sup>1</sup> | See Figure 2    |  |  |  |  |  |

| Common-Mode Input Voltage                  | ±V <sub>S</sub> |  |  |  |  |  |

| Differential Input Voltage                 | ±6 V            |  |  |  |  |  |

| Storage Temperature Range                  |                 |  |  |  |  |  |

| PDIP                                       | −65°C to +125°C |  |  |  |  |  |

| CERDIP                                     | −65°C to +150°C |  |  |  |  |  |

| SOIC_N                                     | −65°C to +125°C |  |  |  |  |  |

| Operating Temperature Range                |                 |  |  |  |  |  |

| AD810A                                     | -40°C to +85°C  |  |  |  |  |  |

| 5962-9313201MPA                            | −55°C to +125°C |  |  |  |  |  |

| Junction Temperature                       |                 |  |  |  |  |  |

| AD810A                                     | 145°C           |  |  |  |  |  |

| 5962-9313201MPA                            | 175°C           |  |  |  |  |  |

| Lead Temperature Range (Soldering 60 sec)  | 300°C           |  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup> Internal short-circuit protection may not be sufficient to guarantee that the maximum junction temperature is not exceeded under all conditions.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one-cubic foot sealed enclosure.

**Table 3. Thermal Resistance**

| Package Type | θ <sub>JA</sub> | Unit |

|--------------|-----------------|------|

| N-8          | 90              | °C/W |

| Q-8          | 110             | °C/W |

| R-8          | 150             | °C/W |

#### MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the AD810 is limited by the associated rise in junction temperature. To ensure proper operation, it is important to observe the derating curves in Figure 2.

Figure 2. Total Power Dissipation vs. Ambient Temperature

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 5. 8-Lead SOIC Pin Configuration

Figure 3. 8-Lead PDIP Pin Configuration

Figure 4. 8-Lead CERDIP Pin Configuration

**Table 4. Pin Function Descriptions**

| 14010 11 111 1 | Tuble II I II I unetton bettiption |                                                        |  |  |  |  |  |

|----------------|------------------------------------|--------------------------------------------------------|--|--|--|--|--|

| Pin No.        | Mnemonic                           | Mnemonic Description                                   |  |  |  |  |  |

| 1, 5           | OFFSET NULL                        | Inverting Input Offset Null Connection. See Figure 47. |  |  |  |  |  |

| 2              | -IN                                | Inverting Input.                                       |  |  |  |  |  |

| 3              | +IN                                | Noninverting Input.                                    |  |  |  |  |  |

| 4              | -Vs                                | Negative Supply Voltage.                               |  |  |  |  |  |

| 6              | OUTPUT                             | Output.                                                |  |  |  |  |  |

| 7              | +Vs                                | Positive Supply Voltage.                               |  |  |  |  |  |

| 8              | DISABLE                            | Disable (Active Low).                                  |  |  |  |  |  |

## TYPICAL PERFORMANCE CHARACTERISTICS

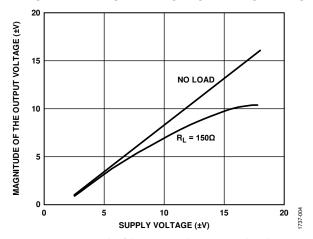

Figure 6. Magnitude of the Output Voltage vs. Supply Voltage

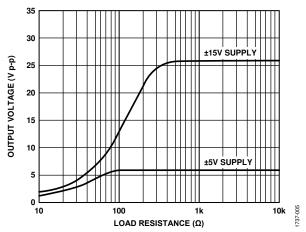

Figure 7. Output Voltage vs. Load Resistance

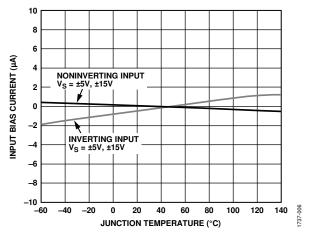

Figure 8. Input Bias Current vs. Junction Temperature

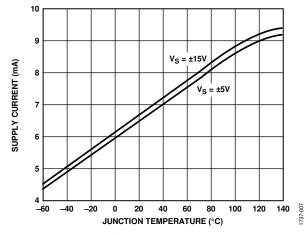

Figure 9. Supply Current vs. Junction Temperature

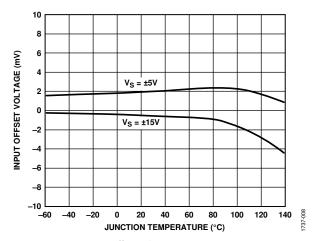

Figure 10. Input Offset Voltage vs. Junction Temperature

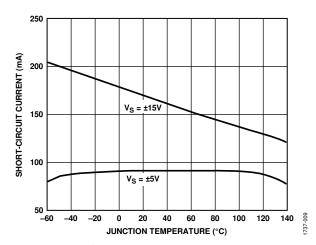

Figure 11. Short-Circuit Current vs. Junction Temperature

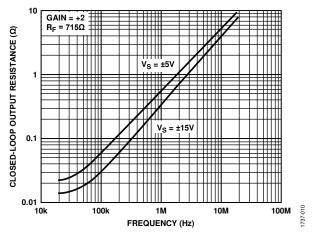

Figure 12. Closed-Loop Output Resistance vs. Frequency

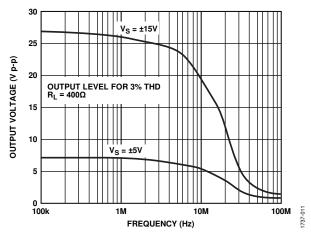

Figure 13. Large Signal Frequency Response

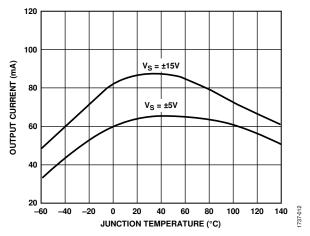

Figure 14. Output Current vs. Junction Temperature

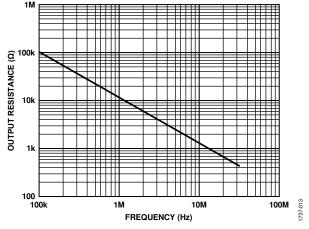

Figure 15. Output Resistance vs. Frequency, Disabled State

Figure 16. Input Voltage Noise and Input Current Noise vs. Frequency

Figure 17. Common-Mode Rejection vs. Frequency

Figure 18. Harmonic Distortion vs. Frequency ( $R_L = 100 \Omega$ )

Figure 19. Output Swing (to 0 V) vs. Settling Time at Various Error Levels

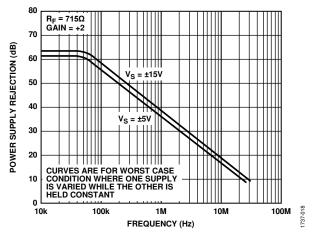

Figure 20. Power Supply Rejection vs. Frequency

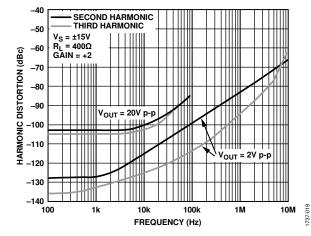

Figure 21. Harmonic Distortion vs. Frequency ( $R_L = 400 \Omega$ )

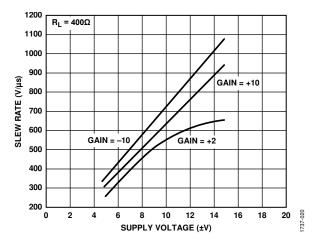

Figure 22. Slew Rate vs. Supply Voltage

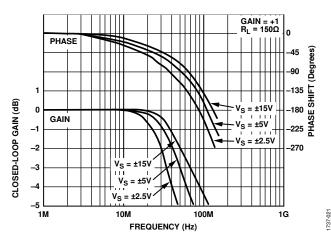

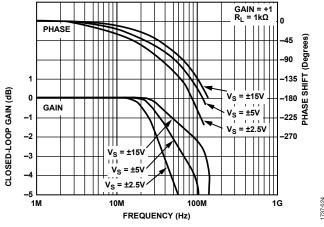

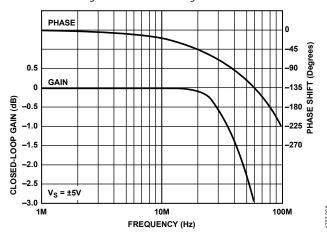

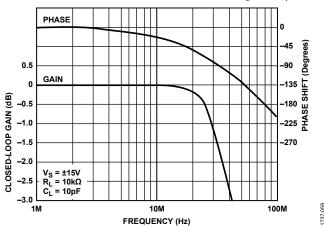

Figure 23. Closed-Loop Gain and Phase Shift vs. Frequency, G=+1,  $R_F=1$  k $\Omega$  for  $\pm$ 15 V, 910  $\Omega$  for  $\pm$ 5 V and  $\pm$ 2.5 V

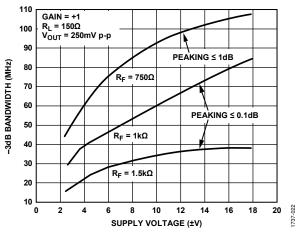

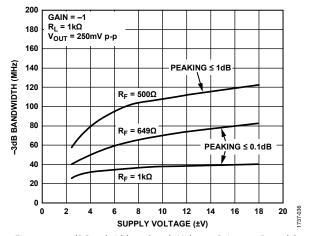

Figure 24. -3 dB Bandwidth vs. Supply Voltage, Gain = +1,  $R_L = 150~\Omega$

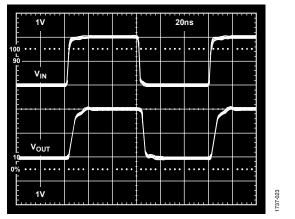

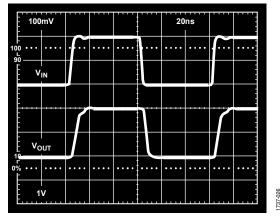

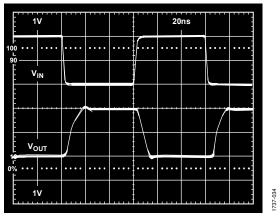

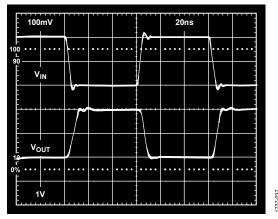

Figure 25. Small Signal Pulse Response, Gain = +1,  $R_F$  = 1  $k\Omega$ ,  $R_L$  = 150  $\Omega$ ,  $V_S$  =  $\pm$ 15 V

Figure 26. Closed-Loop Gain and Phase Shift vs. Frequency, G=+1,  $R_F=1$  k $\Omega$  for  $\pm 15$  V, 910  $\Omega$  for  $\pm 5$  V and  $\pm 2.5$  V

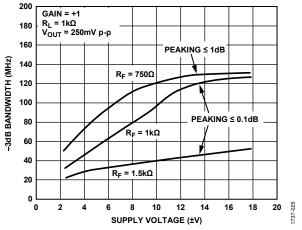

Figure 27. –3 dB Bandwidth vs. Supply Voltage, G = +1,  $R_L = 1 \text{ k}\Omega$

Figure 28. Small Signal Pulse Response, Gain = +10,  $R_F$  = 442  $\Omega$ ,  $R_L$  = 150  $\Omega$ ,  $V_S$  = ±15 V

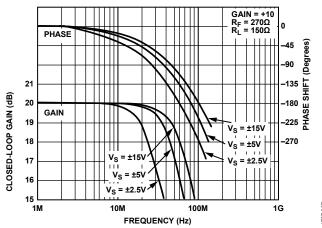

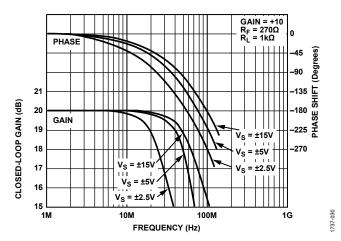

Figure 29. Closed-Loop Gain and Phase Shift vs. Frequency,  $G=+10, R_L=150~\Omega$

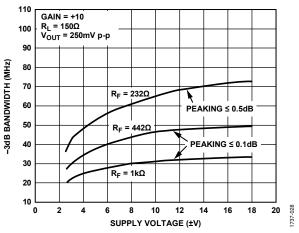

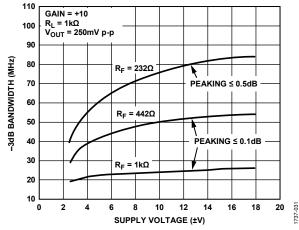

Figure 30. -3 dB Bandwidth vs. Supply Voltage, Gain = +10,  $R_L = 150 \Omega$

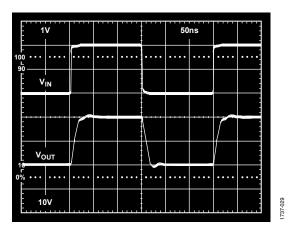

Figure 31. Large Signal Pulse Response, Gain = +10, R\_F = 442  $\Omega$ , R\_L = 400  $\Omega$ ,  $V_S$  =  $\pm 15~V$

Figure 32. Closed-Loop Gain and Phase Shift vs. Frequency,  $G=+10,\,R_L=1\,k\Omega$

Figure 33. –3 dB Bandwidth vs. Supply Voltage, Gain = +10,  $R_L$  = 1  $k\Omega$

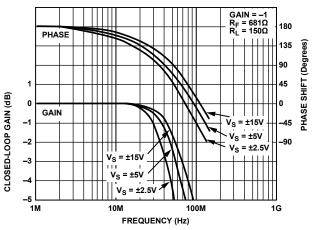

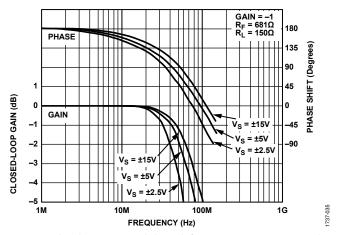

Figure 34. Closed-Loop Gain and Phase Shift vs. Frequency G=-1,  $R_L=150~\Omega$ ,  $R_F=681~\Omega$  for  $\pm15~V$ ,  $620~\Omega$  for  $\pm5~V$  and  $\pm2.5~V$

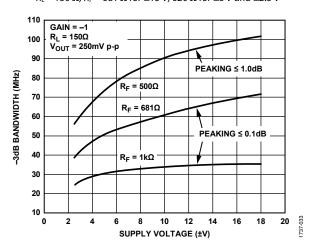

Figure 35. -3 dB Bandwidth vs. Supply Voltage, Gain = -1,  $R_L = 150 \Omega$

Figure 36. Small Signal Pulse Response, Gain = -1,  $R_F = 681~\Omega$ ,  $R_L = 150~\Omega$ ,  $V_S = \pm 5~V$

Figure 37. Closed-Loop Gain and Phase Shift vs. Frequency, G=-1,  $R_L=1$  k $\Omega$ ,  $R_F=681$   $\Omega$  for  $V_S=\pm15$  V, 620  $\Omega$  for  $\pm5$  V and  $\pm2.5$  V

Figure 38. –3 dB Bandwidth vs. Supply Voltage, Gain = –1,  $R_L$  = 1  $k\Omega$

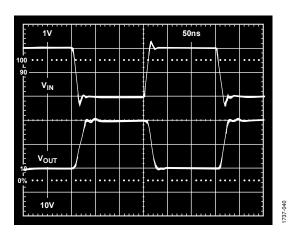

Figure 39. Small Signal Pulse Response, Gain = -10,  $R_F$  = 442  $\Omega$ ,  $R_L$  = 150  $\Omega$ ,  $V_S$  =  $\pm 15~V$

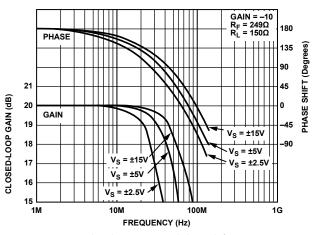

Figure 40. Closed-Loop Gain and Phase Shift vs. Frequency, G=-10,  $R_L=150~\Omega$

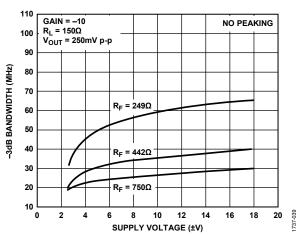

Figure 41. -3 dB Bandwidth vs. Supply Voltage, G = -10,  $R_L = 150 \Omega$

Figure 42. Large Signal Pulse Response, Gain = -10,  $R_F$  = 442  $\Omega$ ,  $R_L$  = 400  $\Omega$ ,  $V_S$  =  $\pm 15~V$

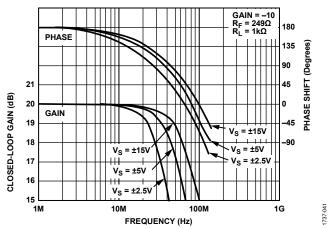

Figure 43. Closed-Loop Gain and Phase Shift vs. Frequency,  $G=-10, R_L=1 \ k\Omega$

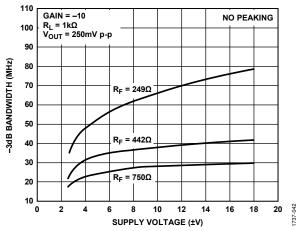

Figure 44. -3 dB Bandwidth vs. Supply Voltage, G=-10,  $R_L=1$   $k\Omega$

## **TEST CIRCUITS**

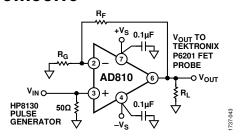

Figure 45. Noninverting Amplifier Connection

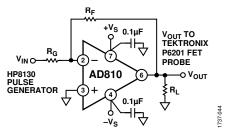

Figure 46. Inverting Amplifier Connection

# THEORY OF OPERATION GENERAL DESIGN CONSIDERATIONS

The AD810 is a current feedback amplifier optimized for use in high performance video and data acquisition systems. Because the AD810 uses a current feedback architecture, its closed-loop bandwidth depends on the value of the feedback resistor. Table 5 and Table 6 list recommended resistor values for some useful closed-loop gains and supply voltages. As shown in Table 5 and Table 6, the closed-loop bandwidth is not a strong function of gain, as it is for a voltage feedback amplifier. The recommended resistor values results in maximum bandwidths with less than 0.1 dB of peaking in the gain vs. frequency response.

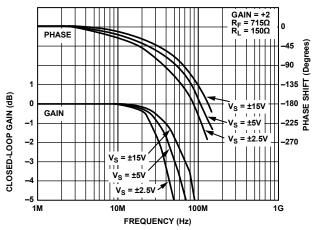

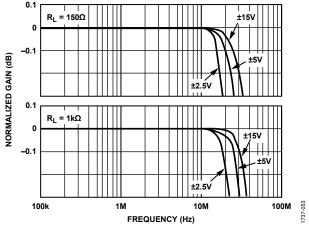

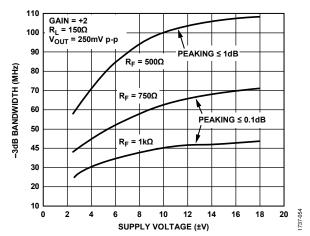

The -3 dB bandwidth is also somewhat dependent on the power supply voltage. Lowering the supplies increases the values of internal capacitances, reducing the bandwidth. To compensate for this reduction, smaller values of feedback resistor are sometimes used at lower supply voltages. The characteristic curves in Figure 23 and Figure 24 illustrate that bandwidths of over 100 MHz on 30 V total supplies and over 50 MHz on 5 V total supplies can be achieved.

Table 5. –3 dB Bandwidth vs. Closed-Loop Gain and Resistance Values ( $R_L = 150 \Omega$ ),  $V_S = \pm 15 V$

| Closed-Loop Gain | R <sub>F</sub> | R <sub>G</sub> | -3 dB Bandwidth (MHz) |

|------------------|----------------|----------------|-----------------------|

| +1               | 1 kΩ           | Open           | 80                    |

| +2               | 715 Ω          | 715 Ω          | 75                    |

| +10              | 270 Ω          | 30 Ω           | 65                    |

| -1               | 681 Ω          | 681 Ω          | 70                    |

| -10              | 249 Ω          | 24.9 Ω         | 65                    |

Table 6. –3 dB Bandwidth vs. Closed-Loop Gain and Resistance Values ( $R_L = 150 \Omega$ ),  $V_S = \pm 5 V$

| Closed-Loop Gain | R <sub>F</sub> | R <sub>G</sub> | -3 dB Bandwidth (MHz) |

|------------------|----------------|----------------|-----------------------|

| +1               | 910 Ω          | Open           | 50                    |

| +2               | 715 Ω          | 715 Ω          | 50                    |

| +10              | 270 Ω          | 30 Ω           | 50                    |

| -1               | 620 Ω          | 620 Ω          | 55                    |

| -10              | 249 Ω          | 24.9 Ω         | 50                    |

# ACHIEVING VERY FLAT GAIN RESPONSE AT HIGH FREQUENCY

Achieving and maintaining gain flatness of less than 0.1 dB above 10 MHz is not difficult if the recommended resistor values are used. Additionally, consider feedback resistor selection, PCB layout, coaxial cable quality, power supply bypassing and operating range, and offset nulling to ensure consistently optimal results.

### **CHOICE OF FEEDBACK RESISTOR**

Because the 3 dB bandwidth depends on the feedback resistor, the fine scale flatness varies to some extent with feedback resistor tolerance. It is recommended that resistors with a 1% tolerance be used to maintain exceptional flatness through high volume production.

### PRINTED CIRCUIT BOARD LAYOUT

As with all wideband amplifiers, PCB parasitics can affect the overall closed-loop performance. Most important are stray capacitances at the output and inverting input nodes. (An added capacitance of 2 pF between the inverting input and ground adds about 0.2 dB of peaking in the gain of 2 response, and increase the bandwidth to 105 MHz). Leave space (3/16 inches is sufficient) around the signal lines to minimize coupling. Also, keep signal lines connecting the feedback and gain resistors short enough so that their associated inductance does not cause high frequency gain errors. Line lengths less than ¼ inches are recommended.

### **OUALITY OF COAXIAL CABLE**

Optimum flatness when driving a coaxial cable is possible only when the driven cable is terminated at each end with a resistor matching its characteristic impedance. With an ideal coaxial cable, the resulting flatness is not affected by the length of the cable. Although outstanding results can be achieved using inexpensive cables, some variation in flatness due to varying cable lengths is to be expected.

### POWER SUPPLY BYPASSING

Adequate power supply bypassing can be critical when optimizing the performance of a high frequency circuit. Inductance in the power supply leads can contribute to resonant circuits that produce peaking in the amplifier response. Although the recommended 0.1  $\mu F$  power supply bypass capacitors are sufficient in most applications, more elaborate bypassing (such as using two paralleled capacitors) may be required in some cases. In addition, if large current transients must be delivered to the load, bypass capacitors (typically greater than 1  $\mu F$ ) are required to optimize settling time and lowest distortion.

### **POWER SUPPLY OPERATING RANGE**

The AD810 operates with supplies from  $\pm 18$  V down to about  $\pm 2.5$  V. On  $\pm 2.5$  V supplies, the low distortion output voltage swing is greater than 1 V p-p. Single-supply operation can be achieved by biasing the input common-mode voltage at the supply midpoint.

### **OFFSET NULLING**

A 10  $k\Omega$  potentiometer connected between Pin 1 and Pin 5, with its wiper connected to  $+V_{S}$  can be used to trim out the inverting input current (with about  $\pm 20~\mu A$  of range). For closed-loop gains above about 5, this configuration may not be sufficient to trim the output offset voltage to zero. Tie the potentiometer wiper to ground through a large value resistor (50  $k\Omega$  for  $\pm 5~V$  supplies, 150  $k\Omega$  for  $\pm 15~V$  supplies) to trim the output to zero at high closed-loop gains.

Figure 47. Offset Null Configuration

### **DISABLE MODE**

By pulling the voltage on Pin 8 to ground (0 V), the AD810 can be put into a disabled state. In this condition, the supply current drops to less than 2.8 mA, the output becomes high impedance, and there is a high level of isolation from input to output. In the case of a line driver, for example, the output impedance is about the same as for a 1.5 k $\Omega$  resistor (the feedback plus gain resistors) in parallel with a 13 pF capacitor (due to the output) and the input to output isolation is greater than 65 dB at 1 MHz.

Leaving the disable pin disconnected (floating) keeps the AD810 operational in the enabled state.

The input impedance of the disable pin is about 35 k $\Omega$  in parallel with a few pF. When grounded, about 50  $\mu$ A flows out of the  $\overline{DISABLE}$  pin for  $\pm 5$  V supplies. If driven by complementary output CMOS logic, the disable time (until the output goes high impedance) is about 100 ns and the enable time (to low impedance output) is about 170 ns on  $\pm 5$  V supplies. The enable time can be extended to about 750 ns by using open-drain logic.

When operated on  $\pm 15$  V supplies, the AD810 disable pin can be driven by open-drain logic. In this case, adding a 10 k $\Omega$  pull-up resistor from the  $\overline{DISABLE}$  pin to the positive supply decreases the enable time to about 150 ns. If there is a nonzero voltage present on the amplifier output at the time the device is switched to the disabled state, some additional decay time is required for the output voltage to decrease to zero. The total time for the output to go to zero is generally about 250 ns and is somewhat dependent on the load impedance.

In cases where the amplifier is driving a high impedance load, the input to output isolation decreases significantly if the input signal is greater than about 1.2 V p-p. The isolation can be restored back to the 65 dB level by adding an extra load (for example, 150  $\Omega$ ) at the amplifier output. This additional load attenuates the feedthrough signal. (This decreased isolation is not an issue for multiplexer applications where the outputs of multiple AD810 devices are tied together as long as at least one channel is in the on state.)

# APPLICATIONS INFORMATION CAPACITIVE LOADS

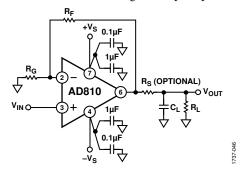

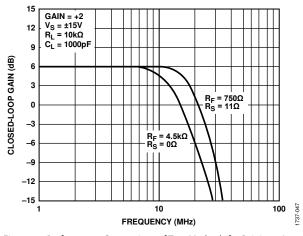

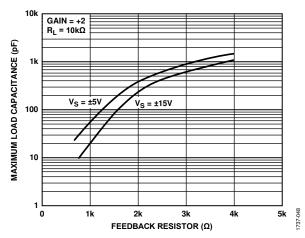

When used with the appropriate feedback resistor, the AD810 can drive capacitive loads exceeding 1000 pF directly without oscillation. By using the curves in Figure 50 to choose the resistor value, less than 1 dB of peaking can easily be achieved without sacrificing much bandwidth. Note that the curves in Figure 50 were generated for the case of a 10 k $\Omega$  load resistor. For smaller load resistances, the peaking is less than indicated by Figure 50.

Another method of compensating for large load capacitances is to insert a resistor in series (Rs) with the loop output, as shown in Figure 48. In most cases, less than 50  $\Omega$  is all that is needed to achieve an extremely flat gain response.

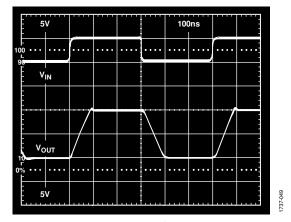

Figure 49 to Figure 51 illustrate the outstanding performance that can be achieved when driving a 1000 pF capacitor.

Figure 48. Circuit Options for Driving a Large Capacitive Load

Figure 49. Performance Comparison of Two Methods for Driving a Large Capacitive Load

Figure 50. Maximum Load Capacitance vs. Feedback Resistor, Peaking < 1 dB

Figure 51. AD810 Driving a 1000 pF Load, Gain = +2,  $R_F$  = 750  $\Omega$ ,  $R_S$  = 11  $\Omega$ ,  $R_L$  = 10  $k\Omega$

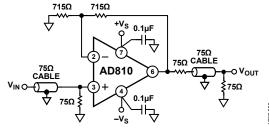

### **OPERATION AS A VIDEO LINE DRIVER**

The AD810 is designed to offer outstanding performance at closed-loop gains of 1 or greater. At a gain of 2, the low differential gain and phase errors and wide -0.1 dB bandwidth are nearly independent of supply voltage and load (as shown in Figure 53 through Figure 55) making the AD810 an excellent video line driver.

Figure 52. Video Line Driver Operating at Gain = +2

Figure 53. Closed-Loop Gain and Phase Shift vs. Frequency, G=+2,  $R_L=150~\Omega$ ,  $R_F=715~\Omega$

Figure 54. Differential Gain and Differential Phase vs. Supply Voltage

Figure 55. Normalized Gain vs. Frequency for Various Supply Voltages, Gain = +2,  $R_F = 715 \Omega$

Figure 56. –3 dB Bandwidth vs. Supply Voltage, G = +2,  $R_L = 150 \Omega$

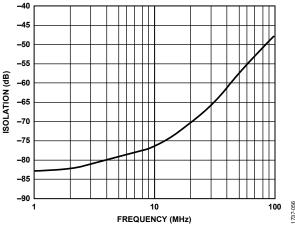

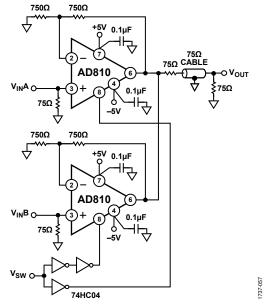

### 2:1 VIDEO MULTIPLEXER

The outputs of two AD810 devices can be wired together to form a 2:1 mux without degrading the flatness of the gain response. Figure 59 shows a recommended configuration that results in  $-0.1~\rm dB$  bandwidth of 20 MHz and off channel isolation of 77 dB at 10 MHz on  $\pm 5~\rm V$  supplies. The time to switch between channels is about 0.75  $\mu s$  when the  $\overline{\rm DISABLE}$  pins are driven by open-drain output logic. Adding pull-up resistors to the logic outputs or using complementary output logic (such as the 74HC04) reduces the switching time to about 180 ns. The switching time is only slightly affected by the signal level.

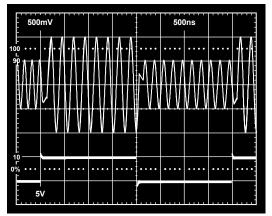

Figure 57. Channel Switching Time for the 2:1 Mux

Figure 58. Isolation vs. Frequency for 2:1 Mux, Off Channel

Figure 59. A Fast Switching 2:1 Video Mux

Figure 60. Closed-Loop Gain and Phase Shift vs. Frequency for 2:1 Mux, On Channel

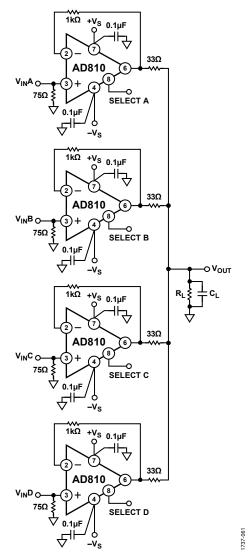

### **4:1 MULTIPLEXER**

A multiplexer of arbitrary size can be formed by combining the desired number of AD810 devices together with the appropriate selection logic. The schematic in Figure 63 shows a recommendation for a 4:1 mux, which can be useful for driving a high impedance such as the input to a video ADC. The output series resistors effectively compensate for the combined output capacitance of the off channels plus the input capacitance of the ADC while maintaining wide bandwidth. In the case illustrated in Figure 63, the -0.1 dB bandwidth is about 20 MHz with no peaking. Switching time and off channel isolation (for the 4:1 mux) are about 250 ns and 60 dB at 10 MHz, respectively.

Figure 61. Closed-Loop Gain and Phase Shift vs. Frequency for 4:1 Mux, On Channel

Figure 62. Isolation vs. Frequency for 4:1 Mux, Off Channel

Figure 63. 4:1 Multiplexer Driving a High Impedance

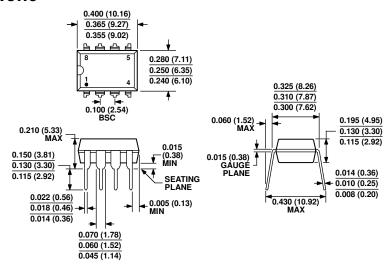

### **OUTLINE DIMENSIONS**

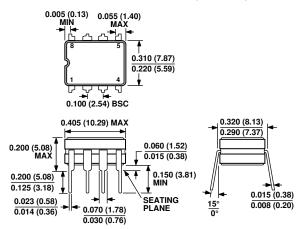

### COMPLIANT TO JEDEC STANDARDS MS-001

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 64. 8-Lead Plastic Dual In-Line Package [PDIP] Narrow Body (N-8)

Dimensions shown in inches and (millimeters)

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 65. 8-Lead Ceramic Dual In-Line Package [CERDIP] (Q-8) Dimensions shown in inches and (millimeters)

Rev. B | Page 21 of 22

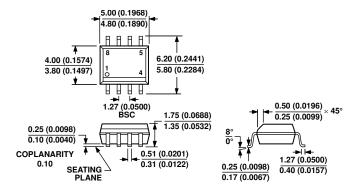

COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 66. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                    | Package Option |

|--------------------|-------------------|--------------------------------------------------------|----------------|

| AD810ANZ           | -40°C to +85°C    | 8-Lead Plastic Dual In-Line Package [PDIP]             | N-8            |

| AD810ARZ           | -40°C to +85°C    | 8-Lead Plastic Standard Small Outline Package [SOIC_N] | R-8            |

| AD810ARZ-REEL      | -40°C to +85°C    | 8-Lead Plastic Standard Small Outline Package [SOIC_N] | R-8            |

| AD810ARZ-REEL7     | -40°C to +85°C    | 8-Lead Plastic Standard Small Outline Package [SOIC_N] | R-8            |

| 5962-9313201MPA    | −55°C to +125°C   | 8-Lead Ceramic Dual In-Line Package [CERDIP]           | Q-8            |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.